Fig 1 Tempos de propagao e de transio

- Slides: 27

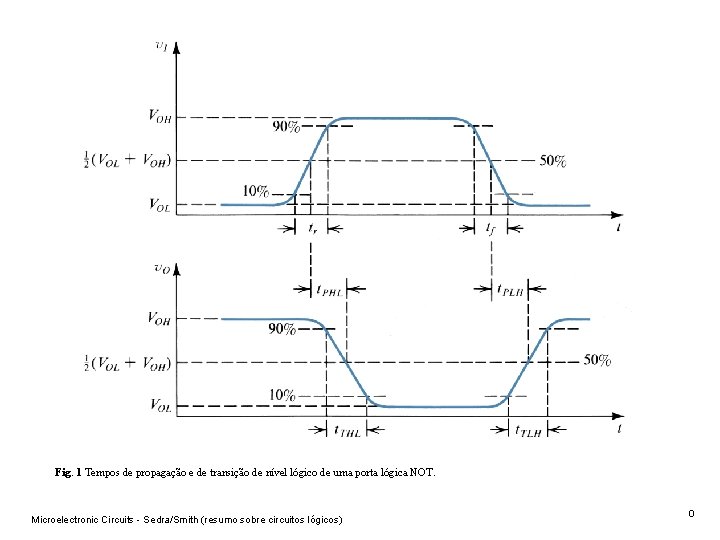

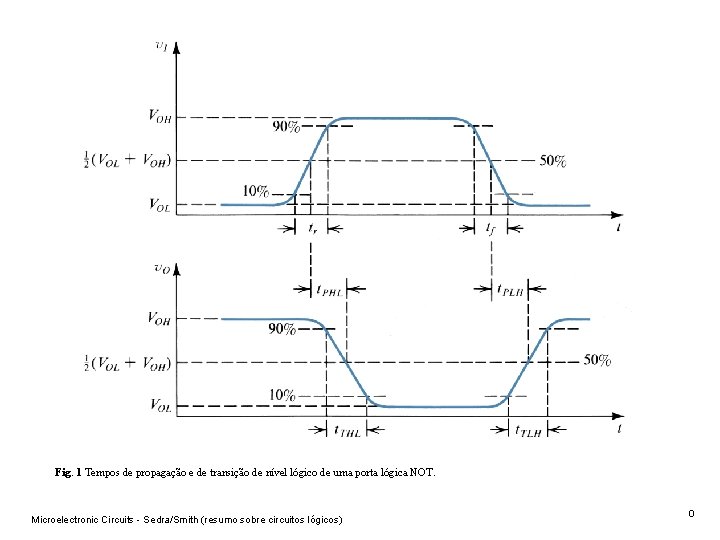

Fig. 1 Tempos de propagação e de transição de nível lógico de uma porta lógica NOT. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 0

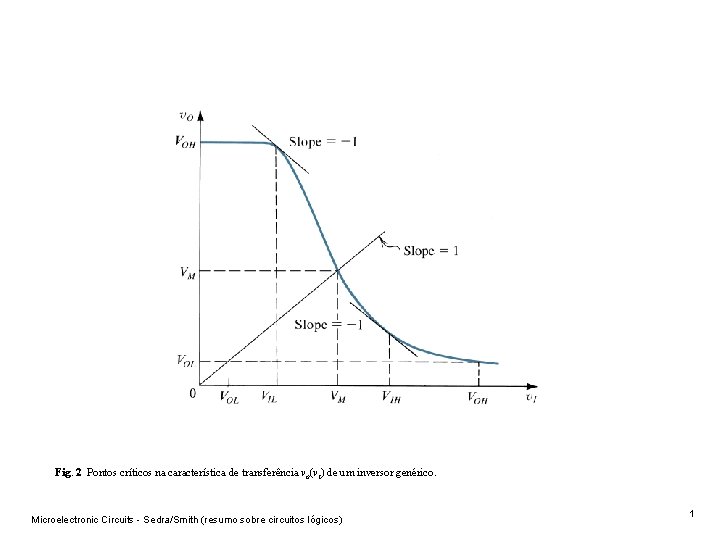

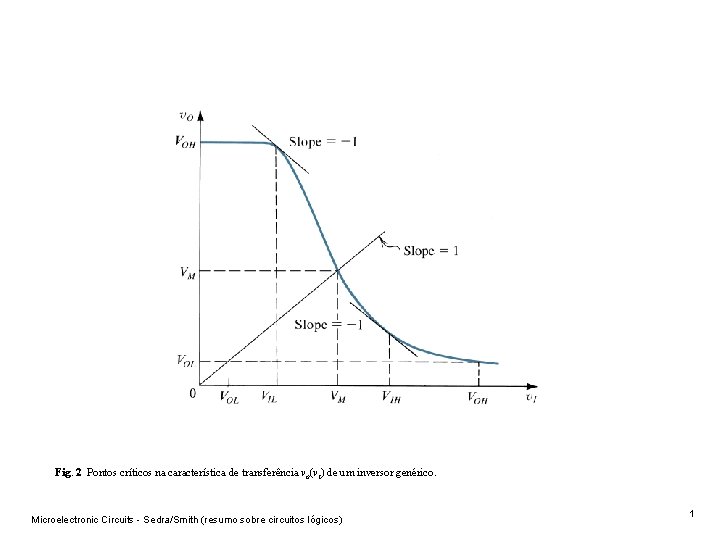

Fig. 2 Pontos críticos na característica de transferência v o(v i) de um inversor genérico. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 1

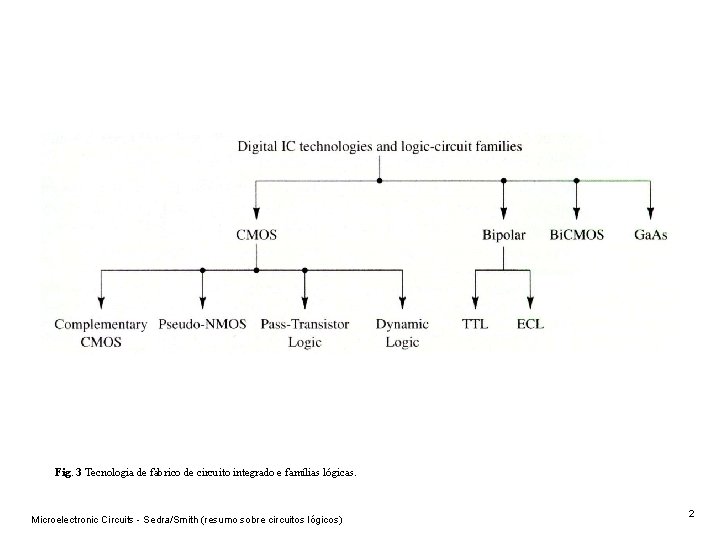

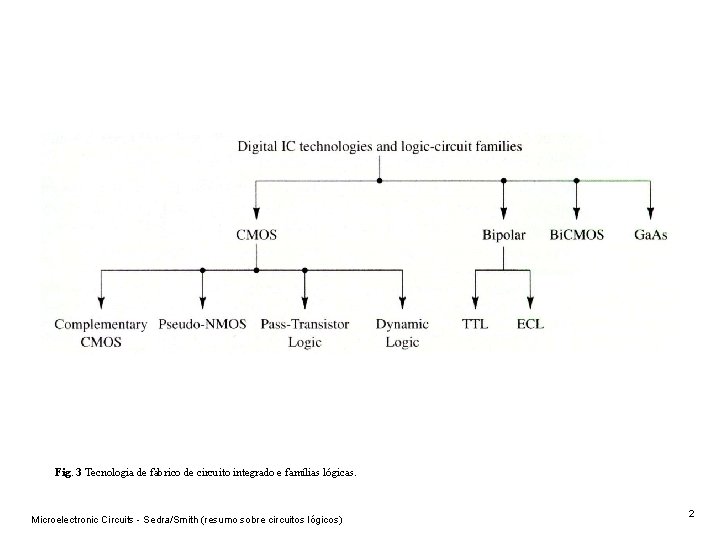

Fig. 3 Tecnologia de fabrico de circuito integrado e famílias lógicas. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 2

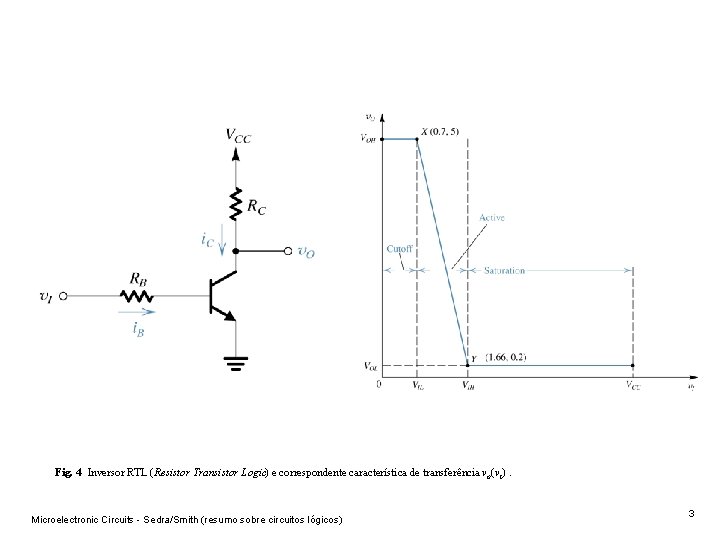

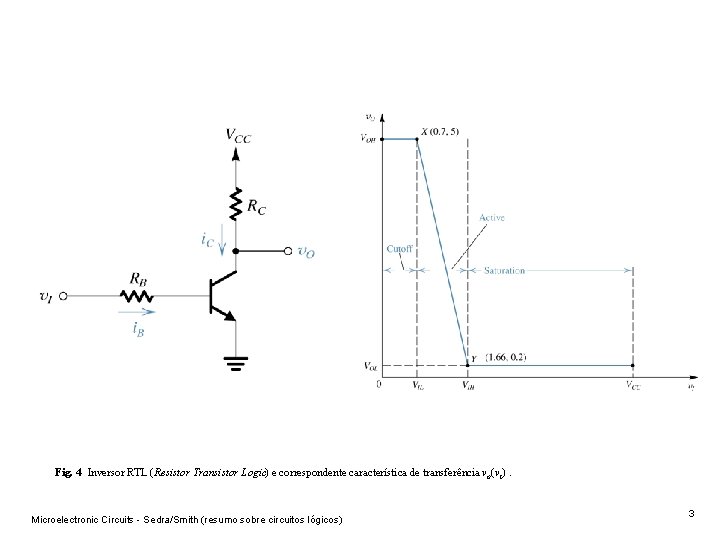

Fig. 4 Inversor RTL (Resistor Transistor Logic) e correspondente característica de transferência v o(v i). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 3

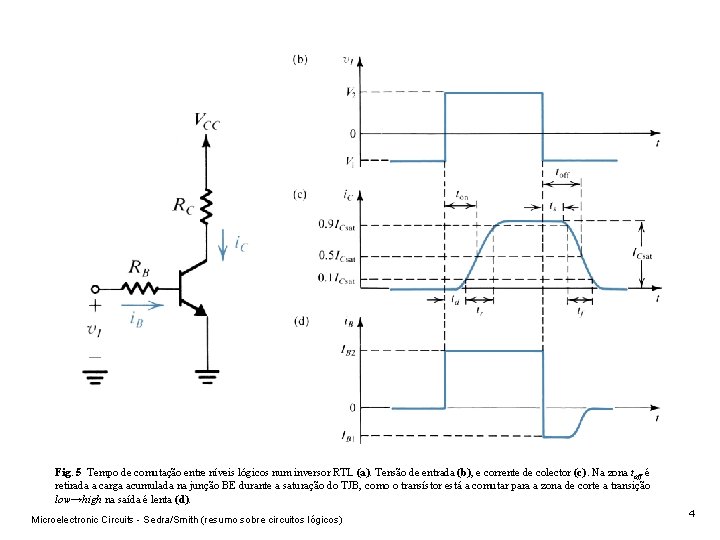

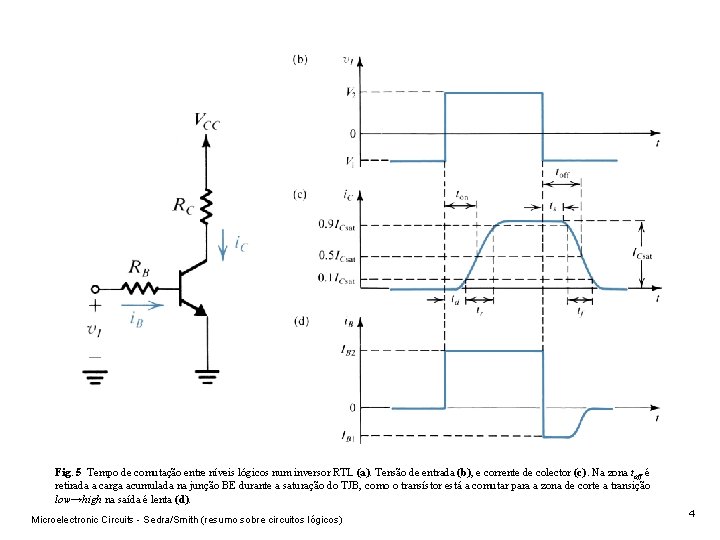

Fig. 5 Tempo de comutação entre níveis lógicos num inversor RTL (a). Tensão de entrada (b), e corrente de colector (c). Na zona toff é retirada a carga acumulada na junção BE durante a saturação do TJB, como o transístor está a comutar para a zona de corte a transição low→high na saída é lenta (d). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 4

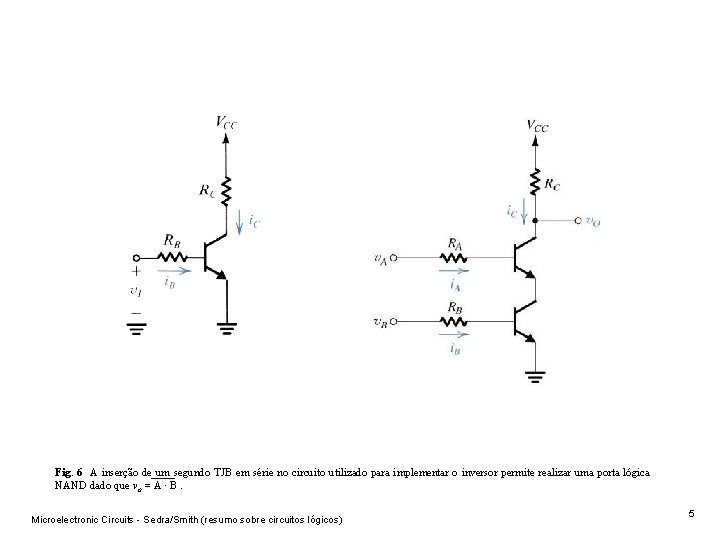

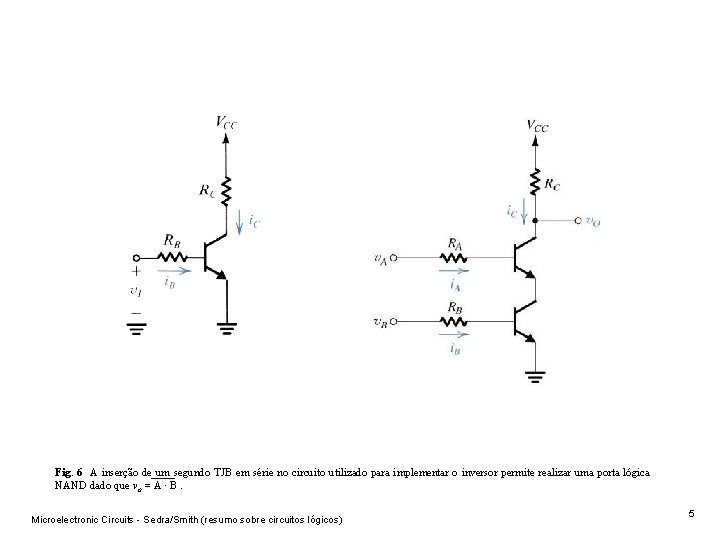

Fig. 6 A inserção de um segundo TJB em série no circuito utilizado para implementar o inversor permite realizar uma porta lógica NAND dado que v o = A · B. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 5

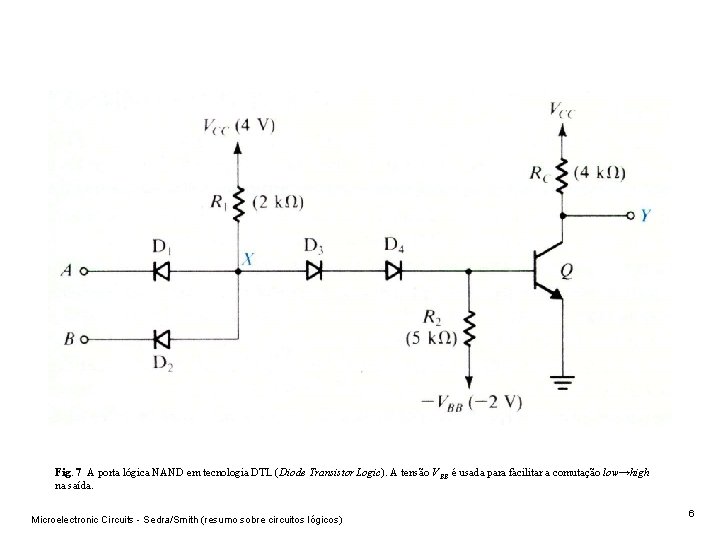

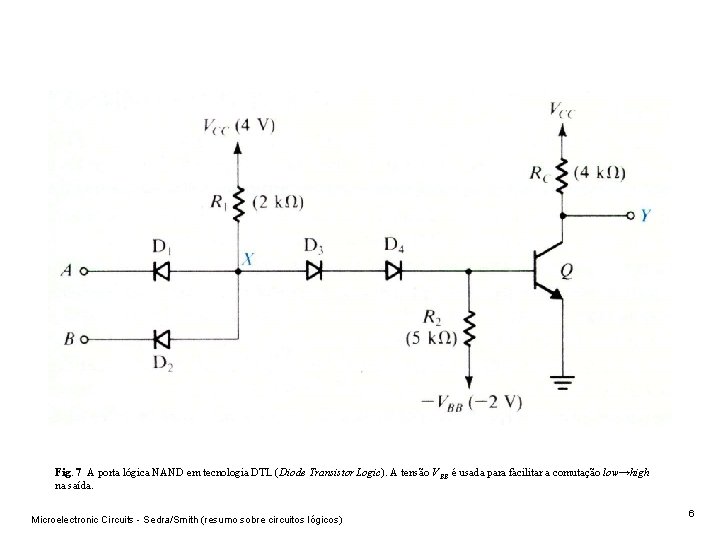

Fig. 7 A porta lógica NAND em tecnologia DTL (Diode Transistor Logic). A tensão V BB é usada para facilitar a comutação low→high na saída. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 6

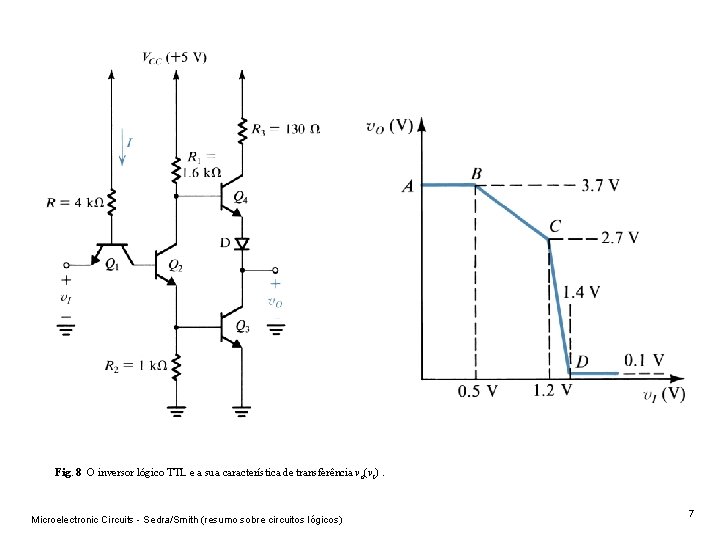

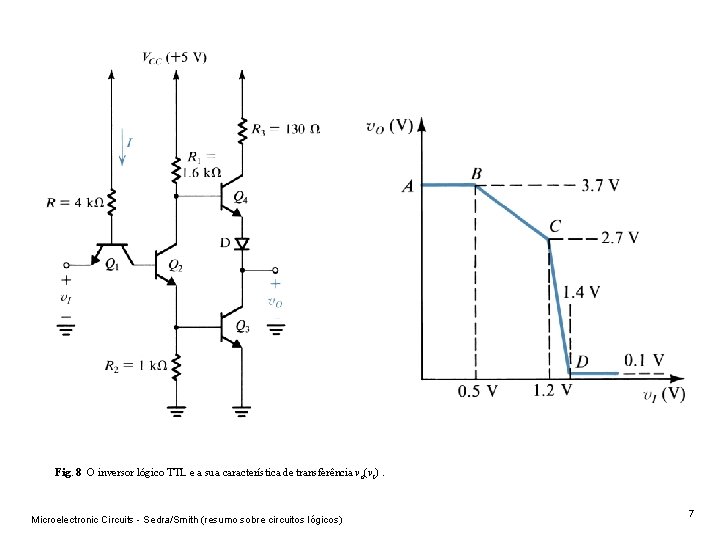

Fig. 8 O inversor lógico TTL e a sua característica de transferência v o(v i). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 7

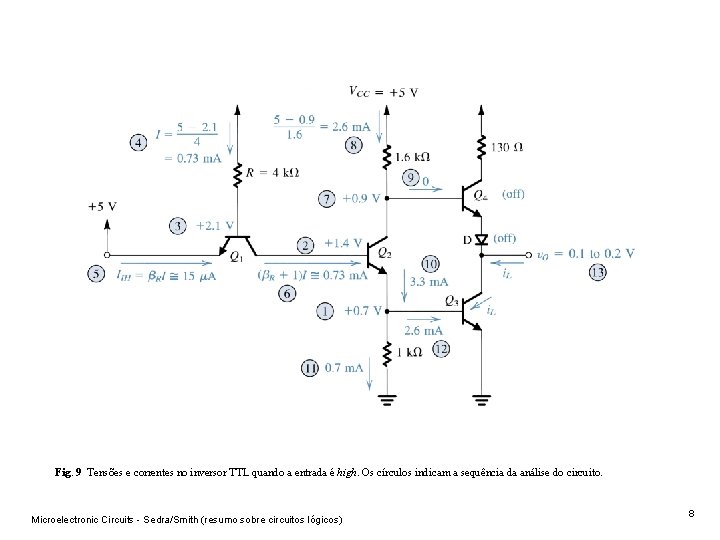

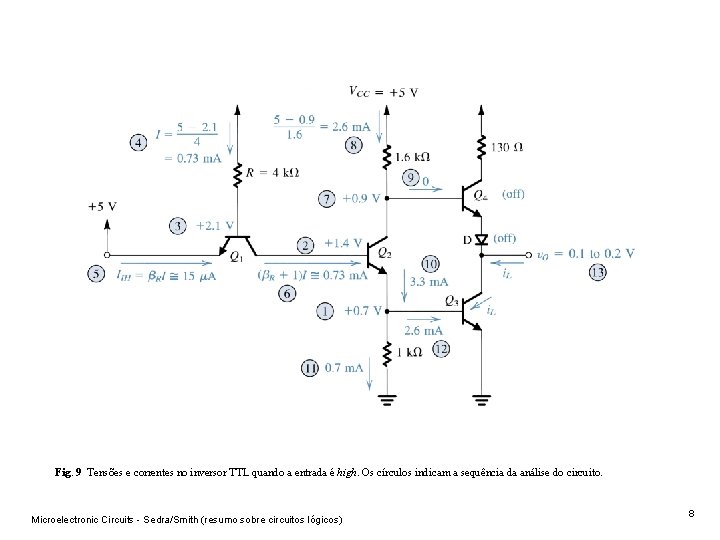

Fig. 9 Tensões e correntes no inversor TTL quando a entrada é high. Os círculos indicam a sequência da análise do circuito. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 8

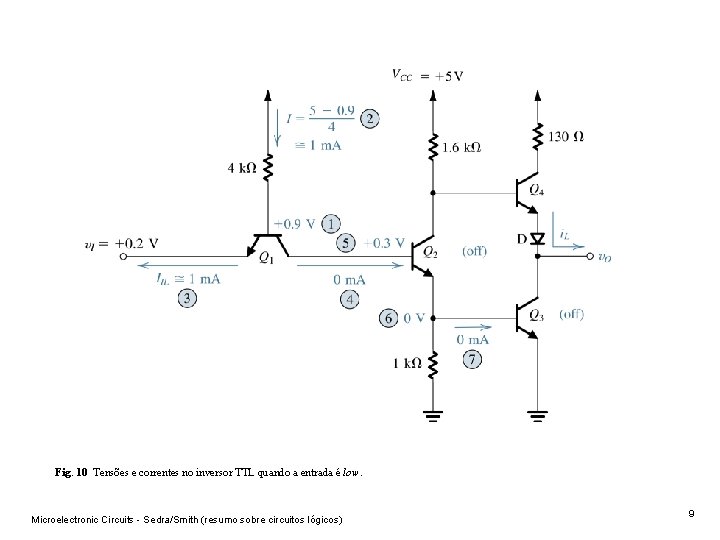

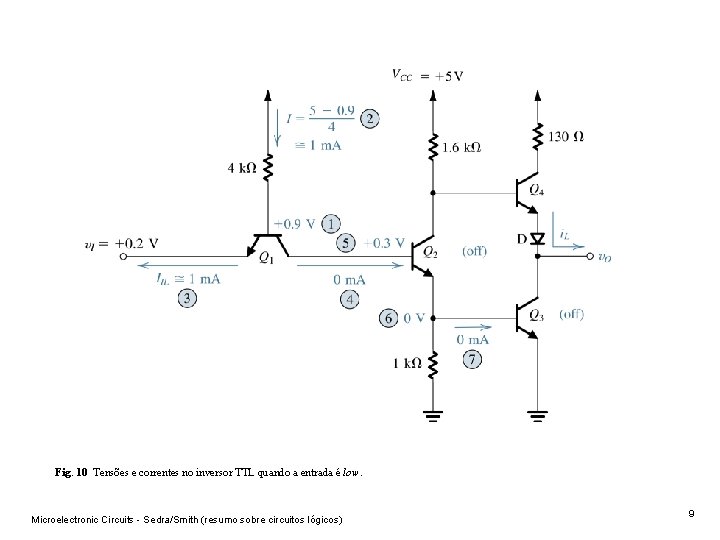

Fig. 10 Tensões e correntes no inversor TTL quando a entrada é low. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 9

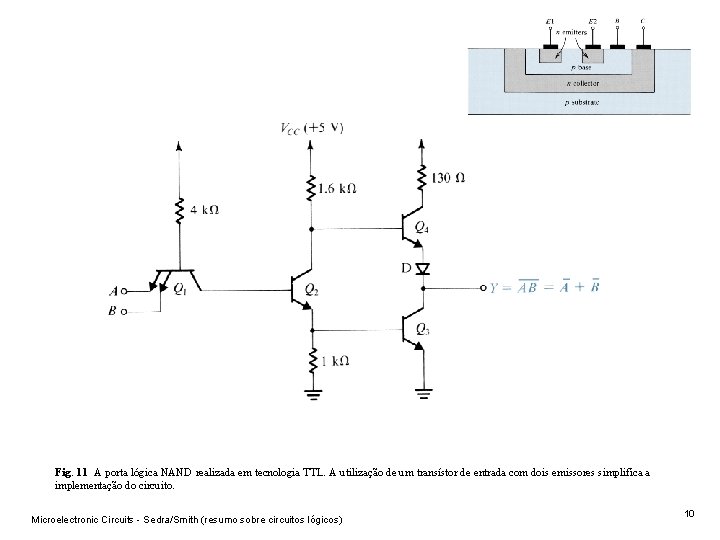

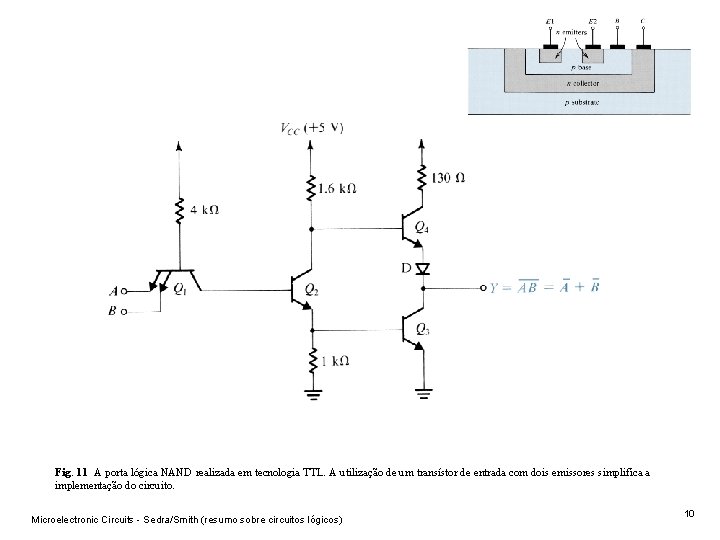

Fig. 11 A porta lógica NAND realizada em tecnologia TTL. A utilização de um transístor de entrada com dois emissores simplifica a implementação do circuito. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 10

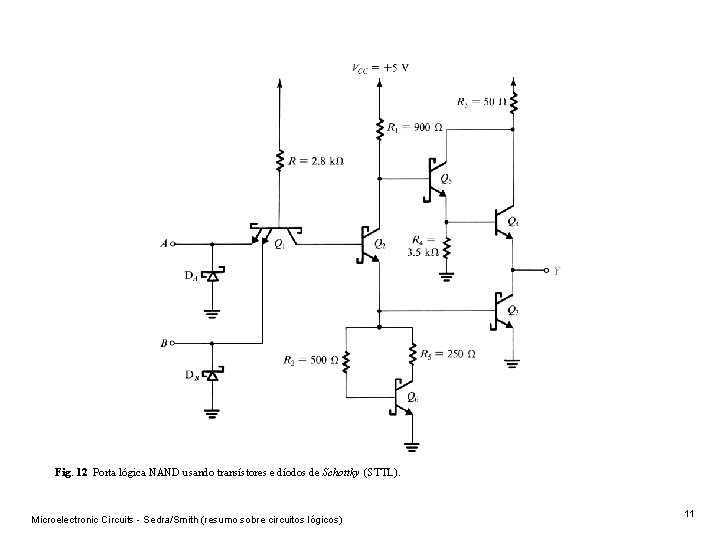

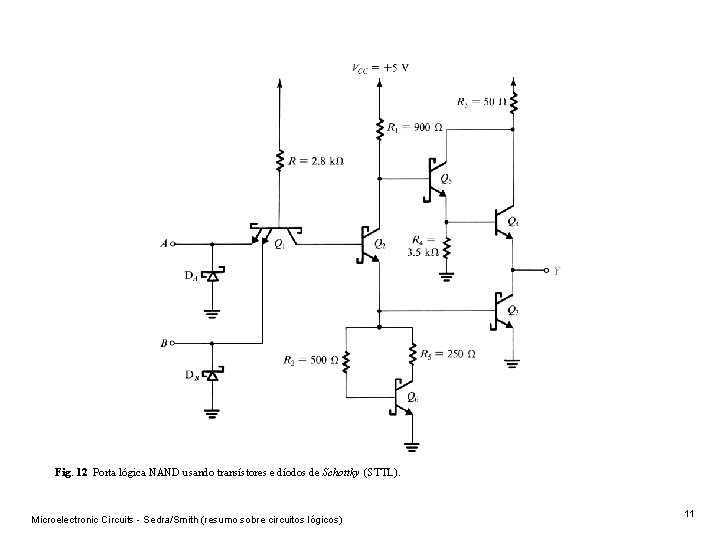

Fig. 12 Porta lógica NAND usando transístores e díodos de Schottky (STTL). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 11

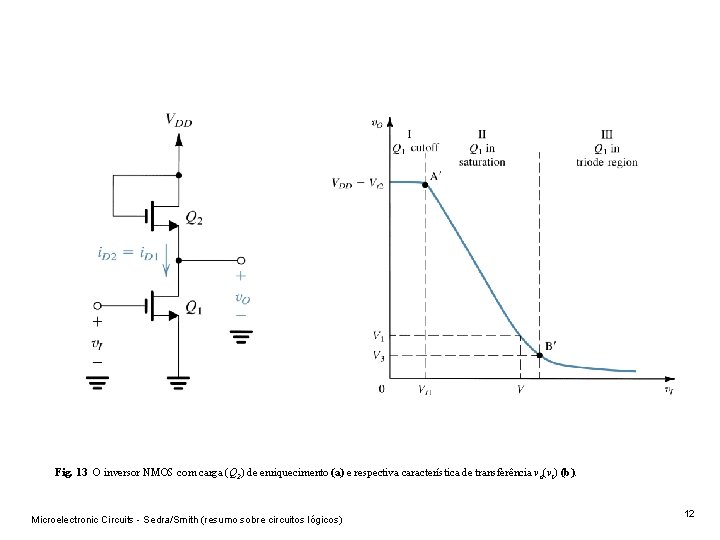

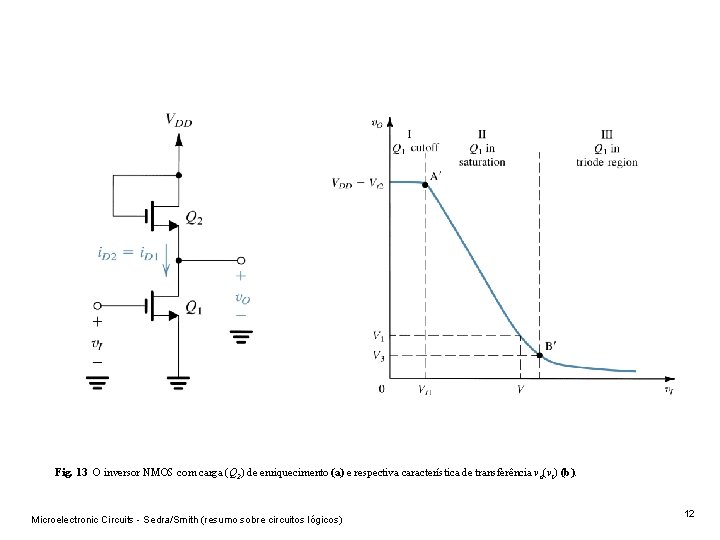

Fig. 13 O inversor NMOS com carga (Q 2) de enriquecimento (a) e respectiva característica de transferência v o(v i) (b). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 12

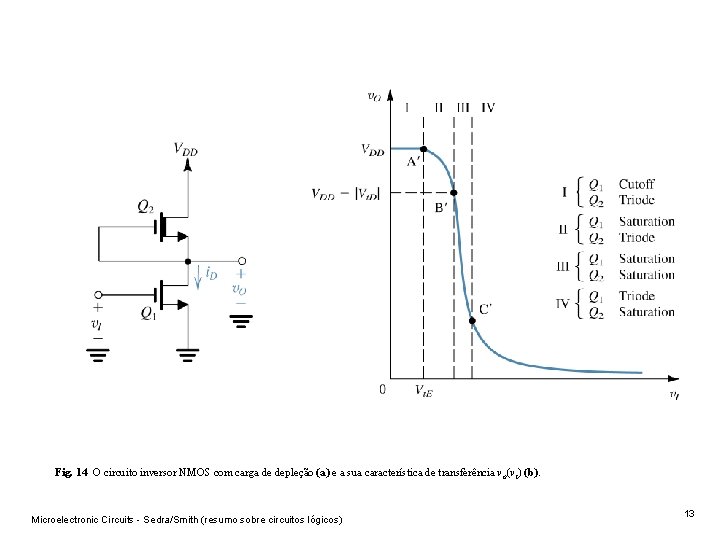

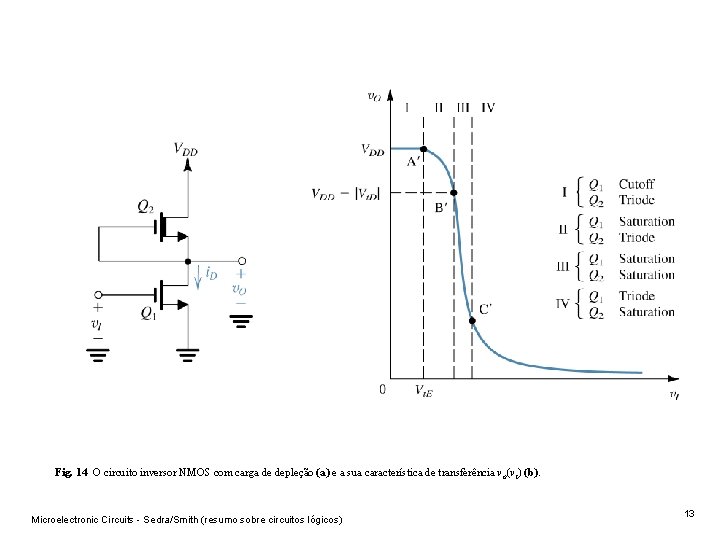

Fig. 14 O circuito inversor NMOS com carga de depleção (a) e a sua característica de transferência v o(v i) (b). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 13

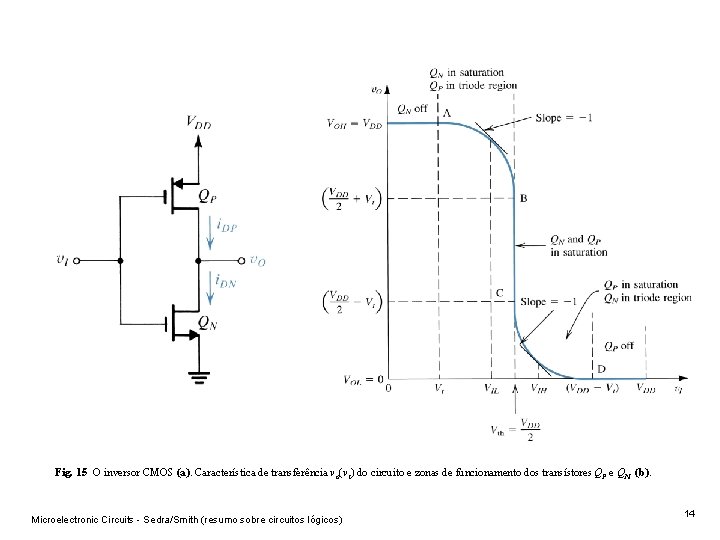

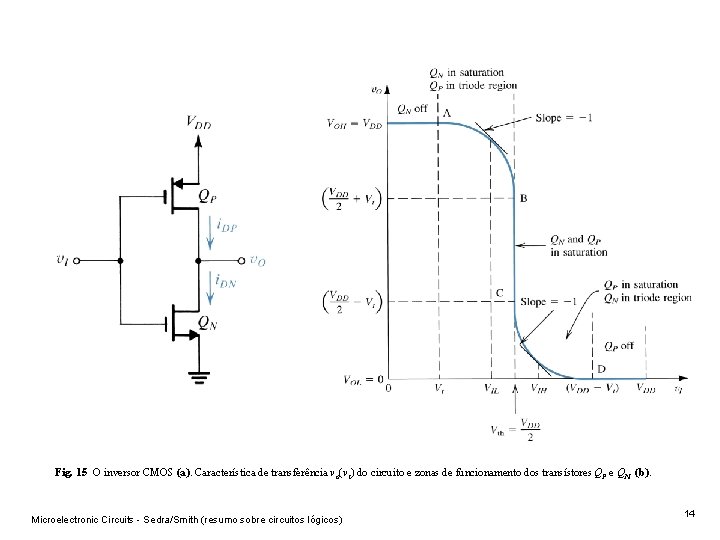

Fig. 15 O inversor CMOS (a). Característica de transferência v o(v i) do circuito e zonas de funcionamento dos transístores QP e QN (b). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 14

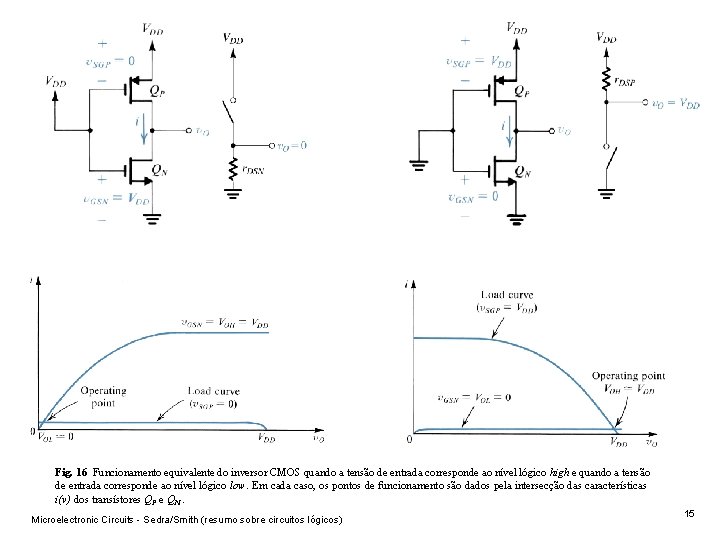

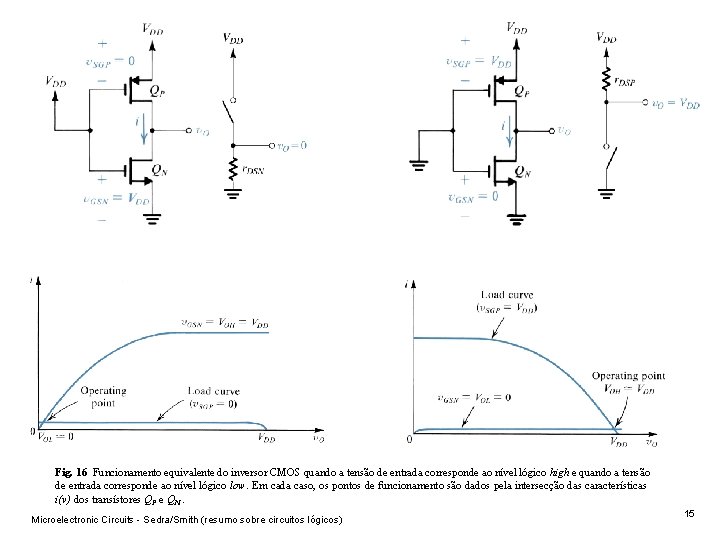

Fig. 16 Funcionamento equivalente do inversor CMOS quando a tensão de entrada corresponde ao nível lógico high e quando a tensão de entrada corresponde ao nível lógico low. Em cada caso, os pontos de funcionamento são dados pela intersecção das características i(v) dos transístores QP e QN. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 15

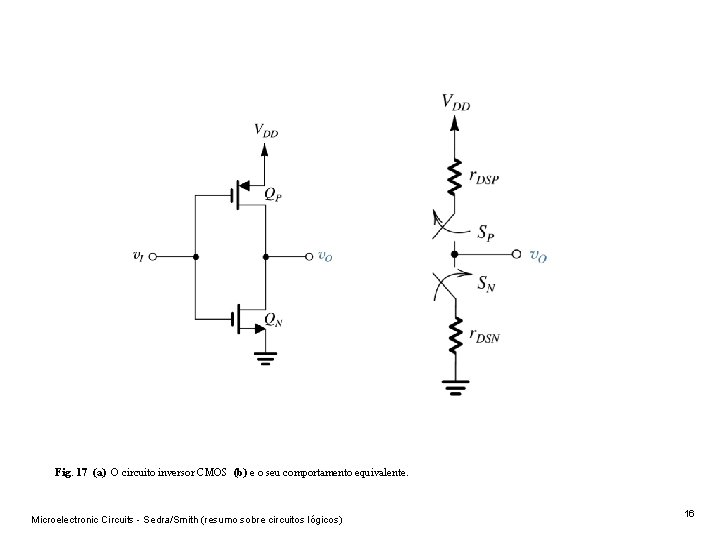

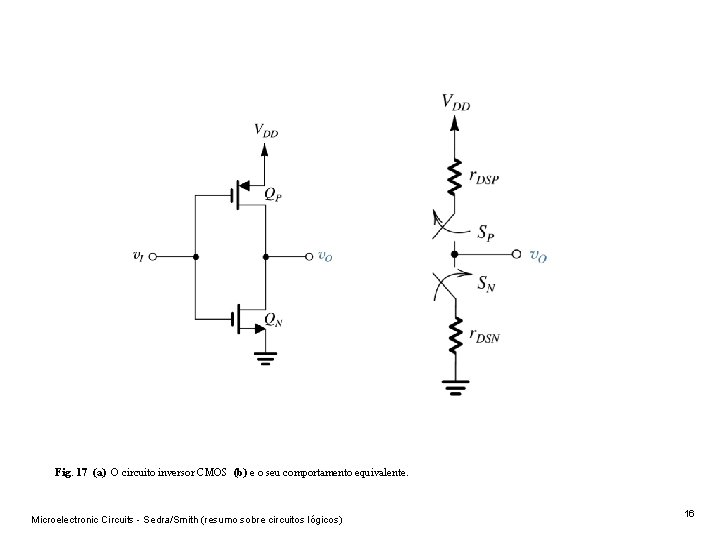

Fig. 17 (a) O circuito inversor CMOS (b) e o seu comportamento equivalente. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 16

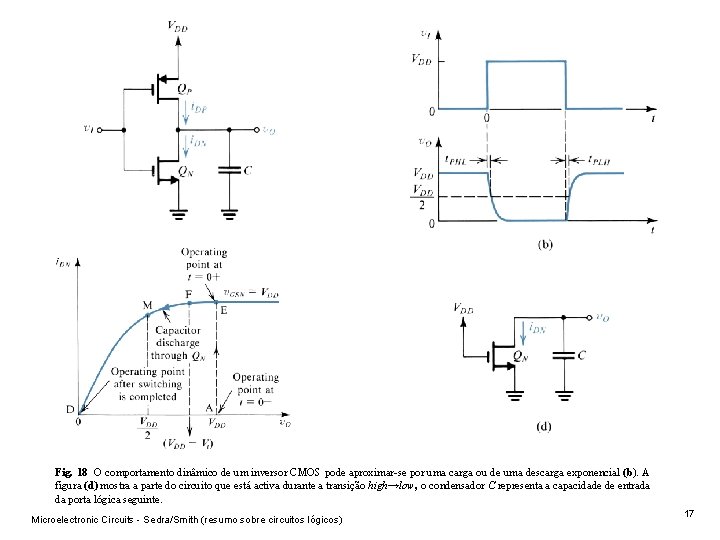

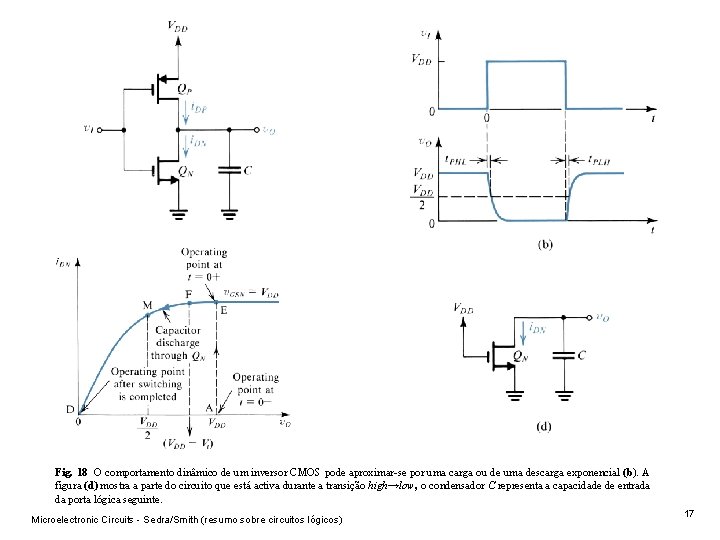

Fig. 18 O comportamento dinâmico de um inversor CMOS pode aproximar-se por uma carga ou de uma descarga exponencial (b). A figura (d) mostra a parte do circuito que está activa durante a transição high→low, o condensador C representa a capacidade de entrada da porta lógica seguinte. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 17

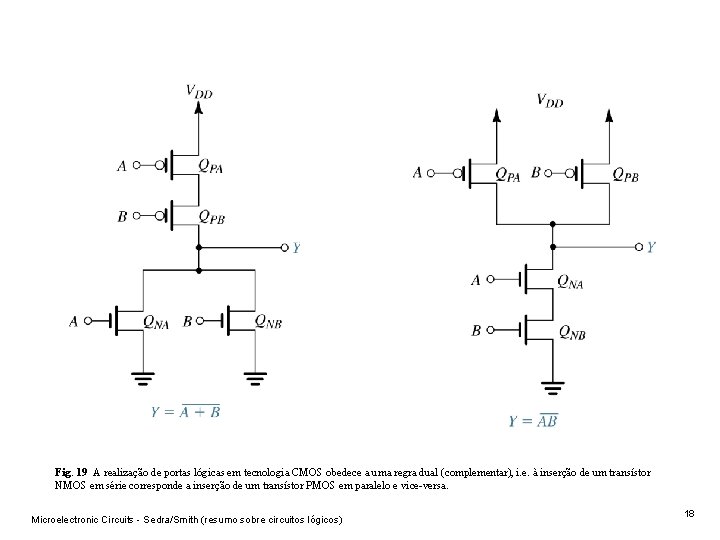

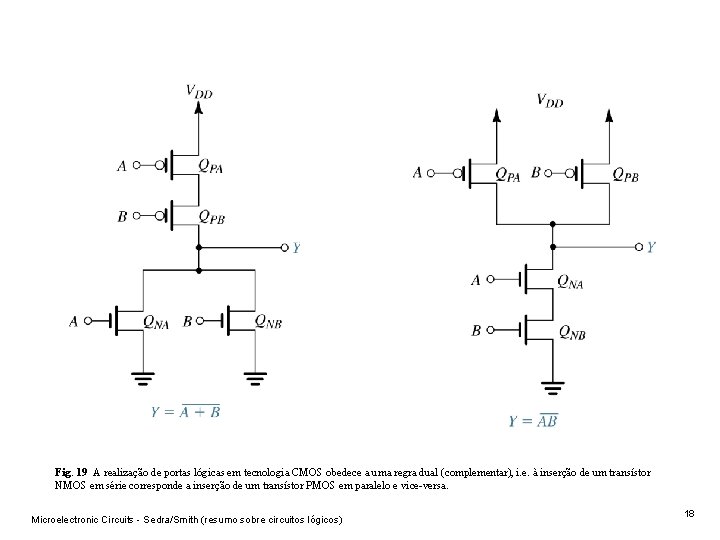

Fig. 19 A realização de portas lógicas em tecnologia CMOS obedece a uma regra dual (complementar), i. e. à inserção de um transístor NMOS em série corresponde a inserção de um transístor PMOS em paralelo e vice-versa. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 18

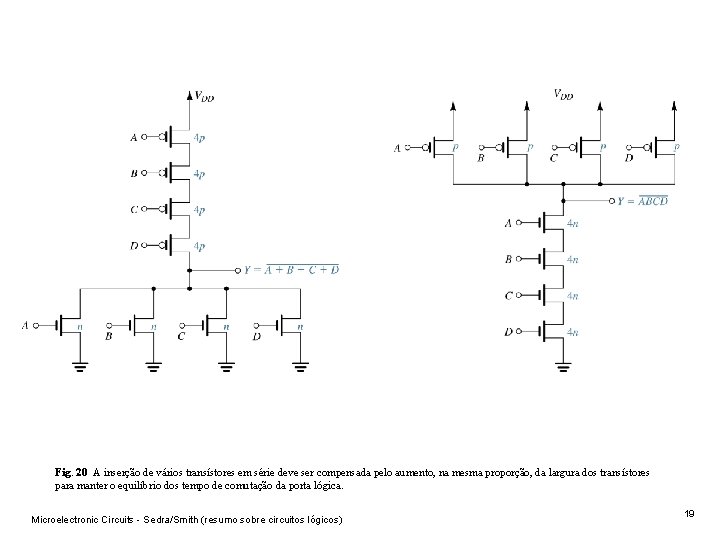

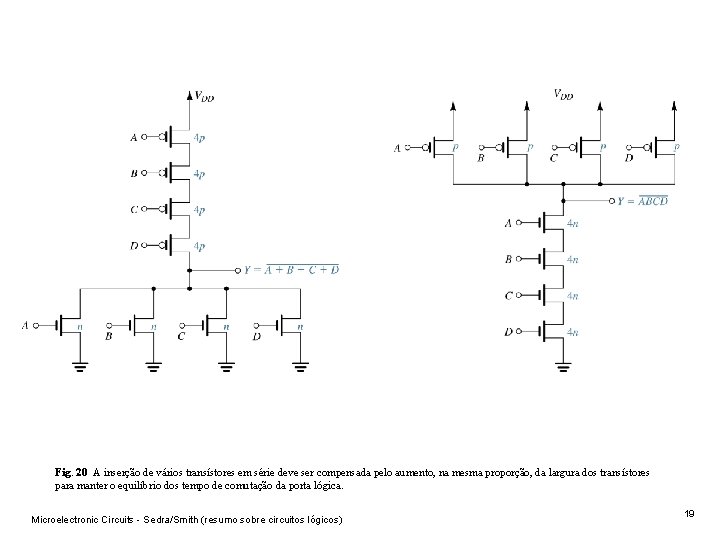

Fig. 20 A inserção de vários transístores em série deve ser compensada pelo aumento, na mesma proporção, da largura dos transístores para manter o equilíbrio dos tempo de comutação da porta lógica. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 19

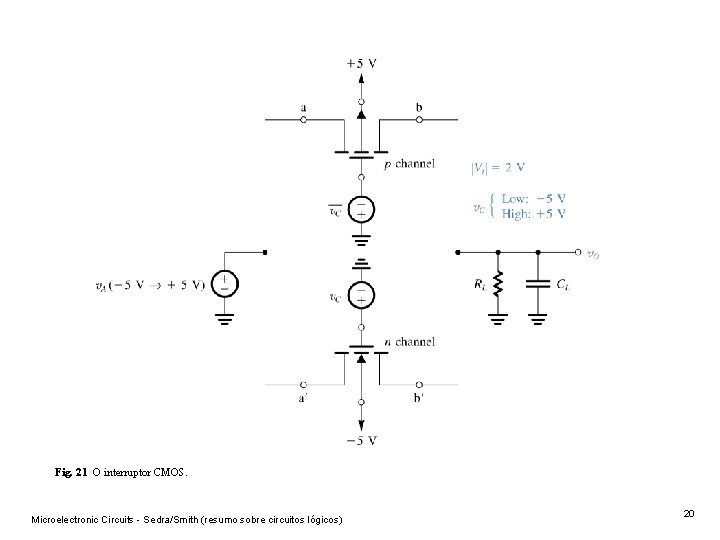

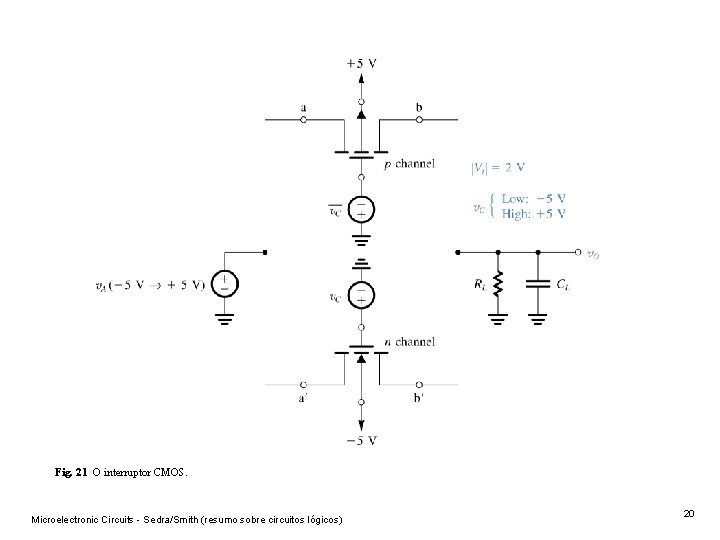

Fig. 21 O interruptor CMOS. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 20

Fig. 22 O circuito básico de memória latch e o seu princípio de funcionamento. O estado actual depende do estado anterior ! Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 21

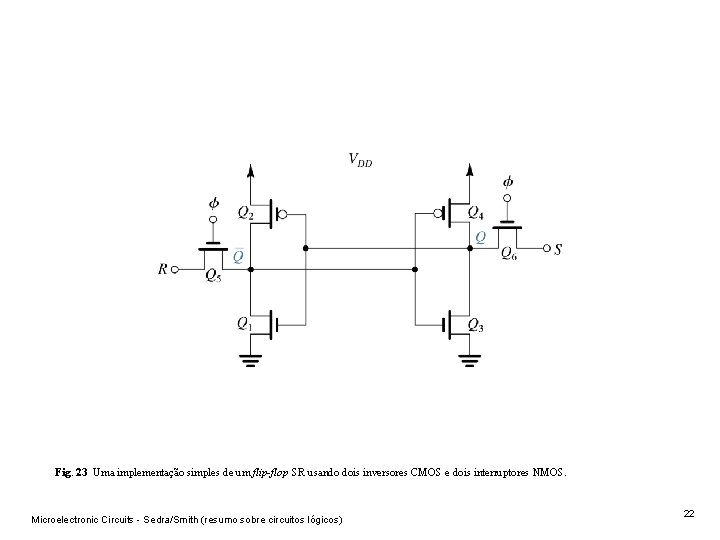

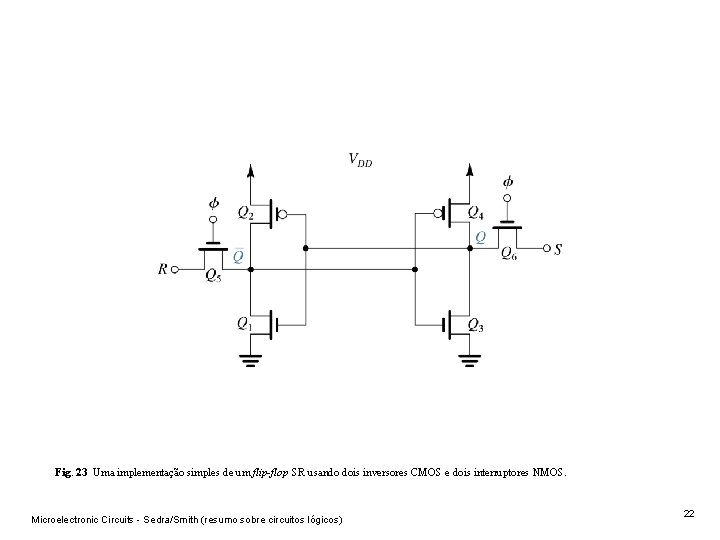

Fig. 23 Uma implementação simples de um flip-flop SR usando dois inversores CMOS e dois interruptores NMOS. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 22

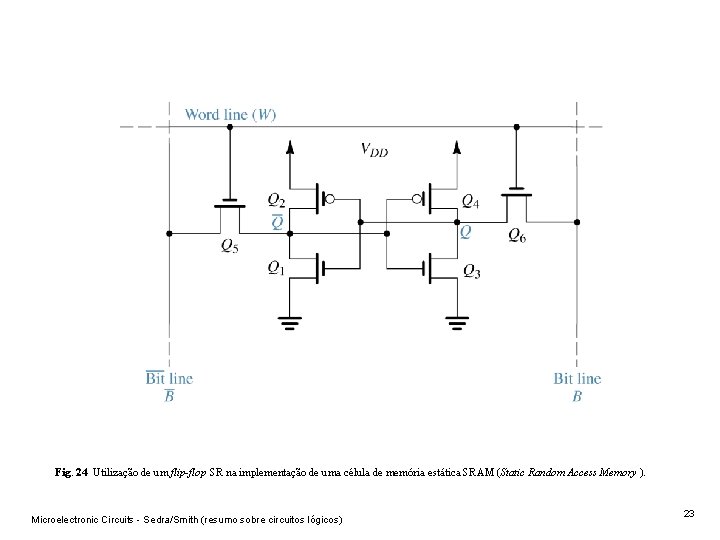

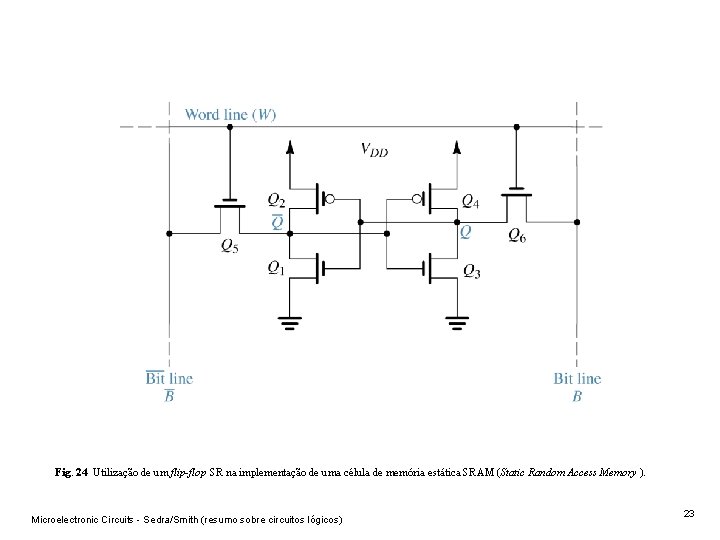

Fig. 24 Utilização de um flip-flop SR na implementação de uma célula de memória estática SRAM (Static Random Access Memory ). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 23

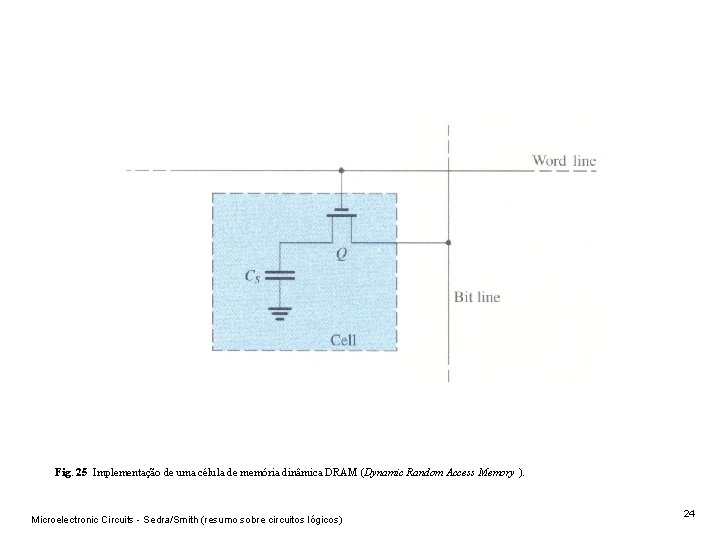

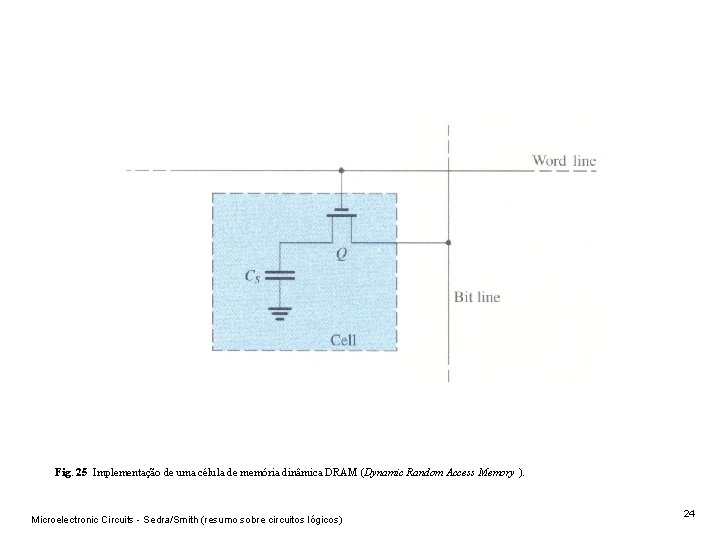

Fig. 25 Implementação de uma célula de memória dinâmica DRAM (Dynamic Random Access Memory ). Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 24

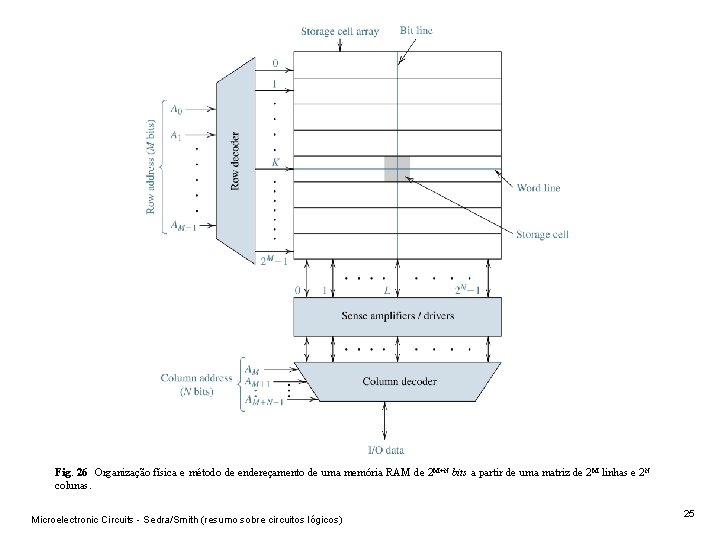

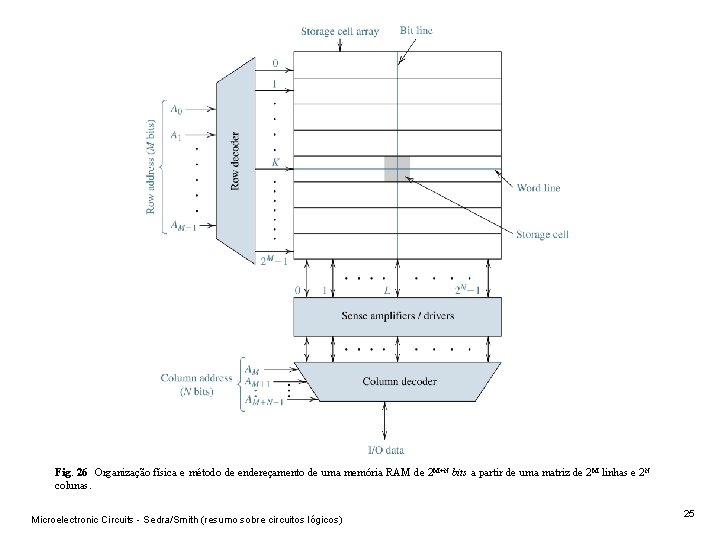

Fig. 26 Organização física e método de endereçamento de uma memória RAM de 2 M+N bits a partir de uma matriz de 2 M linhas e 2 N colunas. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 25

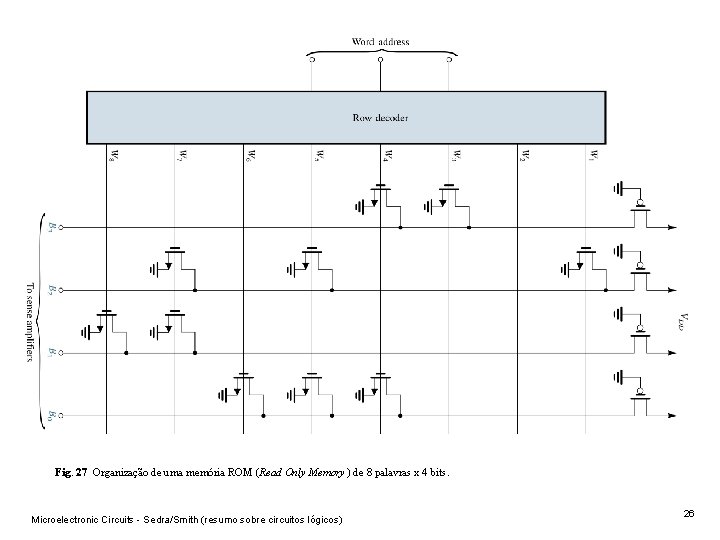

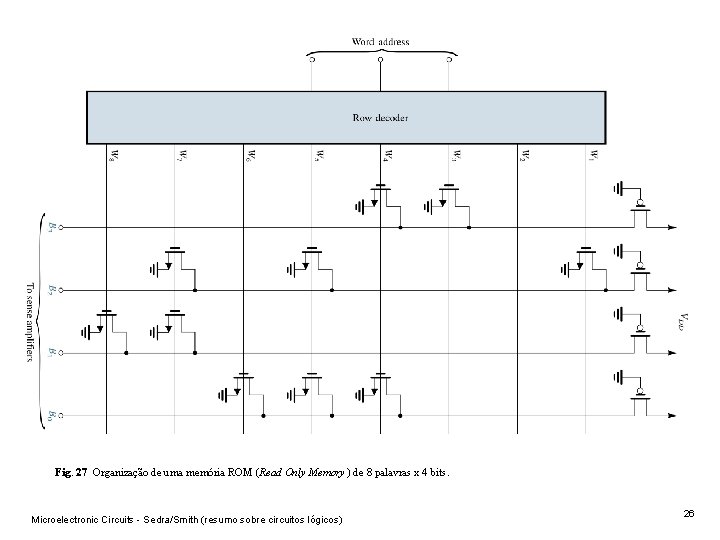

Fig. 27 Organização de uma memória ROM (Read Only Memory ) de 8 palavras x 4 bits. Microelectronic Circuits - Sedra/Smith (resumo sobre circuitos lógicos) 26