Fibonacci Counter Goal Design a Five bit Fibonacci

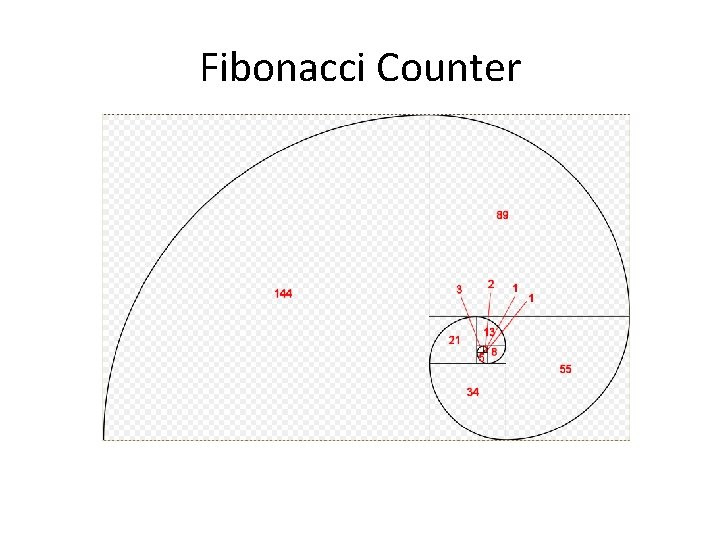

Fibonacci Counter

Goal • Design a Five bit Fibonacci counter • 25= 32 bit size • Count sequence 0, 1, 1, 2, 3, 5, 8, 13, 21…

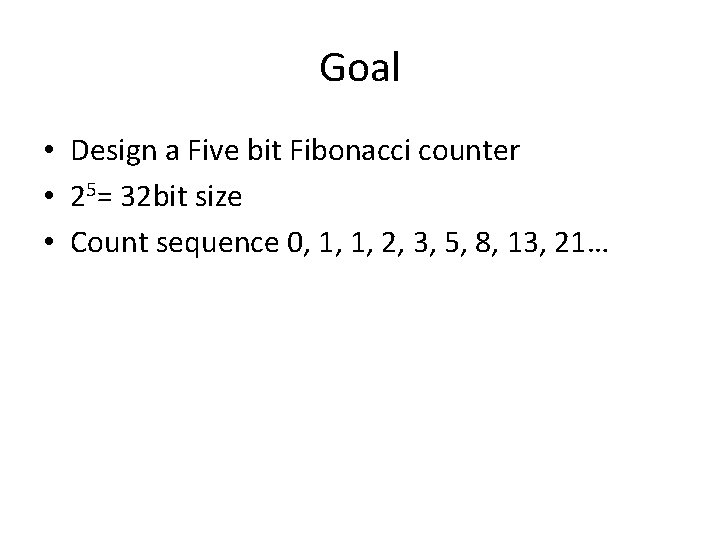

Truth Table Q 1 Q 2 Q 3 Q 4 Q 5 Q 1+ Q 2+ Q 3+ Q 4+ Q 5+ 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 0 1 1 0 1 0 1 0 0 0

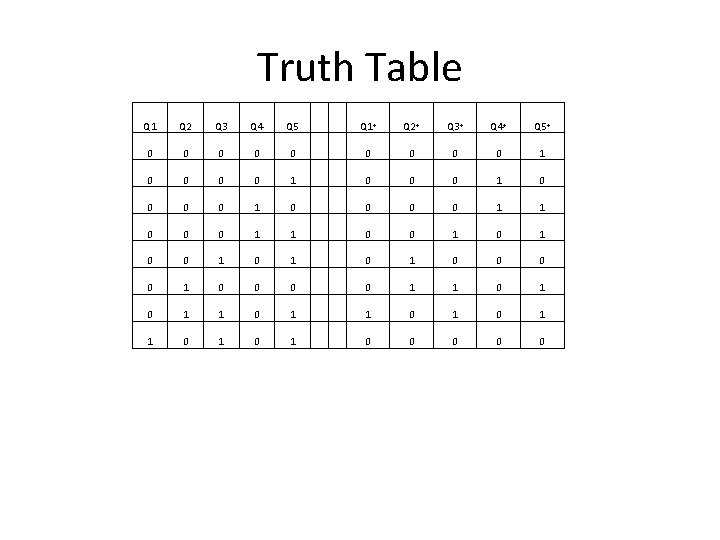

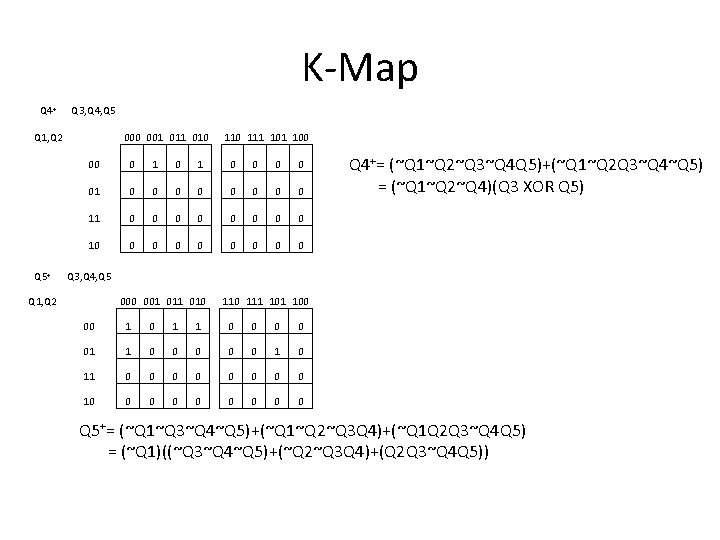

K-Map Q 1+ Q 3, Q 4, Q 5 Q 1, Q 2+ 000 001 010 111 100 00 0 01 0 0 0 1 11 0 0 0 10 0 0 0 Q 1, Q 2 000 001 010 111 100 00 0 0 0 1 0 0 01 1 0 0 0 0 0 11 0 0 0 0 0 10 0 0 0 0 Q 2+=(~Q 1~Q 2 Q 3~Q 4 Q 5)+(~Q 1 Q 2~Q 3~Q 4~Q 5) =(~Q 1~Q 4)((~Q 2 Q 3 Q 5)+(Q 2~Q 3~Q 5)) =(~Q 1~Q 4)(Q 2 XOR Q 3 XOR Q 5) Q 1+= ~Q 1 Q 2 Q 3~Q 4 Q 5 Q 3+ Q 3, Q 4, Q 5 Q 1, Q 2 000 001 010 111 100 00 0 0 1 0 0 01 1 0 0 0 11 0 0 0 0 10 0 0 0 0 Q 3+= (~Q 1~Q 3 Q 4 Q 5)+(~Q 1 Q 2~Q 3~Q 4~Q 5) = (~Q 1~Q 3)((Q 4 Q 5)+(~Q 3~Q 4~Q 5))

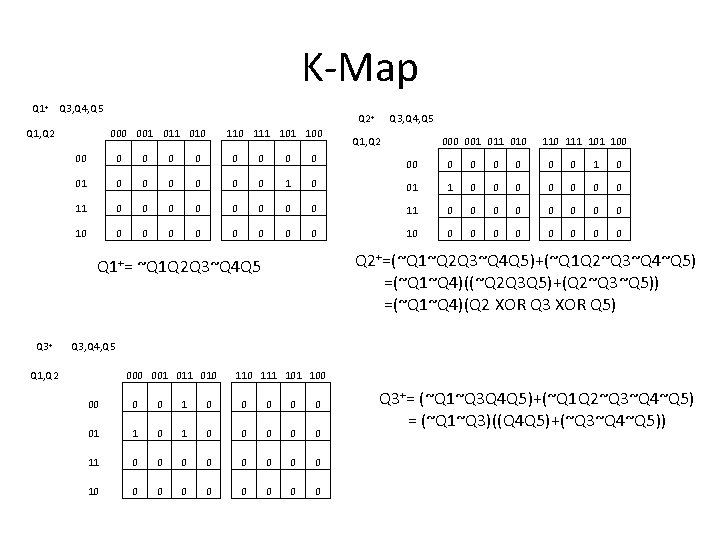

K-Map Q 4+ Q 3, Q 4, Q 5 Q 1, Q 2 Q 5+ 000 001 010 111 100 00 0 1 0 0 01 0 0 0 0 10 0 0 0 0 Q 4+= (~Q 1~Q 2~Q 3~Q 4 Q 5)+(~Q 1~Q 2 Q 3~Q 4~Q 5) = (~Q 1~Q 2~Q 4)(Q 3 XOR Q 5) Q 3, Q 4, Q 5 Q 1, Q 2 000 001 010 111 100 00 1 1 0 0 01 1 0 0 0 11 0 0 0 0 10 0 0 0 0 Q 5+= (~Q 1~Q 3~Q 4~Q 5)+(~Q 1~Q 2~Q 3 Q 4)+(~Q 1 Q 2 Q 3~Q 4 Q 5) = (~Q 1)((~Q 3~Q 4~Q 5)+(~Q 2~Q 3 Q 4)+(Q 2 Q 3~Q 4 Q 5))

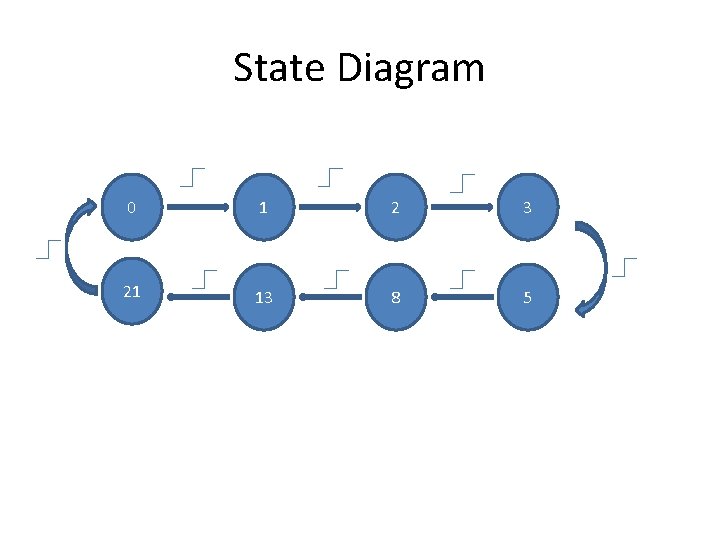

State Diagram 0 1 2 3 21 13 8 5

![Verilog HDL Source code module Fcount(Clk. M, fn); input Clk. M; output[4: 0] fn; Verilog HDL Source code module Fcount(Clk. M, fn); input Clk. M; output[4: 0] fn;](http://slidetodoc.com/presentation_image_h/c7c04040e2f6d0f8c9fdda9d8bc53e29/image-7.jpg)

Verilog HDL Source code module Fcount(Clk. M, fn); input Clk. M; output[4: 0] fn; reg [4: 0] fn; always@(posedge Clk. M) begin case(fn) 0: fn<=1; 1: fn<=2; 2: fn<=3; 3: fn<=5; 5: fn<=8; 8: fn<=13; 13: fn<=21; 21: fn<=0; default: fn<=0; endcase endmodule

![Verilog HDL Testbench code module fcounttest; reg CLKM; wire[4: 0] FN; Fcount TL(CLKM, FN); Verilog HDL Testbench code module fcounttest; reg CLKM; wire[4: 0] FN; Fcount TL(CLKM, FN);](http://slidetodoc.com/presentation_image_h/c7c04040e2f6d0f8c9fdda9d8bc53e29/image-8.jpg)

Verilog HDL Testbench code module fcounttest; reg CLKM; wire[4: 0] FN; Fcount TL(CLKM, FN); initial begin #200 $stop; end initial begin CLKM=0; #1 forever #10 CLKM=~CLKM; endendmodule

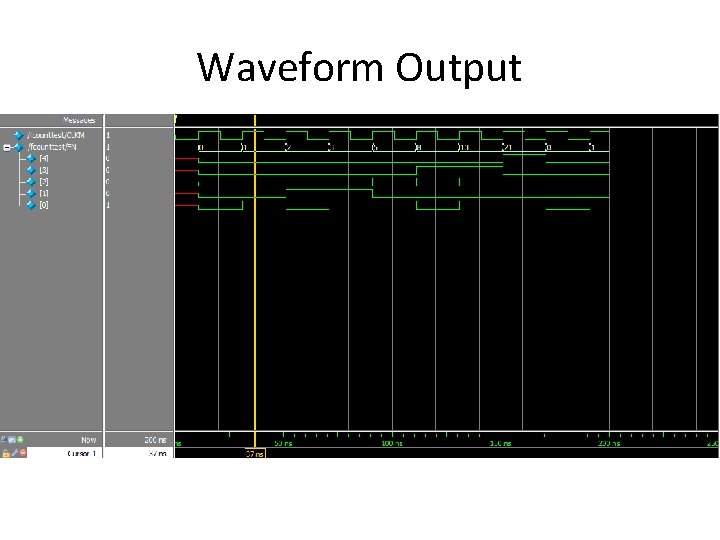

Waveform Output

ISPLever Tutorial To run ISPLever do the following: 1. Start > type in “isplever” 2. Open isplever

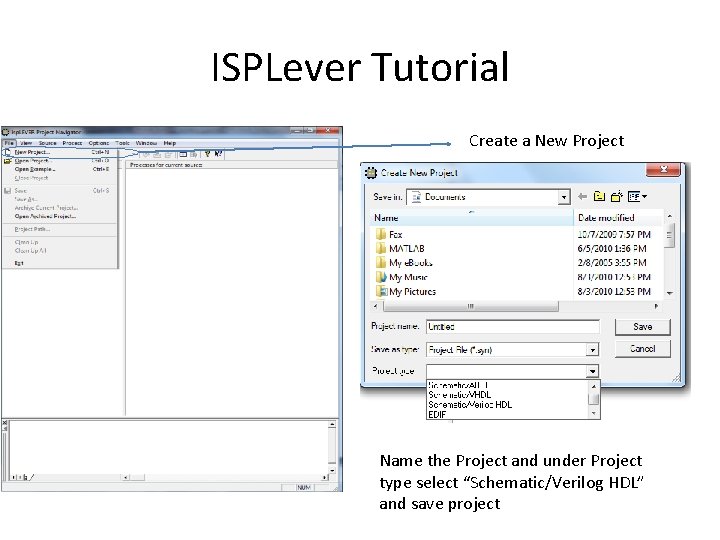

ISPLever Tutorial Create a New Project Name the Project and under Project type select “Schematic/Verilog HDL” and save project

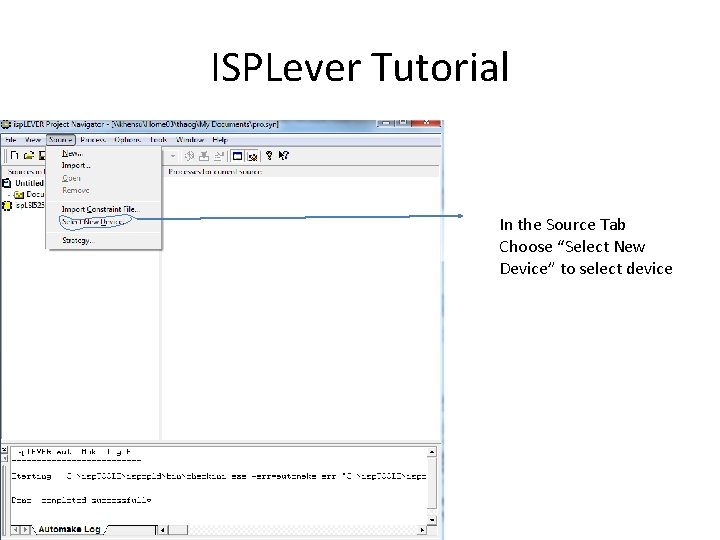

ISPLever Tutorial In the Source Tab Choose “Select New Device” to select device

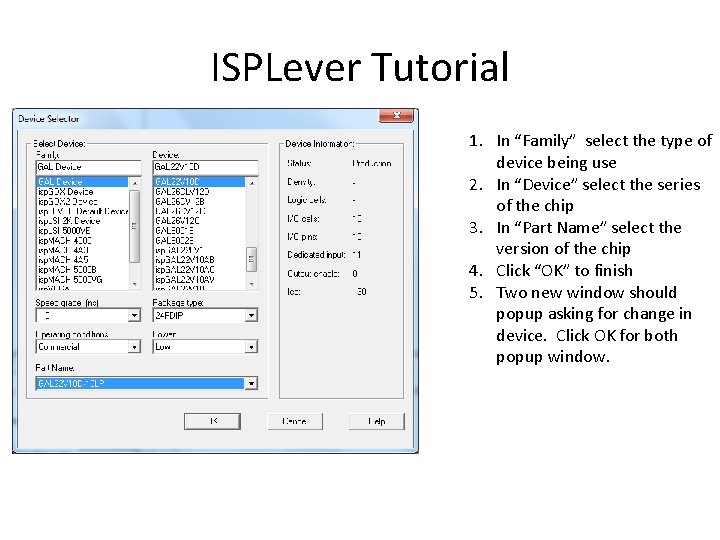

ISPLever Tutorial 1. In “Family” select the type of device being use 2. In “Device” select the series of the chip 3. In “Part Name” select the version of the chip 4. Click “OK” to finish 5. Two new window should popup asking for change in device. Click OK for both popup window.

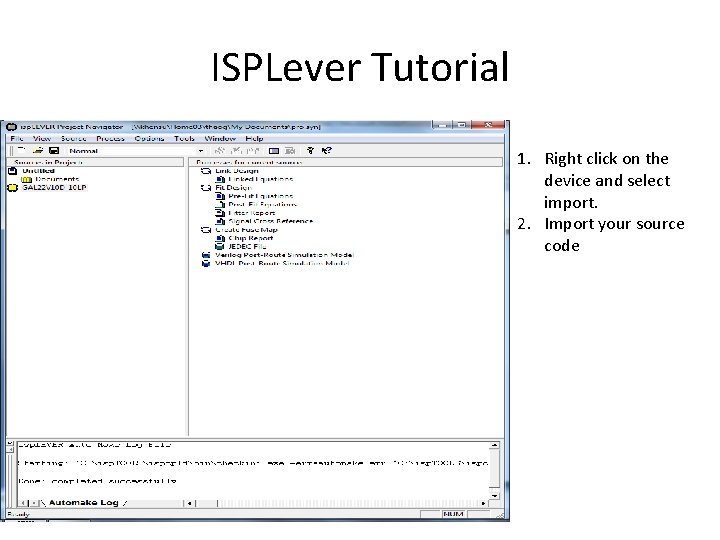

ISPLever Tutorial 1. Right click on the device and select import. 2. Import your source code

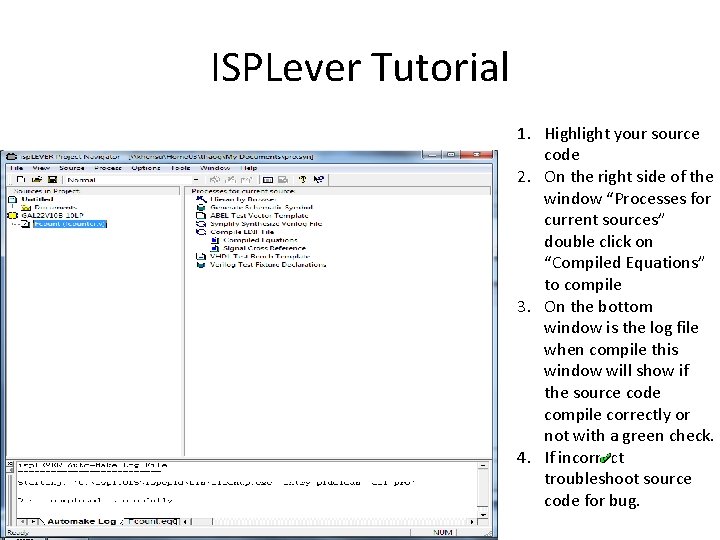

ISPLever Tutorial 1. Highlight your source code 2. On the right side of the window “Processes for current sources” double click on “Compiled Equations” to compile 3. On the bottom window is the log file when compile this window will show if the source code compile correctly or not with a green check. 4. If incorrect troubleshoot source code for bug.

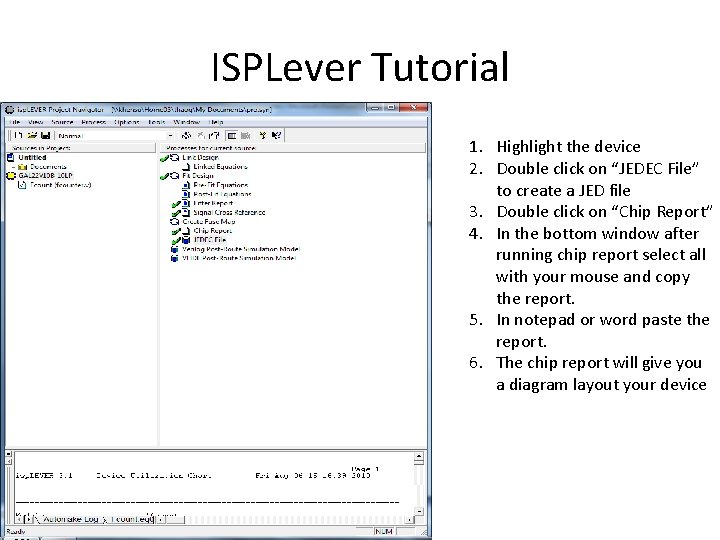

ISPLever Tutorial 1. Highlight the device 2. Double click on “JEDEC File” to create a JED file 3. Double click on “Chip Report” 4. In the bottom window after running chip report select all with your mouse and copy the report. 5. In notepad or word paste the report. 6. The chip report will give you a diagram layout your device

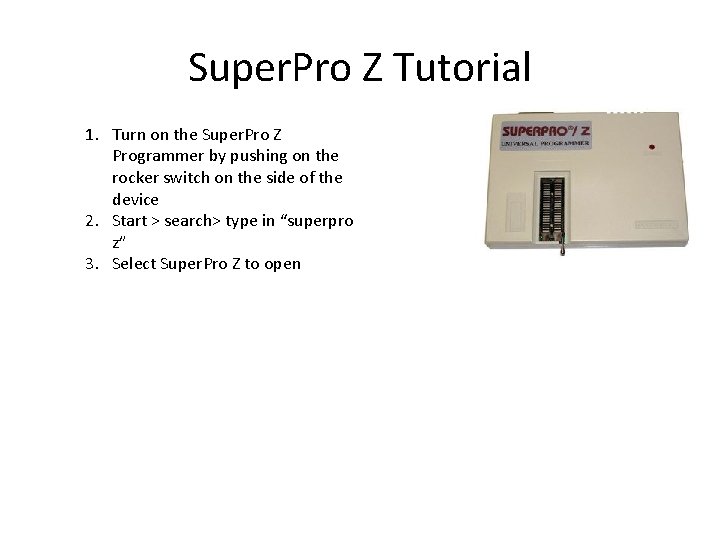

Super. Pro Z Tutorial 1. Turn on the Super. Pro Z Programmer by pushing on the rocker switch on the side of the device 2. Start > search> type in “superpro z” 3. Select Super. Pro Z to open

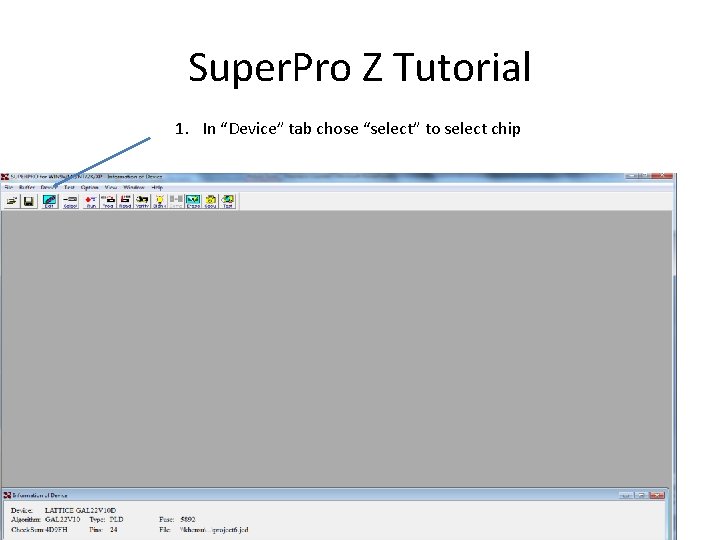

Super. Pro Z Tutorial 1. In “Device” tab chose “select” to select chip

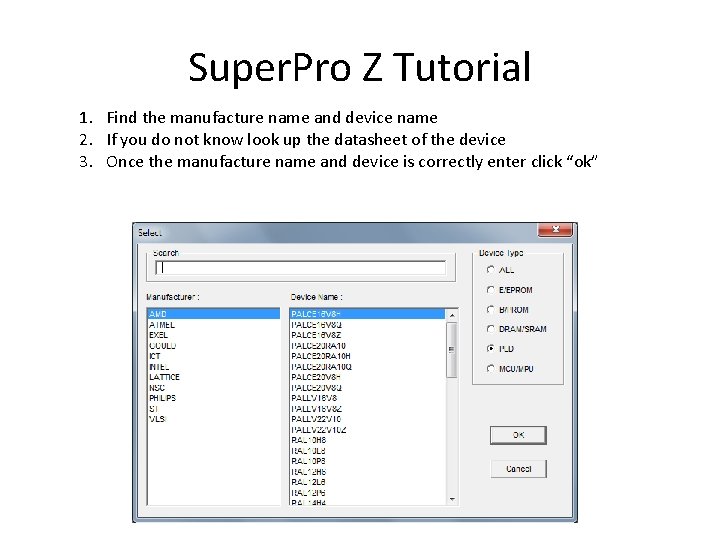

Super. Pro Z Tutorial 1. Find the manufacture name and device name 2. If you do not know look up the datasheet of the device 3. Once the manufacture name and device is correctly enter click “ok”

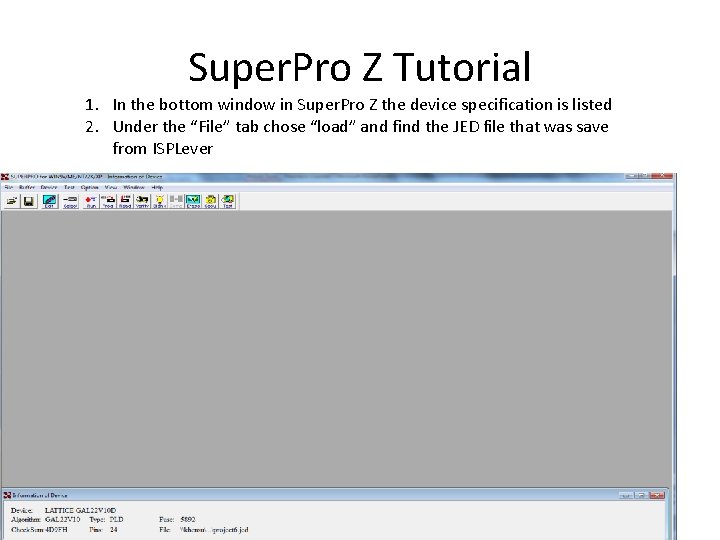

Super. Pro Z Tutorial 1. In the bottom window in Super. Pro Z the device specification is listed 2. Under the “File” tab chose “load” and find the JED file that was save from ISPLever

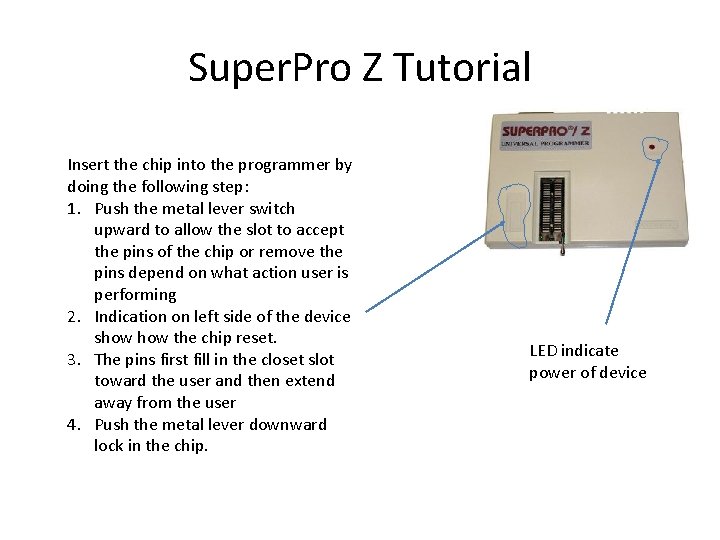

Super. Pro Z Tutorial Insert the chip into the programmer by doing the following step: 1. Push the metal lever switch upward to allow the slot to accept the pins of the chip or remove the pins depend on what action user is performing 2. Indication on left side of the device show the chip reset. 3. The pins first fill in the closet slot toward the user and then extend away from the user 4. Push the metal lever downward lock in the chip. LED indicate power of device

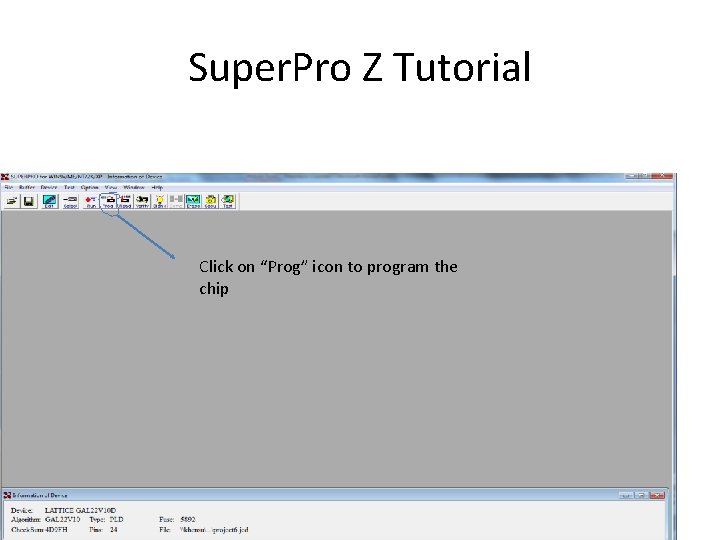

Super. Pro Z Tutorial Click on “Prog” icon to program the chip

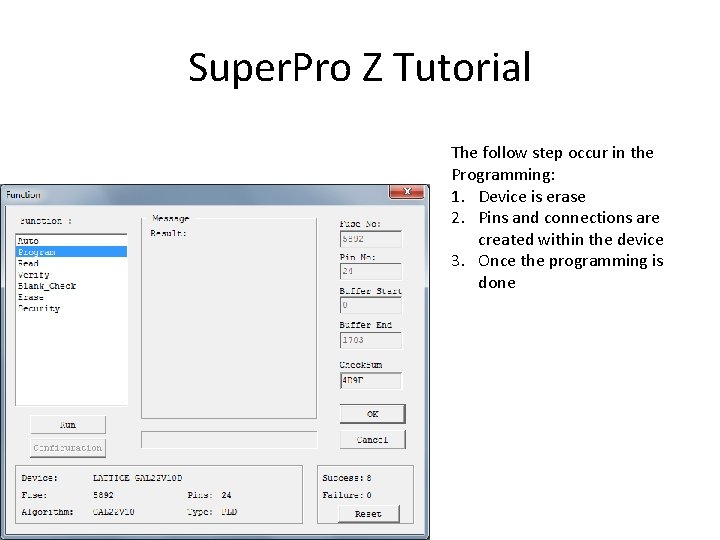

Super. Pro Z Tutorial The follow step occur in the Programming: 1. Device is erase 2. Pins and connections are created within the device 3. Once the programming is done

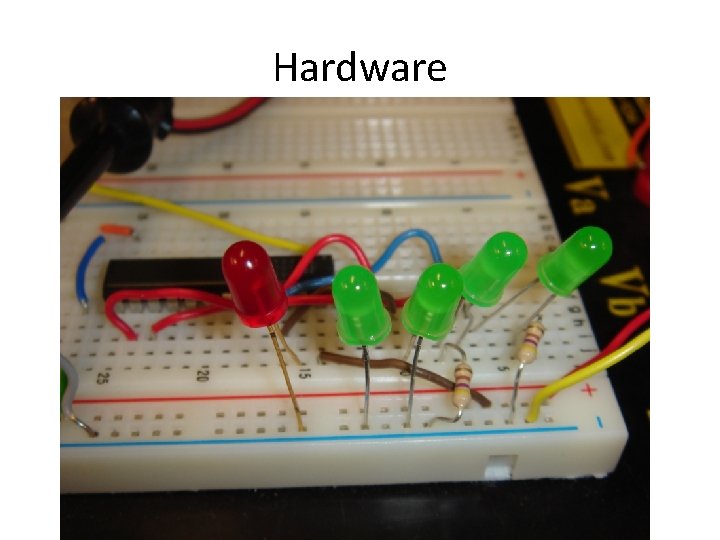

Hardware • • • One GAL 22 V 10 D-10 LP Five LED Power supply 5 VDC Function Generator 1 Hz square wave Resistor

Hardware

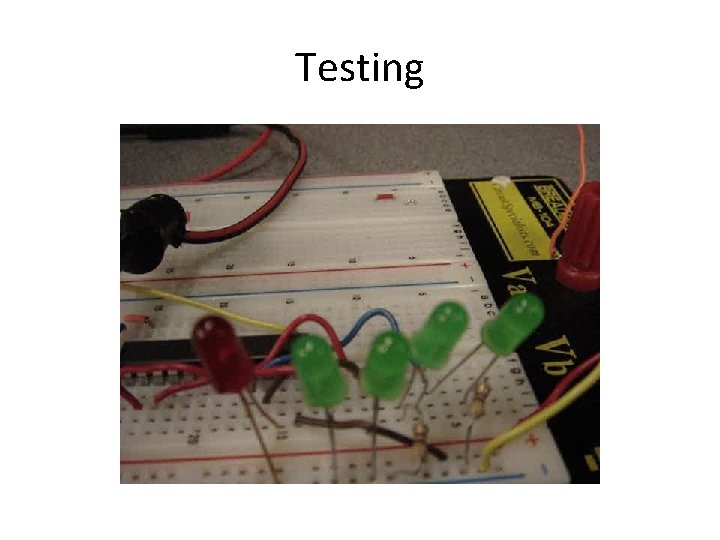

Testing

Question? ? ?

Reference • http: //en. wikipedia. org/wiki/Fibonacci_numb er • http: //www. latticesemi. com/lit/docs/tutorials /tutor 8. pdf? jsessionid=f 030 ed 9 e 982587 c 56 bc c 4864136 a 29666571

Fibonacci Team Member • Torn Saelee • George Thao

- Slides: 29