FEE Electronics progress Mezzanine manufacture progress FEE 64

- Slides: 8

FEE Electronics progress • Mezzanine manufacture progress • FEE 64 testing and VHDL progress • Test mezzanine. • Trial mechanical assembly 10 th November 2009

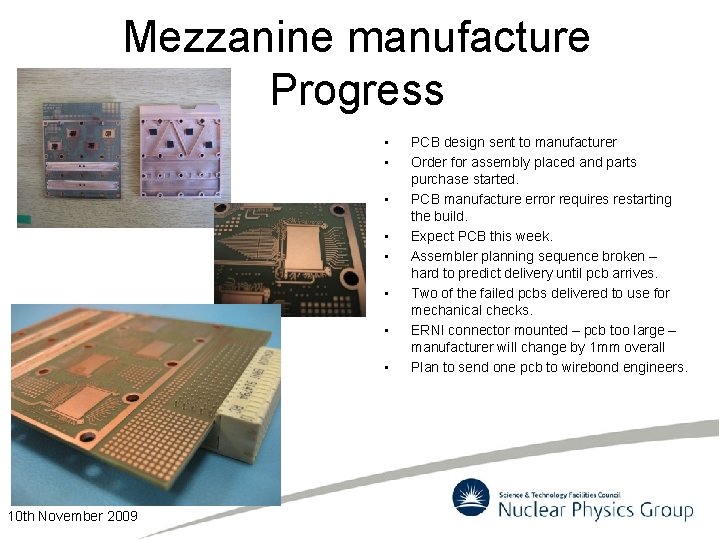

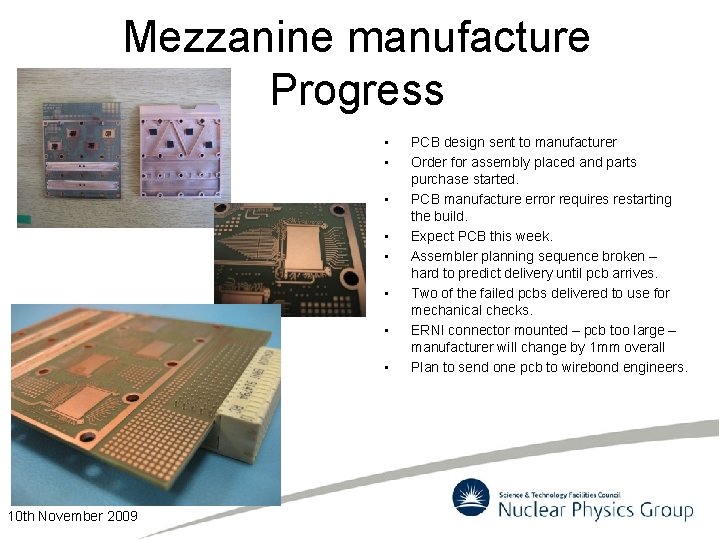

Mezzanine manufacture Progress • • 10 th November 2009 PCB design sent to manufacturer Order for assembly placed and parts purchase started. PCB manufacture error requires restarting the build. Expect PCB this week. Assembler planning sequence broken – hard to predict delivery until pcb arrives. Two of the failed pcbs delivered to use for mechanical checks. ERNI connector mounted – pcb too large – manufacturer will change by 1 mm overall Plan to send one pcb to wirebond engineers.

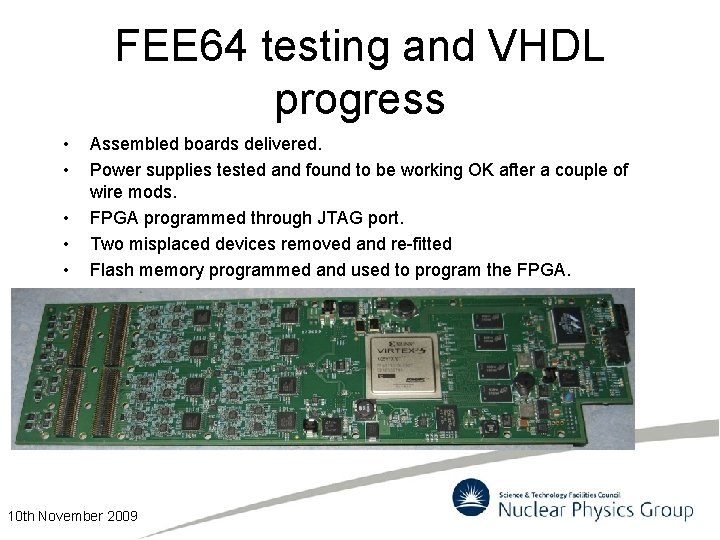

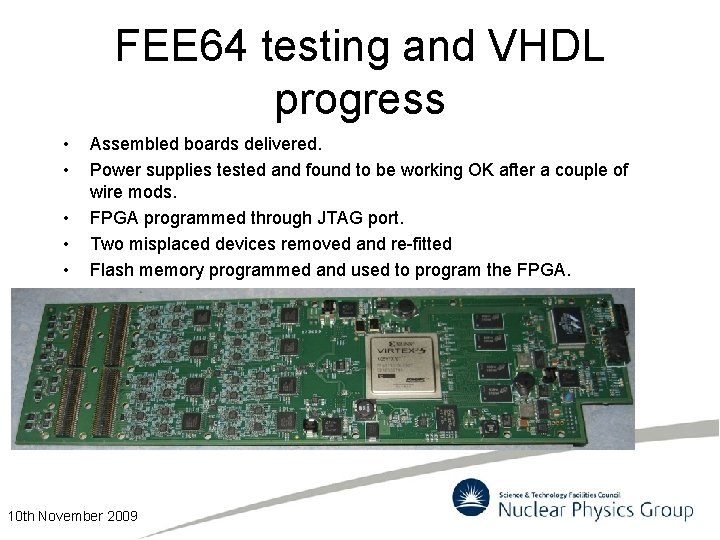

FEE 64 testing and VHDL progress • • • Assembled boards delivered. Power supplies tested and found to be working OK after a couple of wire mods. FPGA programmed through JTAG port. Two misplaced devices removed and re-fitted Flash memory programmed and used to program the FPGA. 10 th November 2009

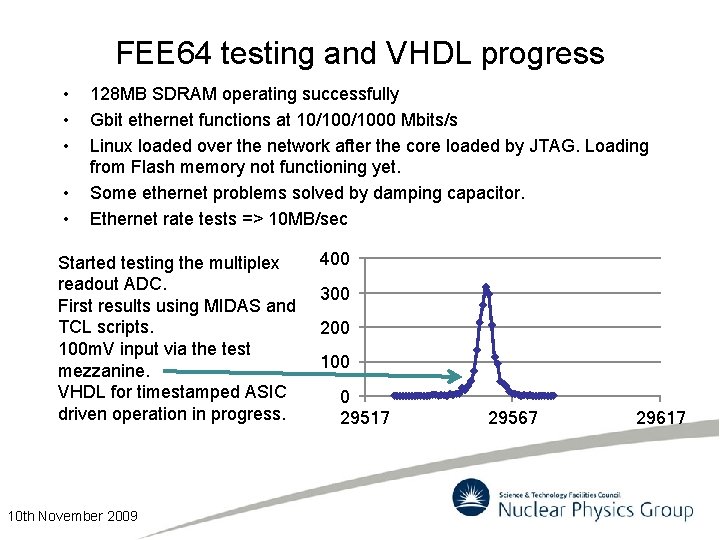

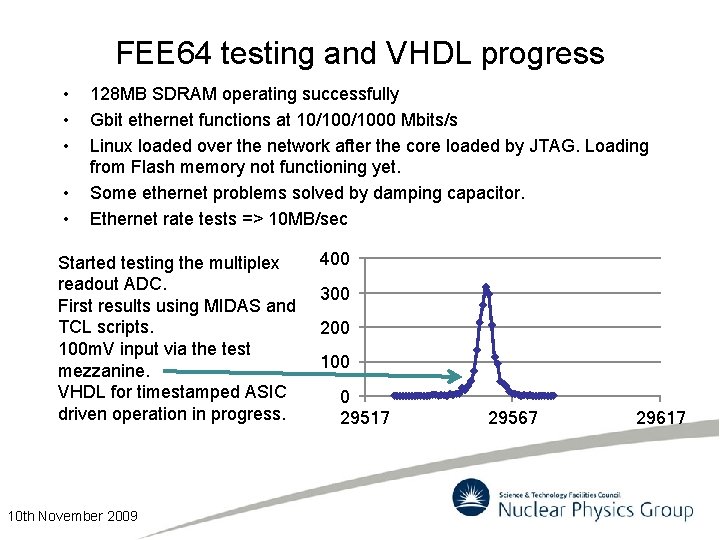

FEE 64 testing and VHDL progress • • • 128 MB SDRAM operating successfully Gbit ethernet functions at 10/1000 Mbits/s Linux loaded over the network after the core loaded by JTAG. Loading from Flash memory not functioning yet. Some ethernet problems solved by damping capacitor. Ethernet rate tests => 10 MB/sec Started testing the multiplex readout ADC. First results using MIDAS and TCL scripts. 100 m. V input via the test mezzanine. VHDL for timestamped ASIC driven operation in progress. 10 th November 2009 400 300 200 100 0 29517 29567 29617

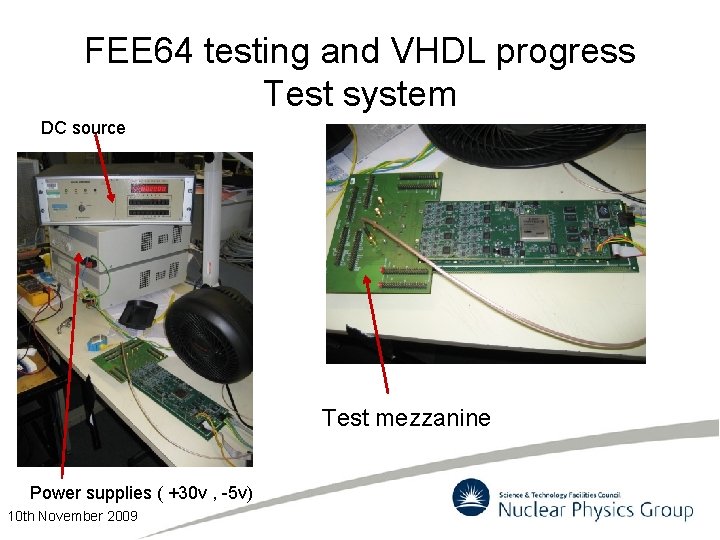

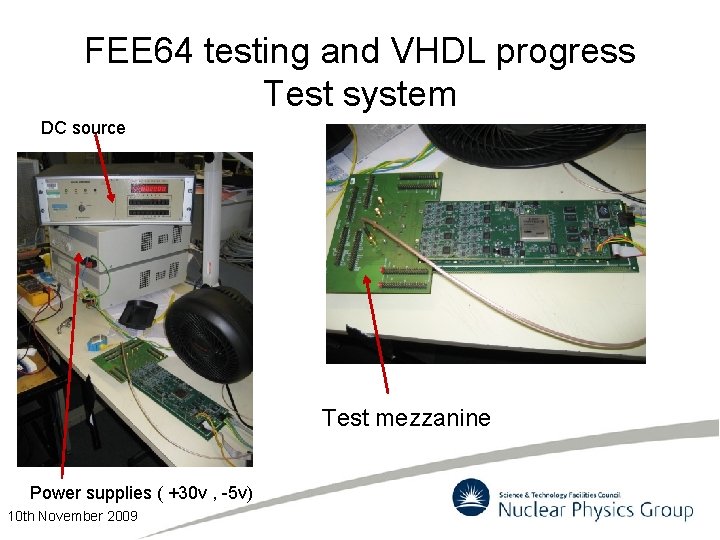

FEE 64 testing and VHDL progress Test system DC source Test mezzanine Power supplies ( +30 v , -5 v) 10 th November 2009

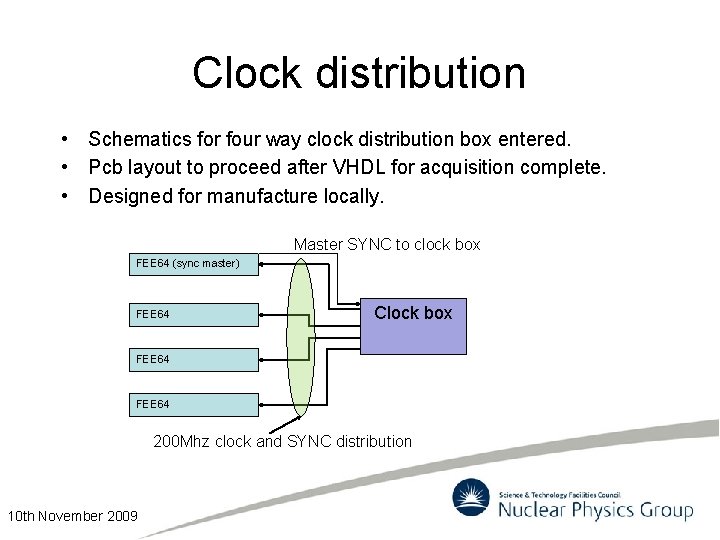

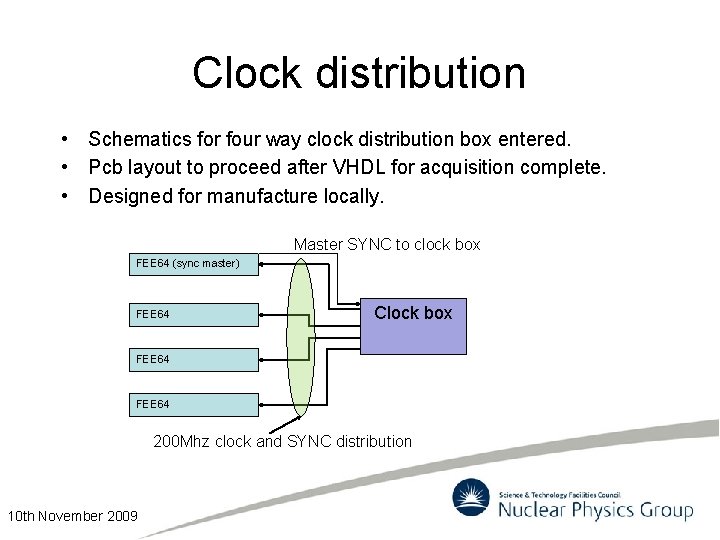

Clock distribution • Schematics for four way clock distribution box entered. • Pcb layout to proceed after VHDL for acquisition complete. • Designed for manufacture locally. Master SYNC to clock box FEE 64 (sync master) FEE 64 Clock box FEE 64 200 Mhz clock and SYNC distribution 10 th November 2009

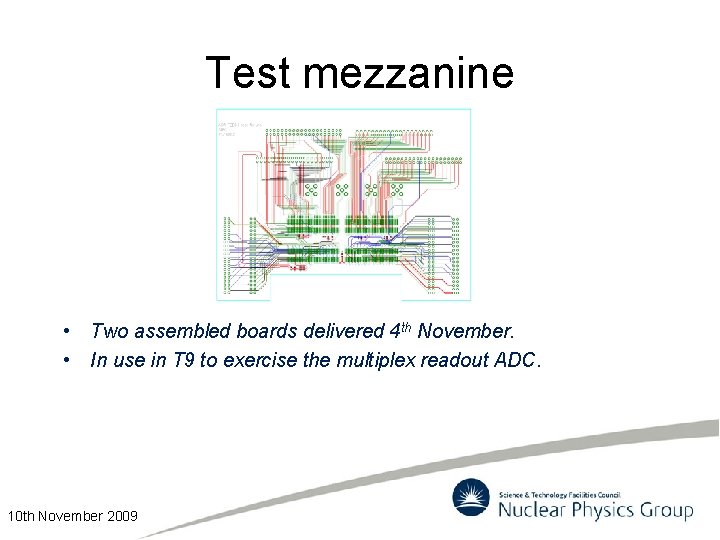

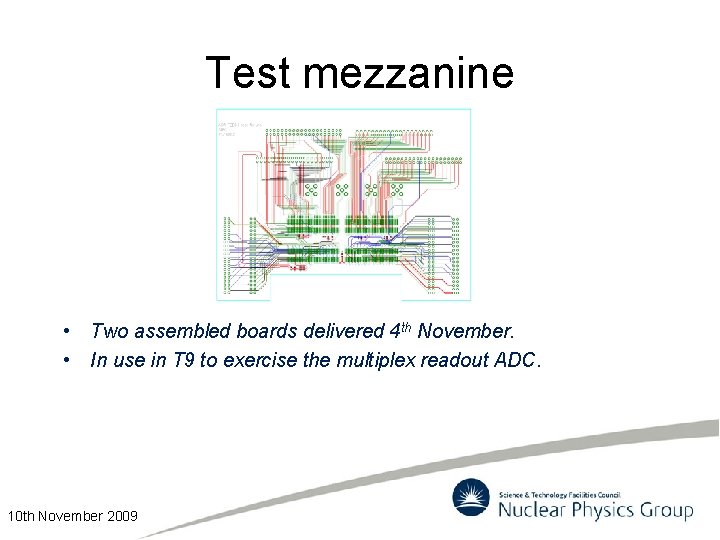

Test mezzanine • Two assembled boards delivered 4 th November. • In use in T 9 to exercise the multiplex readout ADC. 10 th November 2009

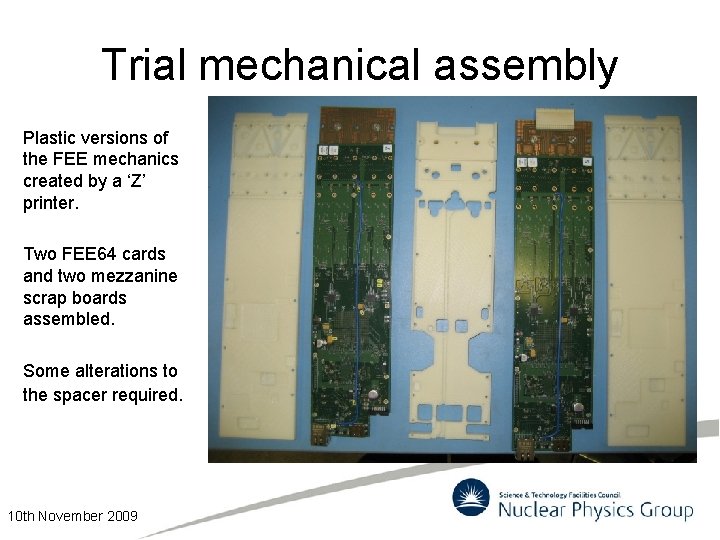

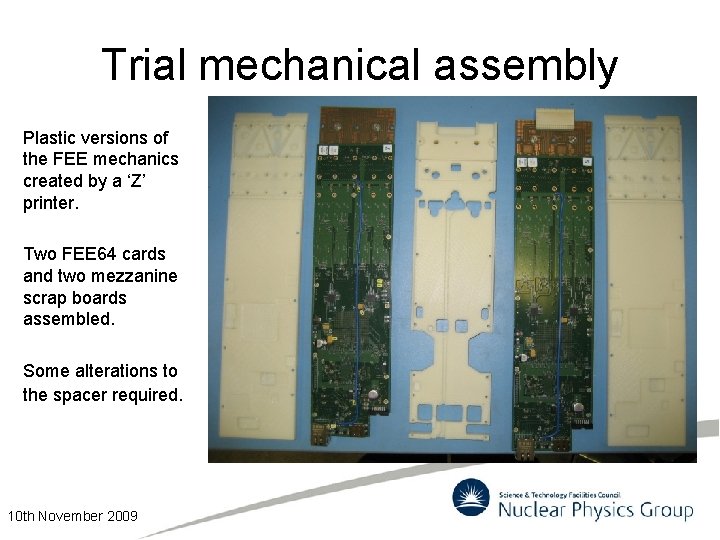

Trial mechanical assembly Plastic versions of the FEE mechanics created by a ‘Z’ printer. Two FEE 64 cards and two mezzanine scrap boards assembled. Some alterations to the spacer required. 10 th November 2009