FATALICs circuits de lecture pour llectronique front end

- Slides: 13

FATALICs : circuits de lecture pour l’électronique front end du Tile. Cal de s-Atlas en IBM 130 nm 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 1

Sommaire • Contexte de développement • Les circuits FATALIC • Building blocks • Résultats de tests • Conclusions et perspectives 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 2

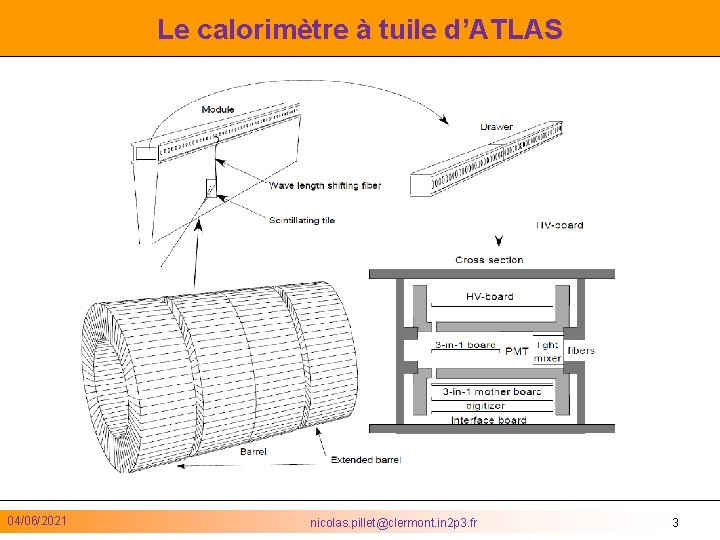

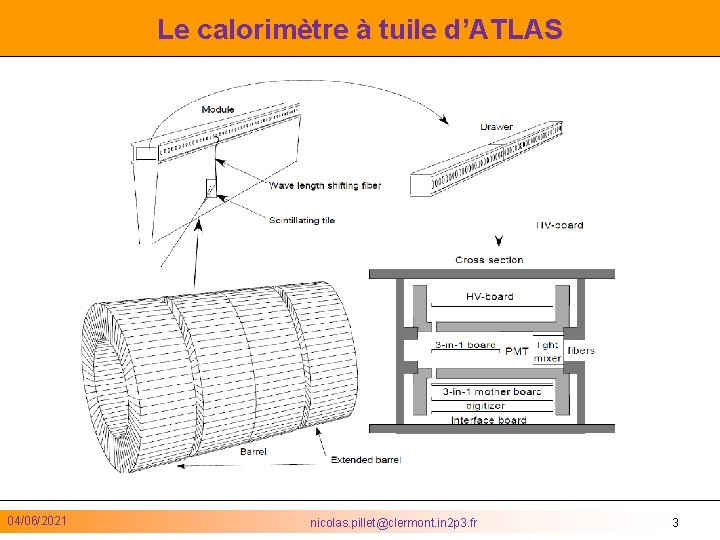

Le calorimètre à tuile d’ATLAS 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 3

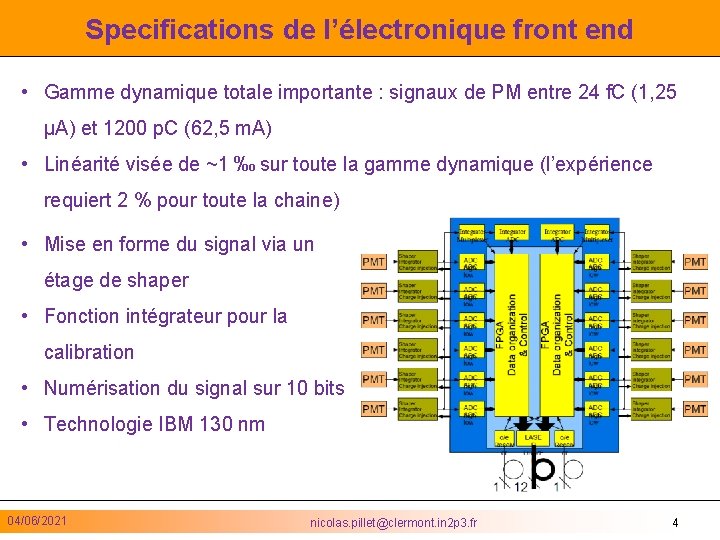

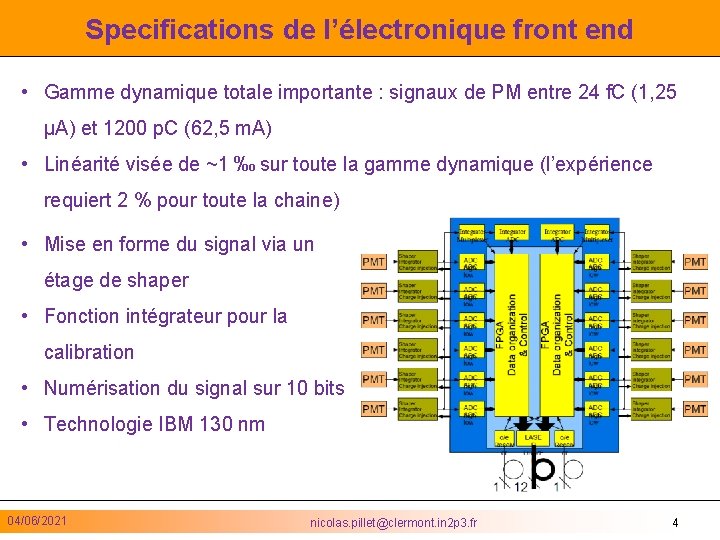

Specifications de l’électronique front end • Gamme dynamique totale importante : signaux de PM entre 24 f. C (1, 25 µA) et 1200 p. C (62, 5 m. A) • Linéarité visée de ~1 ‰ sur toute la gamme dynamique (l’expérience requiert 2 % pour toute la chaine) • Mise en forme du signal via un étage de shaper • Fonction intégrateur pour la calibration • Numérisation du signal sur 10 bits • Technologie IBM 130 nm 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 4

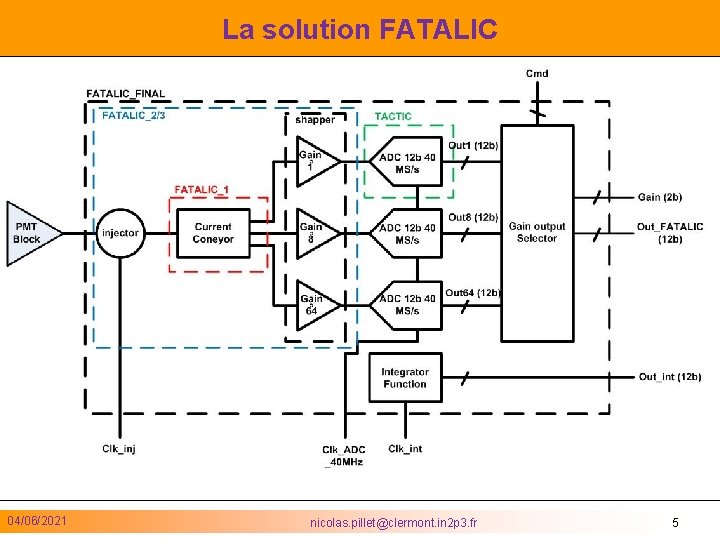

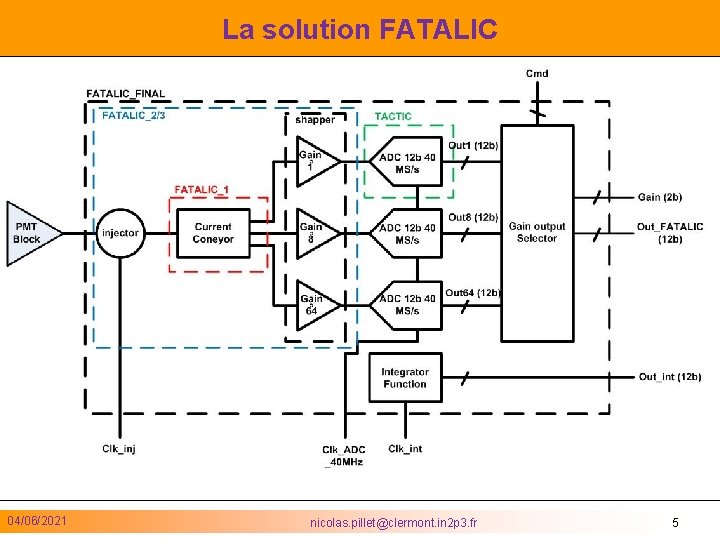

La solution FATALIC 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 5

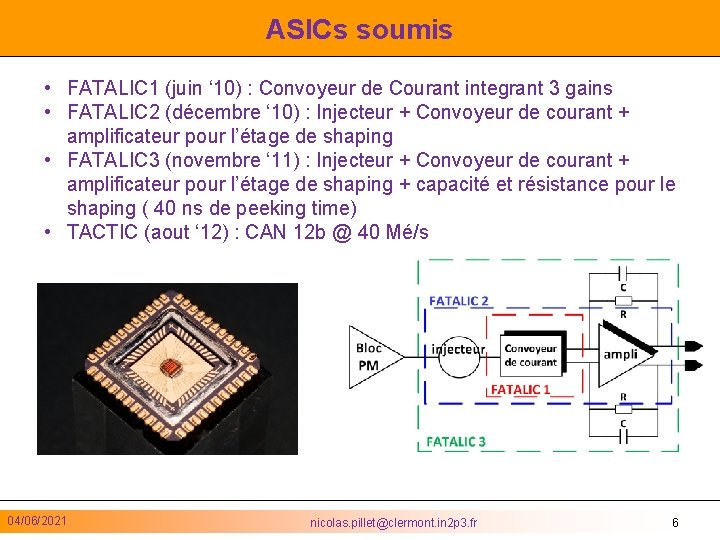

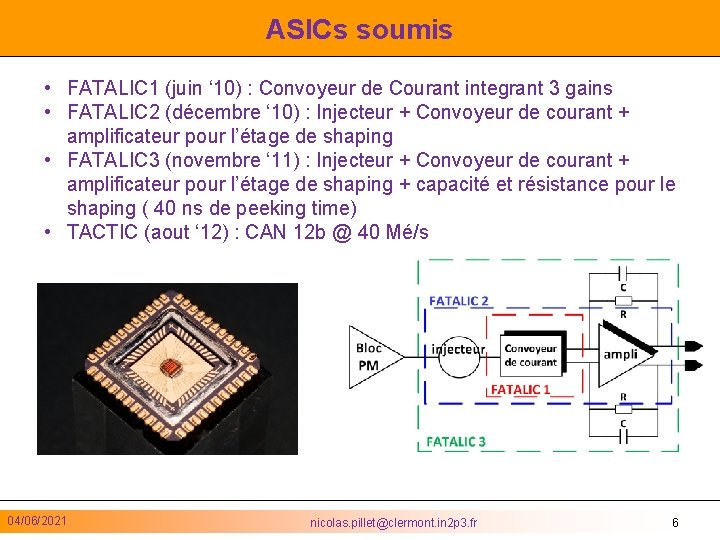

ASICs soumis • FATALIC 1 (juin ‘ 10) : Convoyeur de Courant integrant 3 gains • FATALIC 2 (décembre ‘ 10) : Injecteur + Convoyeur de courant + amplificateur pour l’étage de shaping • FATALIC 3 (novembre ‘ 11) : Injecteur + Convoyeur de courant + amplificateur pour l’étage de shaping + capacité et résistance pour le shaping ( 40 ns de peeking time) • TACTIC (aout ‘ 12) : CAN 12 b @ 40 Mé/s 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 6

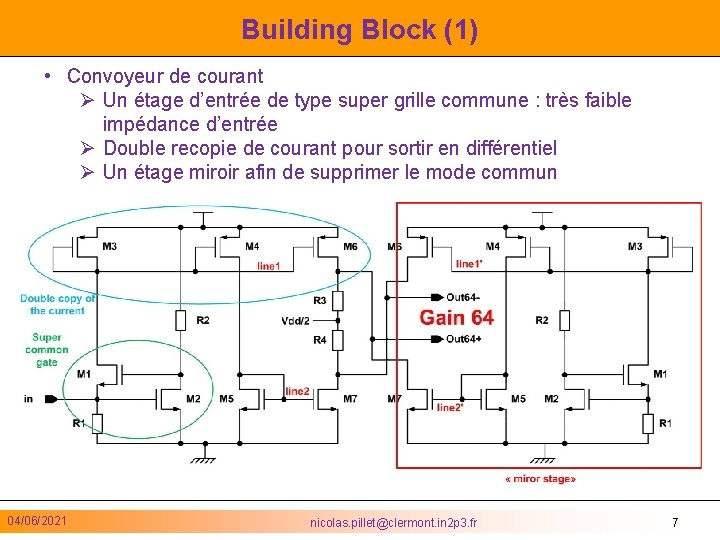

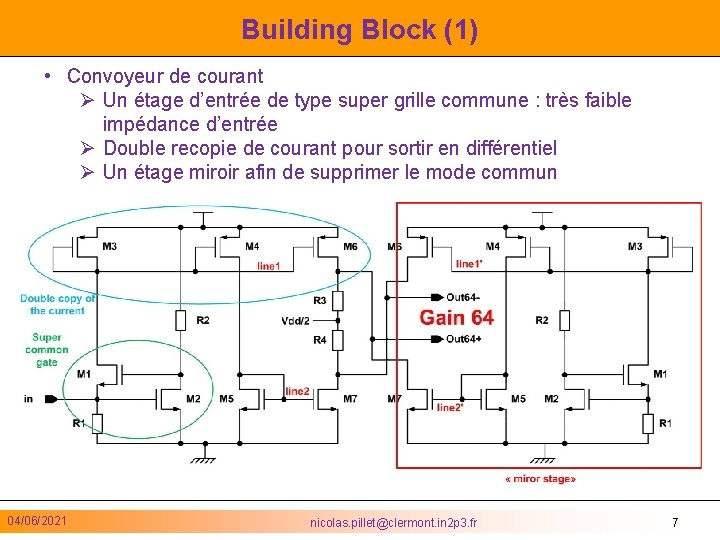

Building Block (1) • Convoyeur de courant Ø Un étage d’entrée de type super grille commune : très faible impédance d’entrée Ø Double recopie de courant pour sortir en différentiel Ø Un étage miroir afin de supprimer le mode commun 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 7

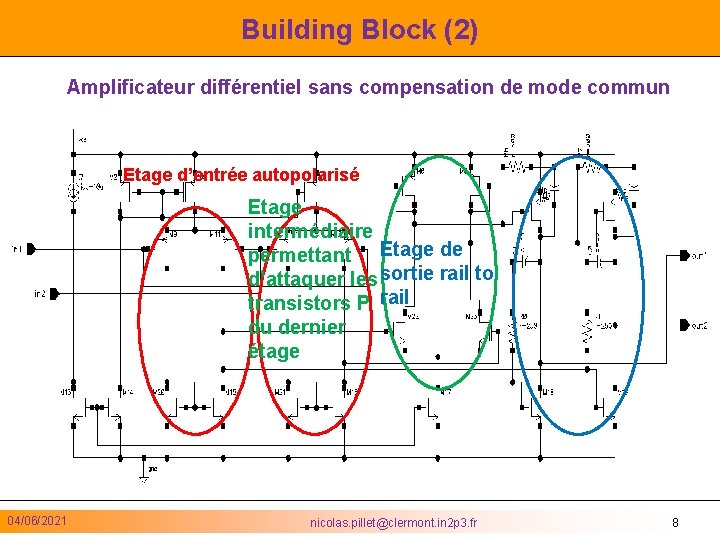

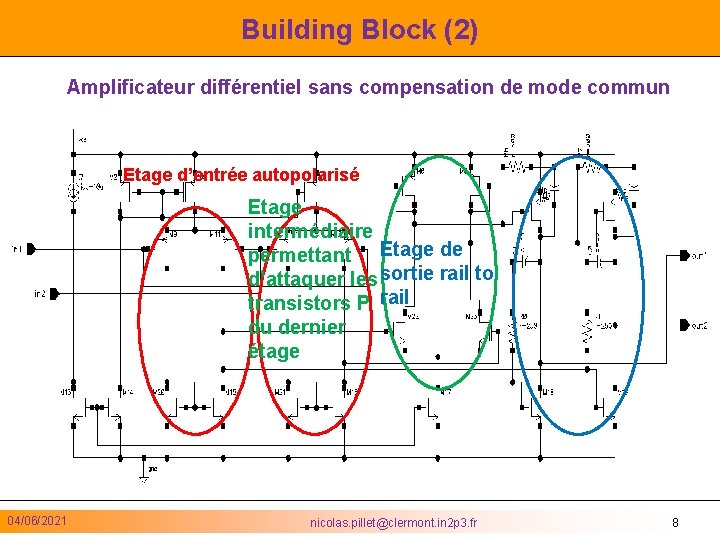

Building Block (2) Amplificateur différentiel sans compensation de mode commun Etage d’entrée autopolarisé Etage intermédiaire permettant Etage de d’attaquer les sortie rail to transistors P rail du dernier étage 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 8

Building Block (3) • Amplificateur différentiel sans compensation de mode commun • Gain en boucle ouverte : 4 400 • Marge de phase : 48° • Produit gain bande : 260 MHz • Capable de fournir 1 V rms sur 40 p. F • Bruit : 60 µV rms • Consommation 6, 8 m. W 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 9

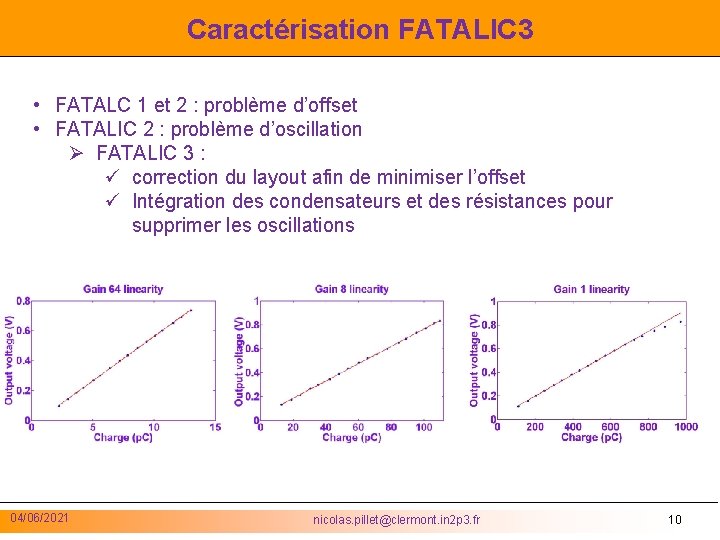

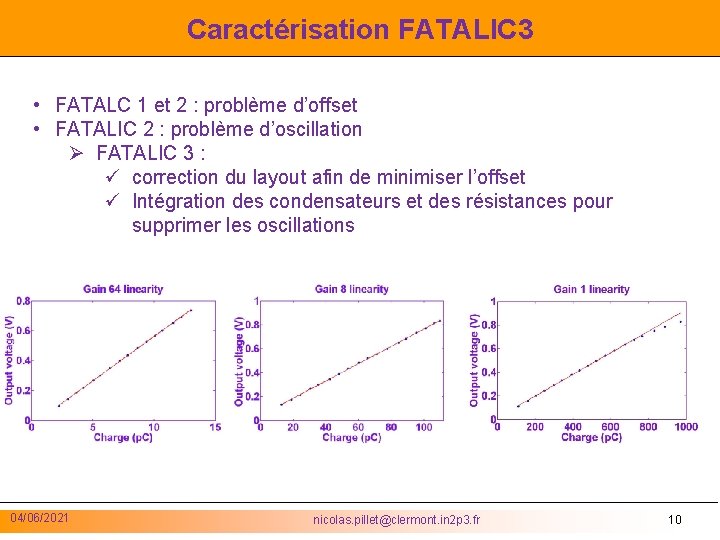

Caractérisation FATALIC 3 • FATALC 1 et 2 : problème d’offset • FATALIC 2 : problème d’oscillation Ø FATALIC 3 : ü correction du layout afin de minimiser l’offset ü Intégration des condensateurs et des résistances pour supprimer les oscillations 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 10

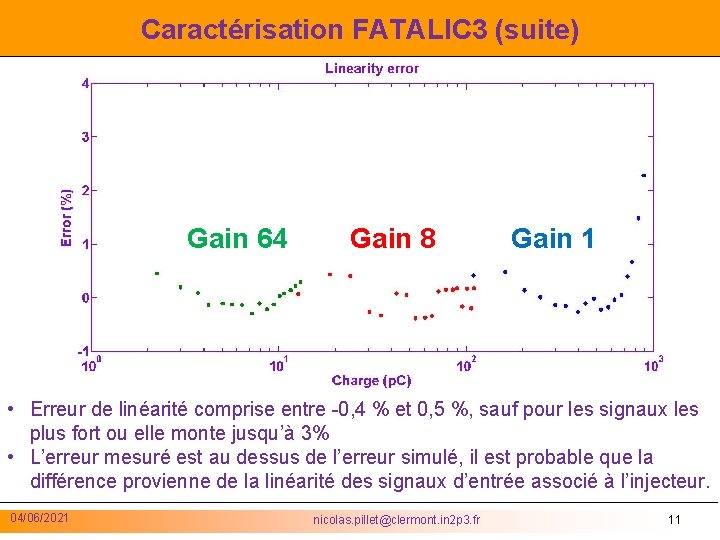

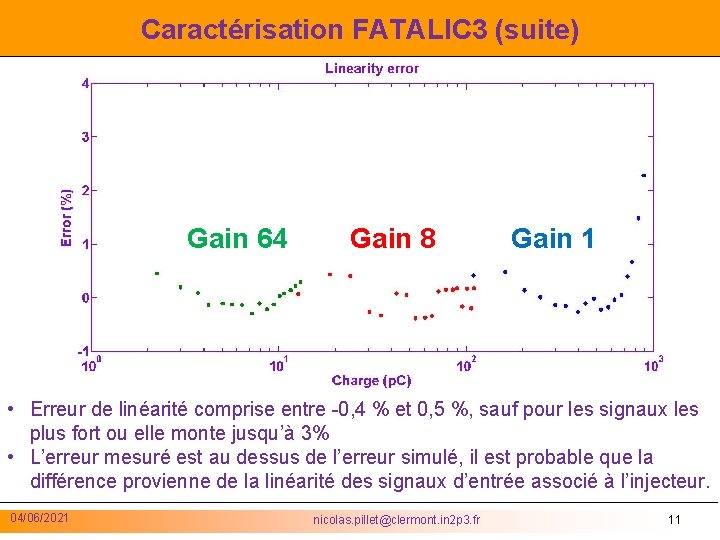

Caractérisation FATALIC 3 (suite) Gain 64 Gain 8 Gain 1 • Erreur de linéarité comprise entre -0, 4 % et 0, 5 %, sauf pour les signaux les plus fort ou elle monte jusqu’à 3% • L’erreur mesuré est au dessus de l’erreur simulé, il est probable que la différence provienne de la linéarité des signaux d’entrée associé à l’injecteur. 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 11

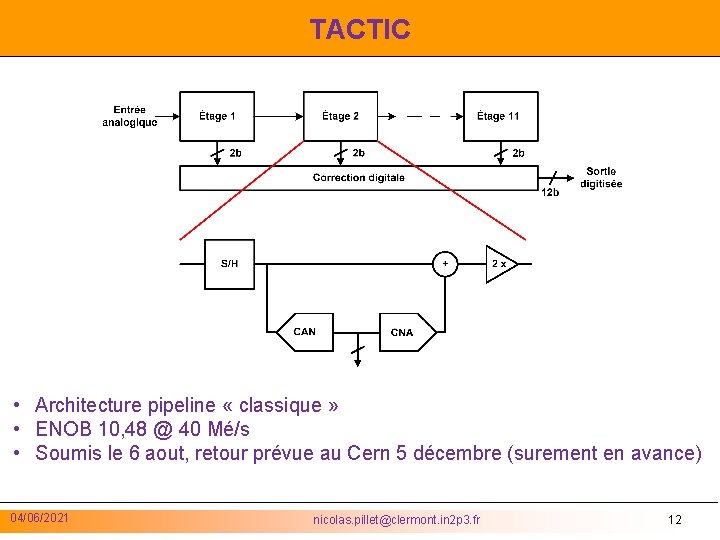

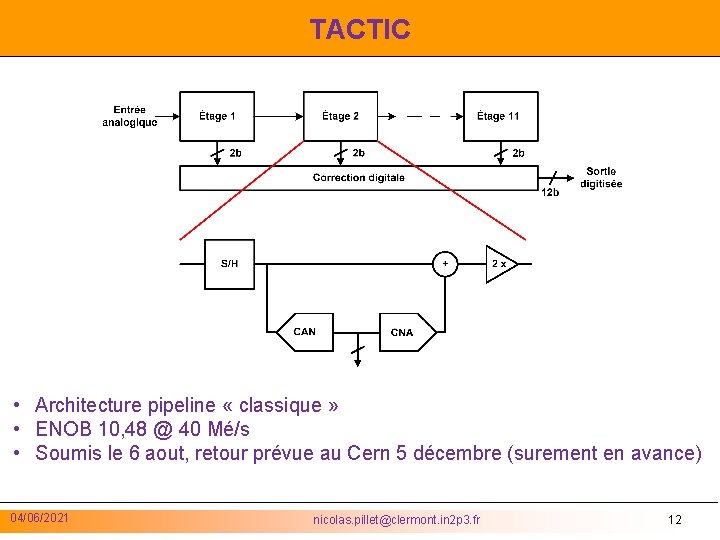

TACTIC • Architecture pipeline « classique » • ENOB 10, 48 @ 40 Mé/s • Soumis le 6 aout, retour prévue au Cern 5 décembre (surement en avance) 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 12

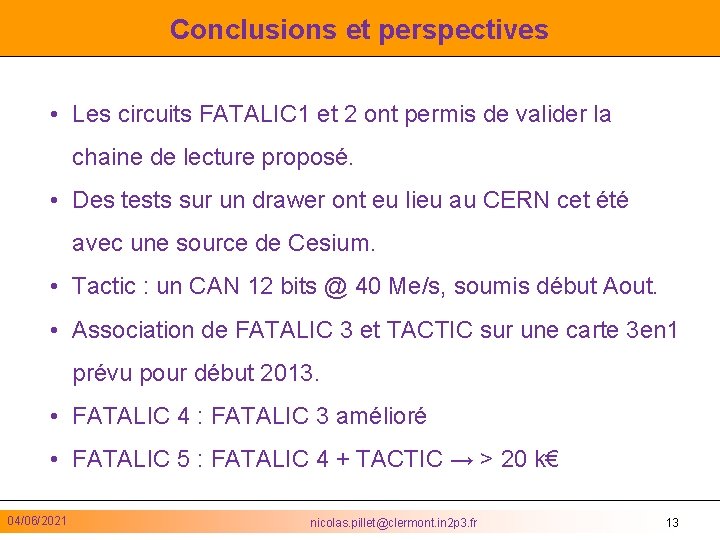

Conclusions et perspectives • Les circuits FATALIC 1 et 2 ont permis de valider la chaine de lecture proposé. • Des tests sur un drawer ont eu lieu au CERN cet été avec une source de Cesium. • Tactic : un CAN 12 bits @ 40 Me/s, soumis début Aout. • Association de FATALIC 3 et TACTIC sur une carte 3 en 1 prévu pour début 2013. • FATALIC 4 : FATALIC 3 amélioré • FATALIC 5 : FATALIC 4 + TACTIC → > 20 k€ 04/06/2021 nicolas. pillet@clermont. in 2 p 3. fr 13