Fast Pix N an ASIC for a fast

- Slides: 19

Fast. Pix. N an ASIC for a fast neutron telescope Maciej Kachel, IPHC Strasbourg

Outline – Fast. Pix. N • Motivation and current status • Chip requirements • Chip structure • Simulations • Future plans Maciej Kachel, IPHC Strasbourg

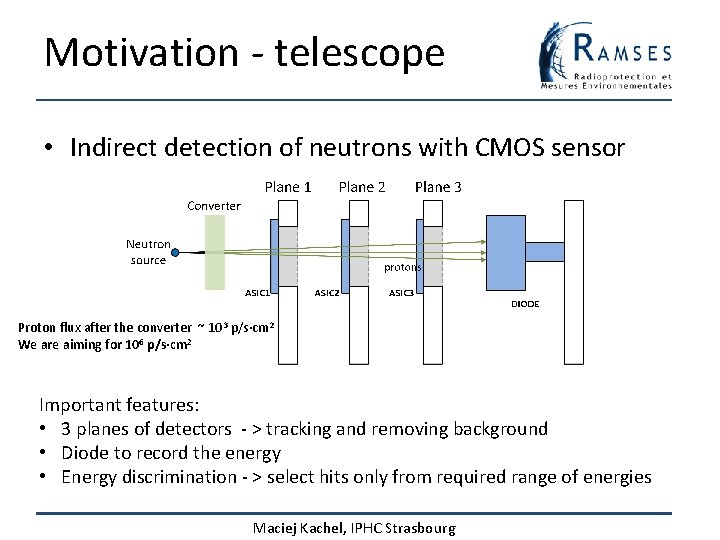

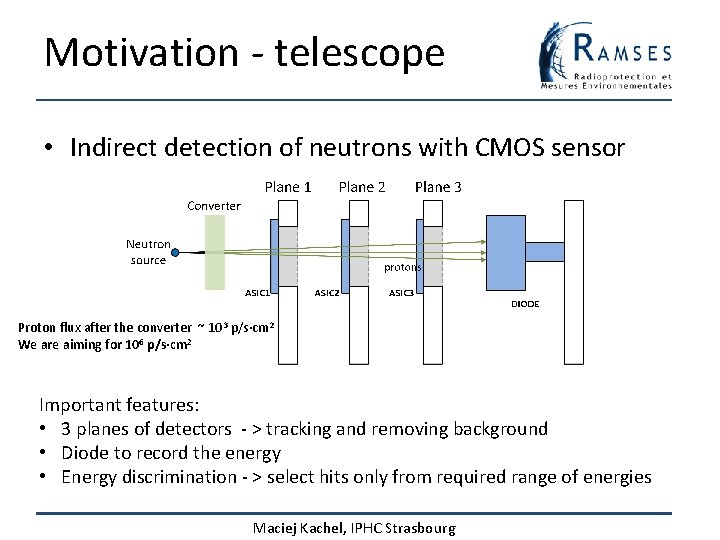

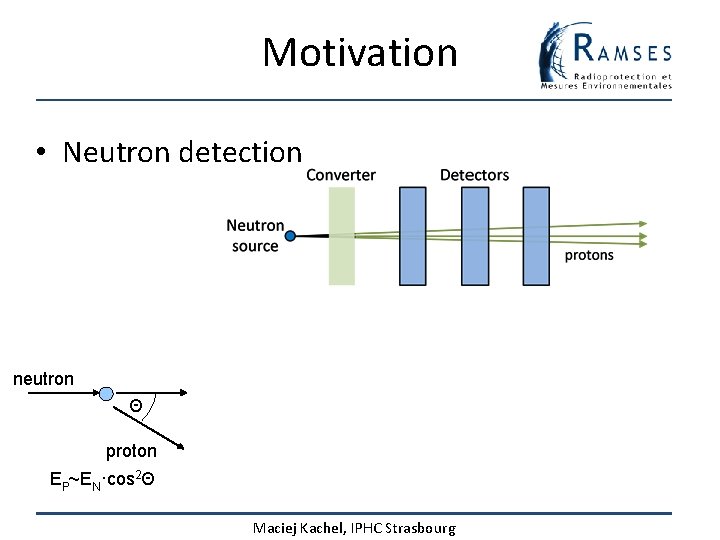

Motivation - telescope • Indirect detection of neutrons with CMOS sensor Proton flux after the converter ~ 103 p/s·cm 2 We are aiming for 106 p/s·cm 2 Important features: • 3 planes of detectors - > tracking and removing background • Diode to record the energy • Energy discrimination - > select hits only from required range of energies Maciej Kachel, IPHC Strasbourg

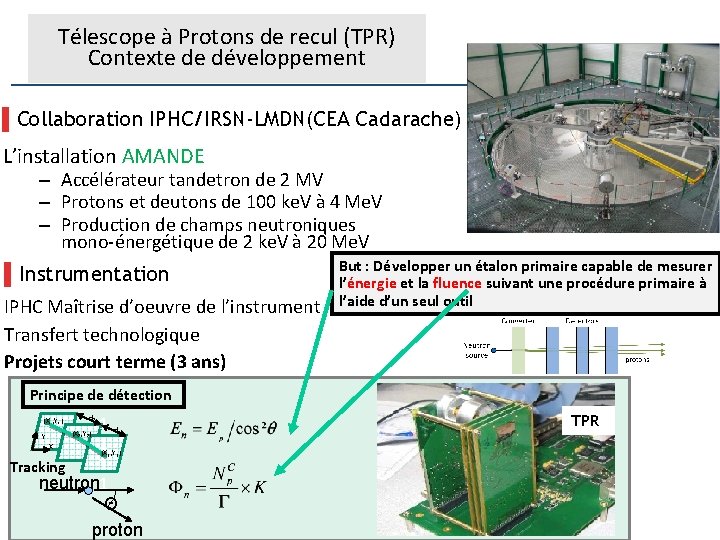

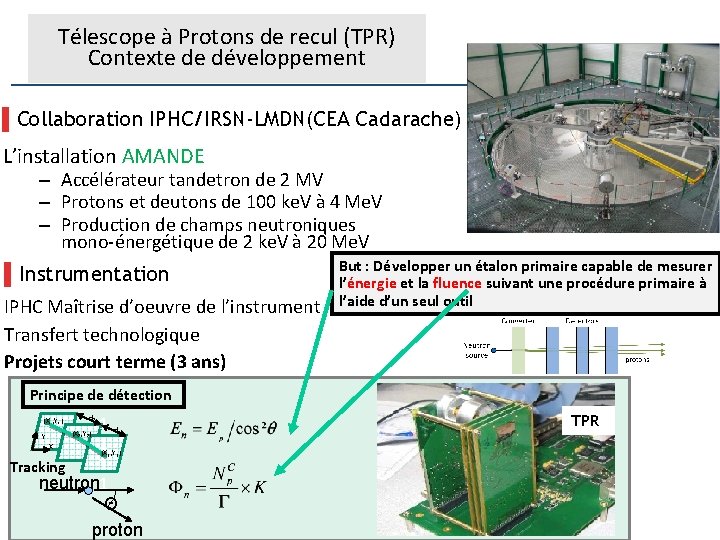

Télescope à Protons de recul (TPR) Contexte de développement ▌Collaboration IPHC/IRSN-LMDN(CEA Cadarache) L’installation AMANDE – Accélérateur tandetron de 2 MV – Protons et deutons de 100 ke. V à 4 Me. V – Production de champs neutroniques mono-énergétique de 2 ke. V à 20 Me. V ▌Instrumentation IPHC Maîtrise d’oeuvre de l’instrument Transfert technologique Projets court terme (3 ans) But : Développer un étalon primaire capable de mesurer l’énergie et la fluence suivant une procédure primaire à l’aide d’un seul outil Principe de détection 1 1 1 Tracking neutron 1 Θ proton (X 1, Y 1) d 2 (X 2, Y 2) Y X d 3 (X 3, Y 3) TPR

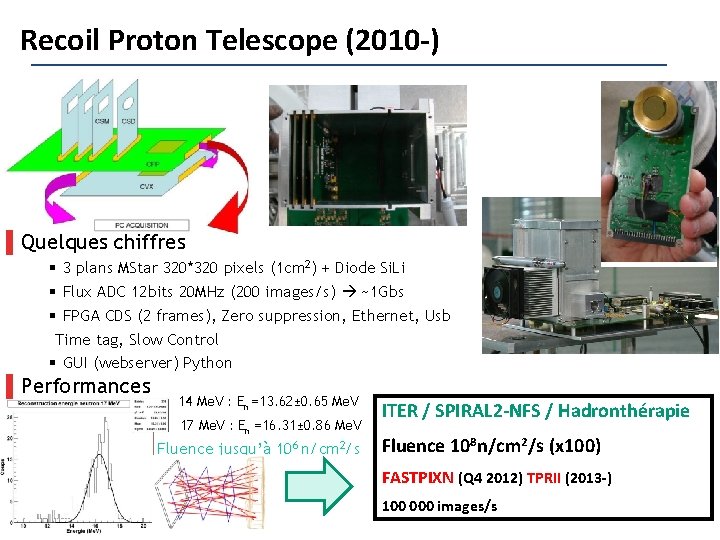

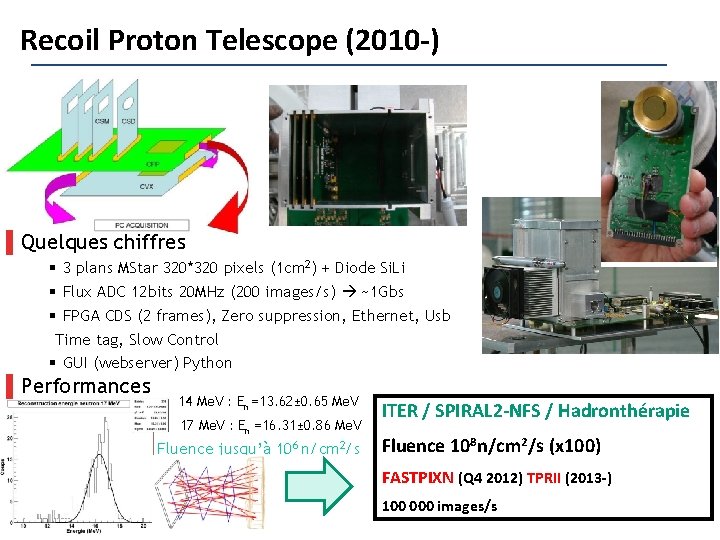

Recoil Proton Telescope (2010 -) ▌Quelques chiffres 3 plans MStar 320*320 pixels (1 cm 2) + Diode Si. Li Flux ADC 12 bits 20 MHz (200 images/s) ~1 Gbs FPGA CDS (2 frames), Zero suppression, Ethernet, Usb Time tag, Slow Control GUI (webserver) Python ▌Performances 14 Me. V : En =13. 62± 0. 65 Me. V 17 Me. V : En =16. 31± 0. 86 Me. V Fluence jusqu’à 106 n/cm 2/s ITER / SPIRAL 2 -NFS / Hadronthérapie Fluence 108 n/cm 2/s (x 100) FASTPIXN (Q 4 2012) TPRII (2013 -) 100 000 images/s

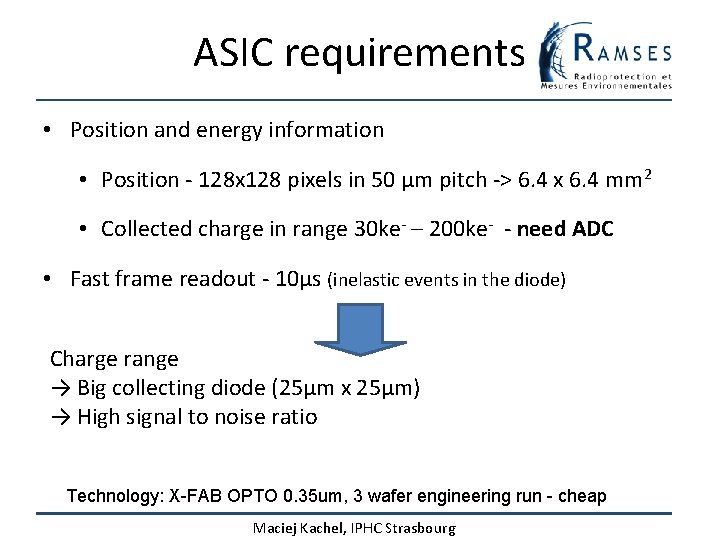

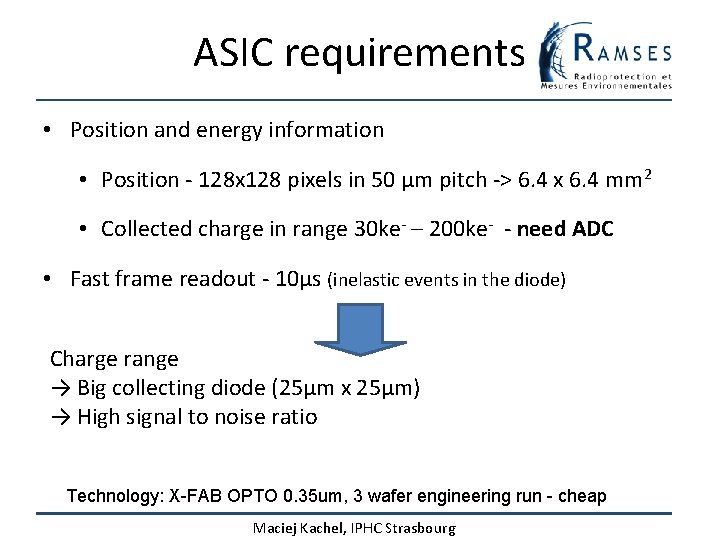

ASIC requirements • Position and energy information • Position - 128 x 128 pixels in 50 µm pitch -> 6. 4 x 6. 4 mm 2 • Collected charge in range 30 ke- – 200 ke- - need ADC • Fast frame readout - 10µs (inelastic events in the diode) Charge range → Big collecting diode (25µm x 25µm) → High signal to noise ratio Technology: X-FAB OPTO 0. 35 um, 3 wafer engineering run - cheap Maciej Kachel, IPHC Strasbourg

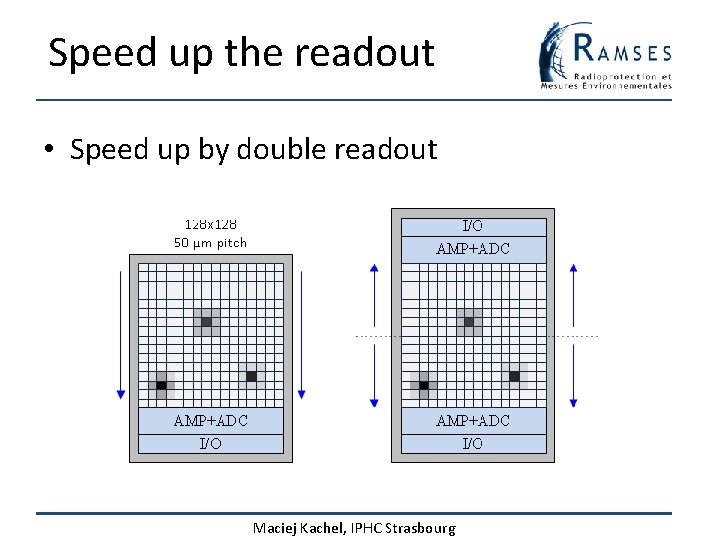

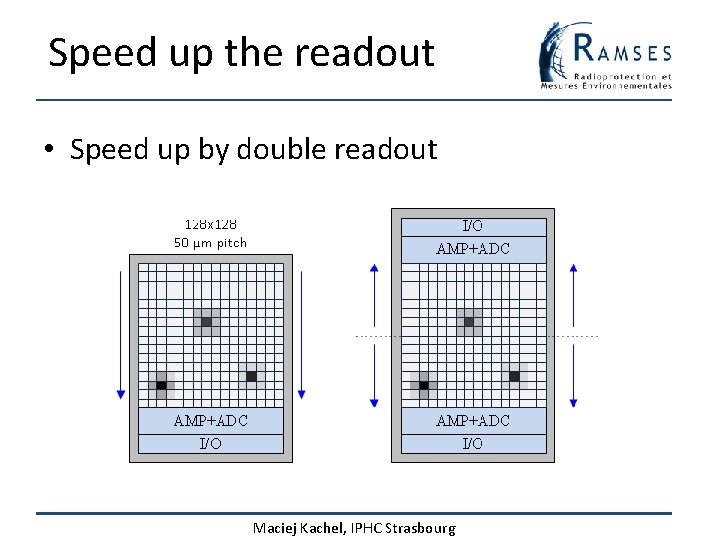

Speed up the readout • Speed up by double readout Maciej Kachel, IPHC Strasbourg

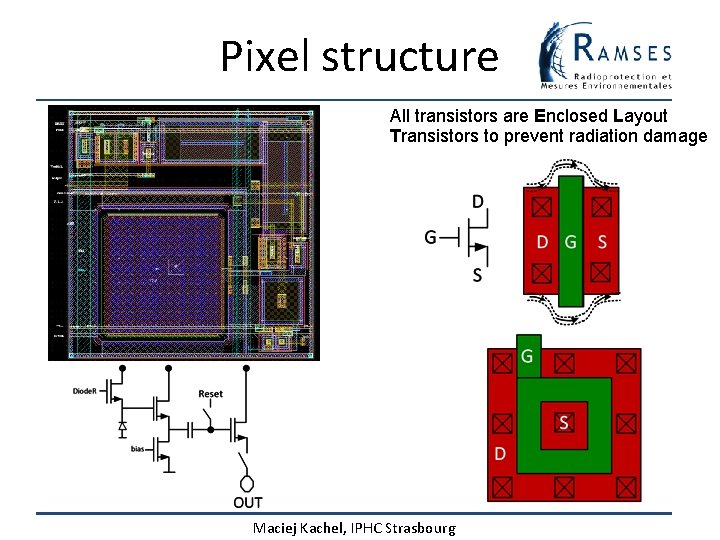

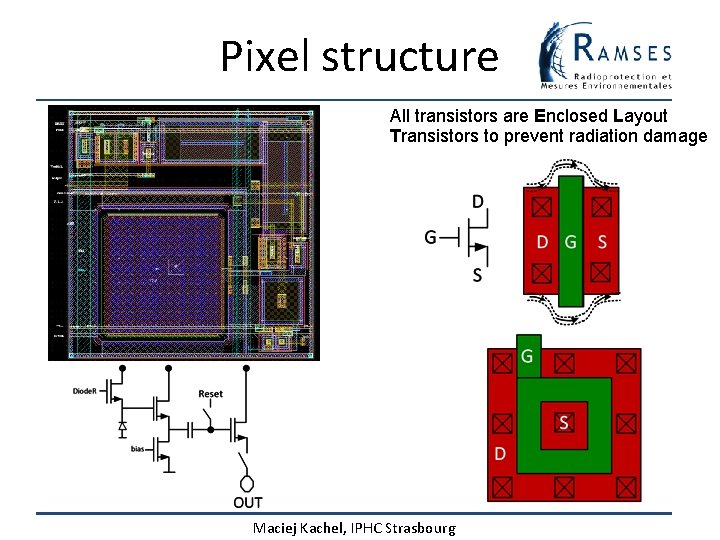

Pixel structure All transistors are Enclosed Layout Transistors to prevent radiation damage Maciej Kachel, IPHC Strasbourg

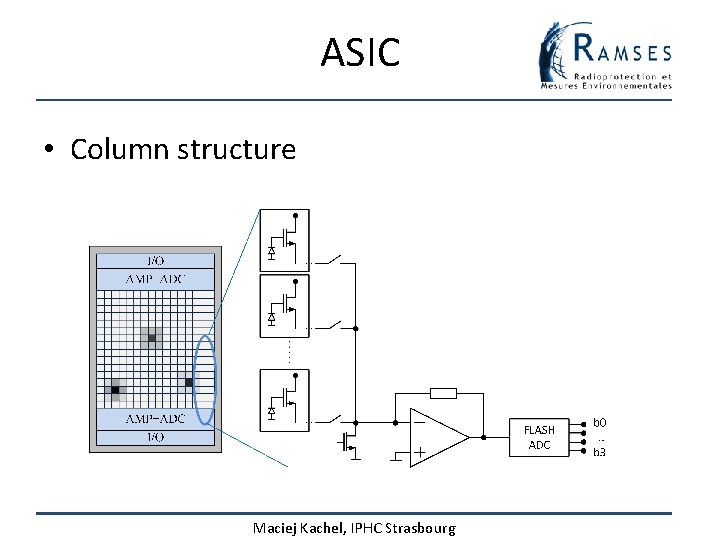

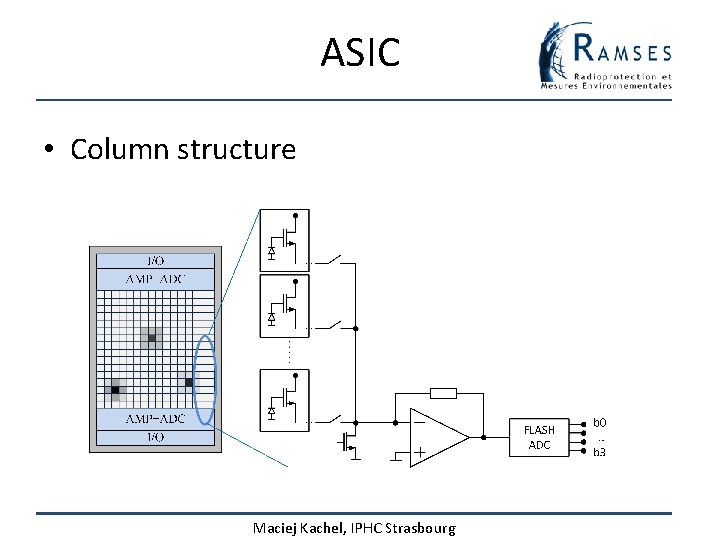

ASIC • Column structure Maciej Kachel, IPHC Strasbourg

ASIC • Readout structure (basic version) High speed LVDS drivers output the data from columns Maciej Kachel, IPHC Strasbourg

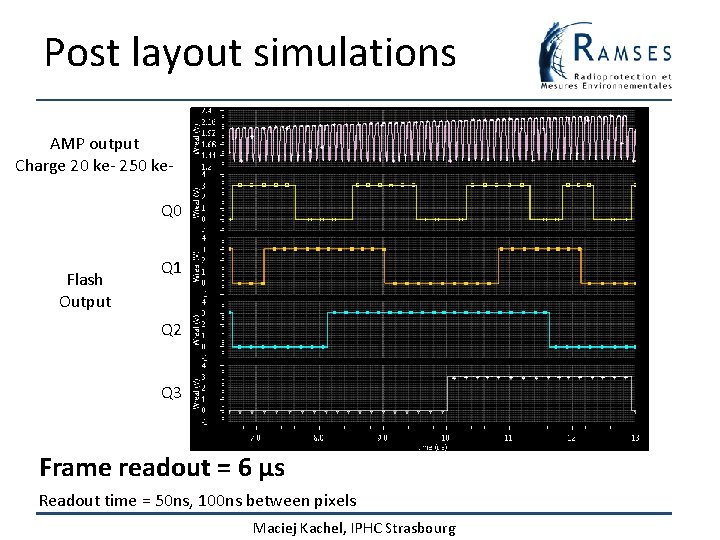

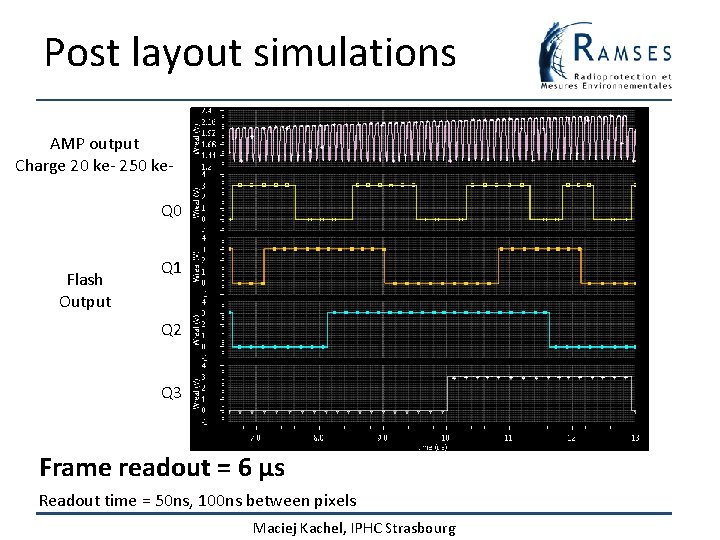

Post layout simulations AMP output Charge 20 ke- 250 ke. Q 0 Flash Output Q 1 Q 2 Q 3 Frame readout = 6 µs Readout time = 50 ns, 100 ns between pixels Maciej Kachel, IPHC Strasbourg

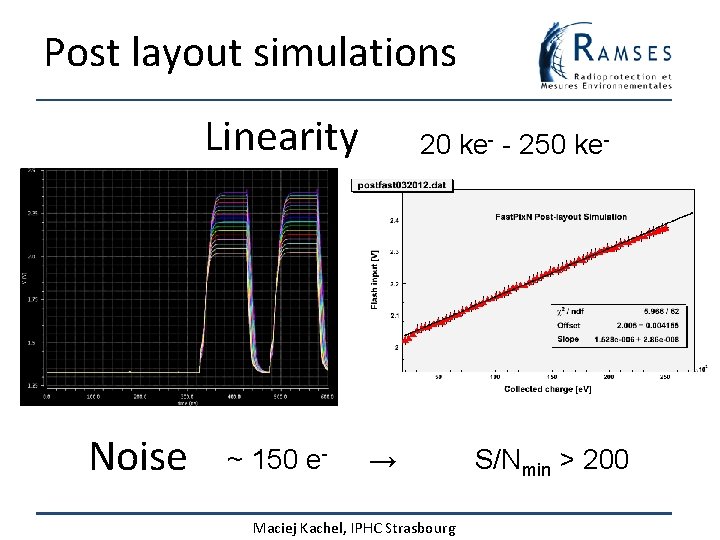

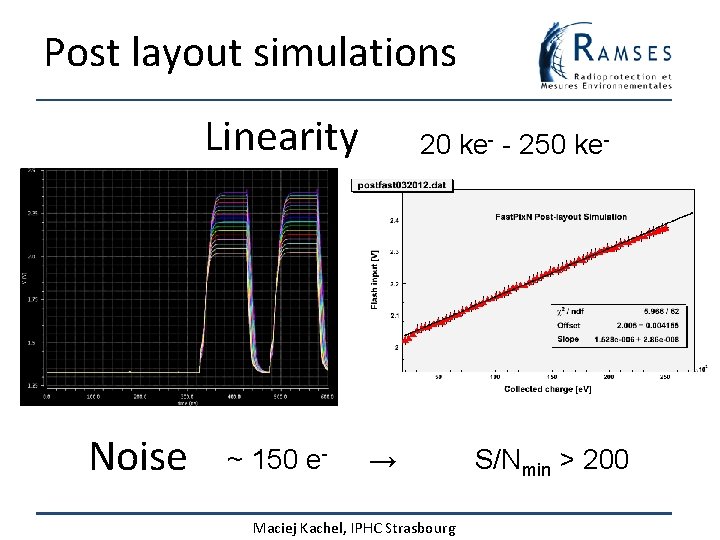

Post layout simulations Linearity Noise ~ 150 e- 20 ke- - 250 ke- → Maciej Kachel, IPHC Strasbourg S/Nmin > 200

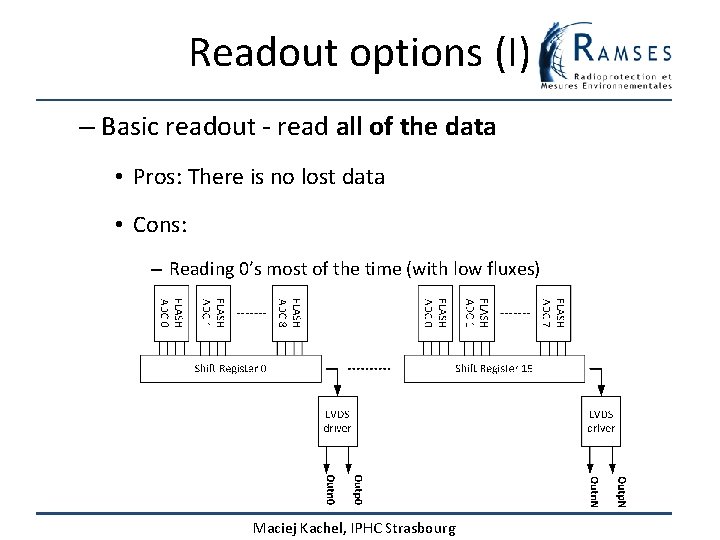

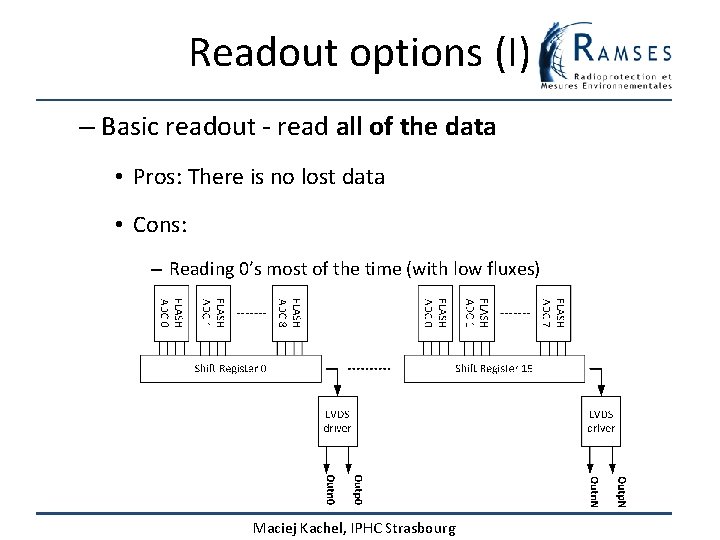

Readout options (I) – Basic readout - read all of the data • Pros: There is no lost data • Cons: – Reading 0’s most of the time (with low fluxes) Maciej Kachel, IPHC Strasbourg

Readout options (II) – Read only non-zero data • Pros: – Increase speed of the readout – Decrease the number of output lines/drivers – Simple with this hit rate • Cons: – may cause data loss (highly improbable) Both solutions will be implemented in the prototype Maciej Kachel, IPHC Strasbourg

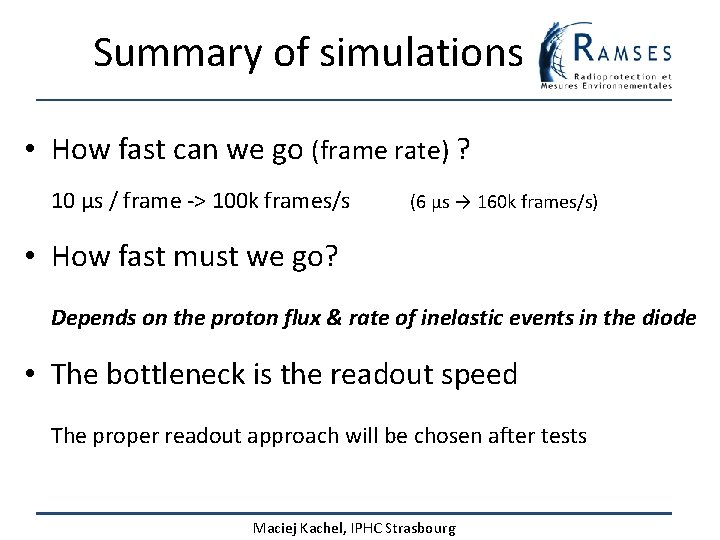

Summary of simulations • How fast can we go (frame rate) ? 10 µs / frame -> 100 k frames/s (6 μs → 160 k frames/s) • How fast must we go? Depends on the proton flux & rate of inelastic events in the diode • The bottleneck is the readout speed The proper readout approach will be chosen after tests Maciej Kachel, IPHC Strasbourg

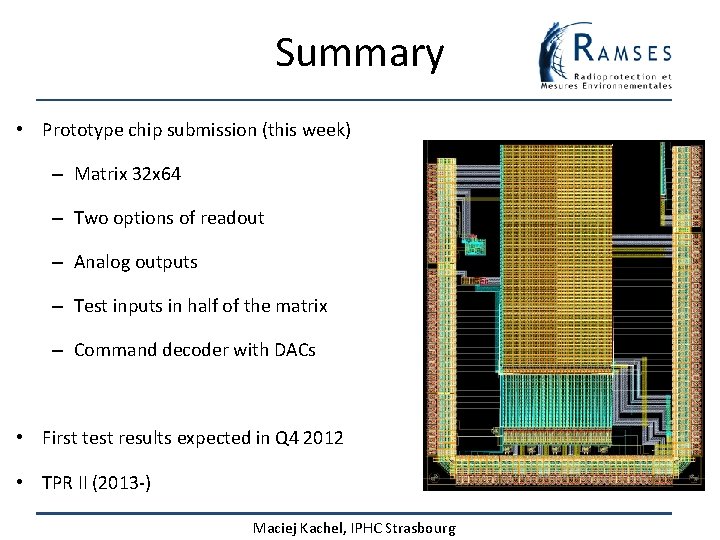

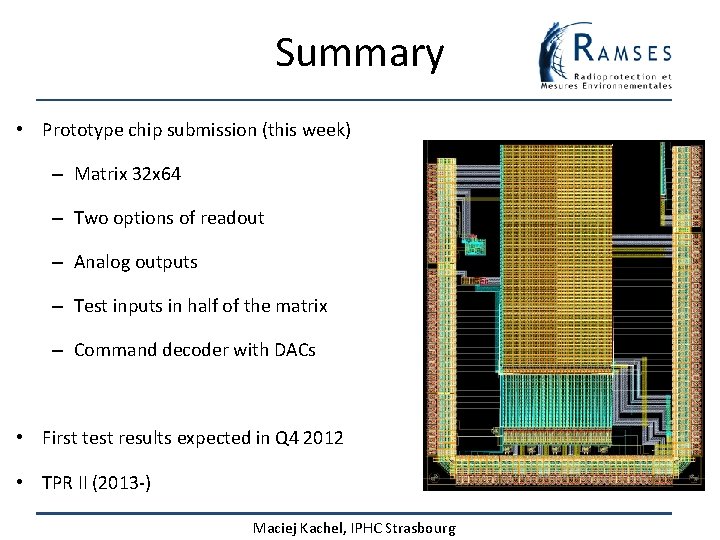

Summary • Prototype chip submission (this week) – Matrix 32 x 64 – Two options of readout – Analog outputs – Test inputs in half of the matrix – Command decoder with DACs • First test results expected in Q 4 2012 • TPR II (2013 -) Maciej Kachel, IPHC Strasbourg

Thank you for your attention Team : Fast. Pix. N D. Husson, S. Higueret, M. Kachel Maciej Kachel, IPHC Strasbourg

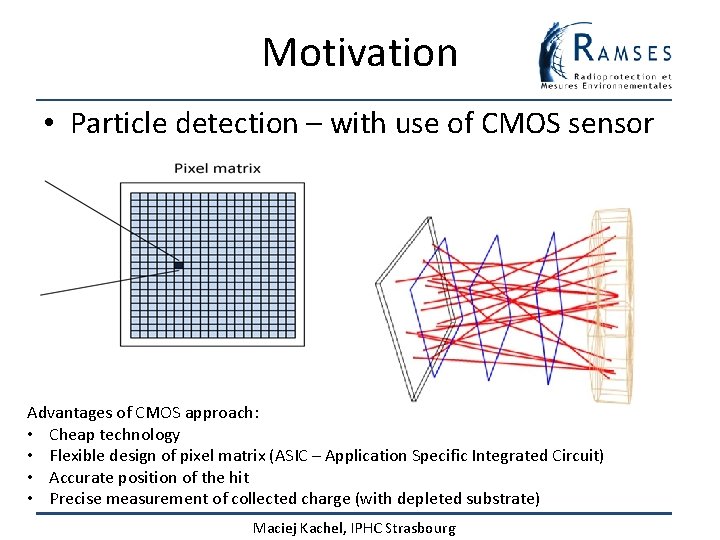

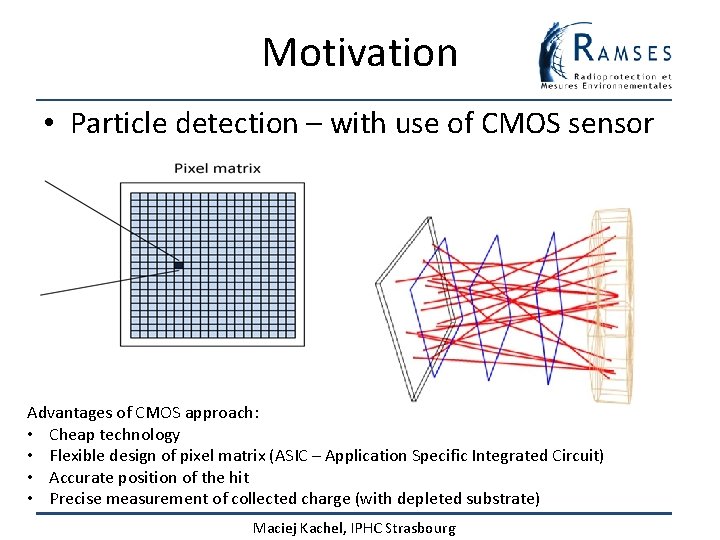

Motivation • Particle detection – with use of CMOS sensor Advantages of CMOS approach: • Cheap technology • Flexible design of pixel matrix (ASIC – Application Specific Integrated Circuit) • Accurate position of the hit • Precise measurement of collected charge (with depleted substrate) Maciej Kachel, IPHC Strasbourg

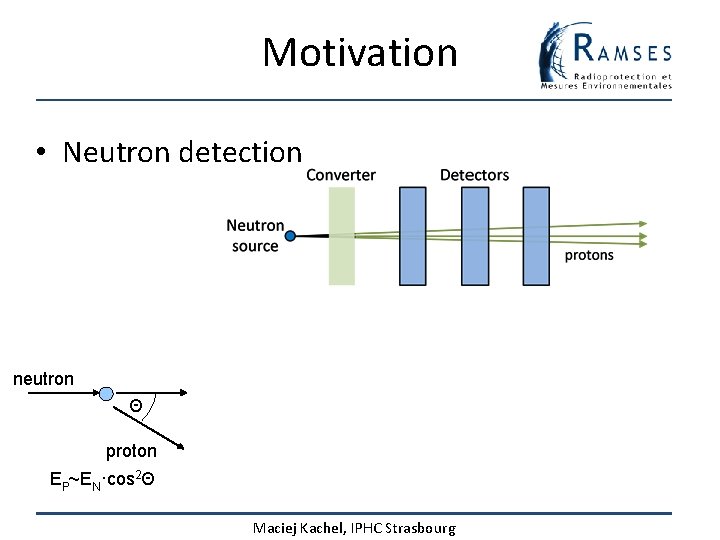

Motivation • Neutron detection neutron Θ proton EP~EN·cos 2Θ Maciej Kachel, IPHC Strasbourg