Fast IC Highly configurable ASIC for Fast Timing

Fast. IC: Highly configurable ASIC for Fast Timing applications Update for the Pico. TDC Users Meeting (23/5/2019) (1) CERN, EP-ESE-ME (2) University of Barcelona, ICCUB Rafael Ballabriga 1, Michael Campbell 1, Jose M. Fernandez-Tenllado 1, 2, David Gascon 2, Sergio Gomez 2, Rafel Manera 2, Joan Mauricio 2, Anand Sanmukh 2 1

Outline I. Motivation and Applications II. Architecture III. Summary and Status

Two different front-end developments for fast timing

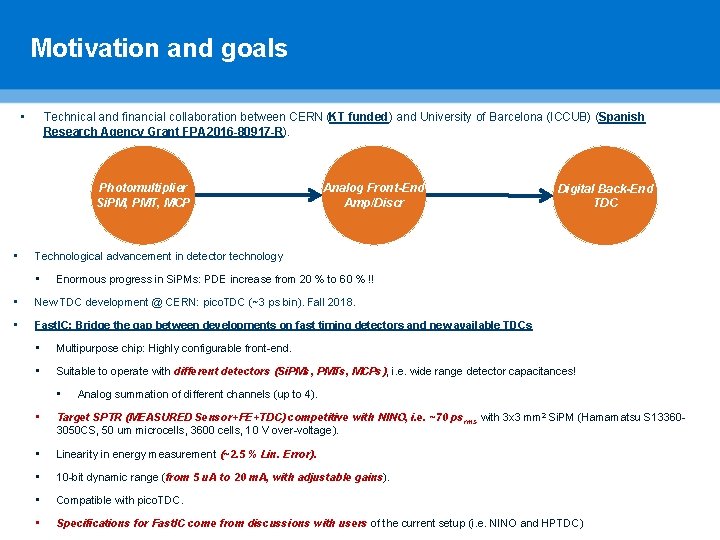

Motivation and goals • Technical and financial collaboration between CERN (KT funded) and University of Barcelona (ICCUB) (Spanish Research Agency Grant FPA 2016 -80917 -R). Photomultiplier Si. PM, PMT, MCP • Analog Front-End Amp/Discr Digital Back-End TDC Technological advancement in detector technology • Enormous progress in Si. PMs: PDE increase from 20 % to 60 % !! • New TDC development @ CERN: pico. TDC (~3 ps bin). Fall 2018. • Fast. IC: Bridge the gap between developments on fast timing detectors and new available TDCs • Multipurpose chip: Highly configurable front-end. • Suitable to operate with different detectors (Si. PMs, PMTs, MCPs), i. e. wide range detector capacitances! • Analog summation of different channels (up to 4). • Target SPTR (MEASURED Sensor+FE+TDC) competitive with NINO, i. e. ~70 psrms with 3 x 3 mm 2 Si. PM (Hamamatsu S 133603050 CS, 50 um microcells, 3600 cells, 10 V over-voltage). • Linearity in energy measurement (~2. 5 % Lin. Error). • 10 -bit dynamic range (from 5 u. A to 20 m. A, with adjustable gains). • Compatible with pico. TDC. • Specifications for Fast. IC come from discussions with users of the current setup (i. e. NINO and HPTDC)

1 st Fast. IC users meeting (Jun 2017) Fast timing with Si. PM for HEP and PET. Research on Scintillation materials & Rad. Hard. Research on meta-materials. LHCb To. F (Particle ID) Calorimetry Cherenkov To. F-PET PET, Hadron therapy Time resolved Spectroscopy (eg. FLIM), LIDAR, 3 D-Imaging

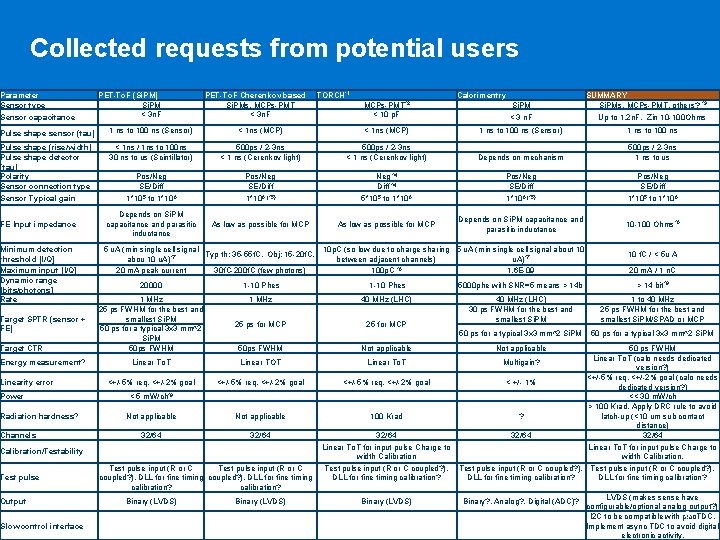

Collected requests from potential users Parameter Sensor type Sensor capacitance PET-To. F (Si. PM) Si. PM < 3 n. F PET-To. F Cherenkov based Si. PMs, MCPs-PMT < 3 n. F TORCH*1 Calorimentry MCPs-PMT*2 < 10 p. F Si. PM SUMMARY Si. PMs, MCPs-PMT, others? *3 < 3 n. F Up to 1. 2 n. F, Zin 10 -100 Ohms Pulse shape sensor (tau) 1 ns to 100 ns (Sensor) < 1 ns (MCP) 1 ns to 100 ns (Sensor) 1 ns to 100 ns Pulse shape (rise/width) Pulse shape detector (tau) Polarity Sensor connection type Sensor Typical gain < 1 ns / 1 ns to 100 ns 30 ns to us (Scintillator) 500 ps / 2 -3 ns < 1 ns (Cerenkov light) Depends on mechanism 500 ps / 2 -3 ns 1 ns to us Pos/Neg SE/Diff 1*105 to 1*10 6 Pos/Neg SE/Diff 1*106 (*5) Neg *4 Diff *4 5*105 to 1*10 6 Pos/Neg SE/Diff 1*106 (*5) Pos/Neg SE/Diff 1*105 to 1*10 6 Depends on Si. PM capacitance and parasitic inductance As low as possible for MCP Depends on Si. PM capacitance and parasitic inductance 10 -100 Ohms *6 FE Input impedance Minimum detection threshold [I/Q] Maximum input [I/Q] Dynamic range [bits/photons] Rate Target SPTR (sensor + FE) Target CTR Energy measurement? Linearity error Power Radiation hardness? Channels 5 u. A (min single cell signal Typ th: 35 -55 f. C. Obj: 15 -20 f. C. abou 10 u. A) *7 20 m. A peak current 30 f. C-200 f. C (few photons) Output Slow control interface 10 f. C / < 5 u A 20 m. A / 1 n. C 20000 1 -10 Phes 5000 phe with SNR=5 means > 14 b > 14 bit*8 1 MHz 25 ps FWHM for the best and smallest Si. PM 50 ps for a typical 3 x 3 mm^2 Si. PM 50 ps FWHM 1 MHz 40 MHz (LHC) 25 ps for MCP 25 for MCP 40 MHz (LHC) 30 ps FWHM for the best and smallest Si. PM 1 to 40 MHz 25 ps FWHM for the best and smallest Si. PM/SPAD or MCP 50 ps for a typical 3 x 3 mm^2 Si. PM 50 ps FWHM Not applicable Linear To. T Linear TOT Linear To. T <+/-5% req, <+/-2% goal Not applicable 100 Krad 32/64 Linear To. T for input pulse Charge to width Calibration Test pulse input (R or C coupled? ). DLL for fine timing calibration? < 5 m. W/ch*9 Calibration/Testability Test pulse 10 p. C (so low due to charge sharing 5 u. A (min single cell signal about 10 between adjacent channels) u. A)*7 *6 100 p. C 1. 6 E-09 Test pulse input (R or C coupled? ). DLL for fine timing calibration? Binary (LVDS) Not applicable 50 ps FWHM Linear To. T (calo needs dedicated Multigain? version? ) <+/-5% req, <+/-2% goal (calo needs < +/- 1% dedicated version? ) << 30 m. W/ch > 100 Krad. Apply DRC rule to avoid latch-up (<10 um sub contact ? distance) 32/64 Linear To. T for input pulse Charge to width Calibration. Test pulse input (R or C coupled? ). DLL for fine timing calibration? Binary? , Analog? , Digital (ADC)? LVDS (makes sense have configurable/optional analog output? ) 6 I 2 C to be compatible with pico. TDC. Implement async TDC to avoid digital electronic activity.

Outline I. Motivation and Applications II. Architecture III. Summary and Status

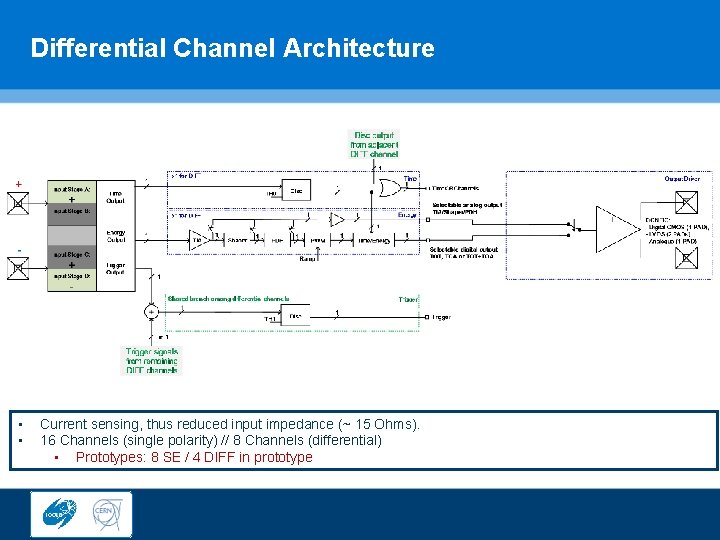

Differential Channel Architecture • • Current sensing, thus reduced input impedance (~ 15 Ohms). 16 Channels (single polarity) // 8 Channels (differential) • Prototypes: 8 SE / 4 DIFF in prototype

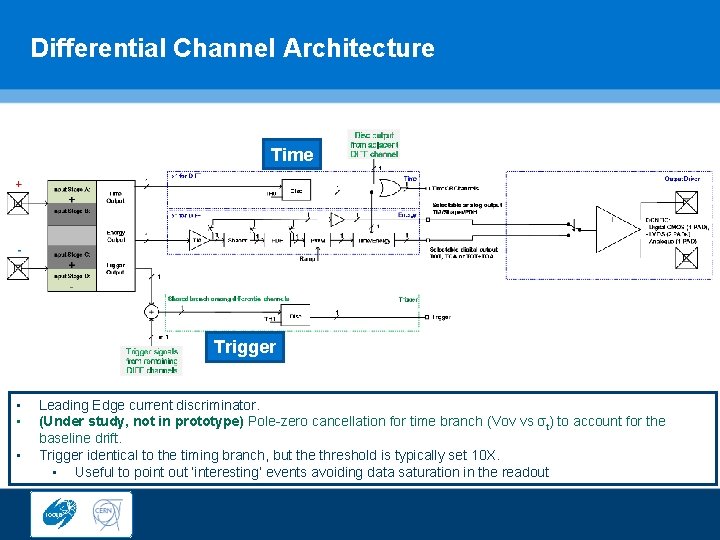

Differential Channel Architecture Time Trigger • • • Leading Edge current discriminator. (Under study, not in prototype) Pole-zero cancellation for time branch (Vov vs σt) to account for the baseline drift. Trigger identical to the timing branch, but the threshold is typically set 10 X. • Useful to point out ‘interesting’ events avoiding data saturation in the readout

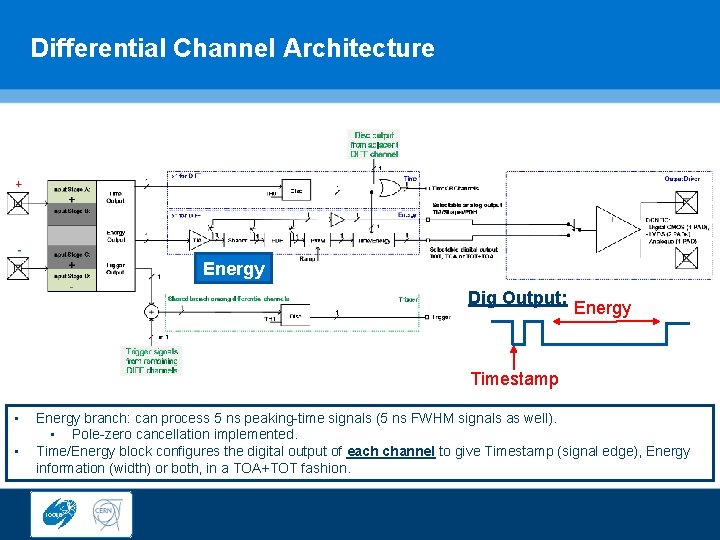

Differential Channel Architecture Energy Dig Output: Energy Timestamp • • Energy branch: can process 5 ns peaking-time signals (5 ns FWHM signals as well). • Pole-zero cancellation implemented. Time/Energy block configures the digital output of each channel to give Timestamp (signal edge), Energy information (width) or both, in a TOA+TOT fashion.

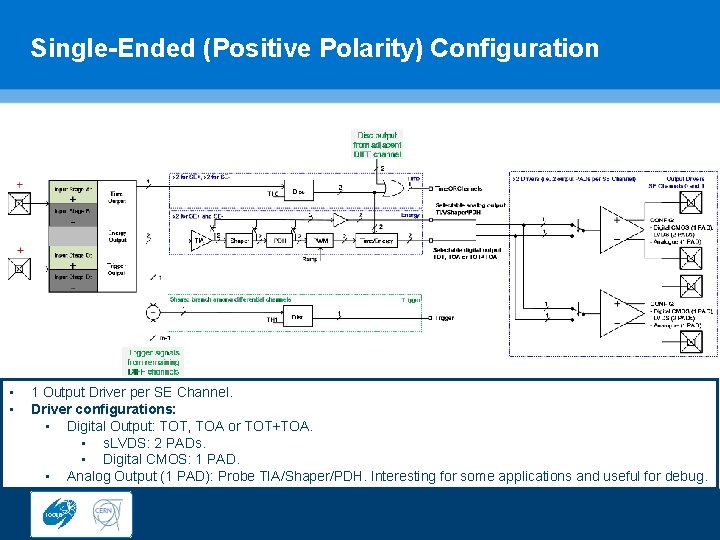

Single-Ended (Positive Polarity) Configuration • • 1 Output Driver per SE Channel. Driver configurations: • Digital Output: TOT, TOA or TOT+TOA. • s. LVDS: 2 PADs. • Digital CMOS: 1 PAD. • Analog Output (1 PAD): Probe TIA/Shaper/PDH. Interesting for some applications and useful for debug.

Single-Ended (Negative Polarity) Configuration • • 1 Output Driver per SE Channel Driver configurations: • Digital Output: TOT, TOA or TOT+TOA. • s. LVDS: 2 PADs. • Digital CMOS: 1 PAD. • Analog Output (1 PAD): Probe TIA/Shaper/PDH. Interesting for some applications and useful for debug.

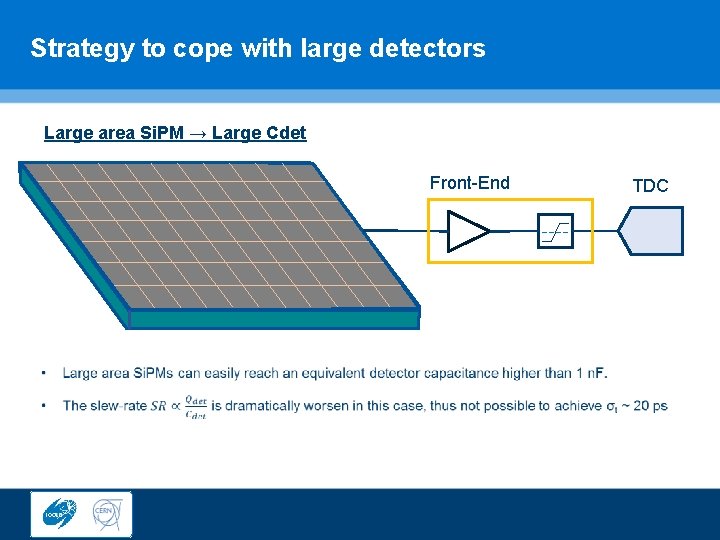

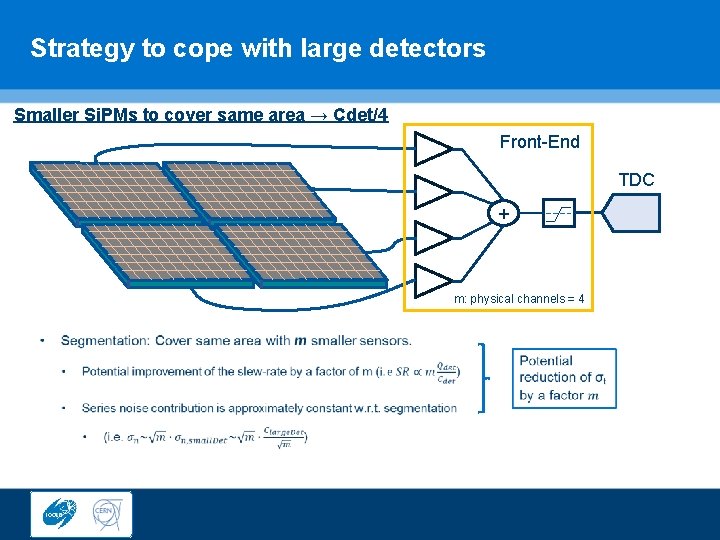

Strategy to cope with large detectors Large area Si. PM → Large Cdet Front-End • TDC

Strategy to cope with large detectors Smaller Si. PMs to cover same area → Cdet/4 Front-End TDC + m: physical channels = 4 •

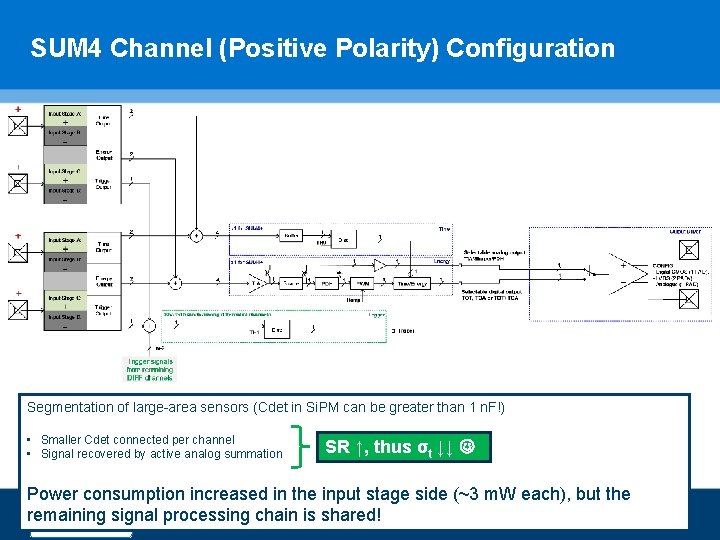

SUM 4 Channel (Positive Polarity) Configuration Segmentation of large-area sensors (Cdet in Si. PM can be greater than 1 n. F!) • Smaller Cdet connected per channel • Signal recovered by active analog summation SR ↑, thus σt ↓↓ Power consumption increased in the input stage side (~3 m. W each), but the remaining signal processing chain is shared!

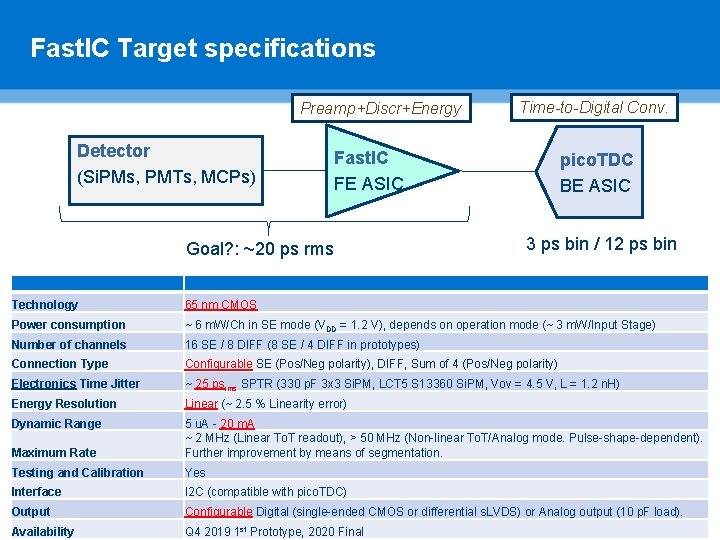

Fast. IC Target specifications Preamp+Discr+Energy Detector (Si. PMs, PMTs, MCPs) Time-to-Digital Conv. Fast. IC FE ASIC Goal? : ~20 ps rms pico. TDC BE ASIC 3 ps bin / 12 ps bin Technology 65 nm CMOS Power consumption ~ 6 m. W/Ch in SE mode (VDD = 1. 2 V), depends on operation mode (~ 3 m. W/Input Stage) Number of channels 16 SE / 8 DIFF (8 SE / 4 DIFF in prototypes) Connection Type Configurable SE (Pos/Neg polarity), DIFF, Sum of 4 (Pos/Neg polarity) Electronics Time Jitter ~ 25 psrms SPTR (330 p. F 3 x 3 Si. PM, LCT 5 S 13360 Si. PM, Vov = 4. 5 V, L = 1. 2 n. H) Energy Resolution Linear (~ 2. 5 % Linearity error) Dynamic Range Maximum Rate 5 u. A - 20 m. A ~ 2 MHz (Linear To. T readout), > 50 MHz (Non-linear To. T/Analog mode. Pulse-shape-dependent). Further improvement by means of segmentation. Testing and Calibration Yes Interface I 2 C (compatible with pico. TDC) Output Configurable Digital (single-ended CMOS or differential s. LVDS) or Analog output (10 p. F load). Availability Q 4 2019 1 st Prototype, 2020 Final

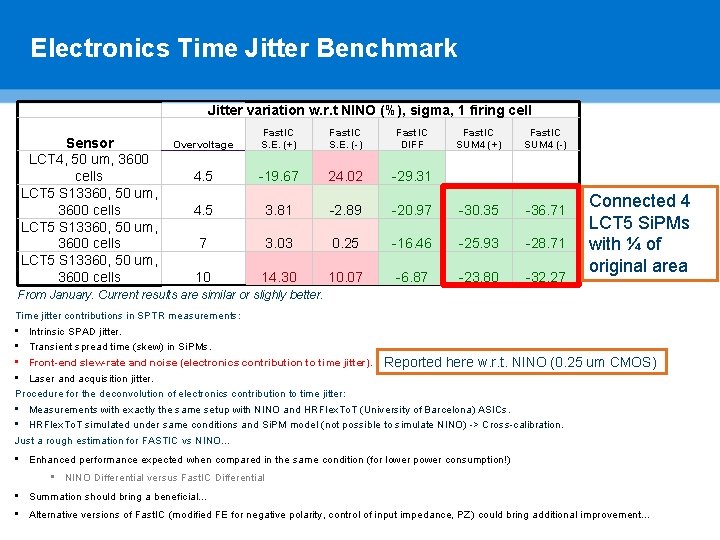

Electronics Time Jitter Benchmark Jitter variation w. r. t NINO (%), sigma, 1 firing cell Sensor LCT 4, 50 um, 3600 cells LCT 5 S 13360, 50 um, 3600 cells Overvoltage Fast. IC S. E. (+) Fast. IC S. E. (-) Fast. IC DIFF Fast. IC SUM 4 (+) Fast. IC SUM 4 (-) 4. 5 -19. 67 24. 02 -29. 31 4. 5 3. 81 -2. 89 -20. 97 -30. 35 -36. 71 7 3. 03 0. 25 -16. 46 -25. 93 -28. 71 10 14. 30 10. 07 -6. 87 -23. 80 -32. 27 Connected 4 LCT 5 Si. PMs with ¼ of original area From January. Current results are similar or slighly better. Time jitter contributions in SPTR measurements: • Intrinsic SPAD jitter. • Transient spread time (skew) in Si. PMs. • Front-end slew-rate and noise (electronics contribution to time jitter). Reported here w. r. t. NINO (0. 25 • Laser and acquisition jitter. Procedure for the deconvolution of electronics contribution to time jitter: • Measurements with exactly the same setup with NINO and HRFlex. To. T (University of Barcelona) ASICs. • HRFlex. To. T simulated under same conditions and Si. PM model (not possible to simulate NINO) -> Cross-calibration. Just a rough estimation for FASTIC vs NINO… um CMOS) • Enhanced performance expected when compared in the same condition (for lower power consumption!) • NINO Differential versus Fast. IC Differential • Summation should bring a beneficial… • Alternative versions of Fast. IC (modified FE for negative polarity, control of input impedance, PZ) could bring additional improvement…

Outline I. Motivation and Applications II. Architecture III. Summary and Status

Summary and Status • • A highly configurable multi-channel ASIC for fast-timing applications is being designed (CERN/KT – University of Barcelona collaboration) - Bridge developments. Similar role as NINO, but with completely different architecture. - Multi-detector compatible (Si. PMs, PMTs, MCPs) - Technology: CMOS 65 nm Exploiting new strategies and some already tested in previous designs - Single ended / differential / SUM 4 configurability, for positive or negative polarities - Linearized To. T and fast analog summation • Simulations and comparison with real measurements of similar ASICs (NINO, HRFlex. To. T) show promising results in terms of time jitter, particularly exploiting segmentation (SUM 4 mode). • Current status: layout and verification phase. • Expected 1 st prototype submission @ Aug 2019, tests during Q 4 2019. • Configurable 8 SE channels OR 4 Diff channels OR 2 SUM 4 channels.

Thanks! Q&A Further technical info: Rafael Ballabriga: rafael. ballabriga@cern. ch David Gascon: dgascon@fqa. ub. edu Jose M. Fernandez-Tenllado: jose. fernandez@cern. ch

- Slides: 20