Fast IC Highly configurable ASIC for Fast Timing

Fast. IC: Highly configurable ASIC for Fast Timing applications Pico. TDC Users Meeting (1) CERN, EP-ESE-ME (2) University of Barcelona, ICCUB R. Ballabriga 1, M. Campbell 1, Jose M. Fernandez-Tenllado 1, 2, D. Gascon 2, S. Gomez 2

Outline I. Motivation and Applications II. Fast. IC (simplified) architecture III. Conclusions

I. MOTIVATION & APPLICATIONS

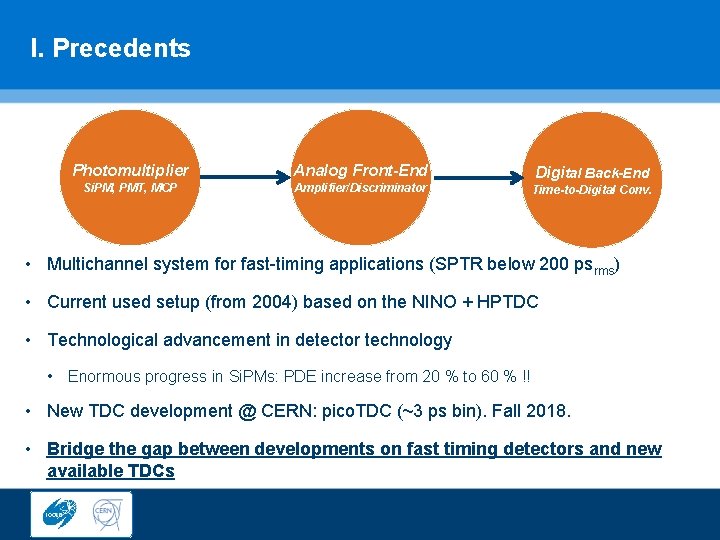

I. Precedents Photomultiplier Analog Front-End Si. PM, PMT, MCP Amplifier/Discriminator Digital Back-End Time-to-Digital Conv. • Multichannel system for fast-timing applications (SPTR below 200 psrms) • Current used setup (from 2004) based on the NINO + HPTDC • Technological advancement in detector technology • Enormous progress in Si. PMs: PDE increase from 20 % to 60 % !! • New TDC development @ CERN: pico. TDC (~3 ps bin). Fall 2018. • Bridge the gap between developments on fast timing detectors and new available TDCs

http: //kt. cern/success-stories/cern-chip-medical-imaging-industry

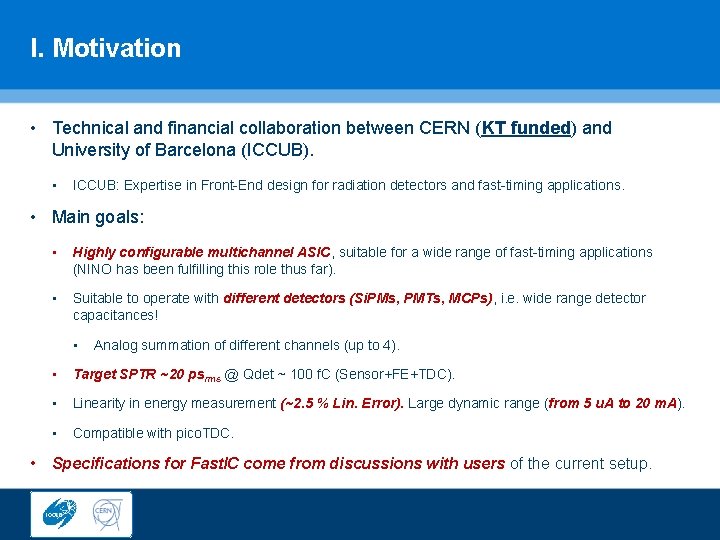

I. Motivation • Technical and financial collaboration between CERN (KT funded) and University of Barcelona (ICCUB). • ICCUB: Expertise in Front-End design for radiation detectors and fast-timing applications. • Main goals: • Highly configurable multichannel ASIC, suitable for a wide range of fast-timing applications (NINO has been fulfilling this role thus far). • Suitable to operate with different detectors (Si. PMs, PMTs, MCPs), i. e. wide range detector capacitances! • Analog summation of different channels (up to 4). • Target SPTR ~20 psrms @ Qdet ~ 100 f. C (Sensor+FE+TDC). • Linearity in energy measurement (~2. 5 % Lin. Error). Large dynamic range (from 5 u. A to 20 m. A). • Compatible with pico. TDC. • Specifications for Fast. IC come from discussions with users of the current setup.

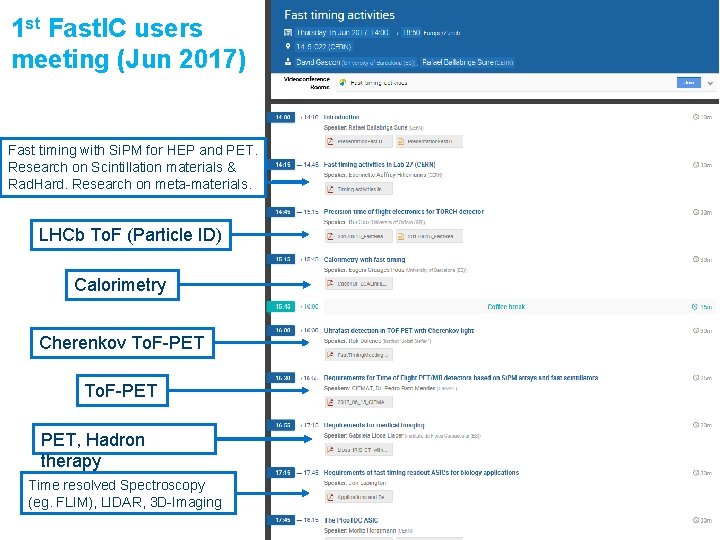

1 st Fast. IC users meeting (Jun 2017) Fast timing with Si. PM for HEP and PET. Research on Scintillation materials & Rad. Hard. Research on meta-materials. LHCb To. F (Particle ID) Calorimetry Cherenkov To. F-PET PET, Hadron therapy Time resolved Spectroscopy (eg. FLIM), LIDAR, 3 D-Imaging

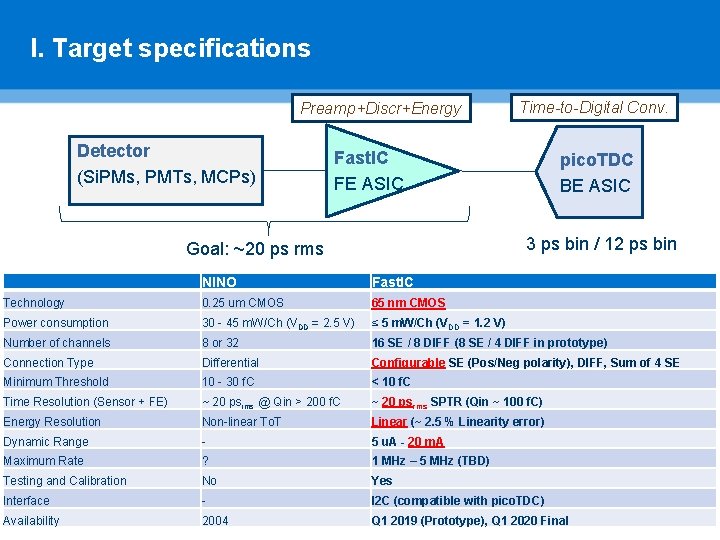

I. Target specifications Preamp+Discr+Energy Detector (Si. PMs, PMTs, MCPs) Time-to-Digital Conv. Fast. IC FE ASIC pico. TDC BE ASIC 3 ps bin / 12 ps bin Goal: ~20 ps rms NINO Fast. IC Technology 0. 25 um CMOS 65 nm CMOS Power consumption 30 - 45 m. W/Ch (VDD = 2. 5 V) ≤ 5 m. W/Ch (VDD = 1. 2 V) Number of channels 8 or 32 16 SE / 8 DIFF (8 SE / 4 DIFF in prototype) Connection Type Differential Configurable SE (Pos/Neg polarity), DIFF, Sum of 4 SE Minimum Threshold 10 - 30 f. C < 10 f. C Time Resolution (Sensor + FE) ~ 20 psrms @ Qin > 200 f. C ~ 20 psrms SPTR (Qin ~ 100 f. C) Energy Resolution Non-linear To. T Linear (~ 2. 5 % Linearity error) Dynamic Range - 5 u. A - 20 m. A Maximum Rate ? 1 MHz – 5 MHz (TBD) Testing and Calibration No Yes Interface - I 2 C (compatible with pico. TDC) Availability 2004 Q 1 2019 (Prototype), Q 1 2020 Final

II. FASTIC ARCHITECTURE

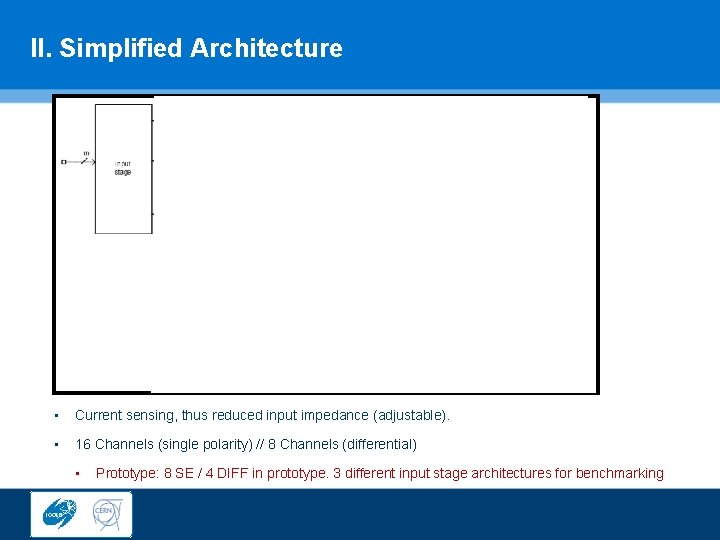

II. Simplified Architecture • Current sensing, thus reduced input impedance (adjustable). • 16 Channels (single polarity) // 8 Channels (differential) • Prototype: 8 SE / 4 DIFF in prototype. 3 different input stage architectures for benchmarking

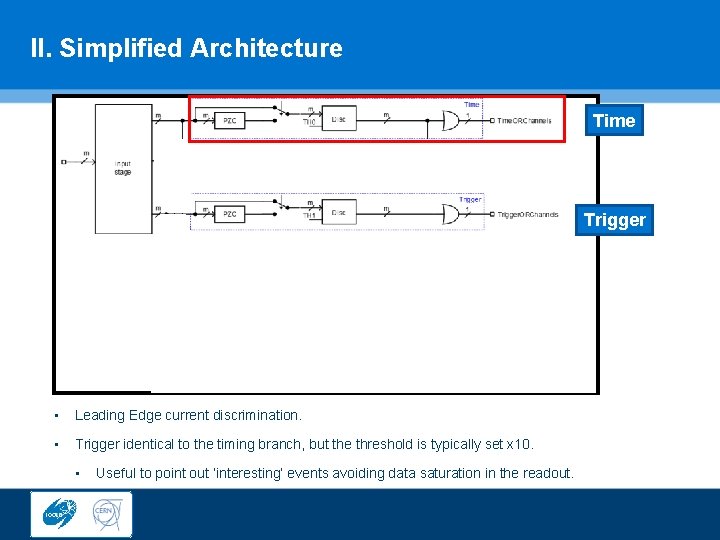

II. Simplified Architecture Time Trigger • Leading Edge current discrimination. • Trigger identical to the timing branch, but the threshold is typically set x 10. • Useful to point out ‘interesting’ events avoiding data saturation in the readout.

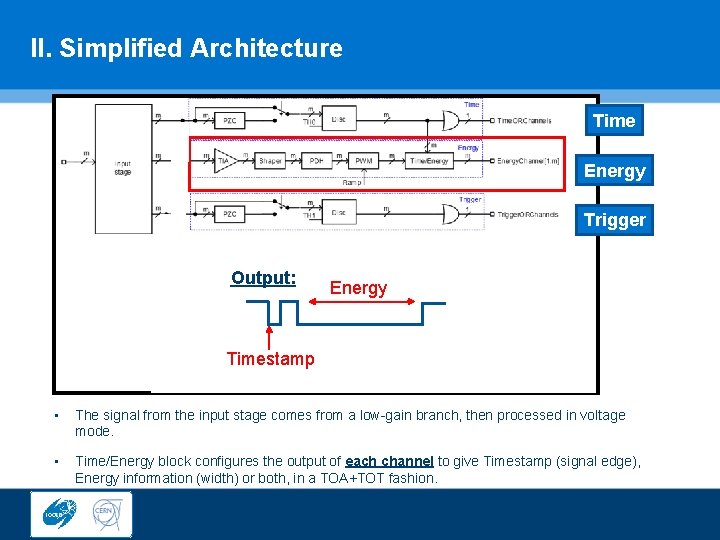

II. Simplified Architecture Time Energy Trigger Output: Energy Timestamp • The signal from the input stage comes from a low-gain branch, then processed in voltage mode. • Time/Energy block configures the output of each channel to give Timestamp (signal edge), Energy information (width) or both, in a TOA+TOT fashion.

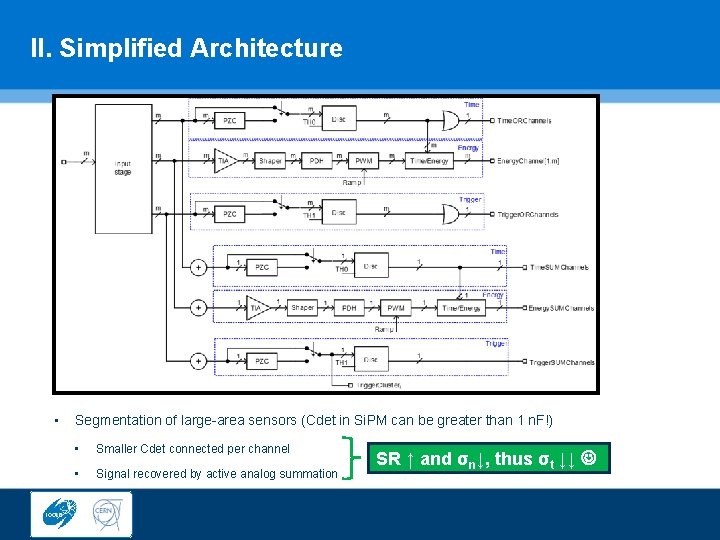

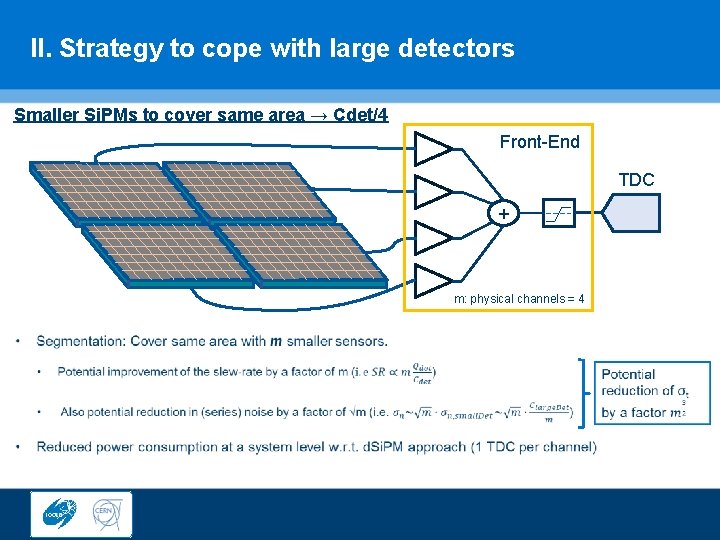

II. Simplified Architecture • Segmentation of large-area sensors (Cdet in Si. PM can be greater than 1 n. F!) • Smaller Cdet connected per channel • Signal recovered by active analog summation SR ↑ and σn↓, thus σt ↓↓

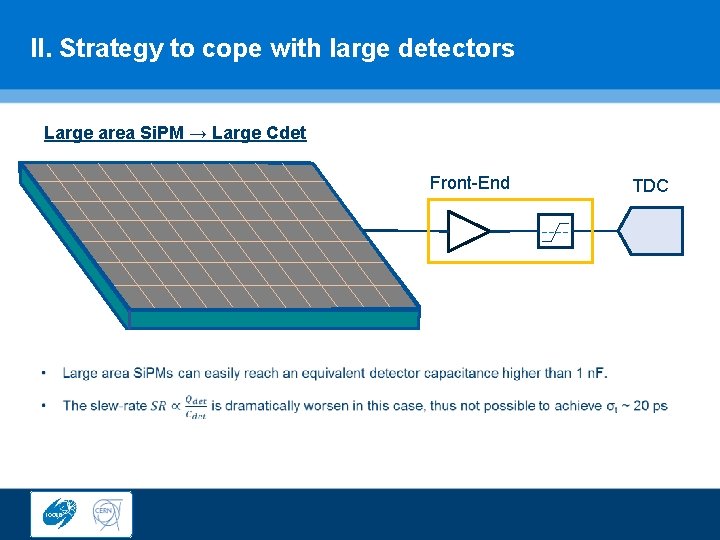

II. Strategy to cope with large detectors Large area Si. PM → Large Cdet Front-End • TDC

II. Strategy to cope with large detectors Smaller Si. PMs to cover same area → Cdet/4 Front-End TDC + m: physical channels = 4 •

III. CONCLUSIONS

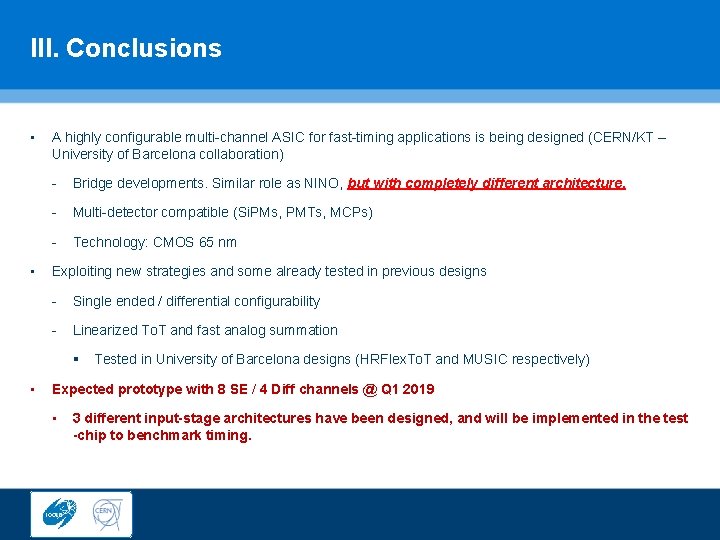

III. Conclusions • • A highly configurable multi-channel ASIC for fast-timing applications is being designed (CERN/KT – University of Barcelona collaboration) - Bridge developments. Similar role as NINO, but with completely different architecture. - Multi-detector compatible (Si. PMs, PMTs, MCPs) - Technology: CMOS 65 nm Exploiting new strategies and some already tested in previous designs - Single ended / differential configurability - Linearized To. T and fast analog summation § • Tested in University of Barcelona designs (HRFlex. To. T and MUSIC respectively) Expected prototype with 8 SE / 4 Diff channels @ Q 1 2019 • 3 different input-stage architectures have been designed, and will be implemented in the test -chip to benchmark timing.

Thanks! Q&A

- Slides: 18