Fast and Accurate Rectilinear Steiner Minimal Tree Algorithm

- Slides: 25

Fast and Accurate Rectilinear Steiner Minimal Tree Algorithm for VLSI Design Chris Chu Iowa State University Yiu-Chung Wong Rio Design Automation

RSMT Problem n Rectilinear Steiner minimal tree (RSMT) problem: n n n Optimal algorithms: n n Griffith et al. [TCAD 94] Batched 1 -Steiner heuristic (BI 1 S) Mandoiu, Vazirani, Ganley [ICCAD-99] Low-complexity algorithms: n n n Hwang, Richards, Winter [ADM 92] Warme, Winter, Zachariasen [AST 00] Geo. Steiner package Near-optimal algorithms: n n Given pin positions, find a rectilinear Steiner tree with minimum WL NP-complete Borah, Owens, Irwin [TCAD 94] Edge-based heuristic, O(n log n) Zhou [ISPD 03] Spanning graph based, O(n log n) Algorithms targeting low-degree nets (VLSI applications): n n Soukup [Proc. IEEE 81] Single Trunk Steiner Tree (STST) Chen et al. [SLIP 02] Refined Single Trunk Tree (RST-T) 2

Overview n A fast and accurate algorithm targeting VLSI applications Based on the FLUTE (Fast Look. Up Table Estimation) idea [ICCAD-04] with three new contributions The new algorithm is still called FLUTE n Handling of low degree nets is extremely well: n n n Optimal and extremely efficient for nets up to 9 pins Still very accurate for nets up to degree 100 So FLUTE is especially suitable for VLSI applications: n Over all 1. 57 million nets in 18 IBM circuits [ISPD 98] n More accurate than Batched 1 -Steiner heuristic n Almost as fast as minimum spanning tree construction 3

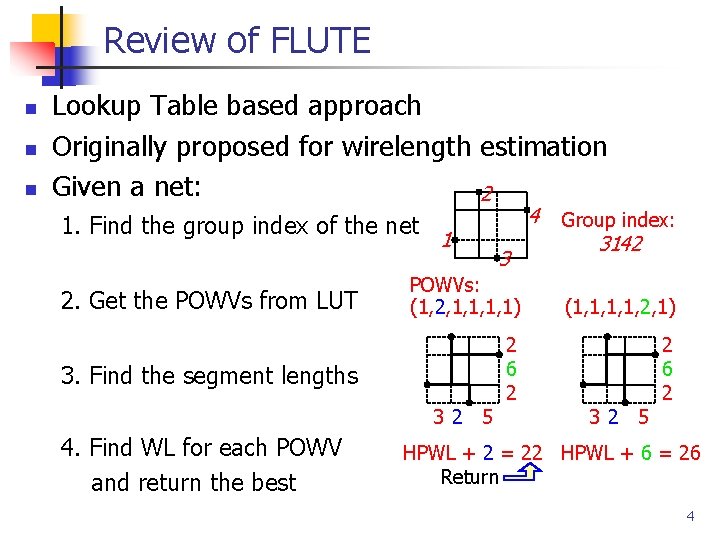

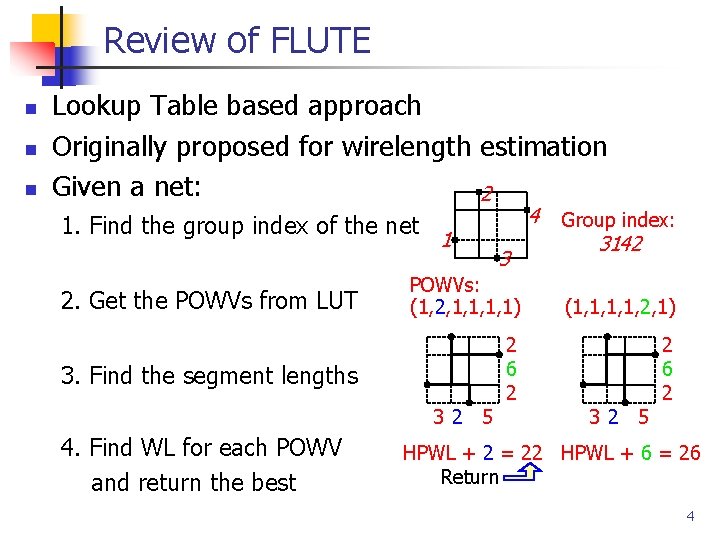

Review of FLUTE n n n Lookup Table based approach Originally proposed for wirelength estimation Given a net: 2 1. Find the group index of the net 1 4 3 Group index: 3142 2. Get the POWVs from LUT POWVs: (1, 2, 1, 1) (1, 1, 2, 1) 3. Find the segment lengths 2 6 2 3 2 5 4. Find WL for each POWV and return the best 3 2 5 HPWL + 2 = 22 HPWL + 6 = 26 Return 4

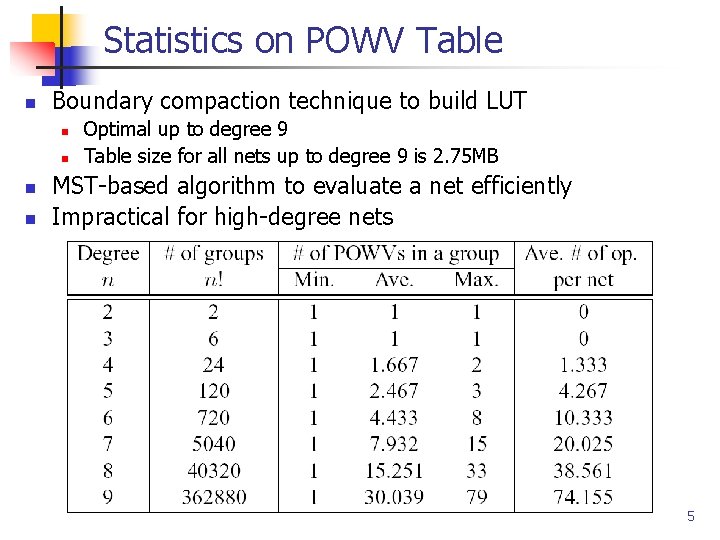

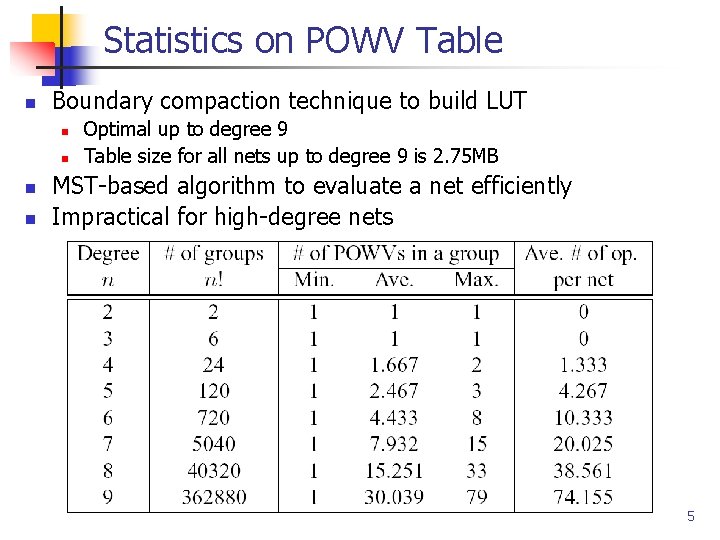

Statistics on POWV Table n Boundary compaction technique to build LUT n n Optimal up to degree 9 Table size for all nets up to degree 9 is 2. 75 MB MST-based algorithm to evaluate a net efficiently Impractical for high-degree nets 5

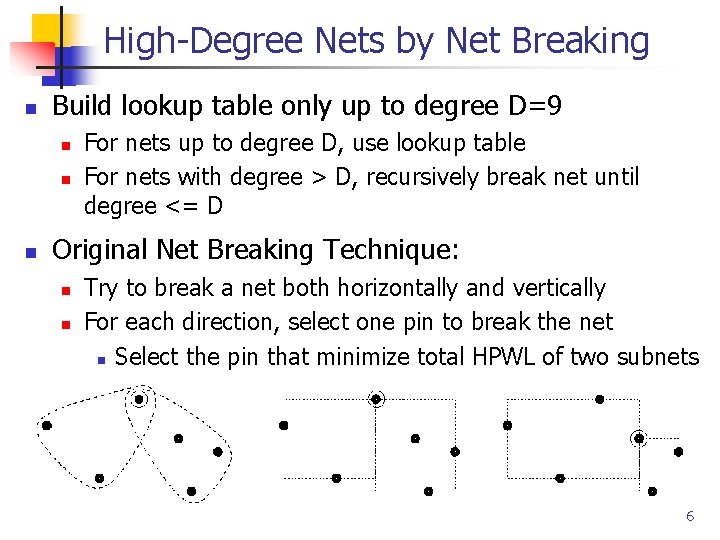

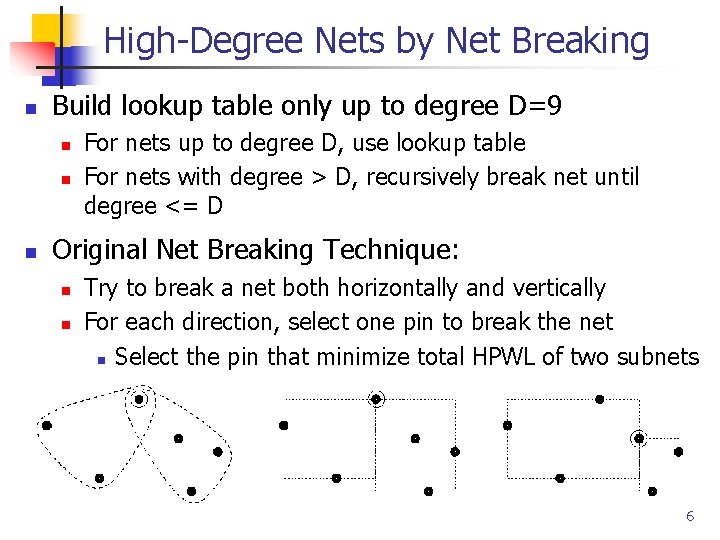

High-Degree Nets by Net Breaking n Build lookup table only up to degree D=9 n n n For nets up to degree D, use lookup table For nets with degree > D, recursively break net until degree <= D Original Net Breaking Technique: n n Try to break a net both horizontally and vertically For each direction, select one pin to break the net n Select the pin that minimize total HPWL of two subnets 6

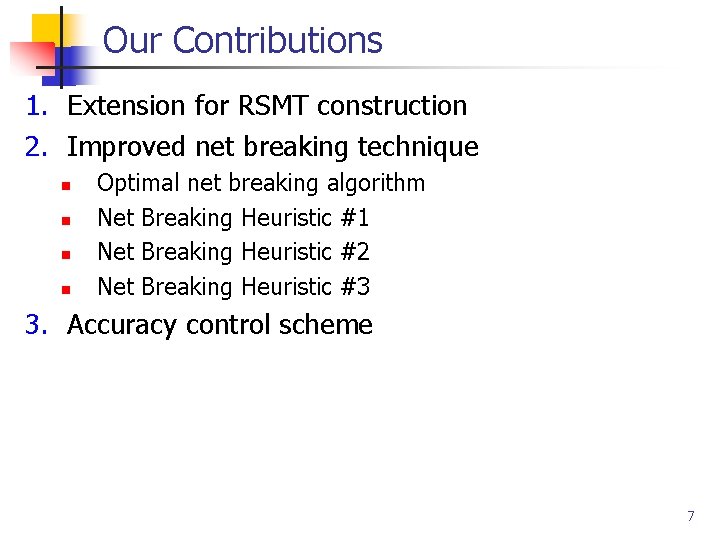

Our Contributions 1. Extension for RSMT construction 2. Improved net breaking technique n n Optimal net breaking algorithm Net Breaking Heuristic #1 Net Breaking Heuristic #2 Net Breaking Heuristic #3 3. Accuracy control scheme 7

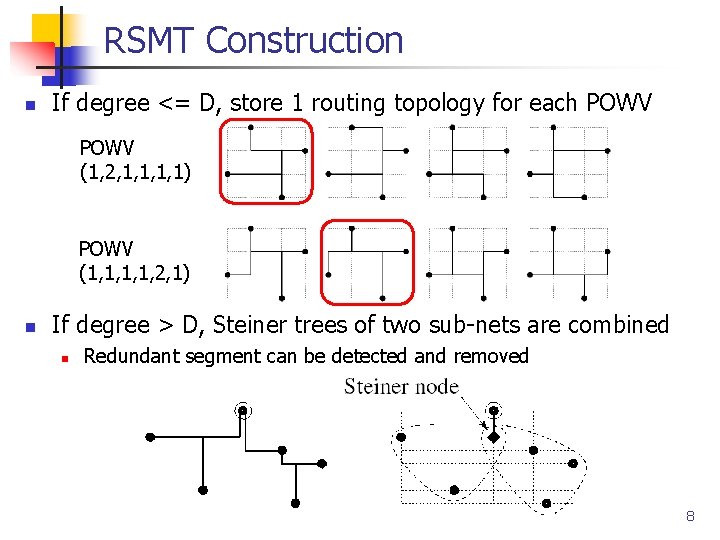

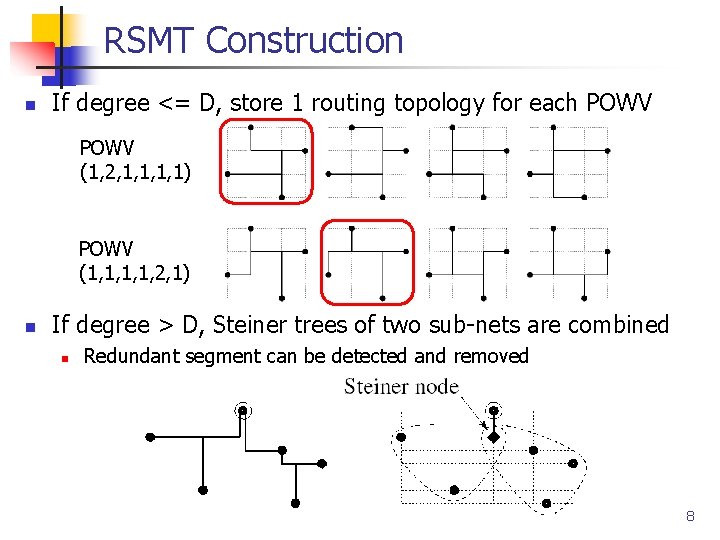

RSMT Construction n If degree <= D, store 1 routing topology for each POWV (1, 2, 1, 1) POWV (1, 1, 2, 1) n If degree > D, Steiner trees of two sub-nets are combined n Redundant segment can be detected and removed 8

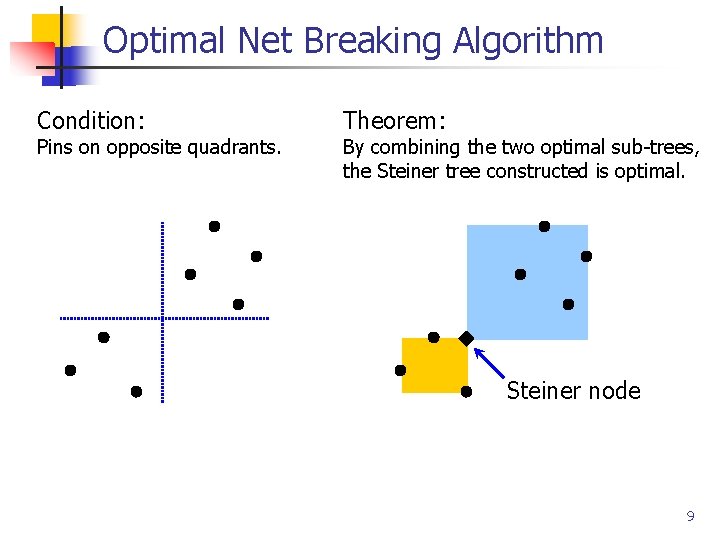

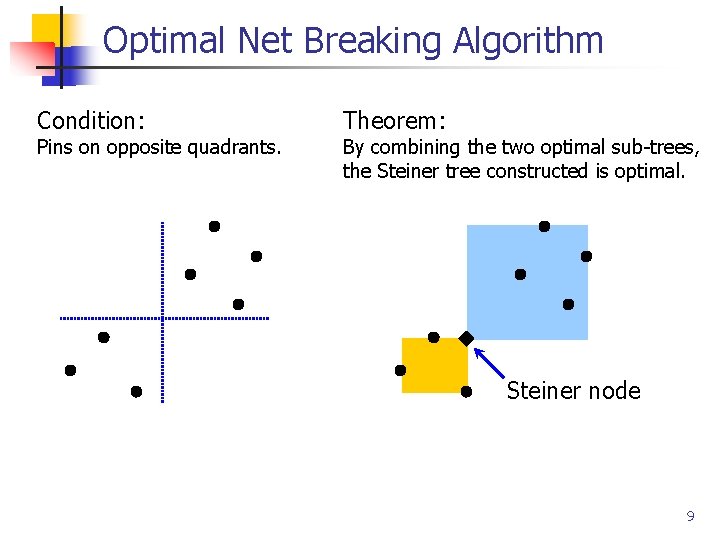

Optimal Net Breaking Algorithm Condition: Pins on opposite quadrants. Theorem: By combining the two optimal sub-trees, the Steiner tree constructed is optimal. Steiner node 9

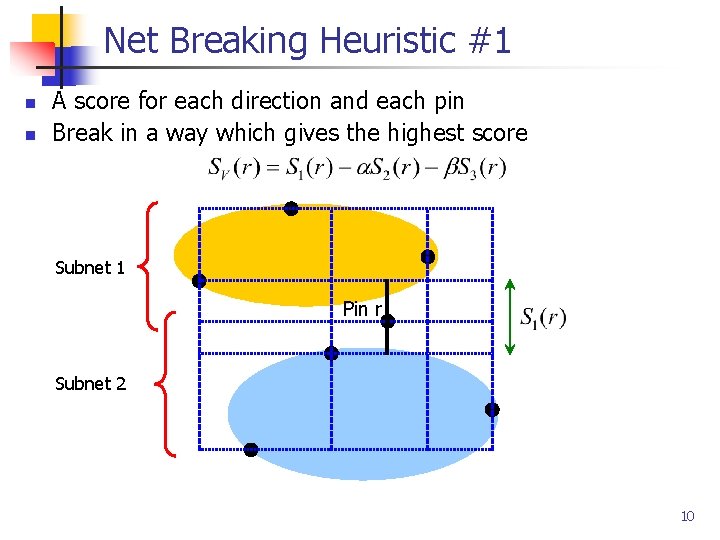

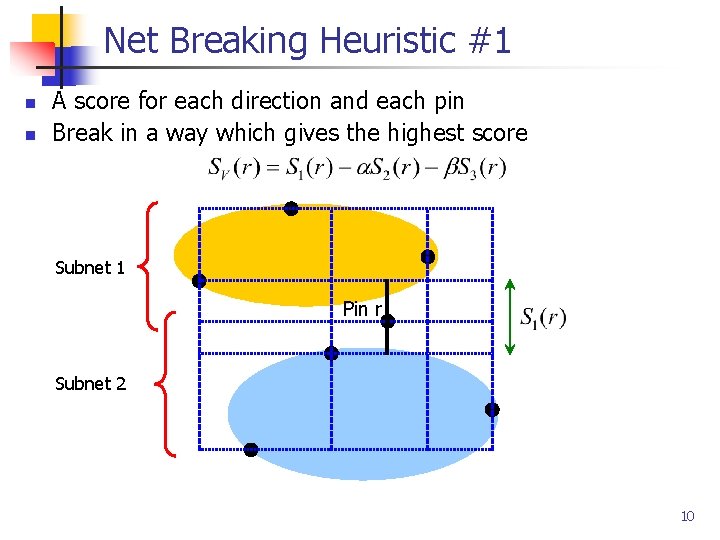

Net Breaking Heuristic #1 n n A score for each direction and each pin Break in a way which gives the highest score Subnet 1 Pin r Subnet 2 10

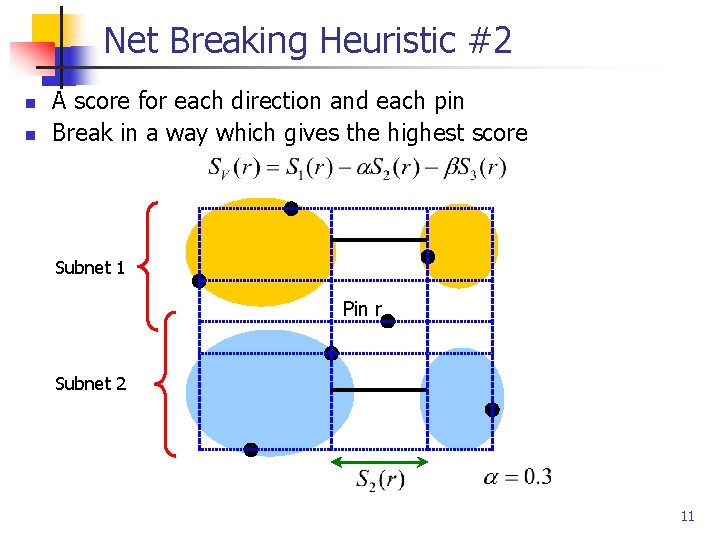

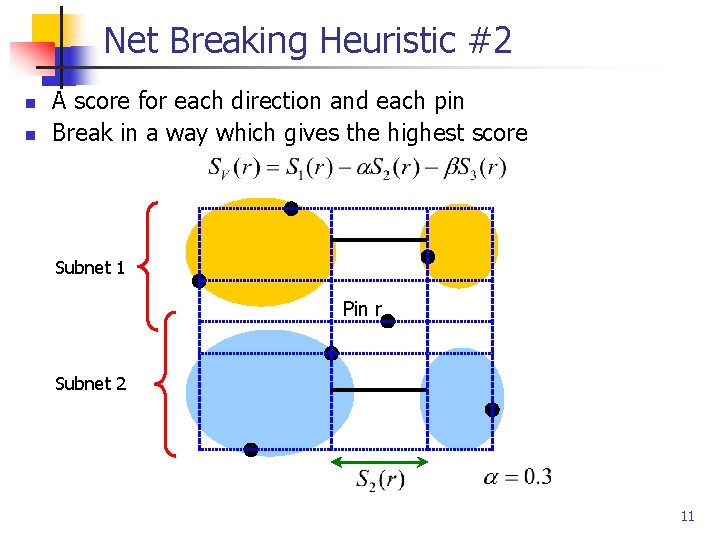

Net Breaking Heuristic #2 n n A score for each direction and each pin Break in a way which gives the highest score Subnet 1 Pin r Subnet 2 11

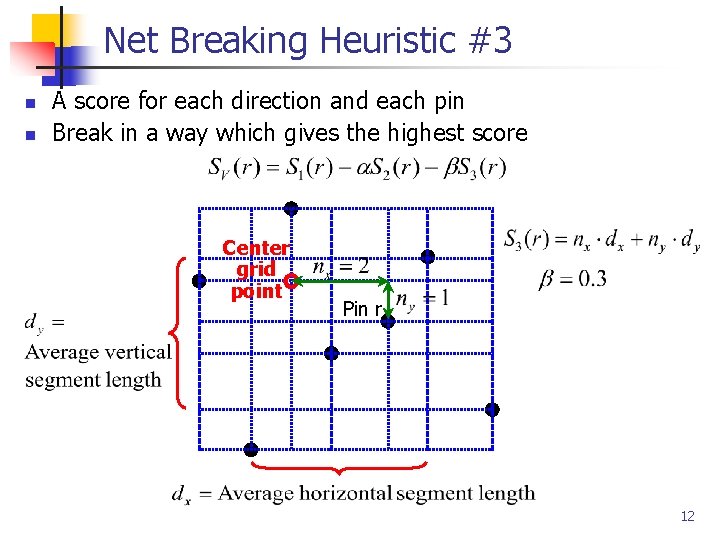

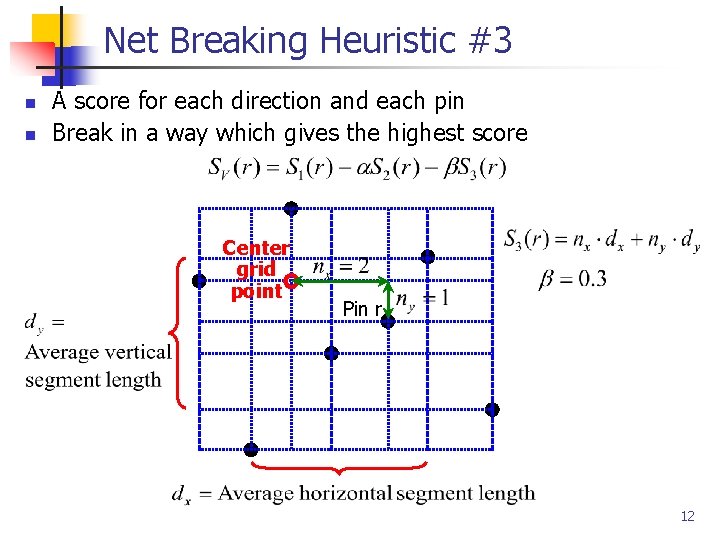

Net Breaking Heuristic #3 n n A score for each direction and each pin Break in a way which gives the highest score Center grid point Pin r 12

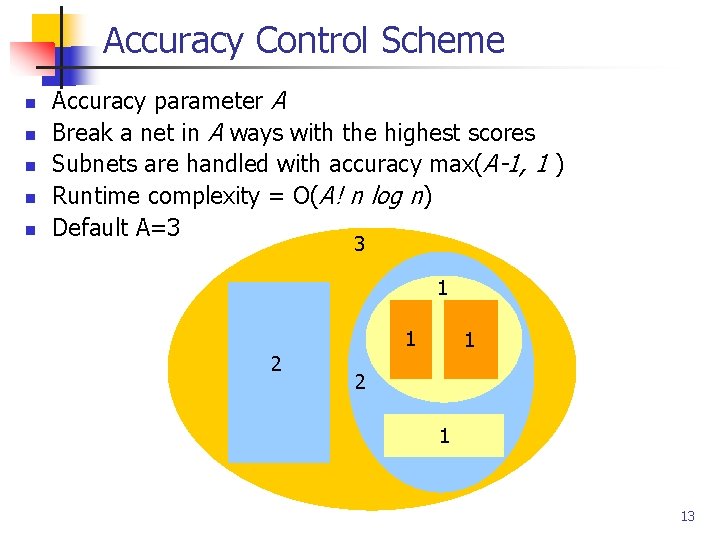

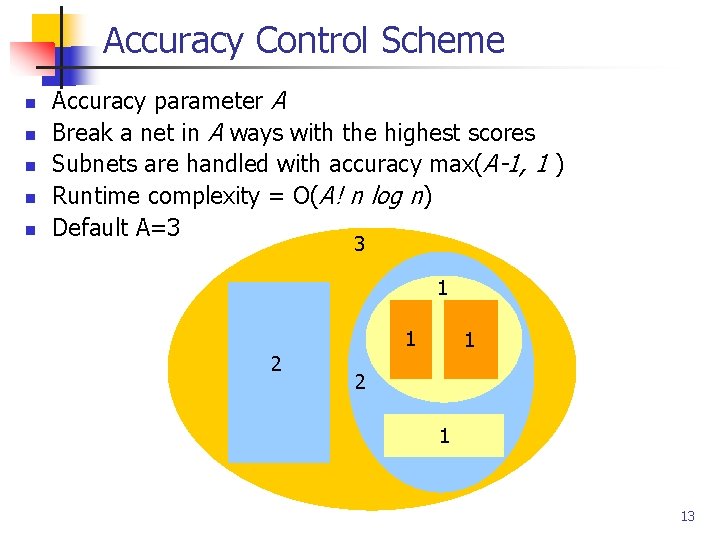

Accuracy Control Scheme n n n Accuracy parameter A Break a net in A ways with the highest scores Subnets are handled with accuracy max(A-1, 1 ) Runtime complexity = O(A! n log n) Default A=3 3 1 1 2 1 13

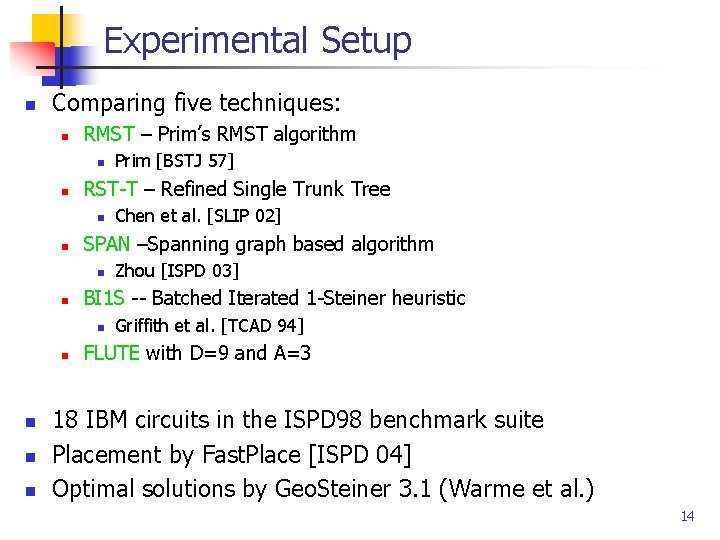

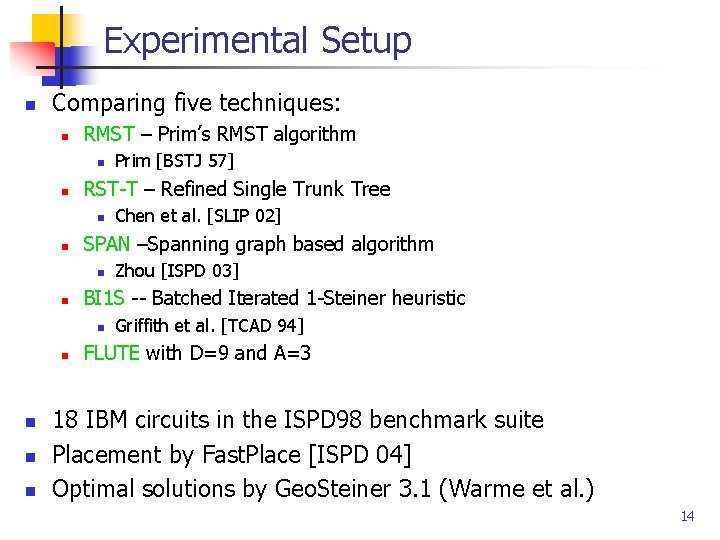

Experimental Setup n Comparing five techniques: n RMST – Prim’s RMST algorithm n n RST-T – Refined Single Trunk Tree n n n Zhou [ISPD 03] BI 1 S -- Batched Iterated 1 -Steiner heuristic n n Chen et al. [SLIP 02] SPAN –Spanning graph based algorithm n n Prim [BSTJ 57] Griffith et al. [TCAD 94] FLUTE with D=9 and A=3 18 IBM circuits in the ISPD 98 benchmark suite Placement by Fast. Place [ISPD 04] Optimal solutions by Geo. Steiner 3. 1 (Warme et al. ) 14

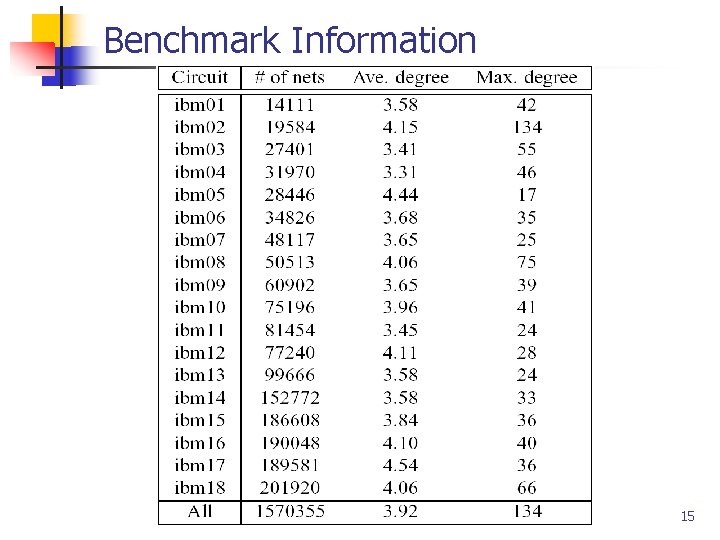

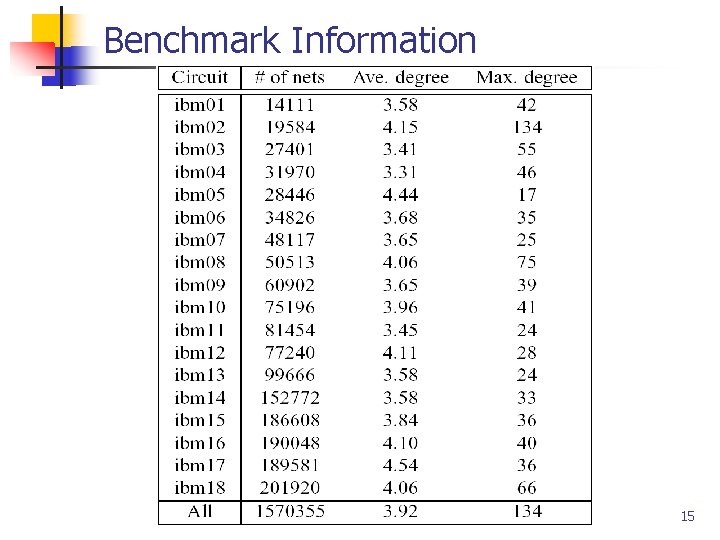

Benchmark Information 15

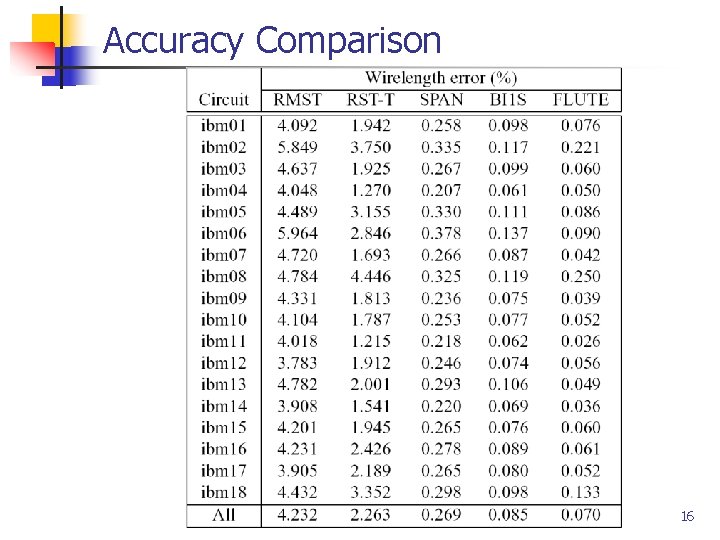

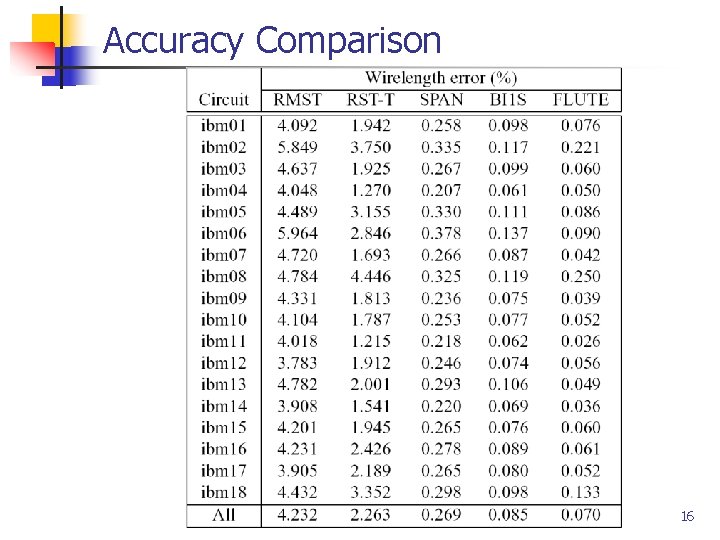

Accuracy Comparison 16

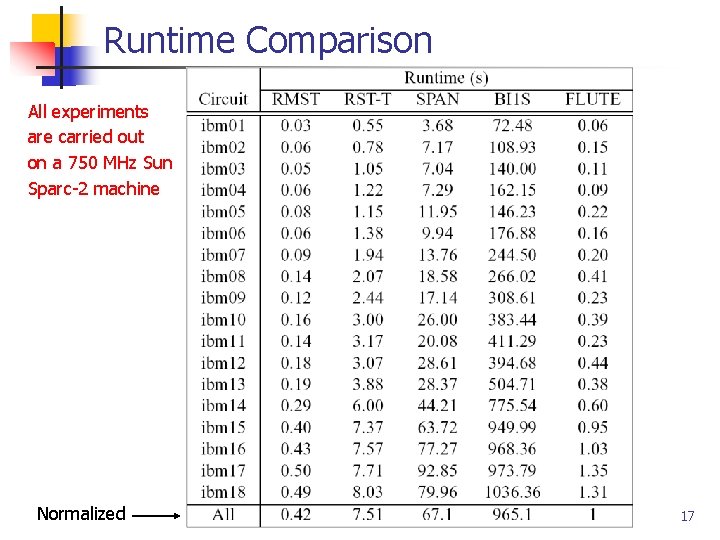

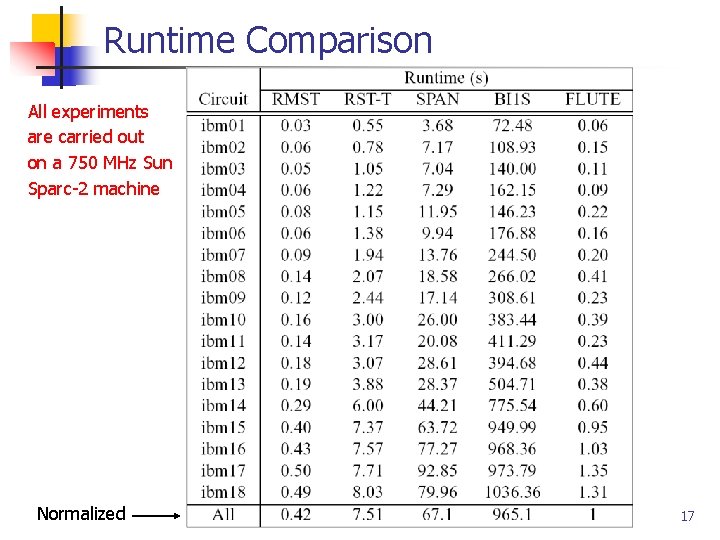

Runtime Comparison All experiments are carried out on a 750 MHz Sun Sparc-2 machine Normalized 17

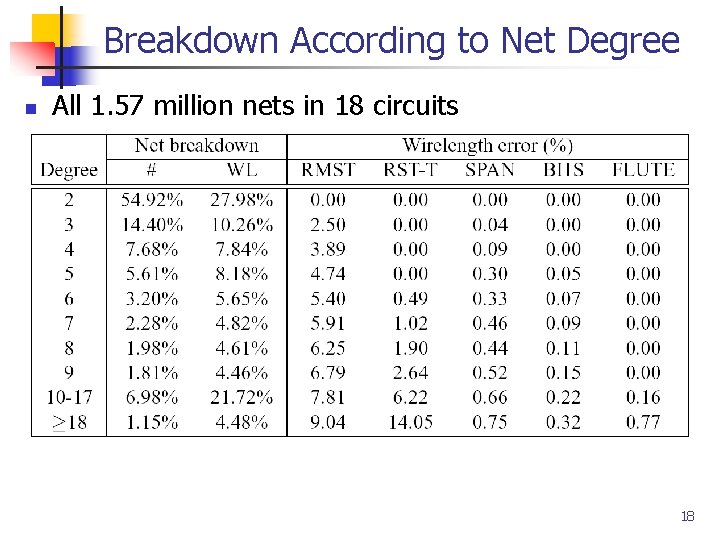

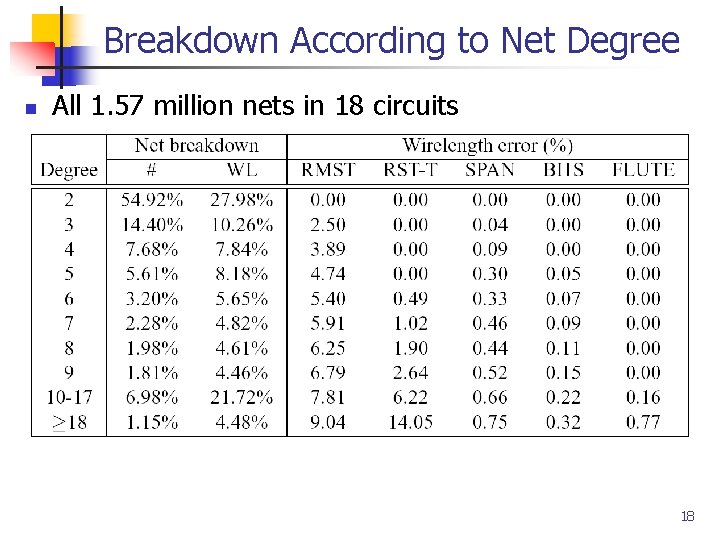

Breakdown According to Net Degree n All 1. 57 million nets in 18 circuits 18

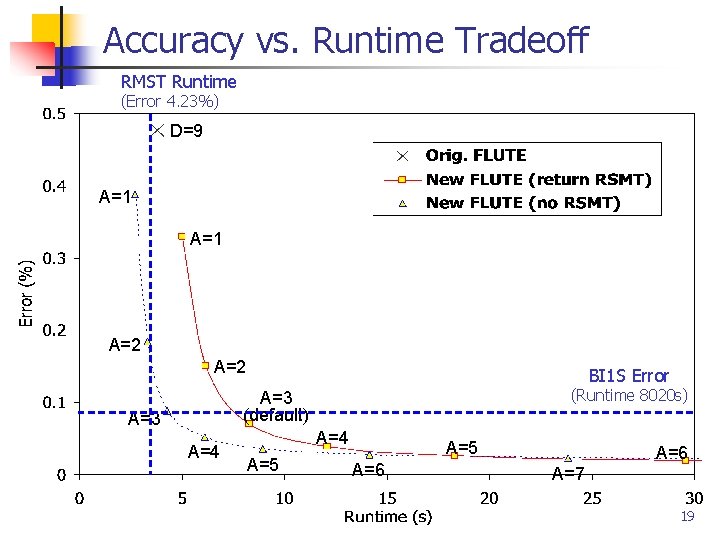

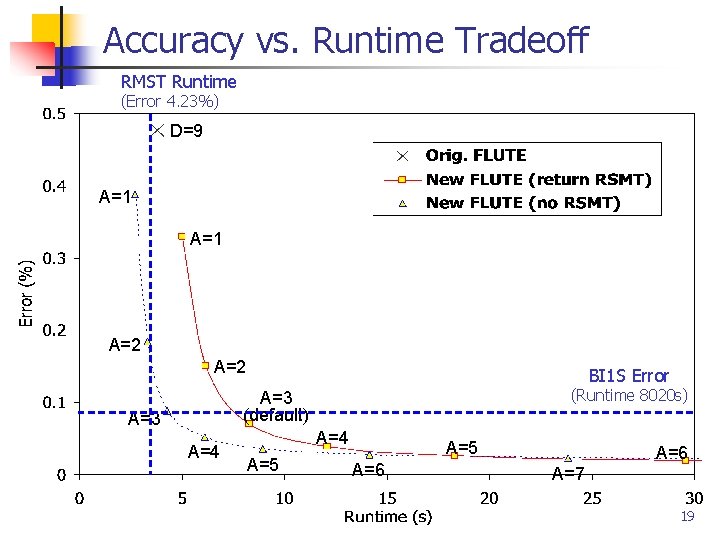

Accuracy vs. Runtime Tradeoff RMST Runtime (Error 4. 23%) D=9 A=1 A=2 BI 1 S Error (Runtime 8020 s) A=3 (default) A=3 A=4 A=5 A=6 A=7 19

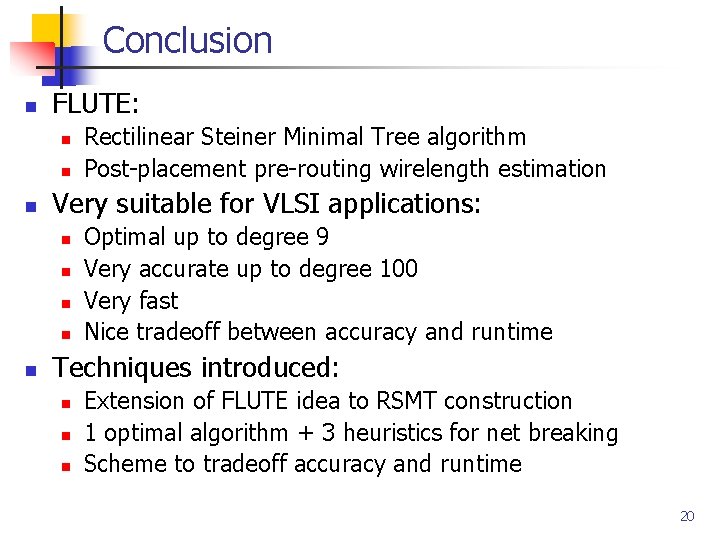

Conclusion n FLUTE: n n n Very suitable for VLSI applications: n n n Rectilinear Steiner Minimal Tree algorithm Post-placement pre-routing wirelength estimation Optimal up to degree 9 Very accurate up to degree 100 Very fast Nice tradeoff between accuracy and runtime Techniques introduced: n n n Extension of FLUTE idea to RSMT construction 1 optimal algorithm + 3 heuristics for net breaking Scheme to tradeoff accuracy and runtime 20

Future Works n n n Better technique to handle high-degree nets RSMT construction with obstacles Extend to timing-driven Steiner tree construction « Source code available in GSRC Bookshelf: http: //vlsicad. eecs. umich. edu/BK/slots (Rectilinear Spanning and Steiner tree slot) 21

Thank You

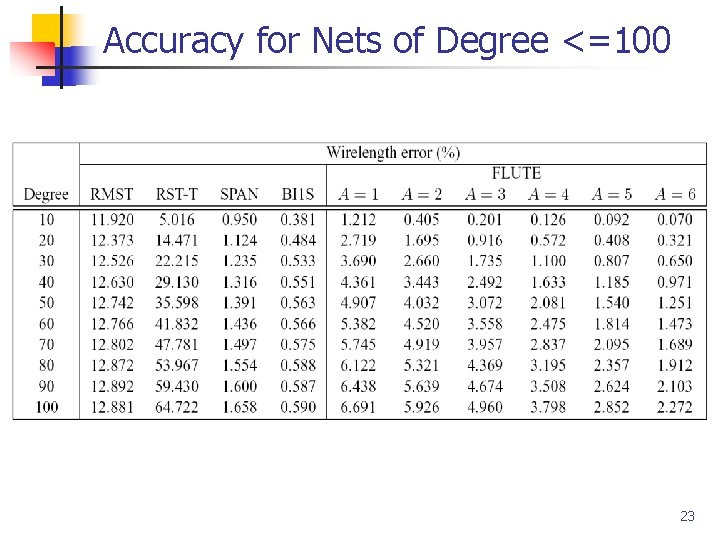

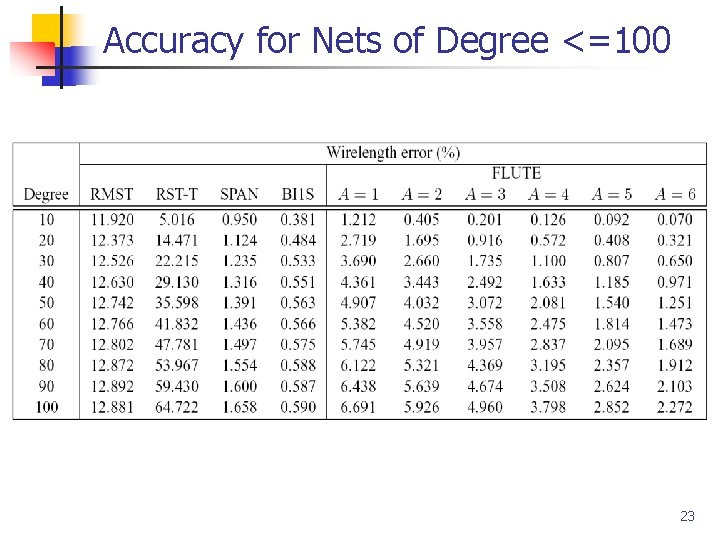

Accuracy for Nets of Degree <=100 23

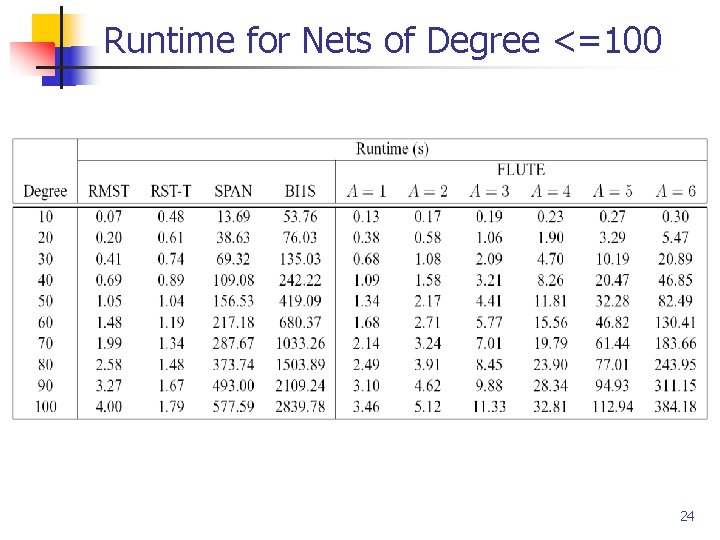

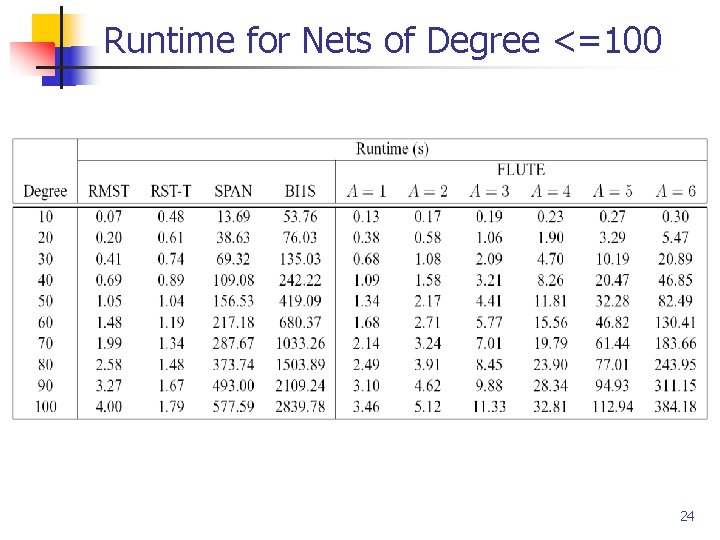

Runtime for Nets of Degree <=100 24

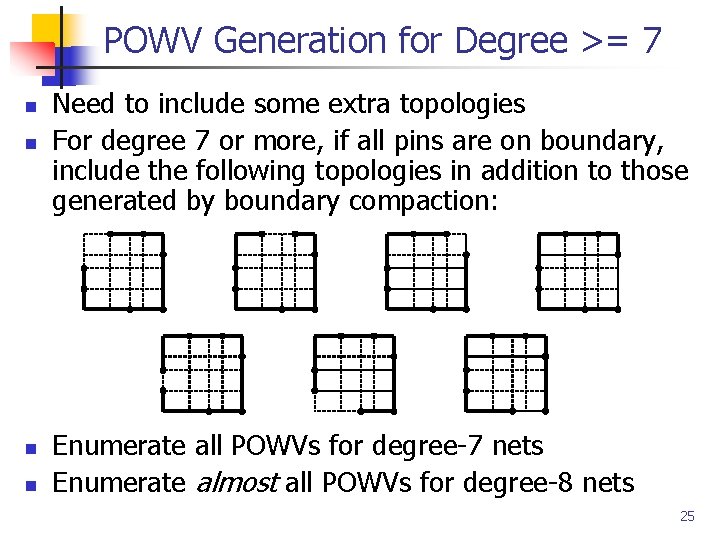

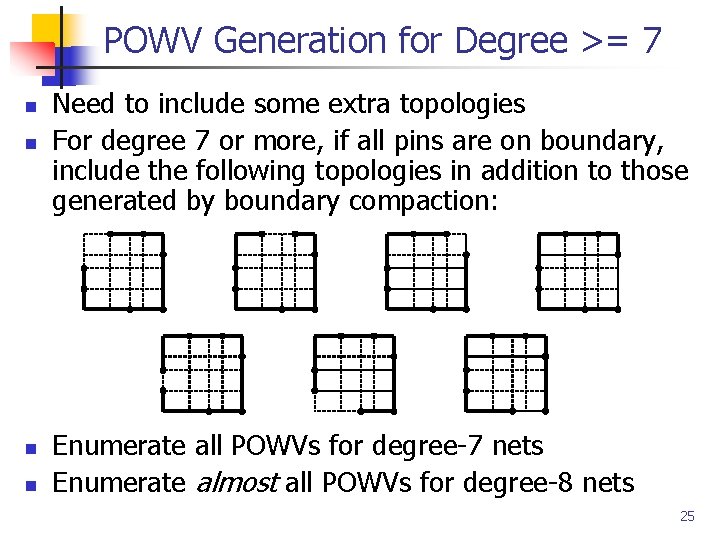

POWV Generation for Degree >= 7 n n Need to include some extra topologies For degree 7 or more, if all pins are on boundary, include the following topologies in addition to those generated by boundary compaction: Enumerate all POWVs for degree-7 nets Enumerate almost all POWVs for degree-8 nets 25