FailSafe Module for Unmanned Autonomous Vehicle CMPE 450490

- Slides: 11

Fail-Safe Module for Unmanned Autonomous Vehicle CMPE 450/490 Project Presentation Presenters: Lai Nguyen, Jesse Xi Chen

Overview • Introduction • Theory of Operation • Hardware • Software • Complications • Future Improvement • Demonstration • Reference

Introduction • University of Alberta Aerial Robotics • Group (UAARG) Current Fail-Safe Module – Simple – Need specialized microcontroller • Objective – – – Improve reliability Adding features Integrate different features onto one chip

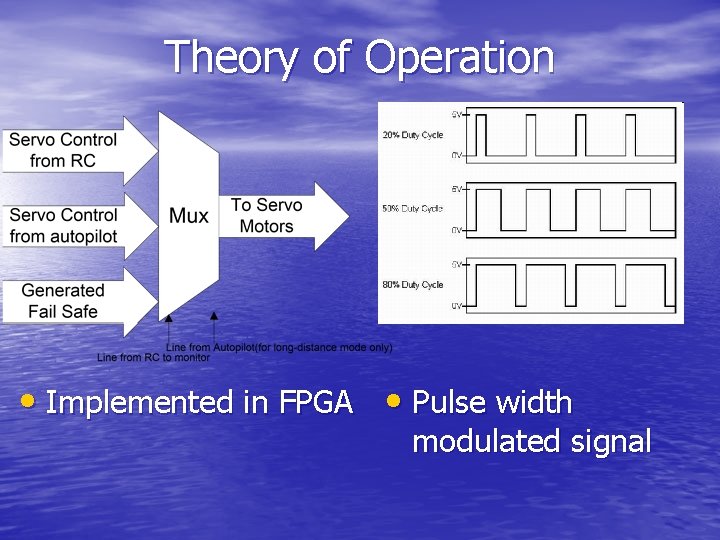

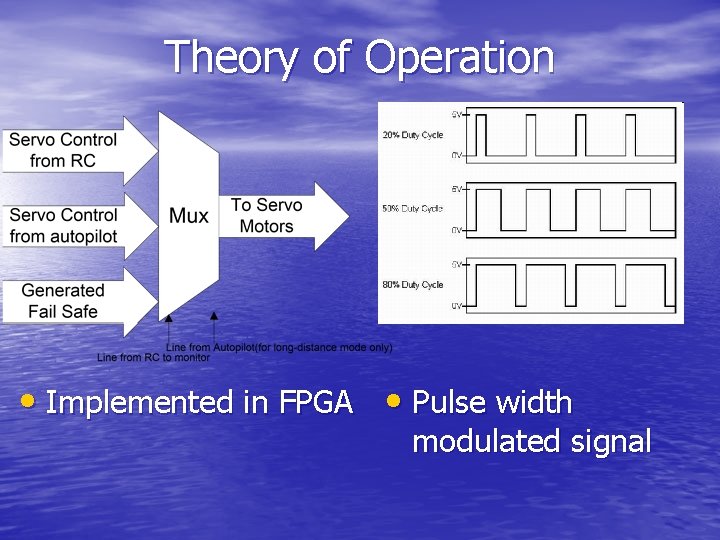

Theory of Operation • Implemented in FPGA • Pulse width modulated signal

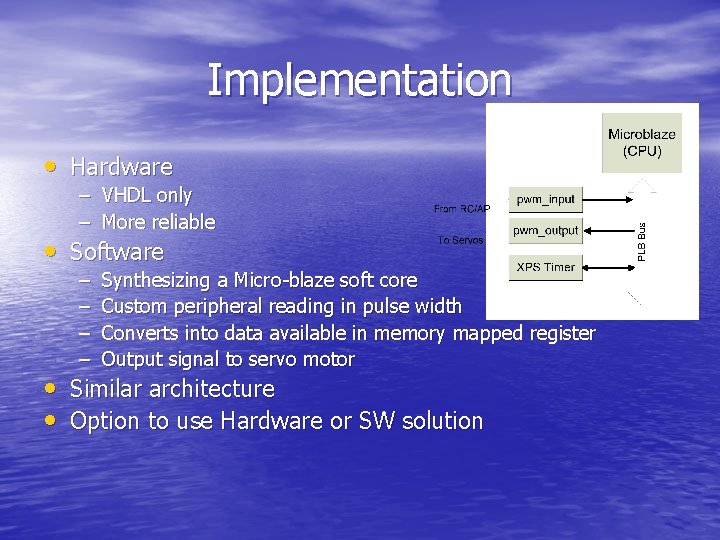

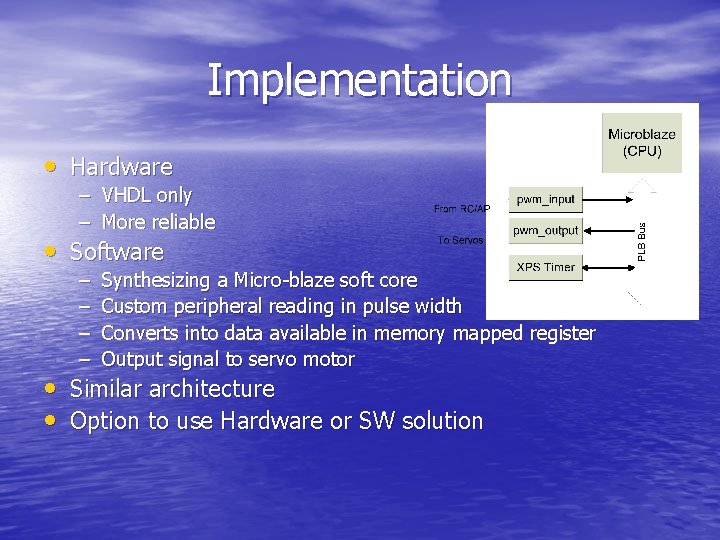

Implementation • Hardware – VHDL only – More reliable • Software – – Synthesizing a Micro-blaze soft core Custom peripheral reading in pulse width Converts into data available in memory mapped register Output signal to servo motor • Similar architecture • Option to use Hardware or SW solution

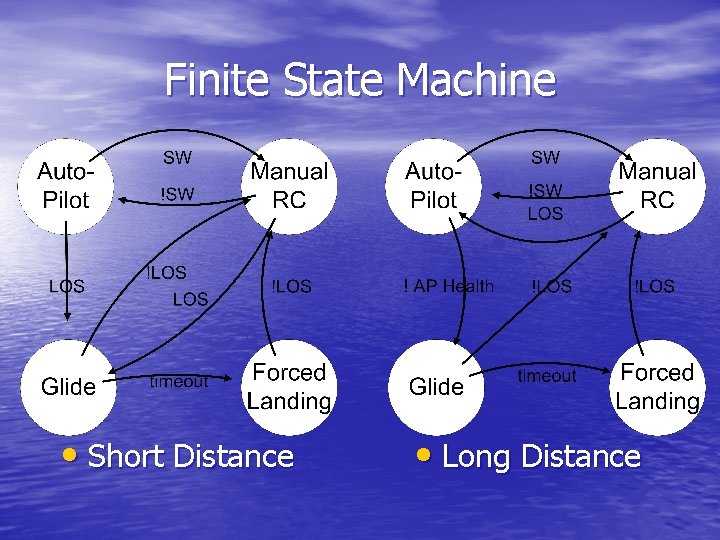

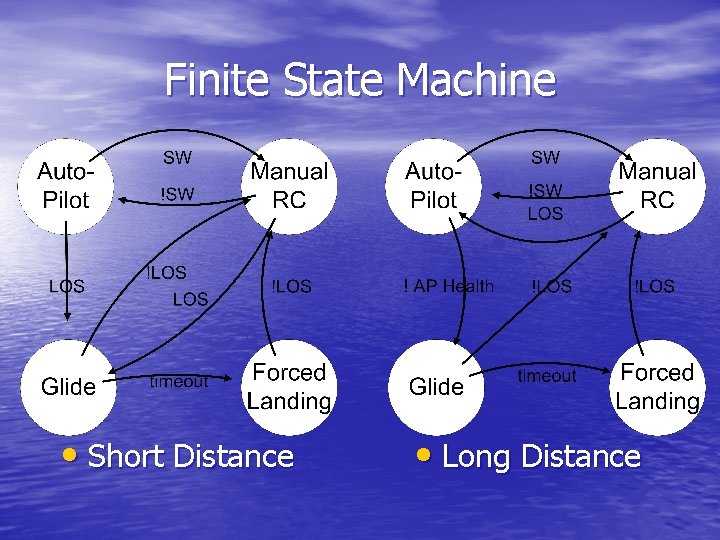

Finite State Machine • Short Distance • Long Distance

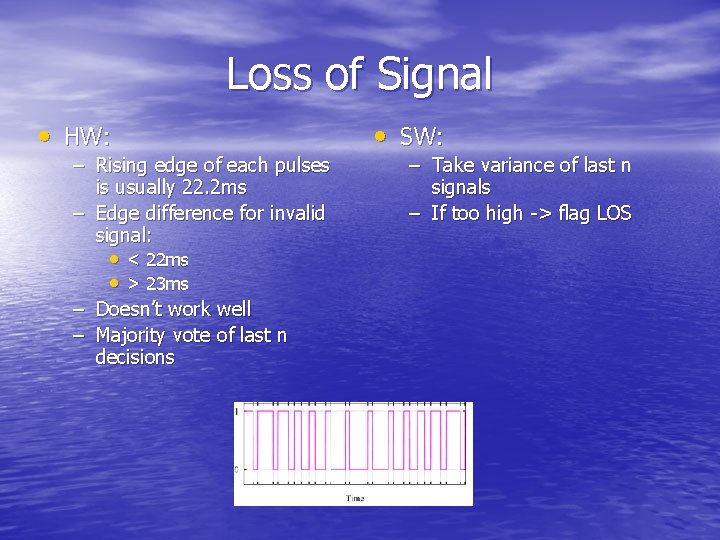

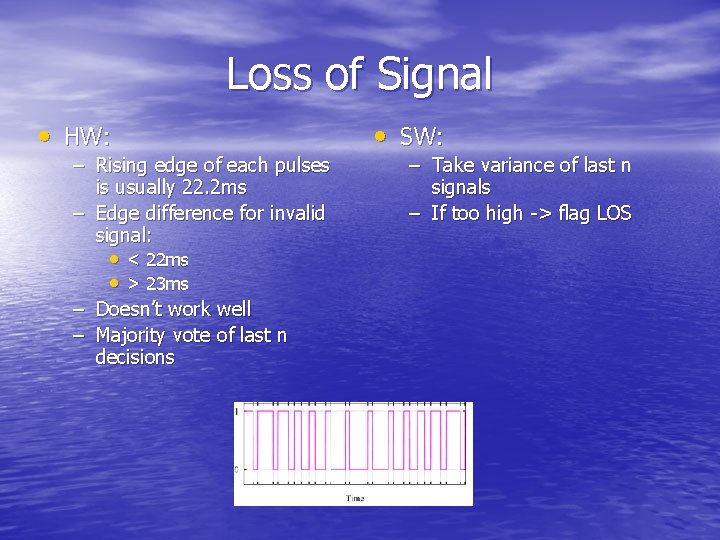

Loss of Signal • HW: – Rising edge of each pulses is usually 22. 2 ms – Edge difference for invalid signal: • < 22 ms • > 23 ms – Doesn’t work well – Majority vote of last n decisions • SW: – Take variance of last n signals – If too high -> flag LOS

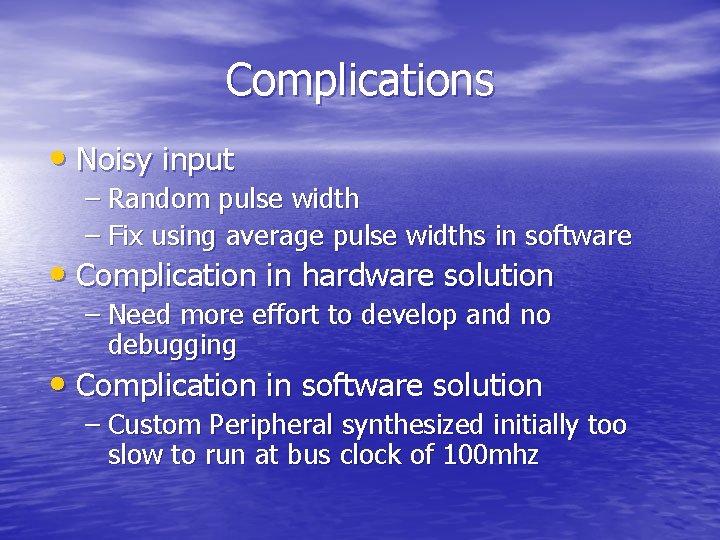

Complications • Noisy input – Random pulse width – Fix using average pulse widths in software • Complication in hardware solution – Need more effort to develop and no debugging • Complication in software solution – Custom Peripheral synthesized initially too slow to run at bus clock of 100 mhz

Future Improvements • • Create schematics design and move the module onto PCB – Put the module onto Spartan board Make module more configurable – – Change mode of operation using jumper Change software/hardware implementation using jumper Change to Hardware implementation when exception encountered from Software implementation Improved pulse width detection

Reference • UAARG: http: //www. ece. ualberta. ca/~uaarg/UAARGV 3/i ndex 2. html • Xilinx: http: //www. xilinx. com/ • Application notes: http: //www. ece. ualberta. ca/~elliott/cmpe 490/a ppnotes/

Demonstration • RC Control mode • Auto-Pilot Mode • Gliding • Crash