Faculty of Computer Science Buses and Memories And

Faculty of Computer Science Buses and Memories And Adders Add footer here 6/6/2021 © 2006

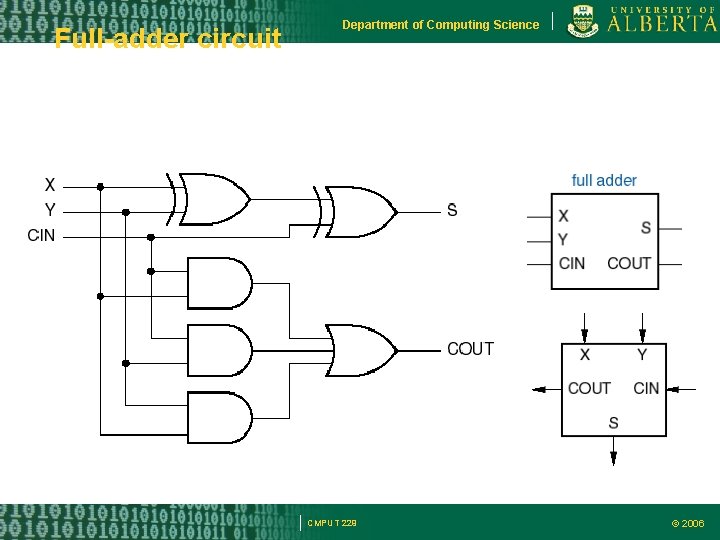

Department of Computing Science Adders Basic building block is “full adder” – 1 -bit-wide adder, produces sum and carry outputs Cout is one if two or more of the inputs are one. S is one if an odd number of inputs are one. CMPUT 229 © 2006

Full-adder circuit Department of Computing Science CMPUT 229 © 2006

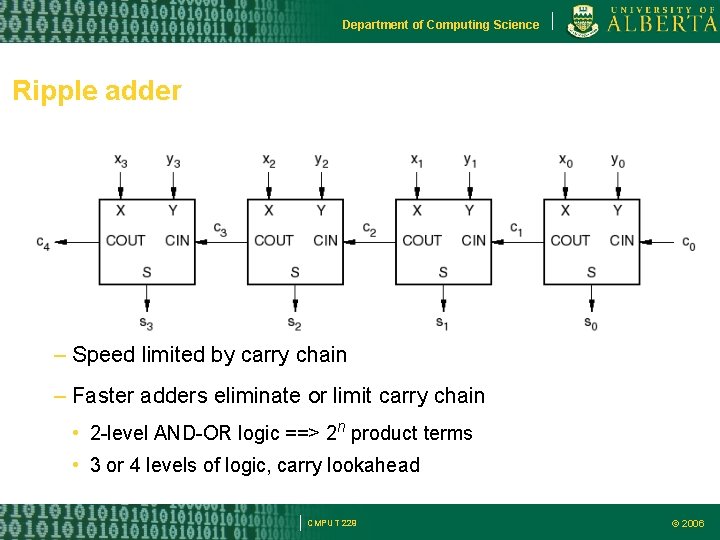

Department of Computing Science Ripple adder – Speed limited by carry chain – Faster adders eliminate or limit carry chain • 2 -level AND-OR logic ==> 2 n product terms • 3 or 4 levels of logic, carry lookahead CMPUT 229 © 2006

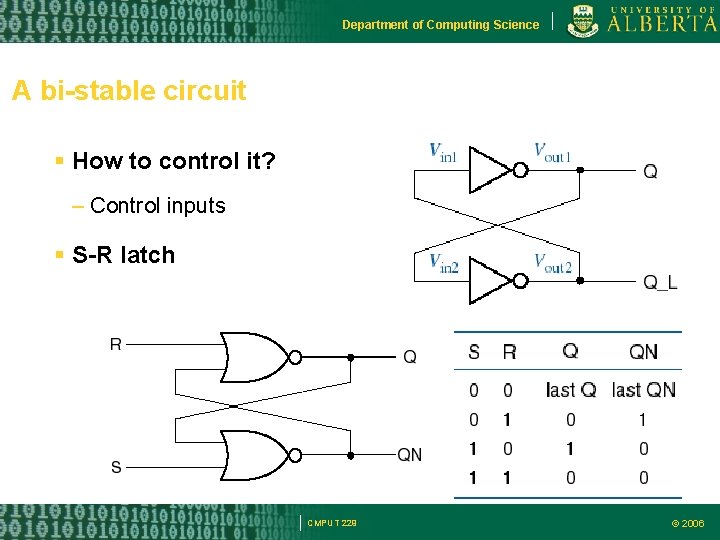

Department of Computing Science A bi-stable circuit How to control it? – Control inputs S-R latch CMPUT 229 © 2006

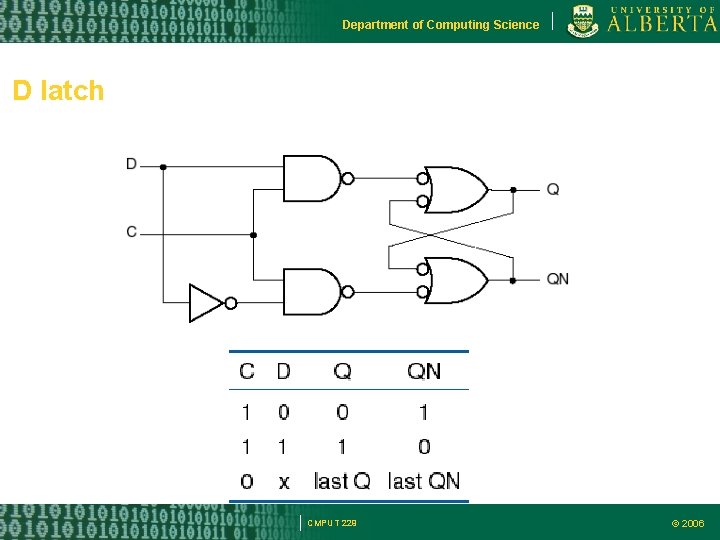

Department of Computing Science D latch CMPUT 229 © 2006

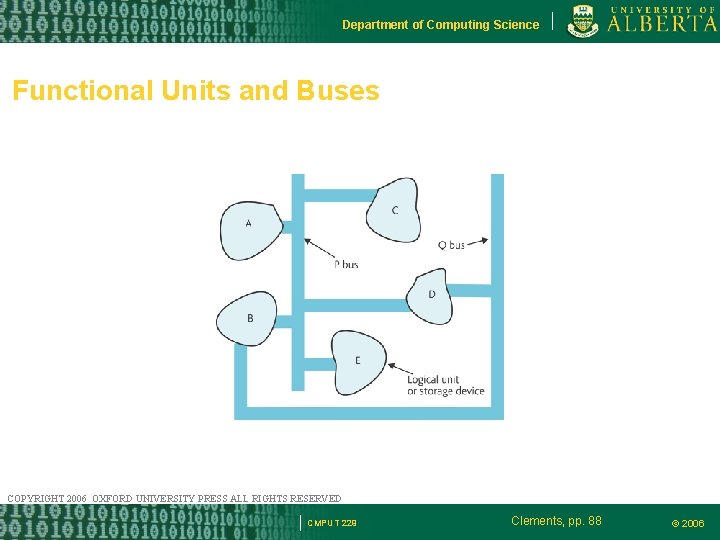

Department of Computing Science Functional Units and Buses COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 88 © 2006

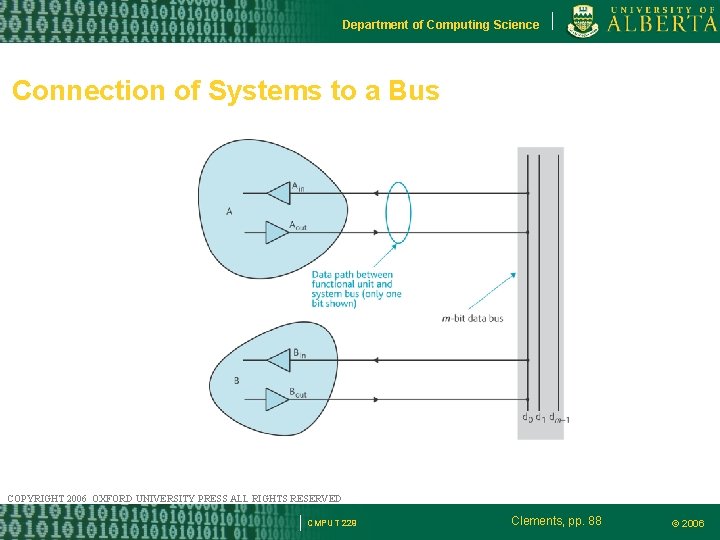

Department of Computing Science Connection of Systems to a Bus COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 88 © 2006

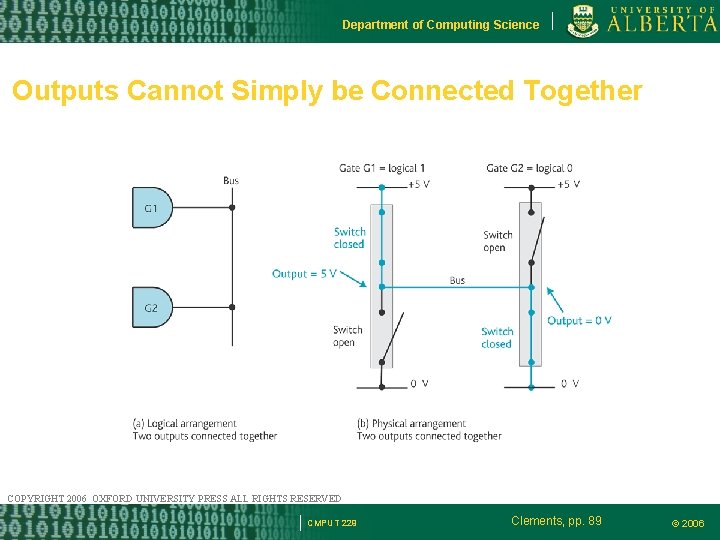

Department of Computing Science Outputs Cannot Simply be Connected Together COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 89 © 2006

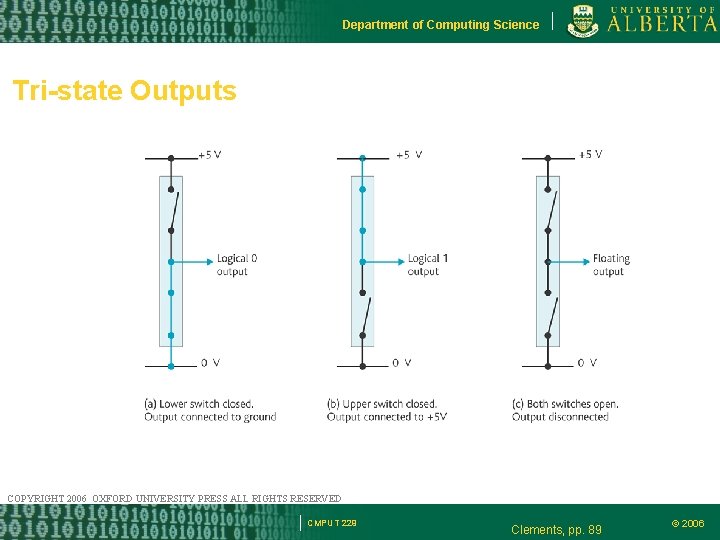

Department of Computing Science Tri-state Outputs COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 89 © 2006

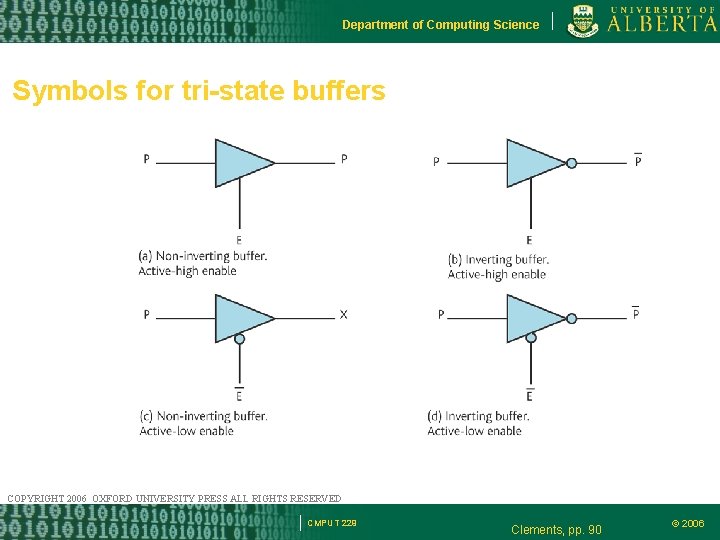

Department of Computing Science Symbols for tri-state buffers COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 90 © 2006

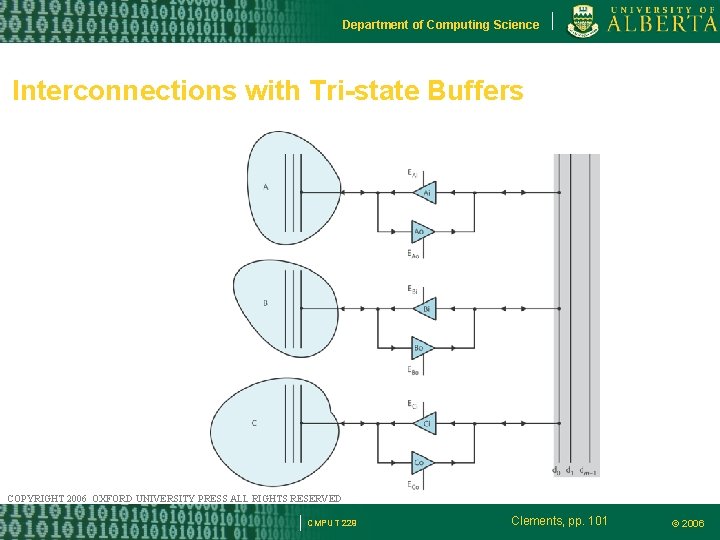

Department of Computing Science Interconnections with Tri-state Buffers COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 101 © 2006

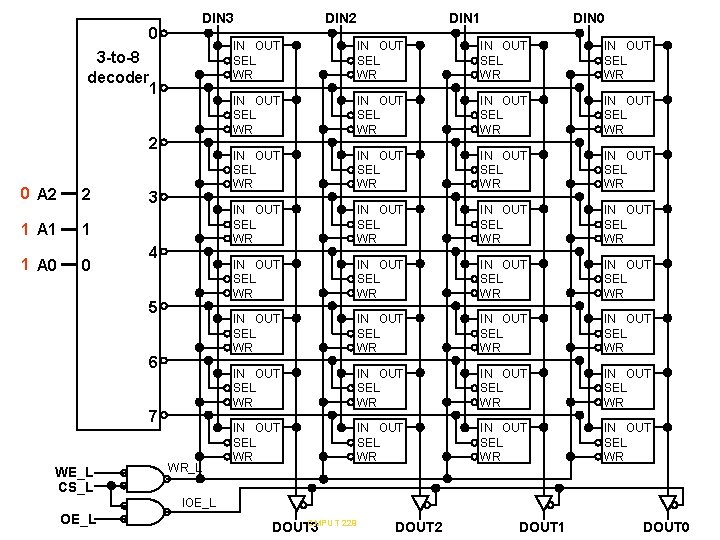

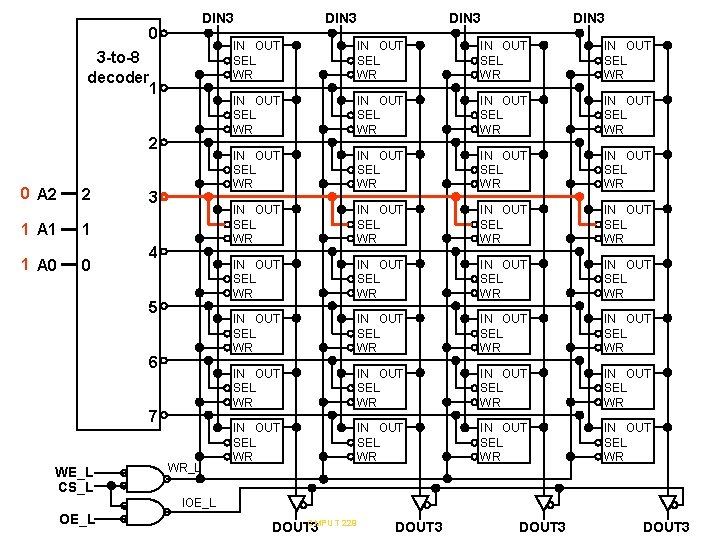

DIN 3 0 3 -to-8 decoder 1 2 0 A 2 2 1 A 1 1 1 A 0 0 3 4 5 6 7 WE_L CS_L WR_L DIN 2 DIN 1 DIN 0 IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IOE_L CMPUT 229 DOUT 3 DOUT 2 DOUT 1 DOUT 0

DIN 3 0 3 -to-8 decoder 1 2 0 A 2 2 1 A 1 1 1 A 0 0 3 4 5 6 7 WE_L CS_L WR_L DIN 3 IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IOE_L CMPUT 229 DOUT 3

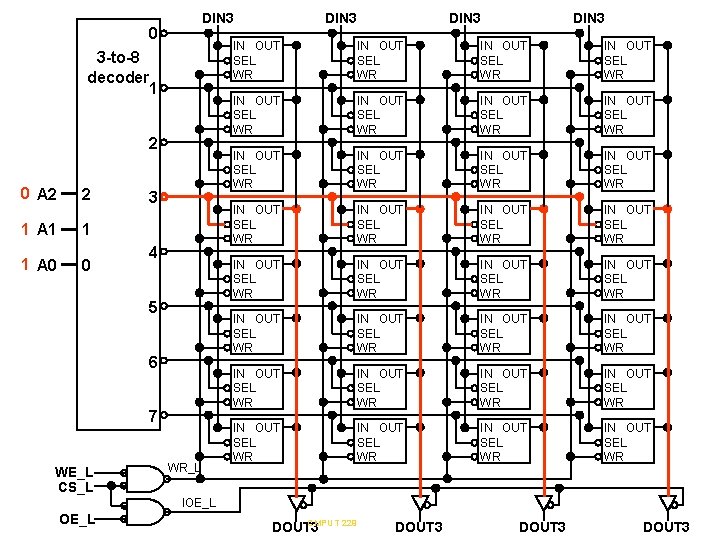

DIN 3 0 3 -to-8 decoder 1 2 0 A 2 2 1 A 1 1 1 A 0 0 3 4 5 6 7 WE_L CS_L WR_L DIN 3 IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IOE_L CMPUT 229 DOUT 3

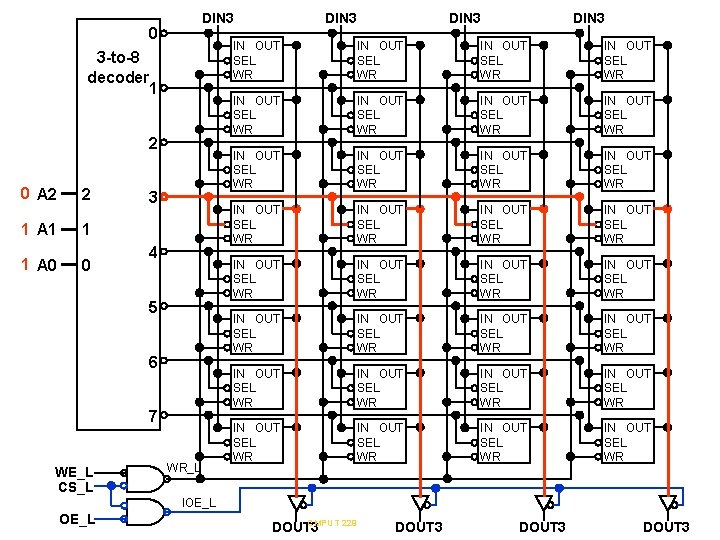

DIN 3 0 3 -to-8 decoder 1 2 0 A 2 2 1 A 1 1 1 A 0 0 3 4 5 6 7 WE_L CS_L WR_L DIN 3 IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IN OUT SEL WR IOE_L CMPUT 229 DOUT 3

- Slides: 16