Faculty of Computer Science Assembly Language Programming Control

Faculty of Computer Science Assembly Language Programming Control Flow, Endianess and Registers Add footer here 1/9/2022 © 2006

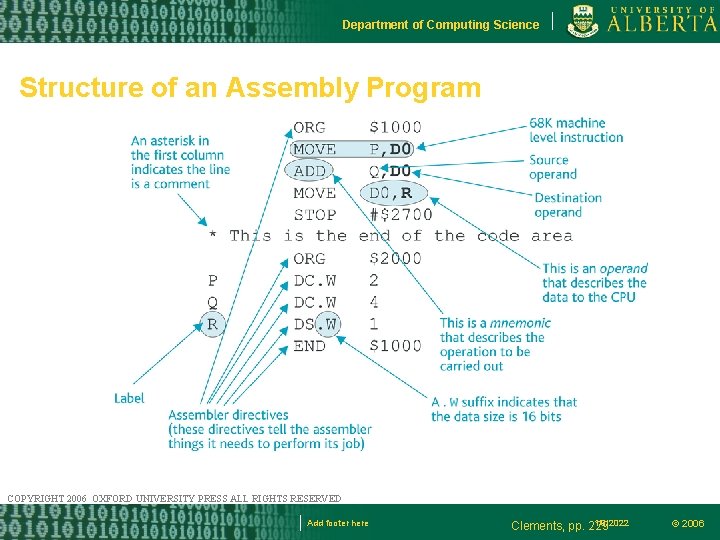

Department of Computing Science Structure of an Assembly Program COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here 1/9/2022 Clements, pp. 229 © 2006

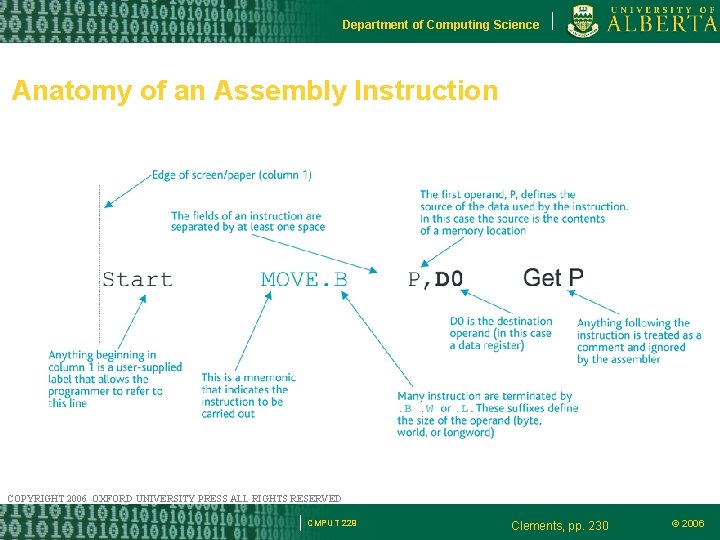

Department of Computing Science Anatomy of an Assembly Instruction COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 230 © 2006

Department of Computing Science Assembling a Program COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 231 © 2006

Department of Computing Science Define Constant Assembly Directive COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 232 © 2006

Department of Computing Science Easy 68 K Simulator See box on page 234 for a list of common beginner’s errors. COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 233 © 2006

Department of Computing Science Unconditional Branch COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 223 1/9/2022 © 2006

Department of Computing Science Conditional Branch COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 224 1/9/2022 © 2006

Department of Computing Science 68 K’s Conditional Branches Mnemonic Condition Flags BEQ Equal Z=1 BNE Not equal Z=0 BCS/BHS Carry set/higher or same C=1 BCC/BLO Carry clear/lower C=0 BMI negative N=1 BPL Positive or zero N=0 BVS Overflow set V=1 BVC Overflow clear V=0 BHI Higher than (signed) (C=1)^(Z=0) BLS Lower or same (signed) (C=0)v(Z=1) BGE Greater than or equal (signed) N=V BLT Less than (signed) N V BGT Greater than (signed) (Z=0)^(N=V) BLE Less than or equal (signed) (Z=1)v(N V) COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED Add footer here Clements, pp. 224 1/9/2022 © 2006

Department of Computing Science An Example A and B are two n-component vectors Write the code that computes the inner product of A and B CMPUT 229 Clements, pp. 225 © 2006

Department of Computing Science Example code CLR. L D 6 ; clear initial sum in D 6 MOVE. B #24, D 5 ; load loop counter with n (assume n=24 here) MOVE. L #A, A 0 ; A 0 points to first position of vector A MOVE. L #B, A 1 ; A 1 points to first position of vector B (A 0), D 2 ; Repeat: get Ai and update pointer to A ADD. L #2, A 0 ; Point to the next element in A MOVE (A 1), D 3 ; get Bi and update pointer to B ADD. L #2, A 1 ; point to next element of B MULU D 2, D 3 ; Ai x Bi ADD. L D 3, D 6 ; s = s + Ai x Bi SUB #1, D 5 ; decrement loop counter BNE Next ; repeat n times Next MOVE CMPUT 229 © 2006

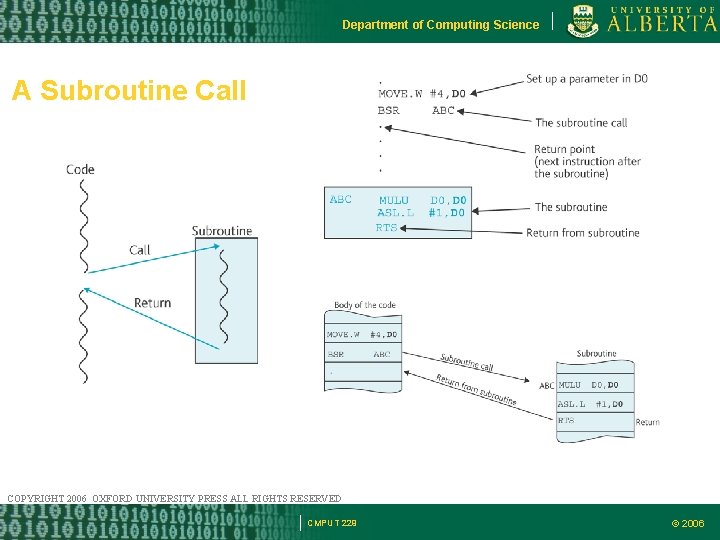

Department of Computing Science A Subroutine Call COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 © 2006

Department of Computing Science Multiple Subroutine calls COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 © 2006

Department of Computing Science Soft-Boiled Eggs Big End Little End CMPUT 229 © 2006

Department of Computing Science Endianess big-endian: in Jonathan Swift's 1726 novel Gulliver’s Travels there are tensions in Lilliput and Blefuscu because a faction called the Bigendians prefer to crack open their soft-boiled eggs from the big end, contrary to a Lilliputian royal edict. (Source: Wikipedia) “In the matter of breaking eggs they were also divided into parties: those that broke their eggs at the smaller end were in power and had banished their opponents who broke eggs at the bigger end. This had all happened because the present Emperor's grandfather while he was a boy and going to eat his egg, and broke it according to the ancient practice, had happened to cut one of his fingers. Then his father published an edict commanding all his subjects, upon great penalties, to break the smaller end of their eggs. ” (from www. hanskokhuis. nl/Lilliput. html) CMPUT 229 © 2006

Department of Computing Science Endianess dilema If you store the 32 -bit long word $12345678 in memory location $1000, where does the byte $12 goes? – Big Endian faction: it goes in location $1000, the big end of the word goes first. – Little Endian faction: it goes in location $1003, the little end of the word goes first. The 68 K is a Big Endian machine. CMPUT 229 Clements, pp. 233 © 2006

Department of Computing Science The 68 K’s Byte-Addressable Memory Space COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 235 © 2006

Department of Computing Science The Endianess Divide Switchable Endianness IA 64 Power PC DEC Alpha MIPS PA-RISC Big Endians Little Endians IBM 370 Motorola 68 K Pentium Intel 86 series VAX Sun SPARC CMPUT 229 © 2006

Department of Computing Science Data Registers The suffix in an instruction indicates in how many bits the instruction operates –. L (long word): 32 bits –. W (word): 16 bits –. B (byte): 8 bits The 68 K data registers are 32 -bit long. – What happens with the other bits when a. B or a. L instruction is executed? CMPUT 229 Clements, pp. 235 © 2006

Department of Computing Science Data Register (cont. ) The bits not affected by an instruction remain unchanged. – The result of CLR. B D 1 is: • D 1 XXXX XXXX 0000 • Where X represent the old value of the corresponding bit. The carry bits and other CCR bits are determined only by the result in the area affected by the operation. CMPUT 229 Clements, pp. 235 © 2006

Department of Computing Science Address Registers Only. W and. L operations are allowed in address registers. – The result of. W operations are sign extended to 32 bits. • Examples: MOVEA. W #$8022, A 3 results in [A 3] $FFFF 8022 MOVEA. W #$7022, A 3 results in [A 3] $00007022 CMPUT 229 Clements, pp. 236 © 2006

Department of Computing Science Instructions to Operate with Address Registers ADDA. L D 1, A 3 ; ADDA = add to address register MOVEA. L D 1, A 2 ; MOVEA = move to an address register SUBA. W D 1, A 3 ; SUBA = subtract from an address register CMPA. L A 2, A 3 ; SUBA = compare with an address register CMPUT 229 Clements, pp. 236 © 2006

Department of Computing Science Address Registers are Pointers MULU #12, D 0 ; Calculate the offset into the data structure MOVEA. L A 0, A 1 ; Copy A 0 to A 1 ADDA. L D 0, A 1 ; Add the offset to A 1 COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 237 © 2006

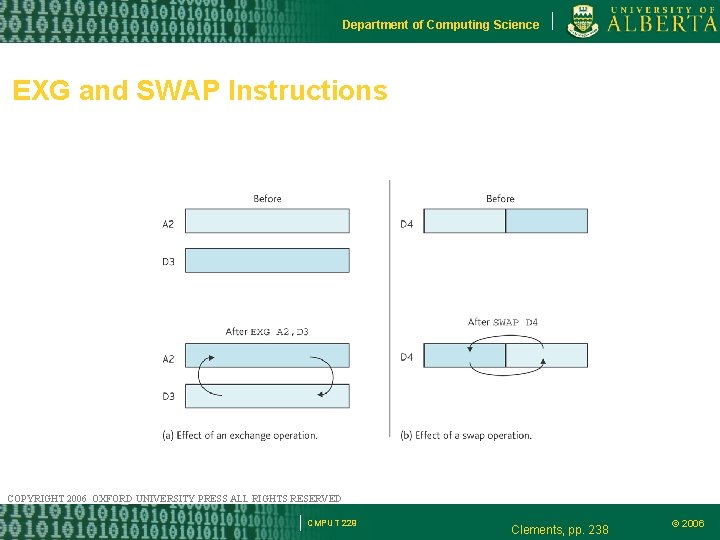

Department of Computing Science EXG and SWAP Instructions COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 238 © 2006

Department of Computing Science Data Movement Instructions The textbook provides examples of data movement (pp. 237 -241) and arithmetic (pp. 241 -244) instructions and illustrates their effect via the simulator. – You may want to complement your reading of these sections by actually trying the program segments in the Simulator yourself. CMPUT 229 © 2006

Department of Computing Science Shift and logical operations Problem: D 0 contains an 8 -bit byte in D 0 with the format xxyyyzzz. We want to find out the value of the field yyy. LSR. B #3, D 0 Shift D 0 right 3 places to get 000 xxyyy in D 0 AND. B #%00000111, D 0 Clear bits 3 to 7 of D 0 to get 00000 yyy CMPUT 229 Clements, pp. 244 © 2006

Department of Computing Science Shift and logical operations Problem: We want to clear bits 0, 1, and 2, set bits 3, 4, and 5, and toggle bits 6 and 7 of the byte in D 0 AND. B #%11111000, D 0 Clear bits 0, 1, and 2 OR. B #%00111000, D 0 Set bits 3, 4, and 5 EOR. B #%11000000, D 0 Toggle bits 6 and 7 CMPUT 229 Clements, pp. 244 © 2006

Department of Computing Science Conditional Branches Problem: Subtract D 1 from D 2 and branch if the result is negative SUB D 1, D 2 Subtract D 1 from D 2 BMI ERROR Jump if the result was negative ERROR What is wrong with this code? CMPUT 229 Clements, pp. 244 © 2006

Department of Computing Science Conditional Branches Problem: Subtract D 1 from D 2 and branch if the result is negative SUB D 1, D 2 Subtract D 1 from D 2 BMI ERROR Jump if the result was negative JOIN Unconditional branch to skip the error handling code BRA ERROR JOIN CMPUT 229 Clements, pp. 244 © 2006

Department of Computing Science Conditional Branches COPYRIGHT 2006 OXFORD UNIVERSITY PRESS ALL RIGHTS RESERVED CMPUT 229 Clements, pp. 244 © 2006

![Department of Computing Science Template of Control Flow Structures IF [D 0] = [D Department of Computing Science Template of Control Flow Structures IF [D 0] = [D](http://slidetodoc.com/presentation_image_h2/62b944180b94170a676303af191a0146/image-31.jpg)

Department of Computing Science Template of Control Flow Structures IF [D 0] = [D 1] THEN Action 1 Start [D 0]=[D 1]? CMP D 0, D 1 Perform test BNE EXIT IF [D 0] [D 1] THEN exit Action 1 ELSE execute Action 1 EXIT Exit point No Yes Action 1 EXIT CMPUT 229 Clements, pp. 247 © 2006

![Department of Computing Science Template of Control Flow Structures IF [D 0] = [D Department of Computing Science Template of Control Flow Structures IF [D 0] = [D](http://slidetodoc.com/presentation_image_h2/62b944180b94170a676303af191a0146/image-32.jpg)

Department of Computing Science Template of Control Flow Structures IF [D 0] = [D 1] THEN Action 1 ELSE Action 2 Start Action 1 CMP D 0, D 1 Perform test BNE Action 2 IF [D 0] [D 1] THEN goto Action 2 BRA Action 2 EXIT Yes [D 0]=[D 1]? No ELSE execute Action 1 EXIT Skip around Action 2 Action 1 Action 2 Exit point EXIT CMPUT 229 Clements, pp. 247 © 2006

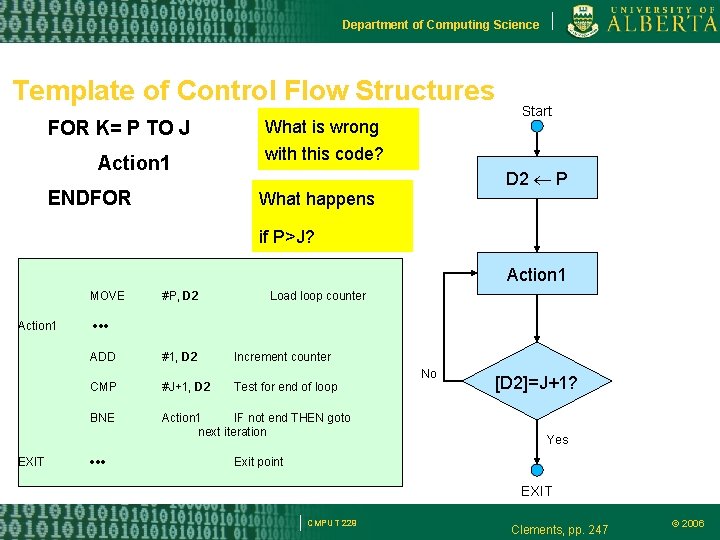

Department of Computing Science Template of Control Flow Structures FOR K= P TO J Action 1 ENDFOR What is wrong with this code? Start D 2 P What happens if P>J? Action 1 MOVE Action 1 EXIT #P, D 2 Load loop counter ADD #1, D 2 Increment counter CMP #J+1, D 2 Test for end of loop BNE Action 1 IF not end THEN goto next iteration No [D 2]=J+1? Yes Exit point EXIT CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures FOR K= P TO J Action 1 Start D 2 P ENDFOR Yes Test Action 1 MOVE #P, D 2 Load loop counter CMP #J, D 2 Compute D 2 -J BGT EXIT Done if D 2 is greater than J No BRA EXIT [D 2]>J? Action 1 Test Exit point EXIT CMPUT 229 Clements, pp. 247 © 2006

![Department of Computing Science Template of Control Flow Structures WHILE [D 0] = [D Department of Computing Science Template of Control Flow Structures WHILE [D 0] = [D](http://slidetodoc.com/presentation_image_h2/62b944180b94170a676303af191a0146/image-35.jpg)

Department of Computing Science Template of Control Flow Structures WHILE [D 0] = [D 1] Start DO Action 1 Yes Repeat Action 1 D 0, D 1 Perform test BNE EXIT Done if D 0 D 1 No BRA EXIT [D 0] [D 1]? CMP Repeat loop Action 1 Exit point EXIT CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures REPEAT Action 1 Start UNTIL [D 0] = [D 1] Action 1 Yes Action 1 EXIT Perform Action CMP D 0, D 1 Perform test BNE Action 1 Done if D 0 = D 1 [D 0]=D[1] No Exit point EXIT CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P Start P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 P>N? P = N Action N No P > N Error. Handler CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Yes D 0 P D 0 4 A 0 Table A 0+D 0 A 0 (A 0) JMP (A 0) Error. Handler A 0 contains address of case P handler EXIT CMPUT 229 Clements, pp. 247 © 2006

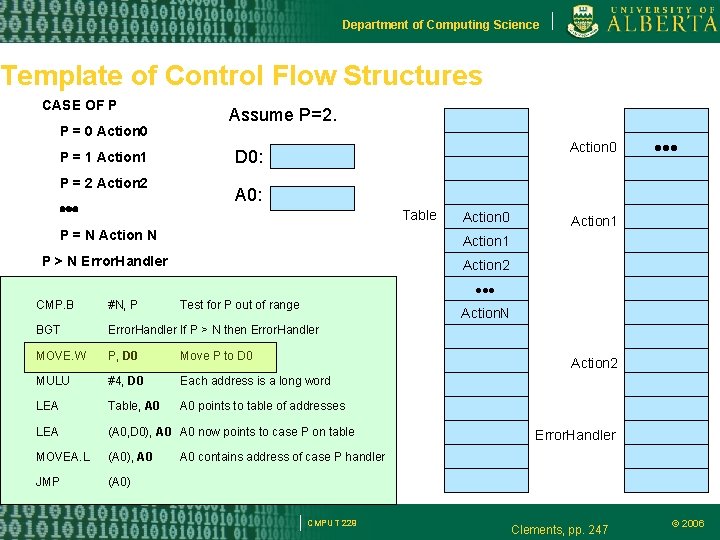

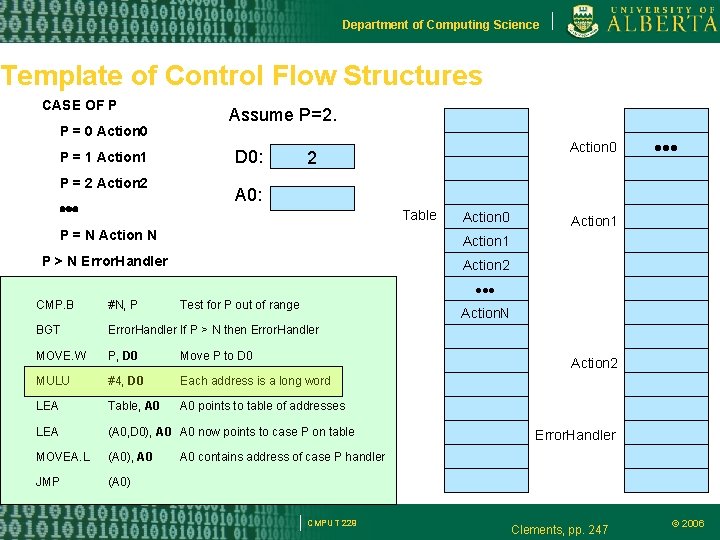

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. Action 0 D 0: A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: Action 0 2 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: Action 0 2 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

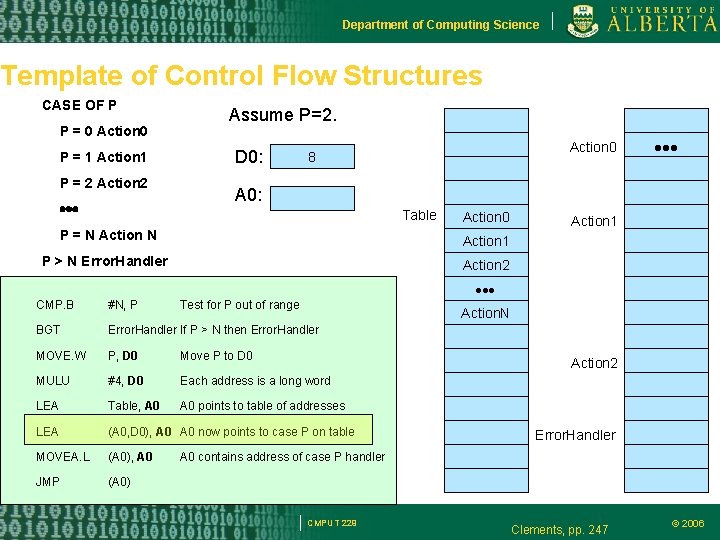

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: Action 0 8 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: Action 0 8 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: Action 0 8 A 0: Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Table + 8 Action 0 Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Table + 8 Action 0 Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Action 2 Action 0 Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Action 2 Action 0 Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science Template of Control Flow Structures CASE OF P P = 0 Action 0 P = 1 Action 1 P = 2 Action 2 Assume P=2. D 0: 8 A 0: Action 2 Action 0 Table Action 0 P = N Action 1 P > N Error. Handler Action 2 Action 1 CMP. B #N, P Test for P out of range BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 MULU #4, D 0 Each address is a long word LEA Table, A 0 points to table of addresses LEA (A 0, D 0), A 0 now points to case P on table MOVEA. L (A 0), A 0 JMP (A 0) Action. N Action 2 BRA EXIT Error. Handler A 0 contains address of case P handler CMPUT 229 Clements, pp. 247 © 2006

Department of Computing Science LOAD EFFECTIVE ADDRESS (LEA) Instead of moving the memory content pointed by an address into the register, it moves the address itself. – Thus if A 0 contains the address $4000 and D 0 contains the data $0008, then the instruction LEA (A 0, D 0), A 0+D 0 Writes the value $4008 into A 0. CMPUT 229 © 2006

Department of Computing Science Difference Between MOVE and LEA It is important to understand the difference between MOVE and LEA: LEA (A 0, D 0), A 1 A 0+D 0 MOVE (A 0, D 0), D 1 (A 0+D 0) LEA writes the effective address into the destination register while MOVE writes the content of the memory position in the address. CMPUT 229 © 2006

Department of Computing Science Two ways to do the same thing The following two instruction sequences do the same thing: SEQ 1 SEQ 2 LEA (A 0, D 0), A 0+D 0 MOVEA. L (A 0), A 0 (A 0) MOVEA. L (A 0, D 0), A 0 (A 0+D 0) CMPUT 229 © 2006

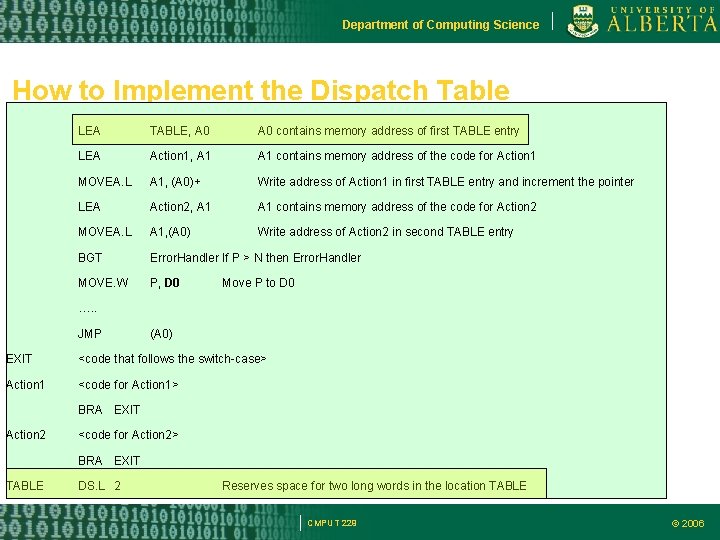

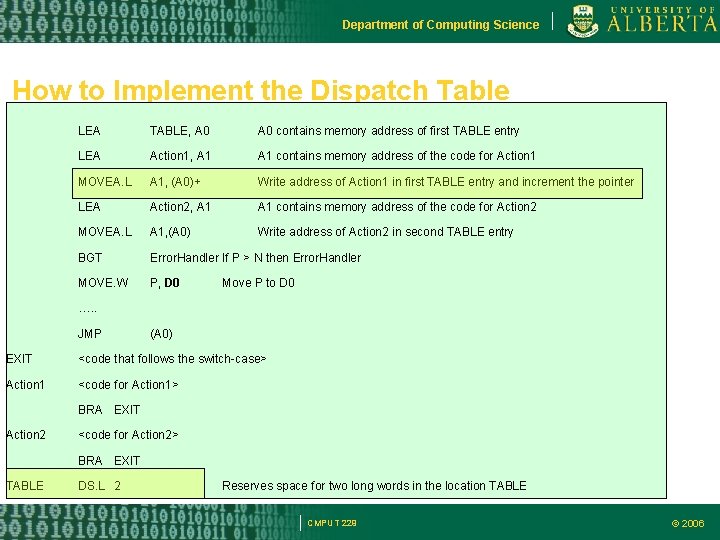

Department of Computing Science How to Implement the Dispatch Table LEA TABLE, A 0 contains memory address of first TABLE entry LEA Action 1, A 1 contains memory address of the code for Action 1 MOVEA. L A 1, (A 0)+ Write address of Action 1 in first TABLE entry and increment the pointer LEA Action 2, A 1 contains memory address of the code for Action 2 MOVEA. L A 1, (A 0) Write address of Action 2 in second TABLE entry BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 …. . JMP (A 0) EXIT <code that follows the switch-case> Action 1 <code for Action 1> BRA EXIT Action 2 <code for Action 2> BRA EXIT TABLE DS. L 2 Reserves space for two long words in the location TABLE CMPUT 229 © 2006

Department of Computing Science How to Implement the Dispatch Table LEA TABLE, A 0 contains memory address of first TABLE entry LEA Action 1, A 1 contains memory address of the code for Action 1 MOVEA. L A 1, (A 0)+ Write address of Action 1 in first TABLE entry and increment the pointer LEA Action 2, A 1 contains memory address of the code for Action 2 MOVEA. L A 1, (A 0) Write address of Action 2 in second TABLE entry BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 …. . JMP (A 0) EXIT <code that follows the switch-case> Action 1 <code for Action 1> BRA EXIT Action 2 <code for Action 2> BRA EXIT TABLE DS. L 2 Reserves space for two long words in the location TABLE CMPUT 229 © 2006

Department of Computing Science How to Implement the Dispatch Table LEA TABLE, A 0 contains memory address of first TABLE entry LEA Action 1, A 1 contains memory address of the code for Action 1 MOVEA. L A 1, (A 0)+ Write address of Action 1 in first TABLE entry and increment the pointer LEA Action 2, A 1 contains memory address of the code for Action 2 MOVEA. L A 1, (A 0) Write address of Action 2 in second TABLE entry BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 …. . JMP (A 0) EXIT <code that follows the switch-case> Action 1 <code for Action 1> BRA EXIT Action 2 <code for Action 2> BRA EXIT TABLE DS. L 2 Reserves space for two long words in the location TABLE CMPUT 229 © 2006

Department of Computing Science How to Implement the Dispatch Table LEA TABLE, A 0 contains memory address of first TABLE entry LEA Action 1, A 1 contains memory address of the code for Action 1 MOVEA. L A 1, (A 0)+ Write address of Action 1 in first TABLE entry and increment the pointer LEA Action 2, A 1 contains memory address of the code for Action 2 MOVEA. L A 1, (A 0) Write address of Action 2 in second TABLE entry BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 …. . JMP (A 0) EXIT <code that follows the switch-case> Action 1 <code for Action 1> BRA EXIT Action 2 <code for Action 2> BRA EXIT TABLE DS. L 2 Reserves space for two long words in the location TABLE CMPUT 229 © 2006

Department of Computing Science How to Implement the Dispatch Table LEA TABLE, A 0 contains memory address of first TABLE entry LEA Action 1, A 1 contains memory address of the code for Action 1 MOVEA. L A 1, (A 0)+ Write address of Action 1 in first TABLE entry and increment the pointer LEA Action 2, A 1 contains memory address of the code for Action 2 MOVEA. L A 1, (A 0) Write address of Action 2 in second TABLE entry BGT Error. Handler If P > N then Error. Handler MOVE. W P, D 0 Move P to D 0 …. . JMP (A 0) EXIT <code that follows the switch-case> Action 1 <code for Action 1> BRA EXIT Action 2 <code for Action 2> BRA EXIT TABLE DS. L 2 Reserves space for two long words in the location TABLE CMPUT 229 © 2006

Department of Computing Science Exercise Write a code segment that reads a byte B from the address 0 x 8400 0040 and: a) writes 0 x 0000 00 FF in address 0 x 8400 0044 if the bit 5 of B is 1; b) writes 0 x. FFFF FF 00 in address 0 x 8400 0044 otherwise CMPUT 229 © 2006

- Slides: 58