Fachhochschule Dortmund PC mit offener Seitenwand University of

- Slides: 28

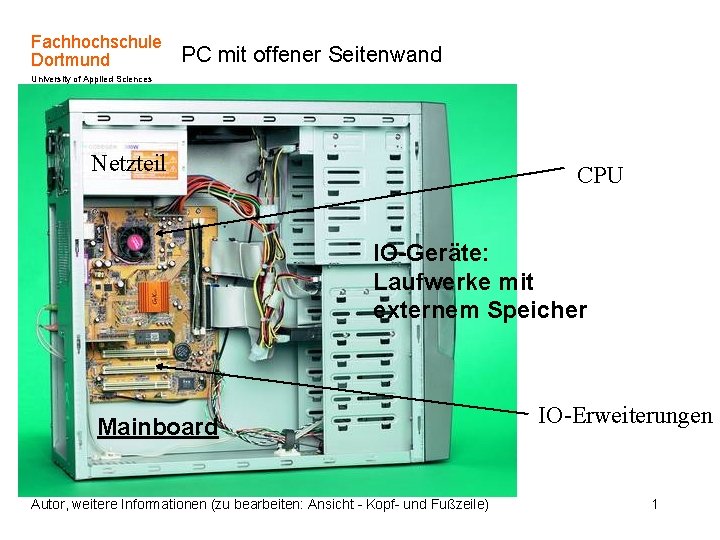

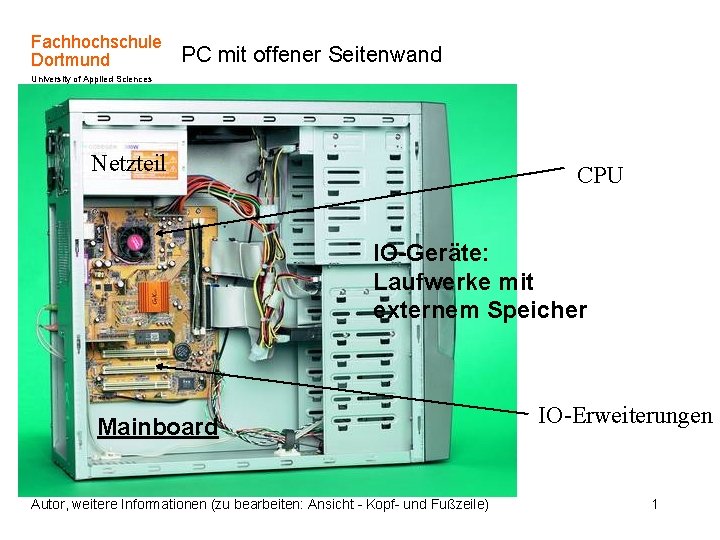

Fachhochschule Dortmund PC mit offener Seitenwand University of Applied Sciences Netzteil CPU IO-Geräte: Laufwerke mit externem Speicher Mainboard Autor, weitere Informationen (zu bearbeiten: Ansicht - Kopf- und Fußzeile) IO-Erweiterungen 1

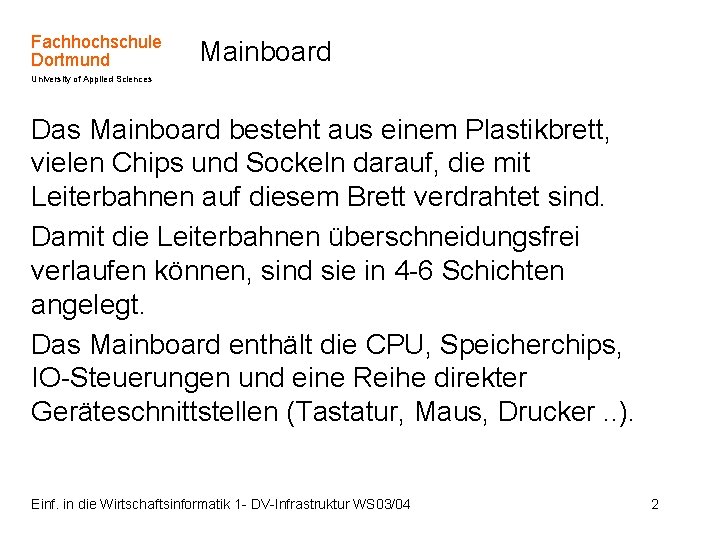

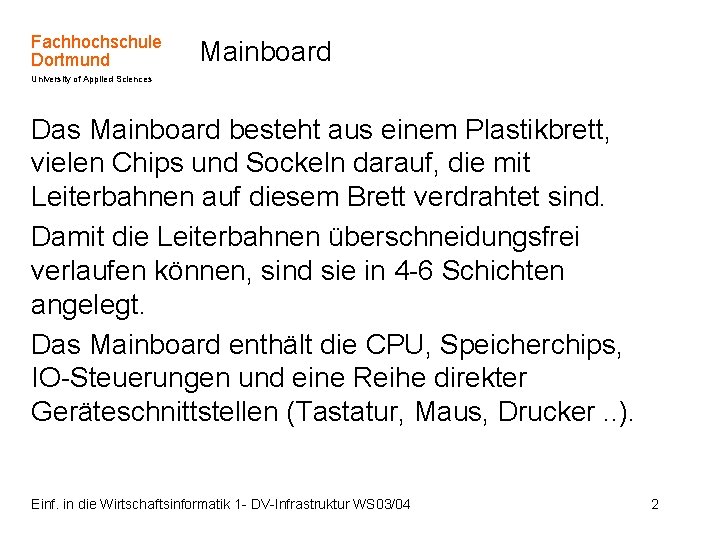

Fachhochschule Dortmund Mainboard University of Applied Sciences Das Mainboard besteht aus einem Plastikbrett, vielen Chips und Sockeln darauf, die mit Leiterbahnen auf diesem Brett verdrahtet sind. Damit die Leiterbahnen überschneidungsfrei verlaufen können, sind sie in 4 -6 Schichten angelegt. Das Mainboard enthält die CPU, Speicherchips, IO-Steuerungen und eine Reihe direkter Geräteschnittstellen (Tastatur, Maus, Drucker. . ). Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 2

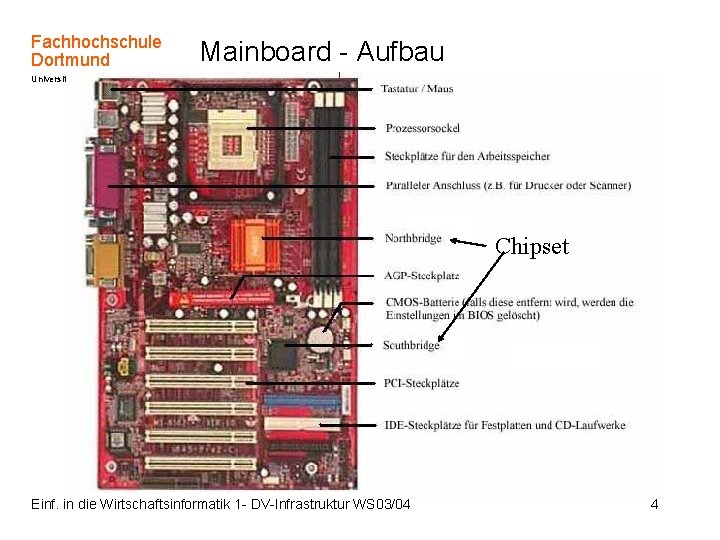

Fachhochschule Dortmund Mainboard University of Applied Sciences Die Bausteine kommunizieren über Bussysteme miteinander. Die Steuerung dieser Bussysteme und Verbindungen wird vom Chipset (Satz von Chips) übernommen. Dieser Chipset wird immer mehr in wenige Chips integriert, sie besitzen mittlerweile eine riesige Funktionalität. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 3

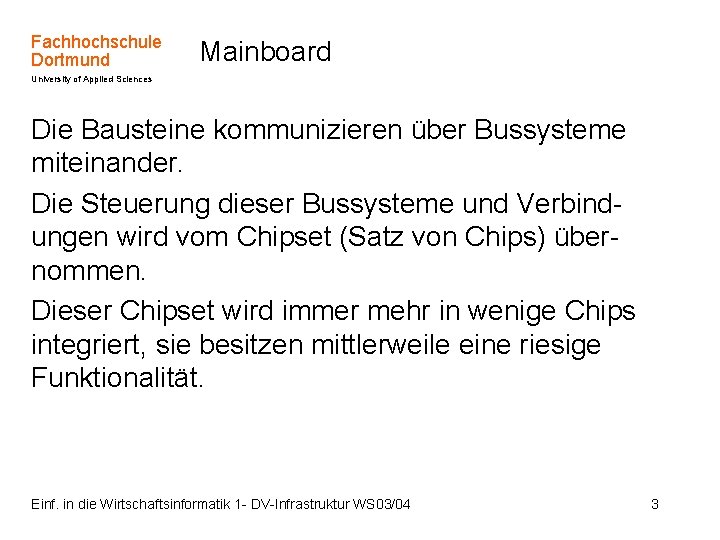

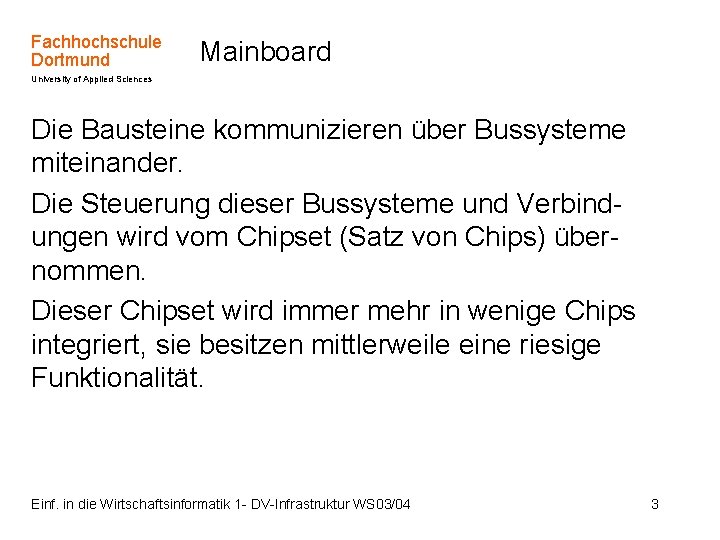

Fachhochschule Dortmund Mainboard - Aufbau University of Applied Sciences Chipset Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 4

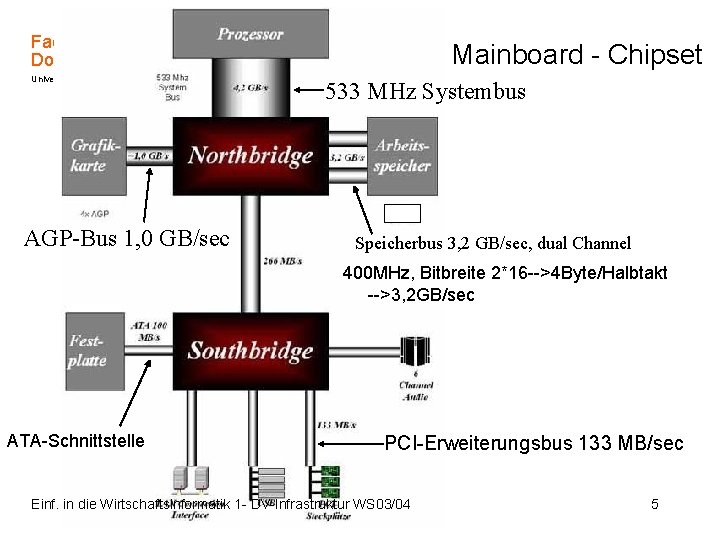

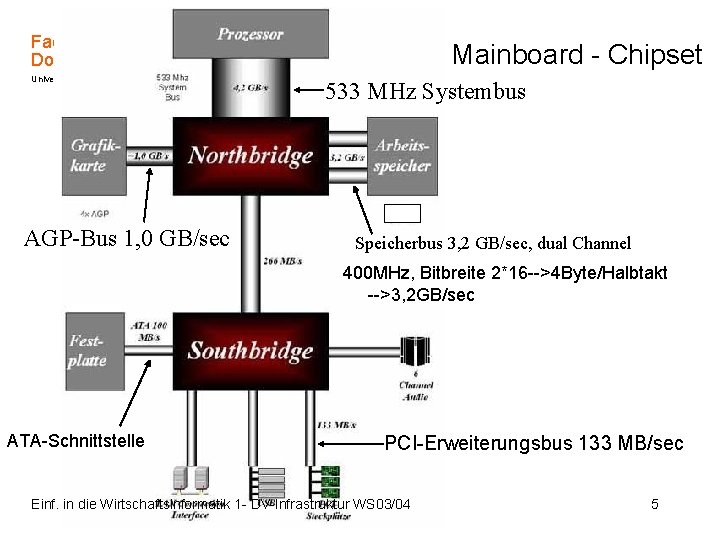

Fachhochschule Dortmund University of Applied Sciences AGP-Bus 1, 0 GB/sec Mainboard - Chipset 533 MHz Systembus Speicherbus 3, 2 GB/sec, dual Channel 400 MHz, Bitbreite 2*16 -->4 Byte/Halbtakt -->3, 2 GB/sec ATA-Schnittstelle PCI-Erweiterungsbus 133 MB/sec Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 5

Fachhochschule Dortmund Mainboard - Chipset University of Applied Sciences In der neueren Entwicklung gibt es neben dem „Brückensystem“ mit North- und Southbridge ein Hub-System (Hub = Verkehrsdrehkreuz). Sternförmige Anordnung, in der Mitte der Hub. Die Northbridge wird zum • Memory Controller Hub(MCH), die Southbridge zum • IO Controller Hub(ICH). Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 6

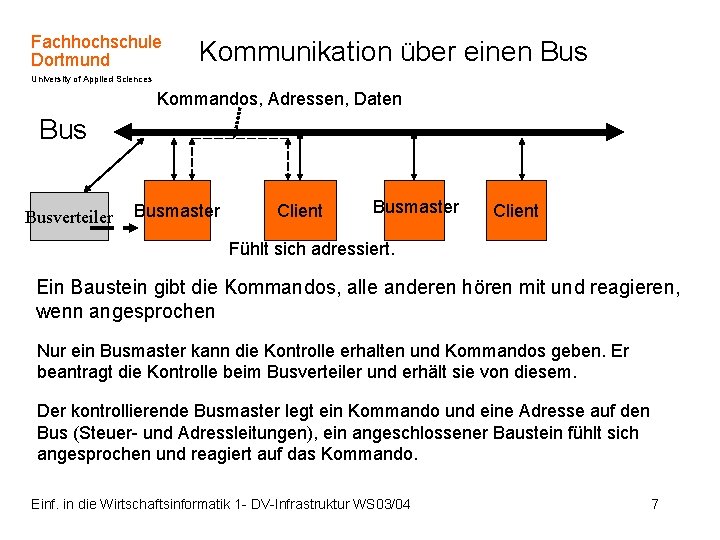

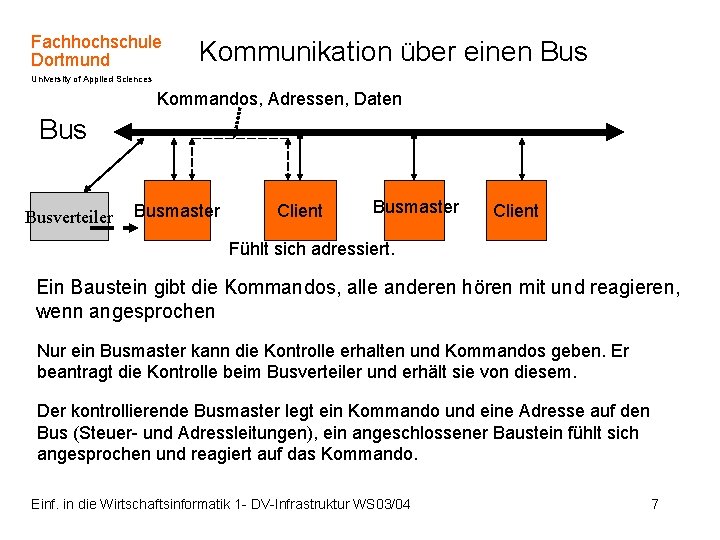

Fachhochschule Dortmund Kommunikation über einen Bus University of Applied Sciences Kommandos, Adressen, Daten Busverteiler Busmaster Client Fühlt sich adressiert. Ein Baustein gibt die Kommandos, alle anderen hören mit und reagieren, wenn angesprochen Nur ein Busmaster kann die Kontrolle erhalten und Kommandos geben. Er beantragt die Kontrolle beim Busverteiler und erhält sie von diesem. Der kontrollierende Busmaster legt ein Kommando und eine Adresse auf den Bus (Steuer- und Adressleitungen), ein angeschlossener Baustein fühlt sich angesprochen und reagiert auf das Kommando. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 7

Fachhochschule Dortmund Kommunikation über einen Bus University of Applied Sciences Der Baustein tauscht - getaktet mit dem Bustakt - mit dem Busmaster Daten aus. · Übertragungskapazität Angabe der maximalen Datenübertragungsrate Kmax in Mbyte/sec T Takt in MHz N Zahl der Takte, die zum Übertragen eines Wertes benötigt werden. M Zahl der Bytes, die parallel übertragen werden (Datenbreite/8). Kmax = M * (T / N) Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 8

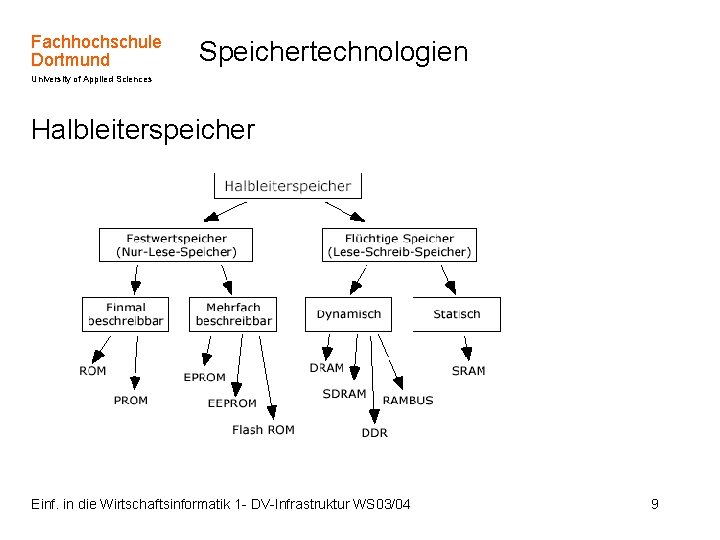

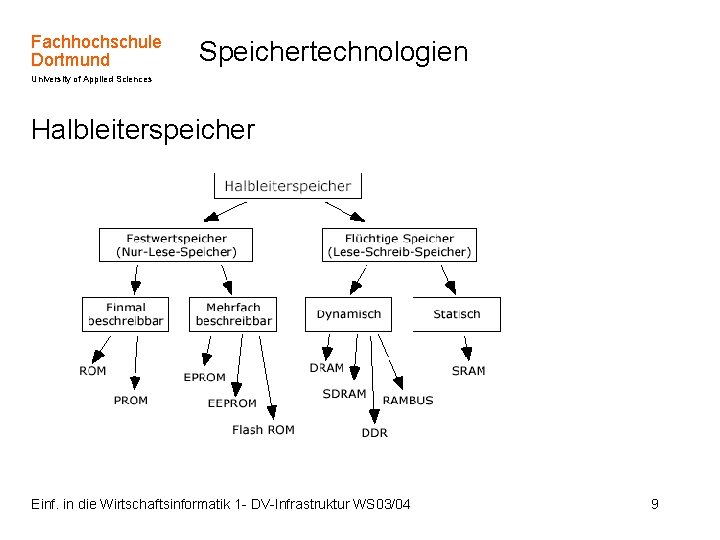

Fachhochschule Dortmund Speichertechnologien University of Applied Sciences Halbleiterspeicher Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 9

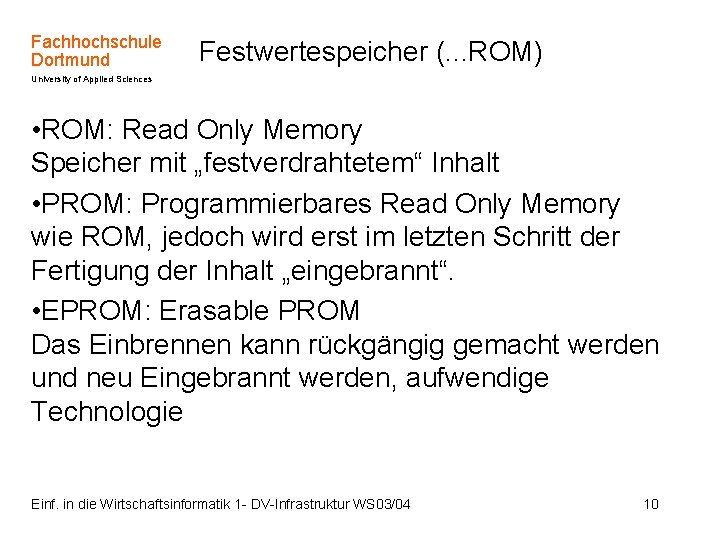

Fachhochschule Dortmund Festwertespeicher (. . . ROM) University of Applied Sciences • ROM: Read Only Memory Speicher mit „festverdrahtetem“ Inhalt • PROM: Programmierbares Read Only Memory wie ROM, jedoch wird erst im letzten Schritt der Fertigung der Inhalt „eingebrannt“. • EPROM: Erasable PROM Das Einbrennen kann rückgängig gemacht werden und neu Eingebrannt werden, aufwendige Technologie Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 10

Fachhochschule Dortmund Festwertespeicher (. . . ROM) University of Applied Sciences • EEPROM: Electrical EPROM, Löschen einfacher • Flash ROM: ähnlich EEPROM, Löschen und Beschreiben noch einfacher, Datensticks, dig. Fotographie u. a. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 11

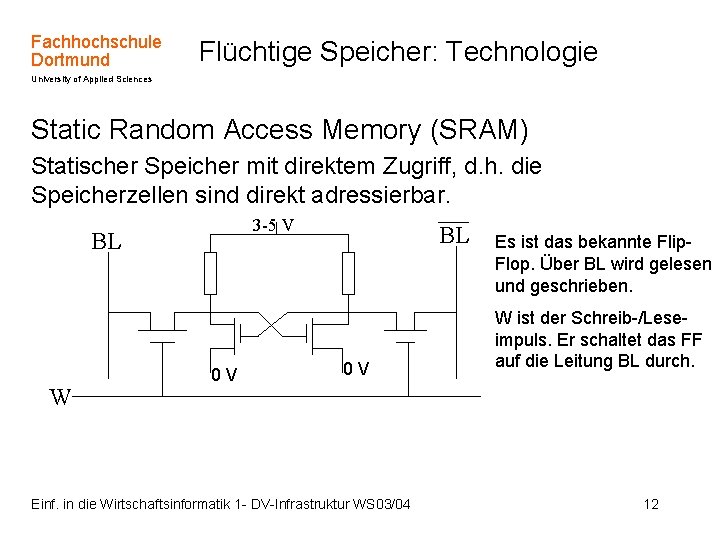

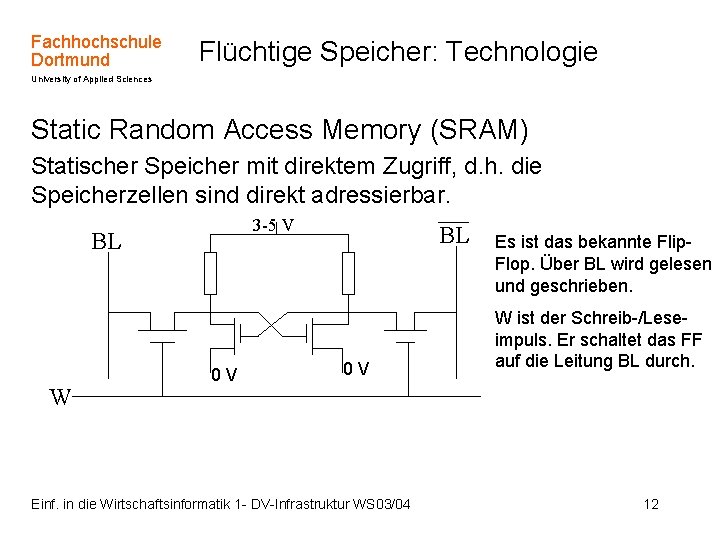

Fachhochschule Dortmund Flüchtige Speicher: Technologie University of Applied Sciences Static Random Access Memory (SRAM) Statischer Speicher mit direktem Zugriff, d. h. die Speicherzellen sind direkt adressierbar. 3 -5 V BL W 0 V BL 0 V Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 Es ist das bekannte Flip. Flop. Über BL wird gelesen und geschrieben. W ist der Schreib-/Leseimpuls. Er schaltet das FF auf die Leitung BL durch. 12

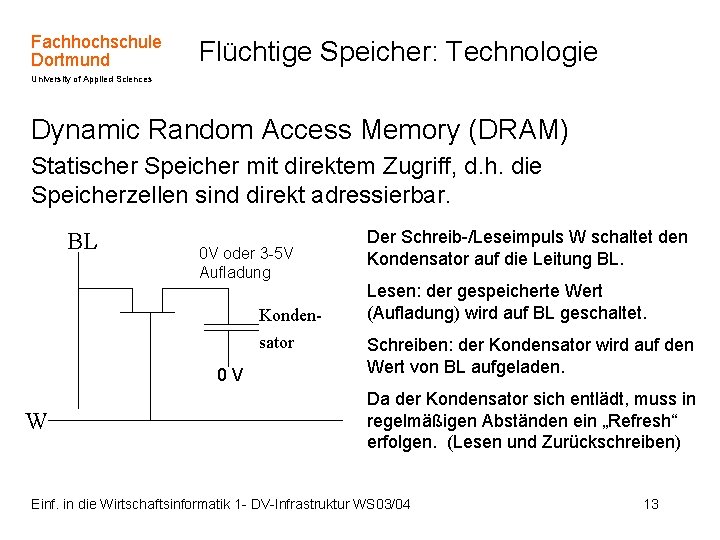

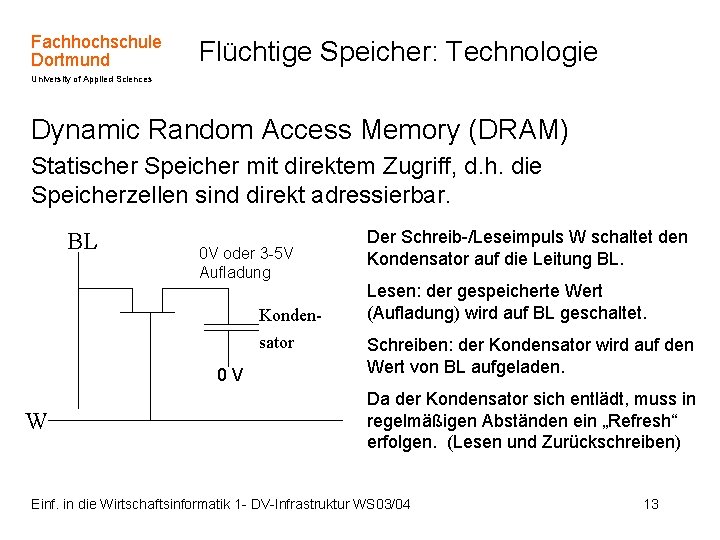

Fachhochschule Dortmund Flüchtige Speicher: Technologie University of Applied Sciences Dynamic Random Access Memory (DRAM) Statischer Speicher mit direktem Zugriff, d. h. die Speicherzellen sind direkt adressierbar. BL 0 V oder 3 -5 V Aufladung Kondensator 0 V W Der Schreib-/Leseimpuls W schaltet den Kondensator auf die Leitung BL. Lesen: der gespeicherte Wert (Aufladung) wird auf BL geschaltet. Schreiben: der Kondensator wird auf den Wert von BL aufgeladen. Da der Kondensator sich entlädt, muss in regelmäßigen Abständen ein „Refresh“ erfolgen. (Lesen und Zurückschreiben) Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 13

Fachhochschule Dortmund University of Applied Sciences Flüchtige Speicher: DRAMBausteine DDR: Abkürzung für DDR-SDRAM Ein SDRAM mit einer Double Data Rate, pro Takt werden 2 Werte übertragen. „QUAD PUMPED“- Technologie: 2 Kanäle à 16 bit werden im DDR Modus betrieben. Mit einem Takt werden vier 16 -bit-Werte übertragen. Taktraten: 266 MHz, 333 MHz, 400 MHz 400 MHz, Bitbreite 2*16 -->4 Byte/Halbtakt--> 8 Byte*400 MHz -->3, 2 GB/sec Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 14

Fachhochschule Dortmund University of Applied Sciences Flüchtige Speicher: DRAMBausteine Beispiel: 512 MB DDR-(SD)RAM PC-333 -233 Kapazität: 512 MB Double Data Rate Synchronous Dynamic Random Access Memory Takt: 333 MHz (max. z. Zt. 400 MHz) Das PC 333 -Modul hat 2 Takte CAS-Latency und je 3 Takte RAS Precharge und RAS-to-CAS Delay. Manchmal auch nur als CL 2 (CAS -Latency 2) bezeichnet. RAS- und CAS-Lat. sind Verzögerungszeiten beim Lesen/Schreiben. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 15

Fachhochschule Dortmund Flüchtige Speicher: RDRAM University of Applied Sciences RDRAM Der Rambus-Speicher funktioniert nach einem anderen Prinzip als der SDRAM-Speicher. Das Kernstück des Rambus-Speichers ist ein Direct Rambus Channel, ein 16 Bit breiter Bus, der mit bis zu 400 MHz betrieben wird. Da hier auch beide Flanken des Taktsignals verwendet werden ergibt sich eine max. theoretische Datenübertragung von 1, 6 GB/s. Die 'Dual Channel'RDRAMs, erreichen 3, 2 GB/s , da zwei Speicher-Channels vorhanden sind. Der RAMBUS-Speicher konnte sich wegen des Preises nicht bis heute durchsetzen. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 16

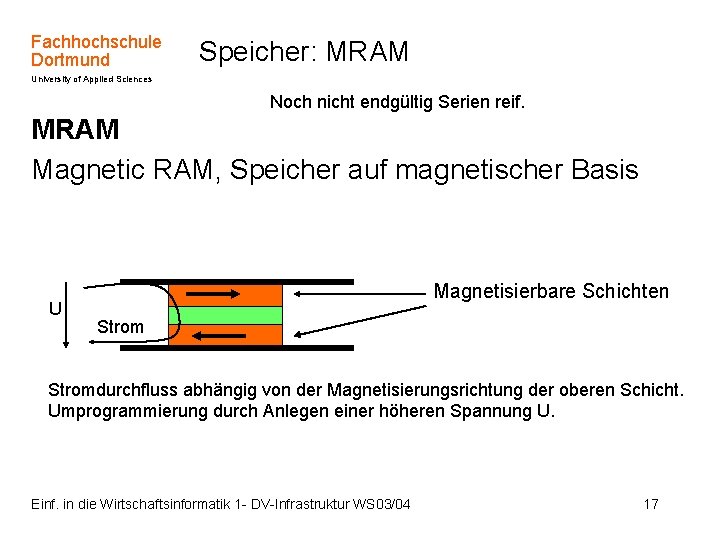

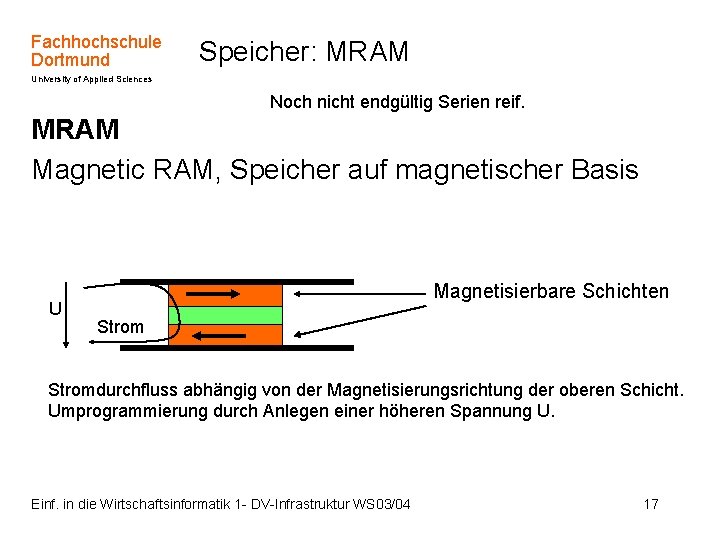

Fachhochschule Dortmund Speicher: MRAM University of Applied Sciences Noch nicht endgültig Serien reif. MRAM Magnetic RAM, Speicher auf magnetischer Basis U Magnetisierbare Schichten Stromdurchfluss abhängig von der Magnetisierungsrichtung der oberen Schicht. Umprogrammierung durch Anlegen einer höheren Spannung U. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 17

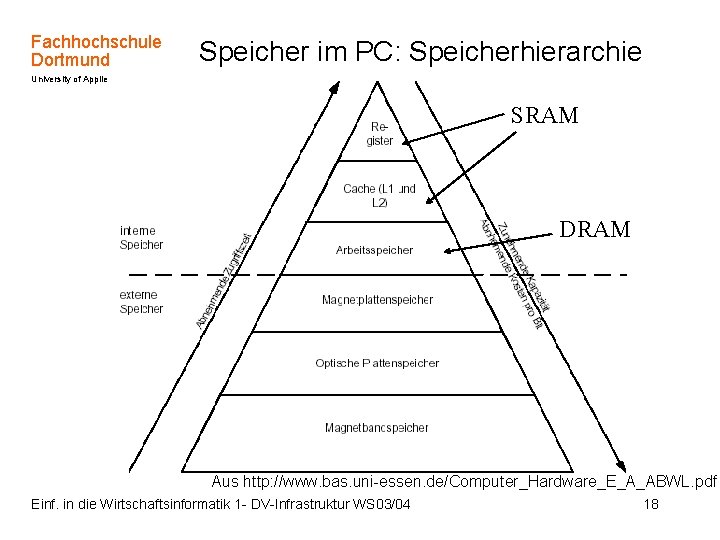

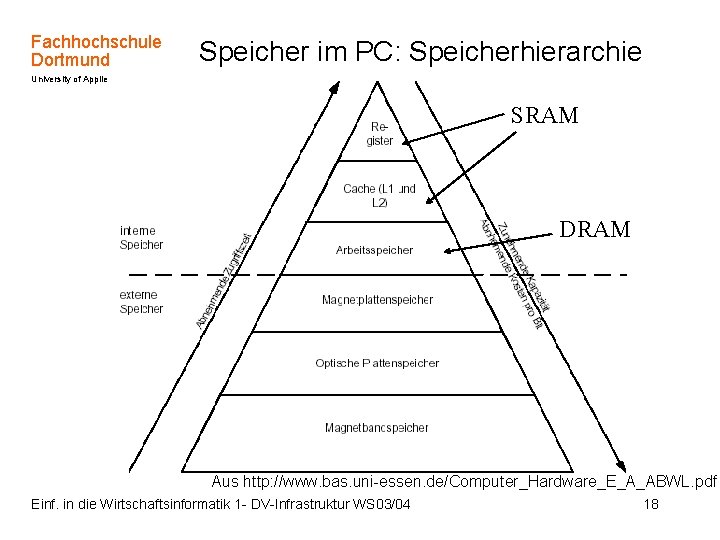

Fachhochschule Dortmund Speicher im PC: Speicherhierarchie University of Applied Sciences SRAM DRAM Aus http: //www. bas. uni-essen. de/Computer_Hardware_E_A_ABWL. pdf Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 18

Fachhochschule Dortmund Speicher im PC: Registerspeicher University of Applied Sciences Die Bedeutung der Register wurde bereits behandelt. Speicher mit dem schnellsten Zugriff. Zusätzlich zu den allgemeinen Registern (Zwischenspeichern von Daten) gibt es eine Menge von Spezialregistern. Zugriffszeit ist sehr schnell: 1 Takt der CPU. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 19

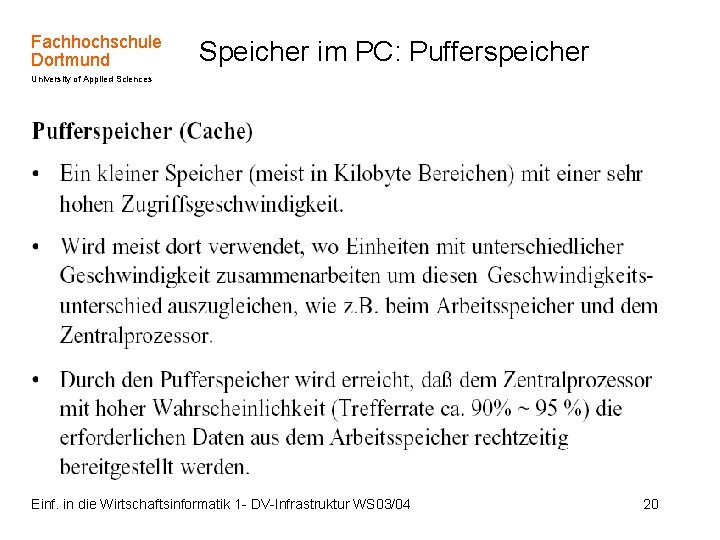

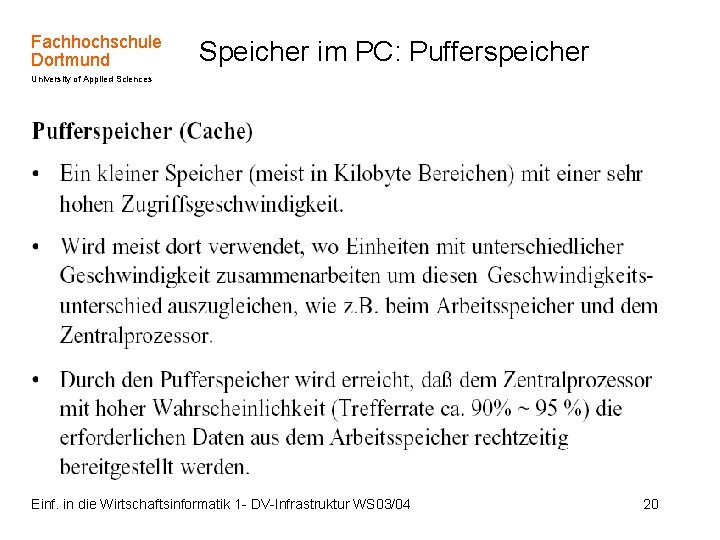

Fachhochschule Dortmund Speicher im PC: Pufferspeicher University of Applied Sciences Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 20

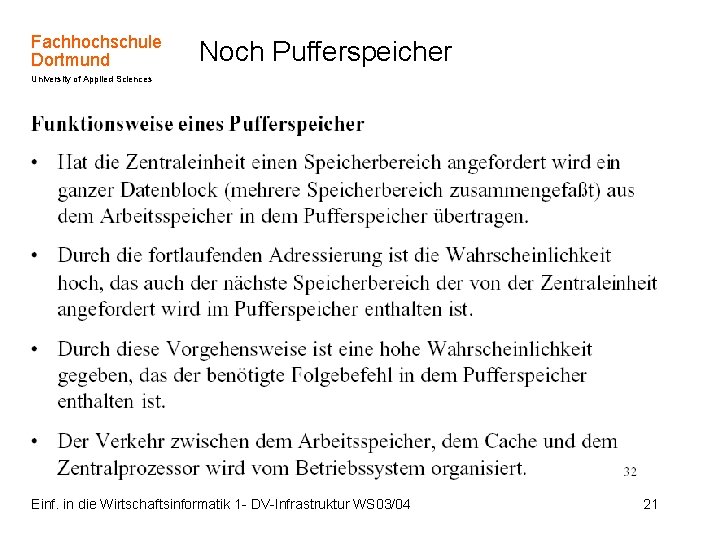

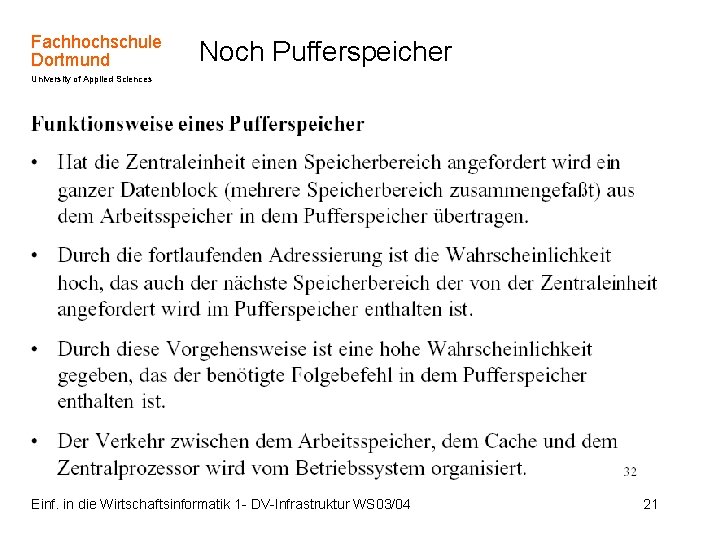

Fachhochschule Dortmund Noch Pufferspeicher University of Applied Sciences Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 21

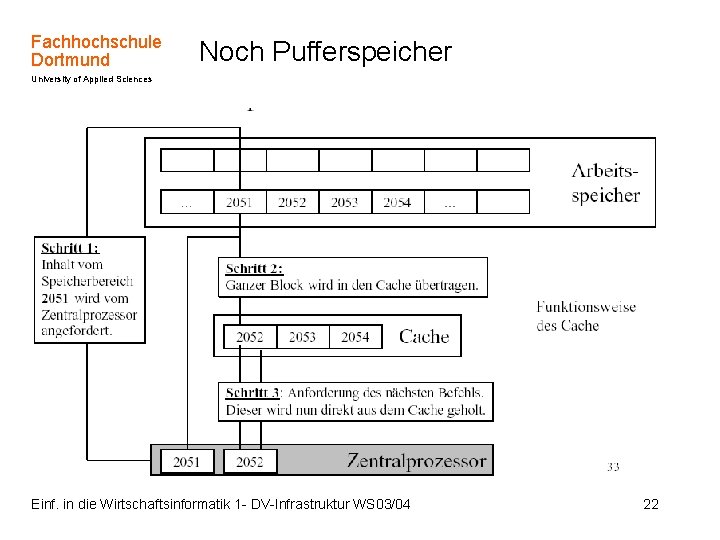

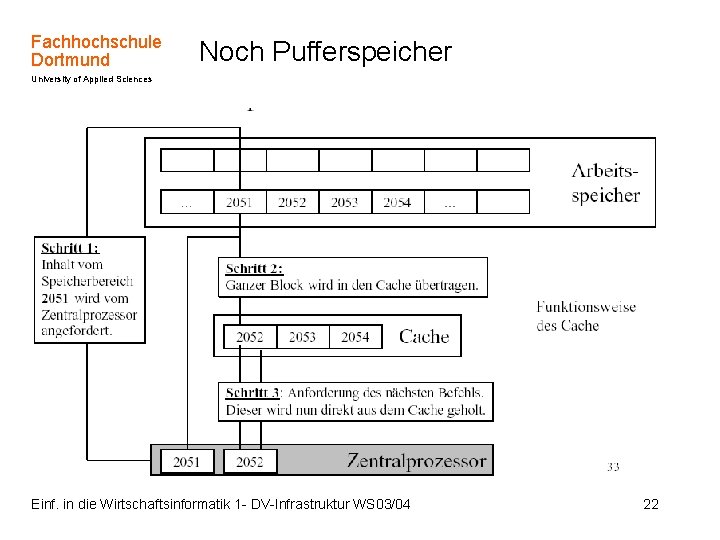

Fachhochschule Dortmund Noch Pufferspeicher University of Applied Sciences Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 22

Fachhochschule Dortmund Speicher im PC: Arbeitsspeicher University of Applied Sciences Realisiert als DRAM (Dynamic Random Access Memory). Die Speicherzellen haben die Länge 8 bit = 1 byte. Sie sind ab 0 durchlaufend adressiert. Die CPU hat unmittelbaren Zugang zu diesem Speicher. Zweck: Der Arbeitsspeicher enthält alle Programmtexte und Daten, auf die von der CPU direkt zugegriffen wird. Größenordnung: bis zu 1 Gigabyte (GB), in PC‘s meist 256 Megabyte (MB) oder 512 Megabyte (MB). Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 23

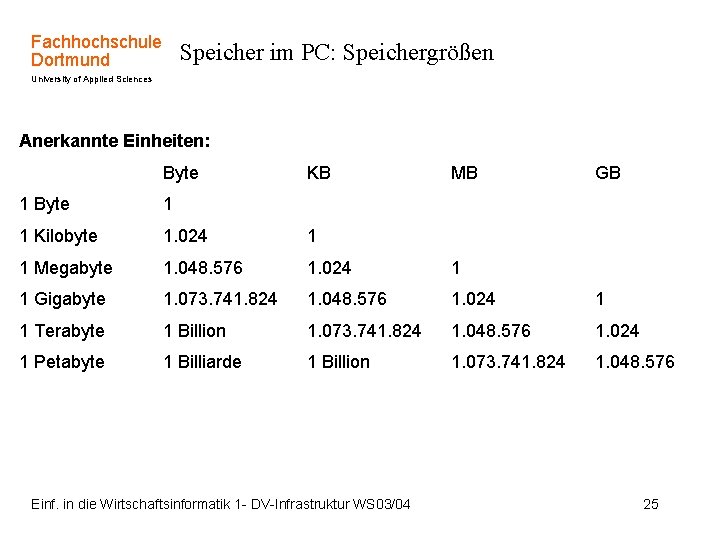

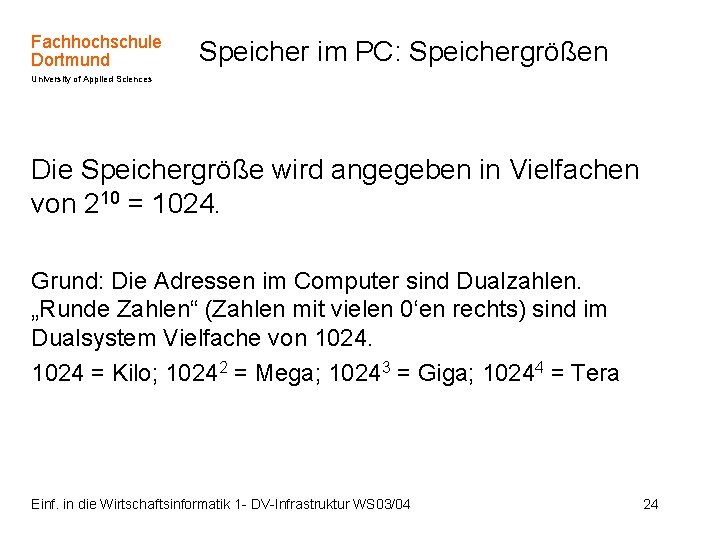

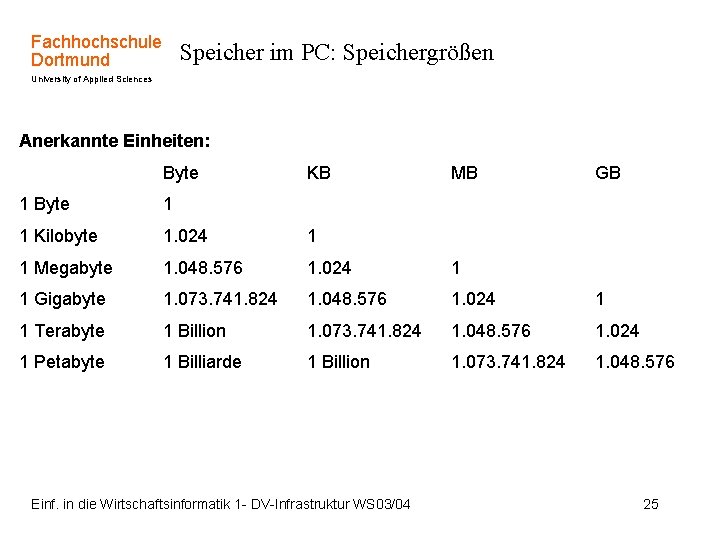

Fachhochschule Dortmund Speicher im PC: Speichergrößen University of Applied Sciences Die Speichergröße wird angegeben in Vielfachen von 210 = 1024. Grund: Die Adressen im Computer sind Dualzahlen. „Runde Zahlen“ (Zahlen mit vielen 0‘en rechts) sind im Dualsystem Vielfache von 1024 = Kilo; 10242 = Mega; 10243 = Giga; 10244 = Tera Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 24

Fachhochschule Dortmund Speicher im PC: Speichergrößen University of Applied Sciences Anerkannte Einheiten: Byte KB MB GB 1 Byte 1 1 Kilobyte 1. 024 1 1 Megabyte 1. 048. 576 1. 024 1 1 Gigabyte 1. 073. 741. 824 1. 048. 576 1. 024 1 1 Terabyte 1 Billion 1. 073. 741. 824 1. 048. 576 1. 024 1 Petabyte 1 Billiarde 1 Billion 1. 073. 741. 824 1. 048. 576 Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 25

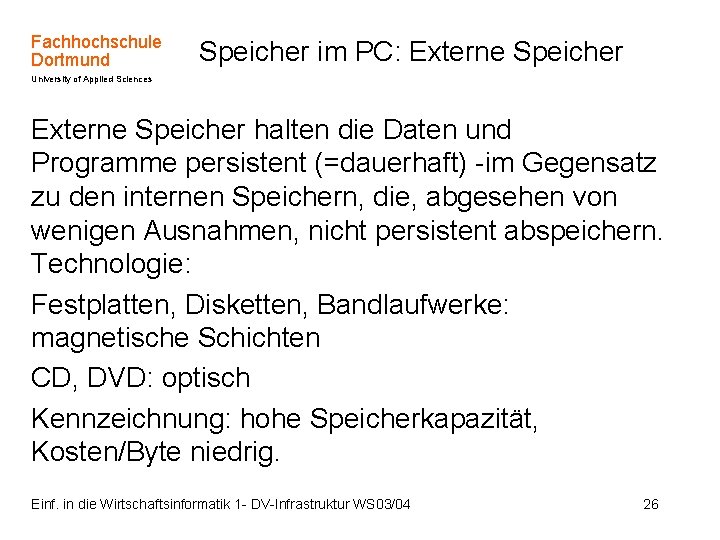

Fachhochschule Dortmund Speicher im PC: Externe Speicher University of Applied Sciences Externe Speicher halten die Daten und Programme persistent (=dauerhaft) -im Gegensatz zu den internen Speichern, die, abgesehen von wenigen Ausnahmen, nicht persistent abspeichern. Technologie: Festplatten, Disketten, Bandlaufwerke: magnetische Schichten CD, DVD: optisch Kennzeichnung: hohe Speicherkapazität, Kosten/Byte niedrig. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 26

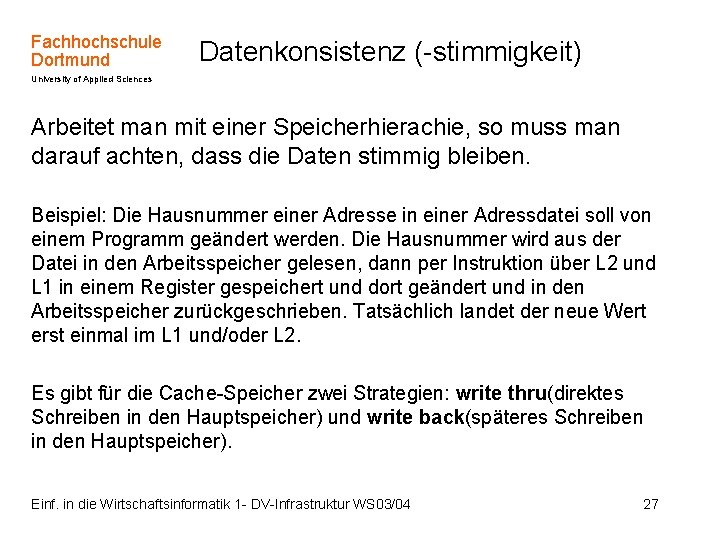

Fachhochschule Dortmund Datenkonsistenz (-stimmigkeit) University of Applied Sciences Arbeitet man mit einer Speicherhierachie, so muss man darauf achten, dass die Daten stimmig bleiben. Beispiel: Die Hausnummer einer Adresse in einer Adressdatei soll von einem Programm geändert werden. Die Hausnummer wird aus der Datei in den Arbeitsspeicher gelesen, dann per Instruktion über L 2 und L 1 in einem Register gespeichert und dort geändert und in den Arbeitsspeicher zurückgeschrieben. Tatsächlich landet der neue Wert erst einmal im L 1 und/oder L 2. Es gibt für die Cache-Speicher zwei Strategien: write thru(direktes Schreiben in den Hauptspeicher) und write back(späteres Schreiben in den Hauptspeicher). Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 27

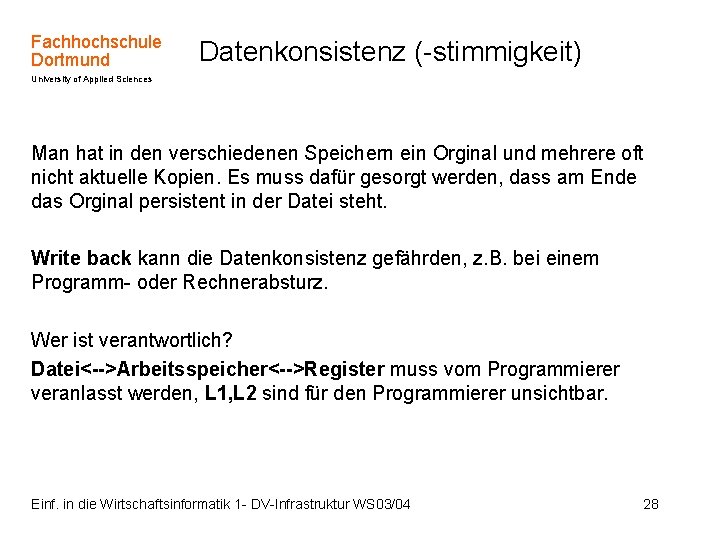

Fachhochschule Dortmund Datenkonsistenz (-stimmigkeit) University of Applied Sciences Man hat in den verschiedenen Speichern ein Orginal und mehrere oft nicht aktuelle Kopien. Es muss dafür gesorgt werden, dass am Ende das Orginal persistent in der Datei steht. Write back kann die Datenkonsistenz gefährden, z. B. bei einem Programm- oder Rechnerabsturz. Wer ist verantwortlich? Datei<-->Arbeitsspeicher<-->Register muss vom Programmierer veranlasst werden, L 1, L 2 sind für den Programmierer unsichtbar. Einf. in die Wirtschaftsinformatik 1 - DV-Infrastruktur WS 03/04 28