Fabrication Steps Pwell Process Diffusion VDD P P

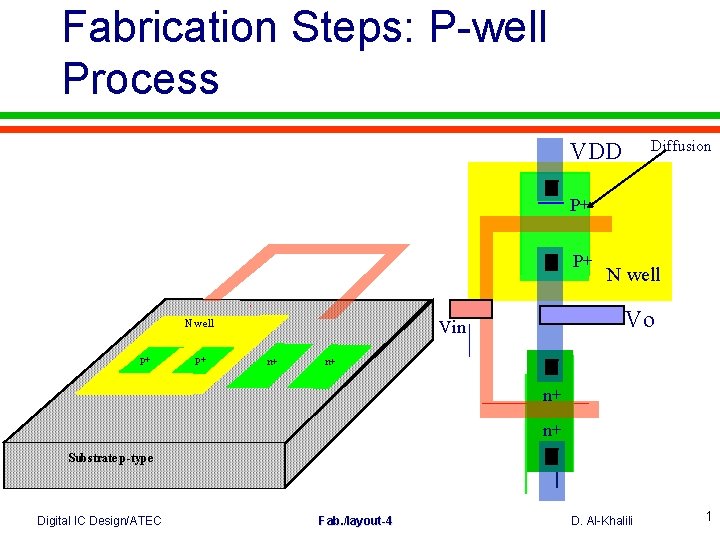

Fabrication Steps: P-well Process Diffusion VDD P+ P+ p+ p+ Vo Vin N well p+ n+ n+ n+ Substrate p-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 1

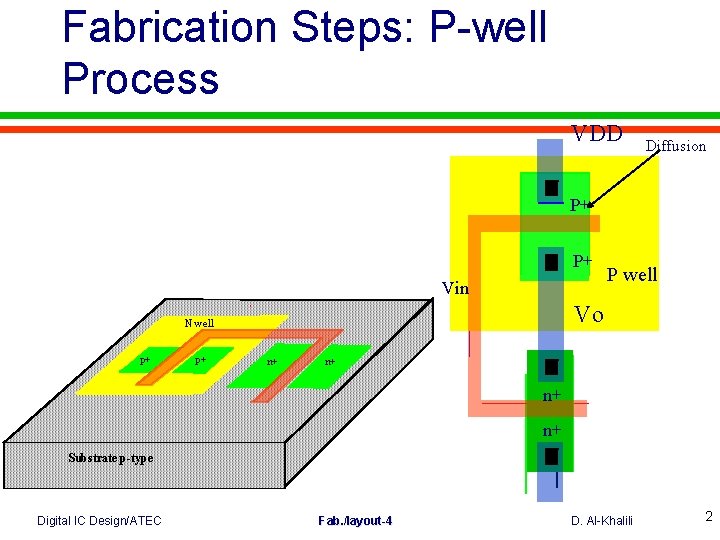

Fabrication Steps: P-well Process VDD Diffusion P+ P+ Vin Vo N well p+ p+ P well p+ n+ n+ n+ Substrate p-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 2

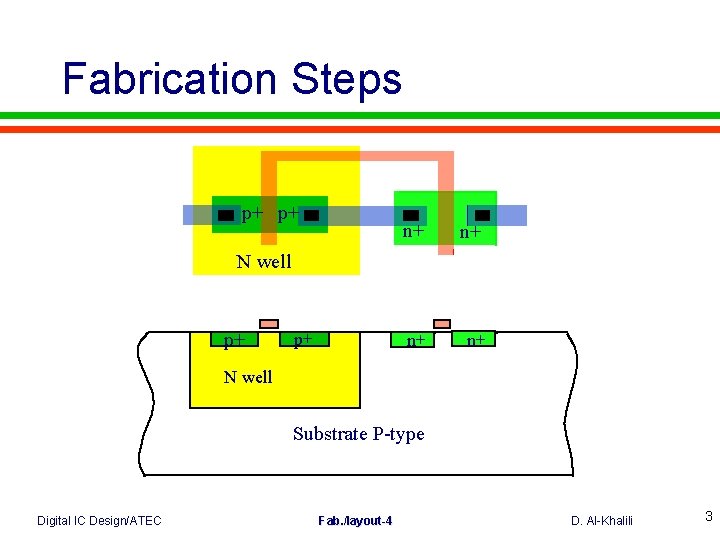

Fabrication Steps p+ p+ n+ n+ N well p+ p+ N well Substrate P-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 3

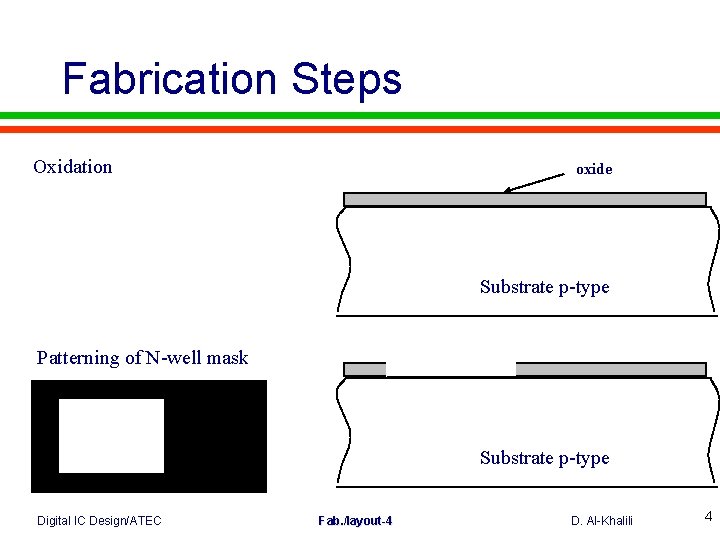

Fabrication Steps Oxidation oxide Substrate p-type Patterning of N-well mask Substrate p-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 4

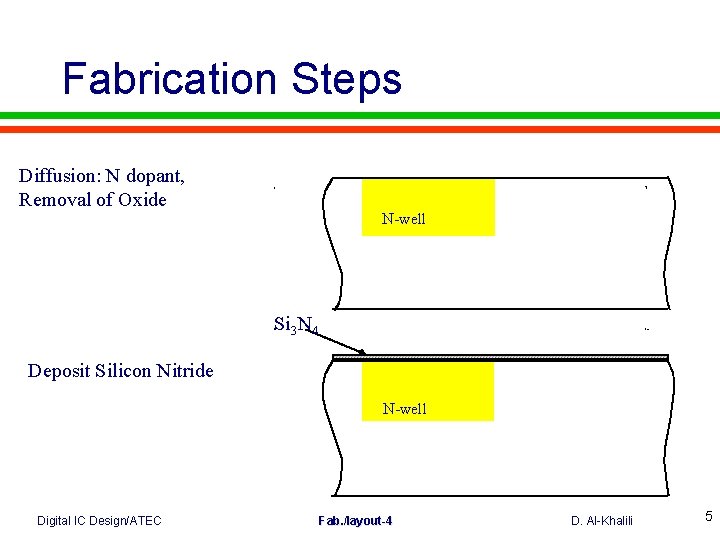

Fabrication Steps Diffusion: N dopant, Removal of Oxide N-well Si 3 N 4 Deposit Silicon Nitride N-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 5

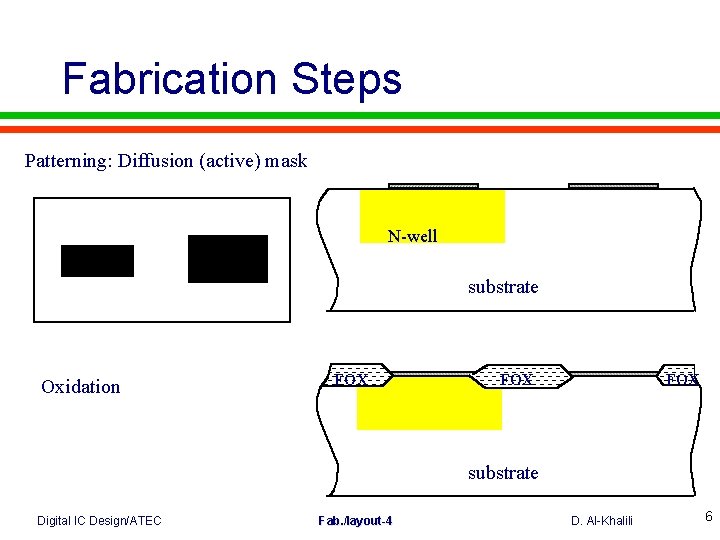

Fabrication Steps Patterning: Diffusion (active) mask N-well substrate Oxidation FOX FOX substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 6

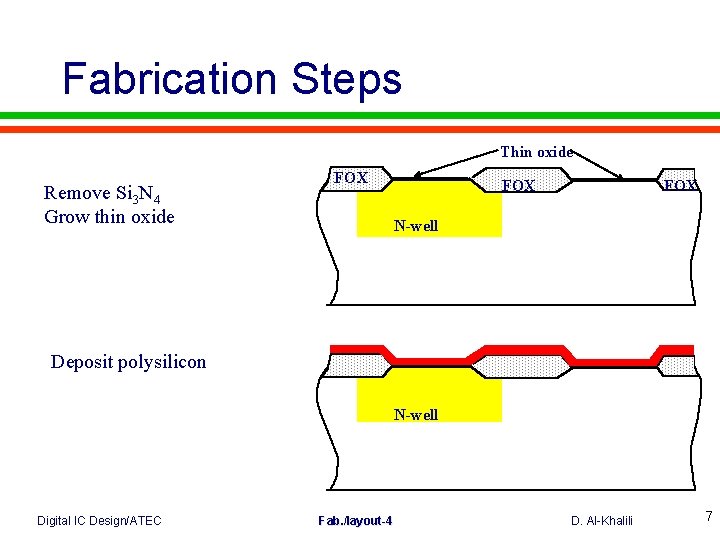

Fabrication Steps Thin oxide Remove Si 3 N 4 Grow thin oxide FOX FOX N-well Deposit polysilicon N-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 7

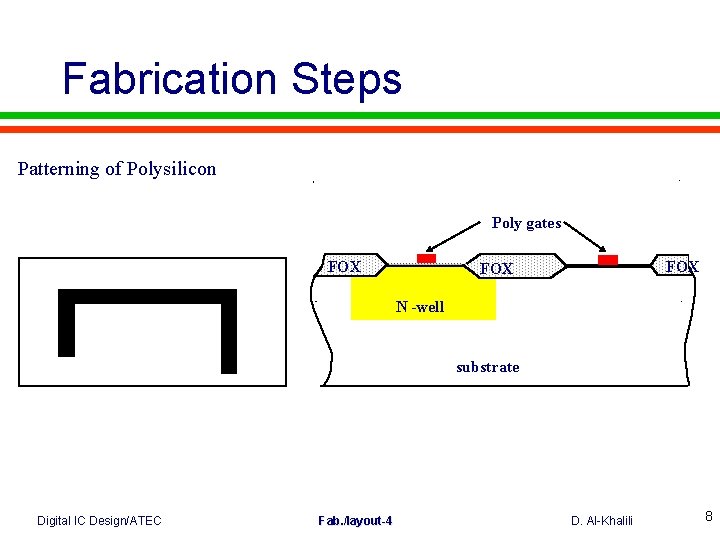

Fabrication Steps Patterning of Polysilicon Poly gates FOX FOX N -well substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 8

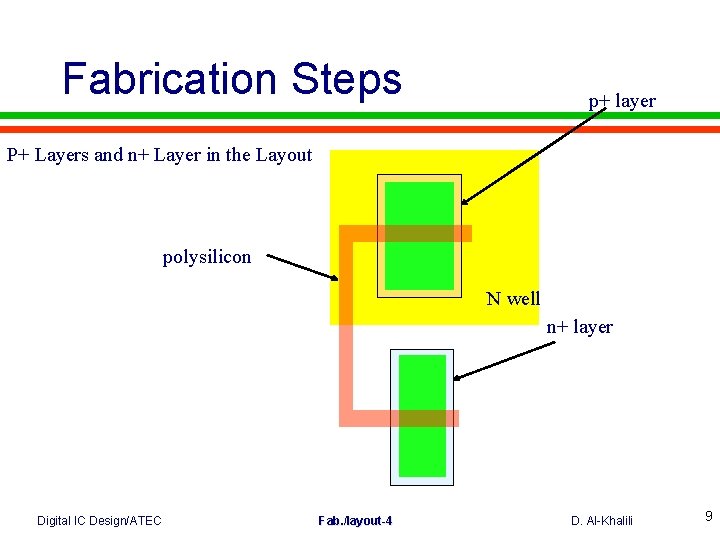

Fabrication Steps p+ layer P+ Layers and n+ Layer in the Layout polysilicon N well n+ layer Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 9

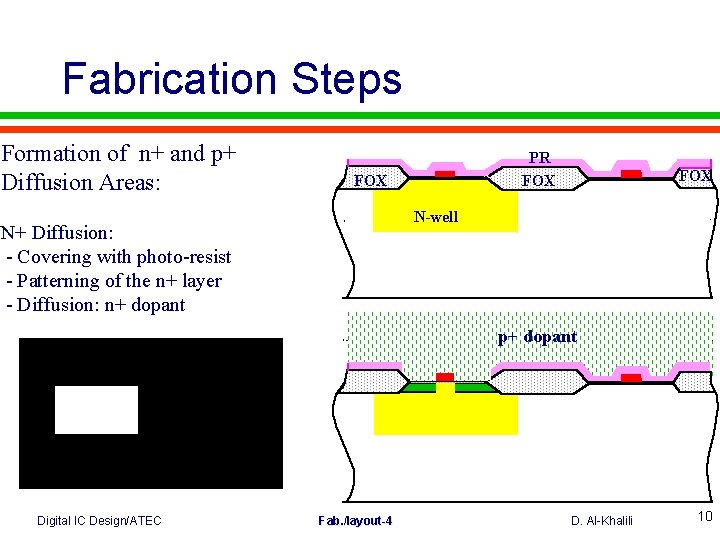

Fabrication Steps Formation of n+ and p+ Diffusion Areas: PR FOX FOX N-well N+ Diffusion: - Covering with photo-resist - Patterning of the n+ layer - Diffusion: n+ dopant p+ dopant Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 10

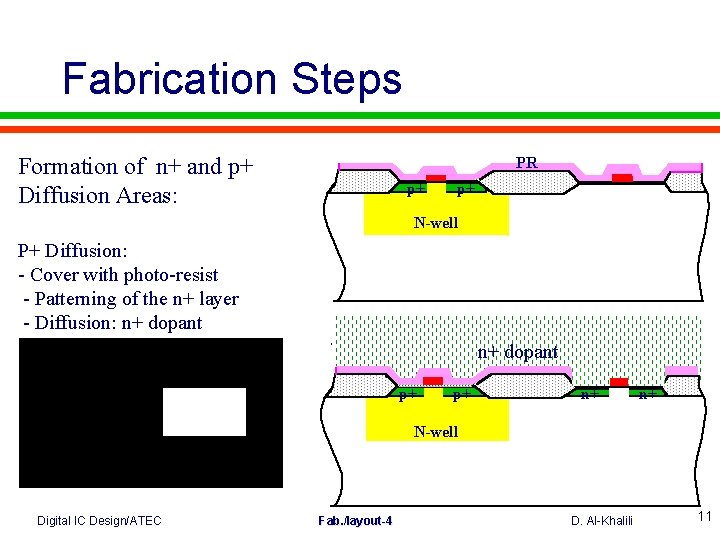

Fabrication Steps Formation of n+ and p+ Diffusion Areas: PR p+ p+ N-well P+ Diffusion: - Cover with photo-resist - Patterning of the n+ layer - Diffusion: n+ dopant p+ p+ n+ n+ N-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 11

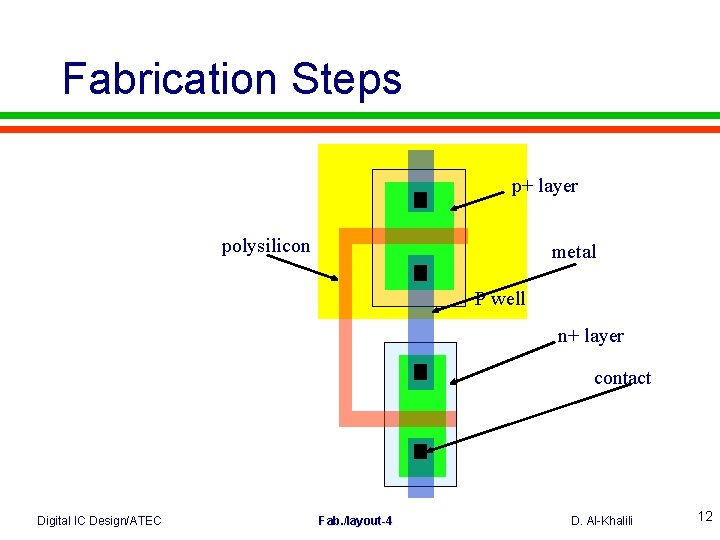

Fabrication Steps p+ layer polysilicon metal P well n+ layer contact Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 12

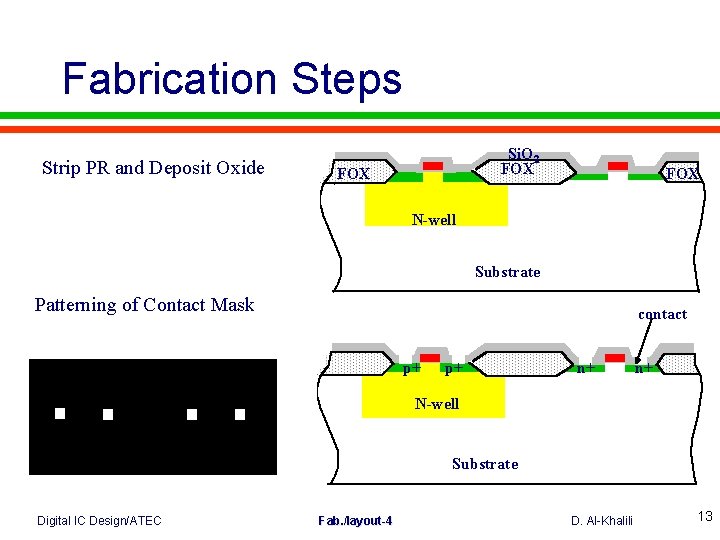

Fabrication Steps Strip PR and Deposit Oxide Si. O 2 FOX FOX N-well Substrate Patterning of Contact Mask contact p+ p+ n+ n+ N-well Substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 13

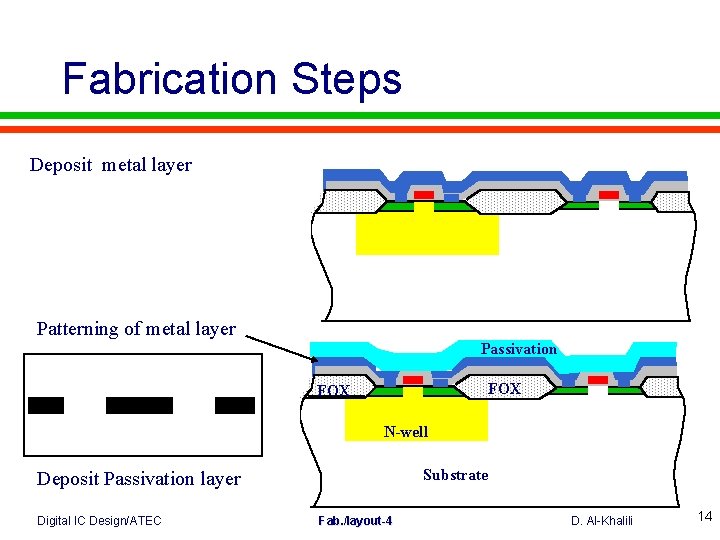

Fabrication Steps Deposit metal layer Patterning of metal layer Passivation FOX N-well Substrate Deposit Passivation layer Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 14

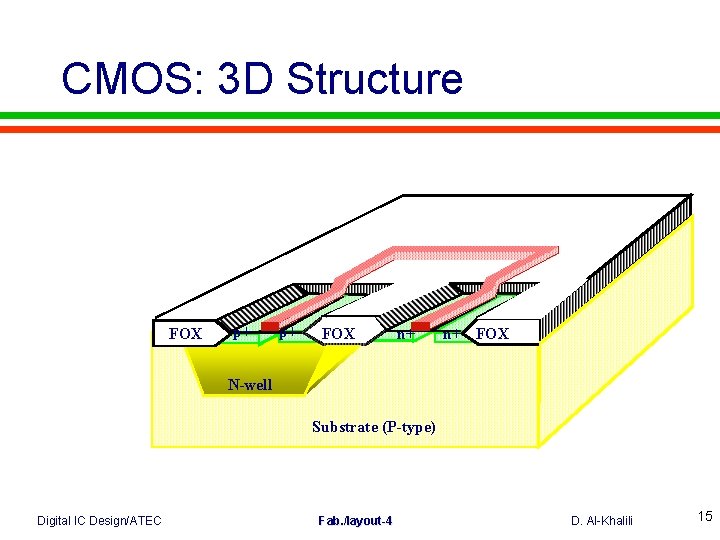

CMOS: 3 D Structure FOX p+ p+ FOX n+ n+ FOX N-well Substrate (P-type) Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 15

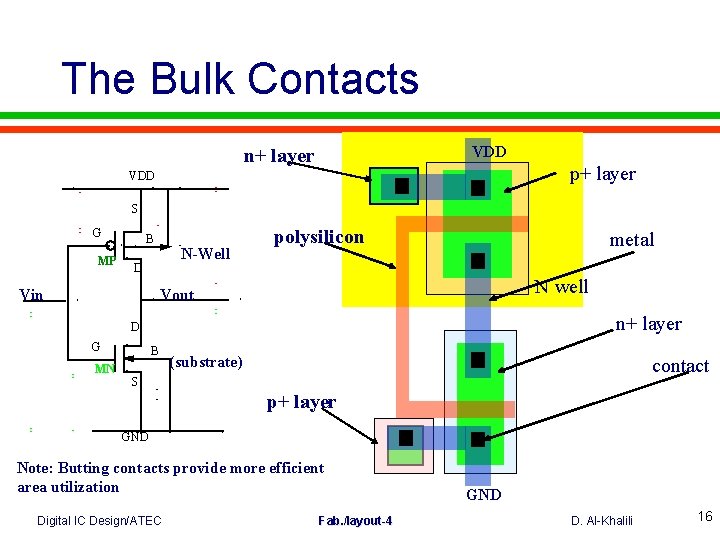

The Bulk Contacts VDD n+ layer p+ layer VDD S G MP B N-Well D Vin polysilicon metal N well Vout n+ layer D G MN B (substrate) contact S p+ layer GND Note: Butting contacts provide more efficient area utilization Digital IC Design/ATEC Fab. /layout-4 GND D. Al-Khalili 16

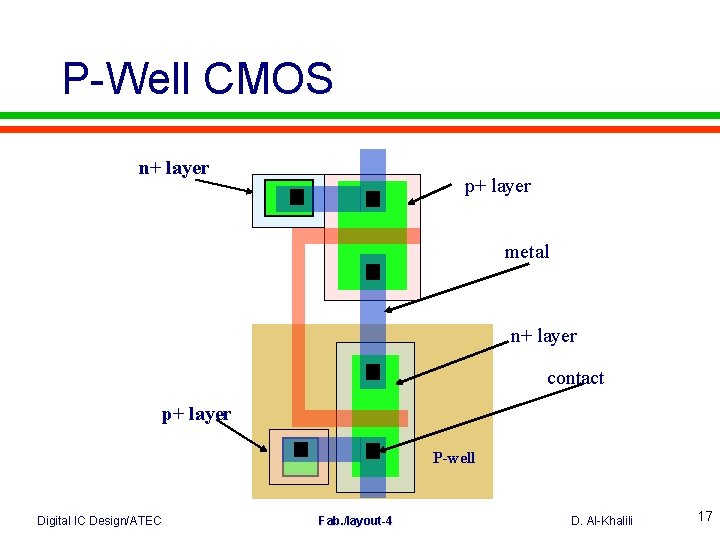

P-Well CMOS n+ layer p+ layer metal n+ layer contact p+ layer P-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 17

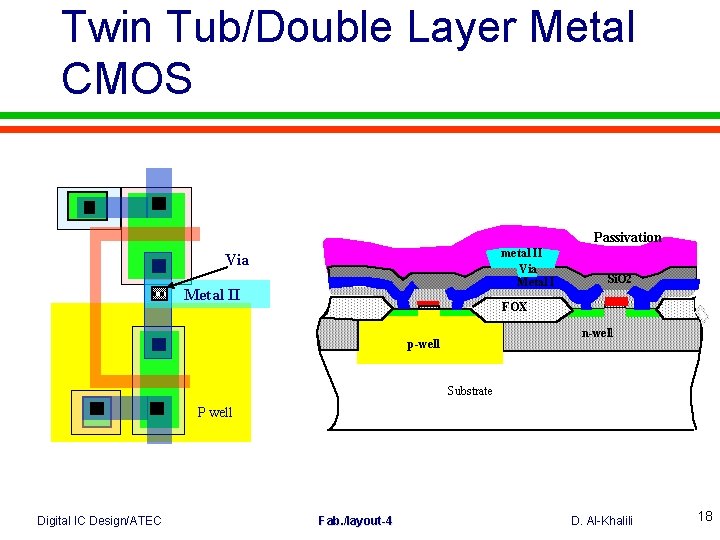

Twin Tub/Double Layer Metal CMOS Passivation metal II Via Metal II Si. O 2 FOX n-well p-well Substrate P well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 18

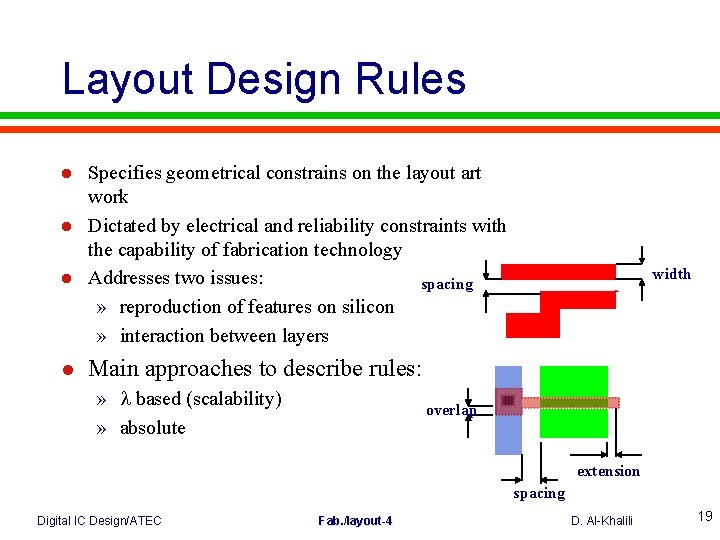

Layout Design Rules l l Specifies geometrical constrains on the layout art work Dictated by electrical and reliability constraints with the capability of fabrication technology Addresses two issues: spacing » reproduction of features on silicon » interaction between layers width Main approaches to describe rules: » based (scalability) » absolute overlap extension spacing Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 19

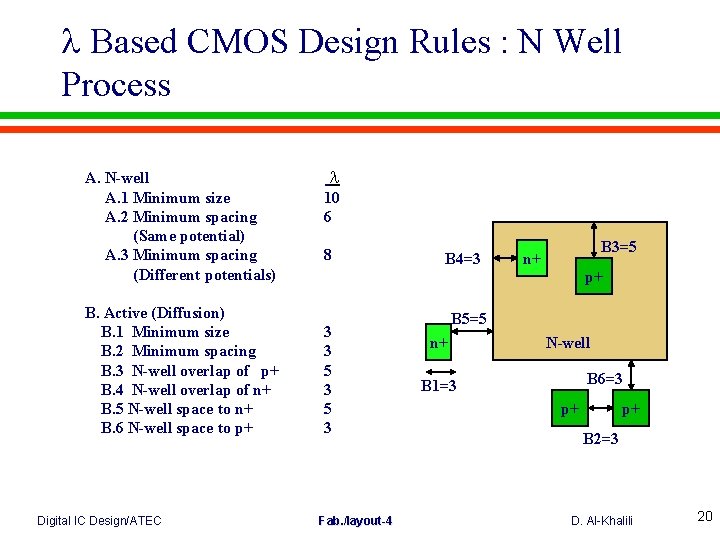

Based CMOS Design Rules : N Well Process A. N-well A. 1 Minimum size A. 2 Minimum spacing (Same potential) A. 3 Minimum spacing (Different potentials) B. Active (Diffusion) B. 1 Minimum size B. 2 Minimum spacing B. 3 N-well overlap of p+ B. 4 N-well overlap of n+ B. 5 N-well space to n+ B. 6 N-well space to p+ Digital IC Design/ATEC 10 6 8 B 4=3 B 3=5 n+ p+ 3 3 5 3 Fab. /layout-4 B 5=5 n+ N-well B 6=3 B 1=3 p+ p+ B 2=3 D. Al-Khalili 20

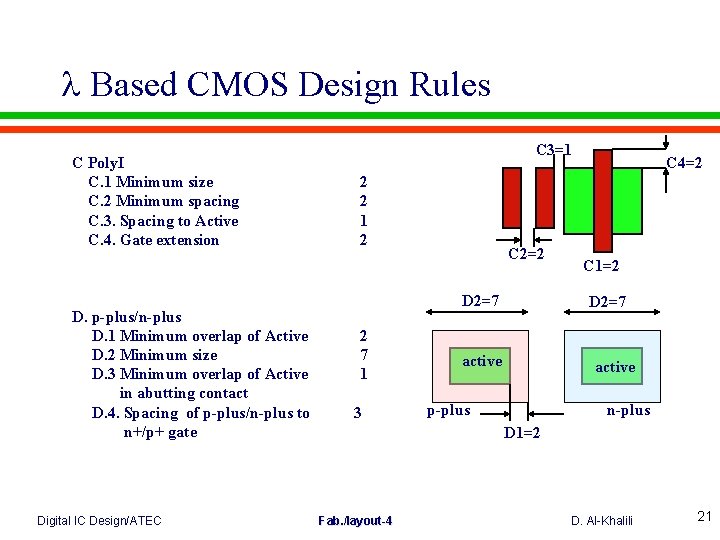

Based CMOS Design Rules C Poly. I C. 1 Minimum size C. 2 Minimum spacing C. 3. Spacing to Active C. 4. Gate extension D. p-plus/n-plus D. 1 Minimum overlap of Active D. 2 Minimum size D. 3 Minimum overlap of Active in abutting contact D. 4. Spacing of p-plus/n-plus to n+/p+ gate Digital IC Design/ATEC C 3=1 2 2 1 2 C 2=2 D 2=7 2 7 1 3 C 4=2 C 1=2 D 2=7 active p-plus n-plus D 1=2 Fab. /layout-4 D. Al-Khalili 21

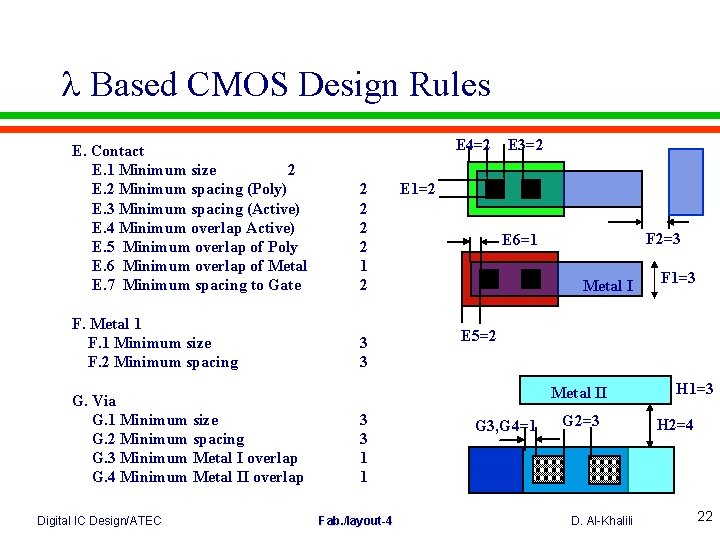

Based CMOS Design Rules E 4=2 E. Contact E. 1 Minimum size 2 E. 2 Minimum spacing (Poly) E. 3 Minimum spacing (Active) E. 4 Minimum overlap Active) E. 5 Minimum overlap of Poly E. 6 Minimum overlap of Metal E. 7 Minimum spacing to Gate 2 2 1 2 F. Metal 1 F. 1 Minimum size F. 2 Minimum spacing 3 3 G. Via G. 1 Minimum size G. 2 Minimum spacing G. 3 Minimum Metal I overlap G. 4 Minimum Metal II overlap Digital IC Design/ATEC E 3=2 E 1=2 F 2=3 E 6=1 Metal I E 5=2 Metal II 3 3 1 1 Fab. /layout-4 F 1=3 G 3, G 4=1 G 2=3 D. Al-Khalili H 1=3 H 2=4 22

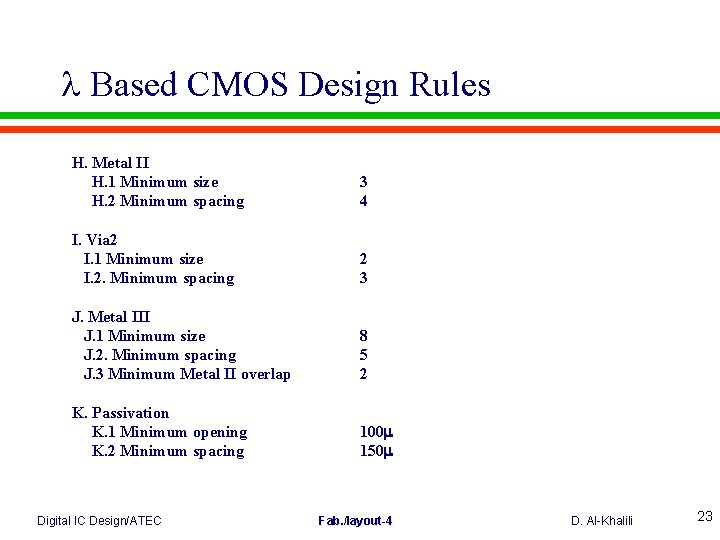

Based CMOS Design Rules H. Metal II H. 1 Minimum size H. 2 Minimum spacing 3 4 I. Via 2 I. 1 Minimum size I. 2. Minimum spacing 2 3 J. Metal III J. 1 Minimum size J. 2. Minimum spacing J. 3 Minimum Metal II overlap 8 5 2 K. Passivation K. 1 Minimum opening K. 2 Minimum spacing 100 m 150 m Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 23

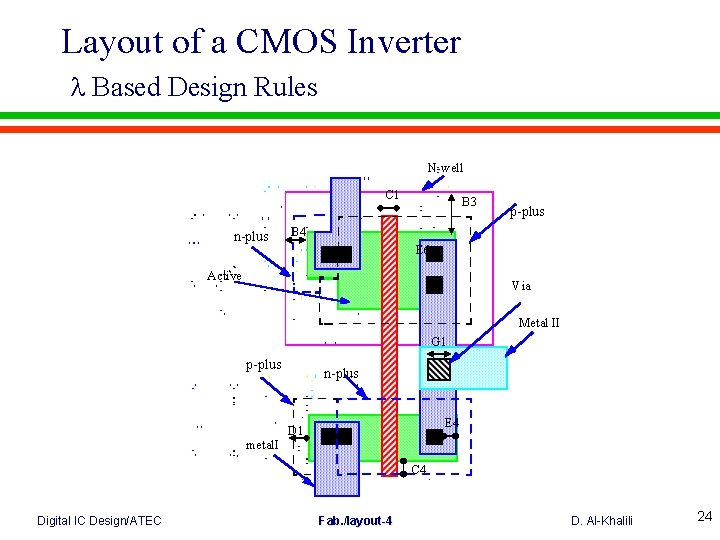

Layout of a CMOS Inverter Based Design Rules N-well C 1 n-plus B 3 p-plus B 4 E 6 Active Via Metal II G 1 p-plus metal. I n-plus E 4 D 1 C 4 Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 24

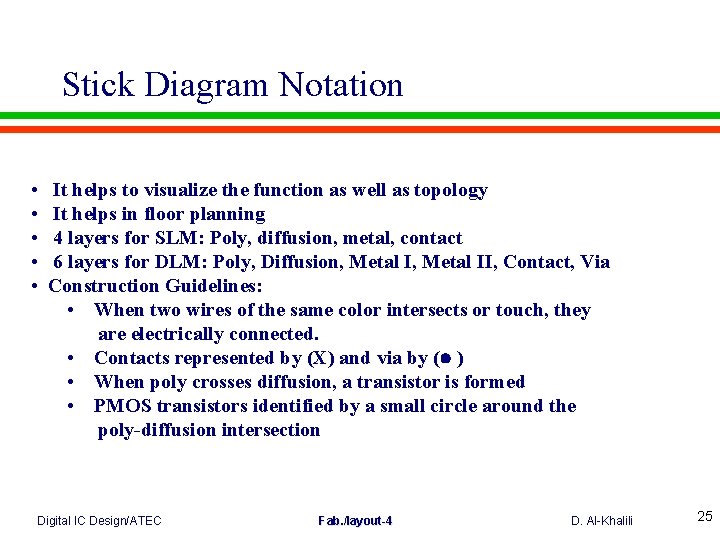

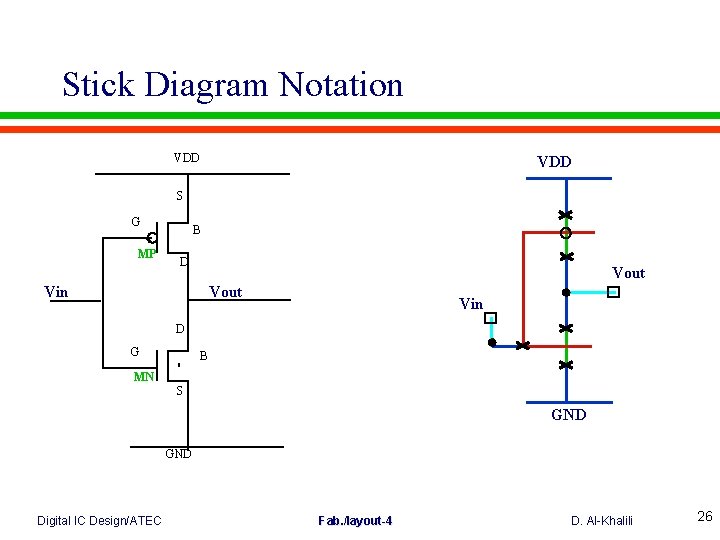

Stick Diagram Notation • • • It helps to visualize the function as well as topology It helps in floor planning 4 layers for SLM: Poly, diffusion, metal, contact 6 layers for DLM: Poly, Diffusion, Metal II, Contact, Via Construction Guidelines: • When two wires of the same color intersects or touch, they are electrically connected. • Contacts represented by (X) and via by ( ) • When poly crosses diffusion, a transistor is formed • PMOS transistors identified by a small circle around the poly-diffusion intersection Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 25

Stick Diagram Notation VDD S G MP B D Vout Vin D G B MN S GND Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 26

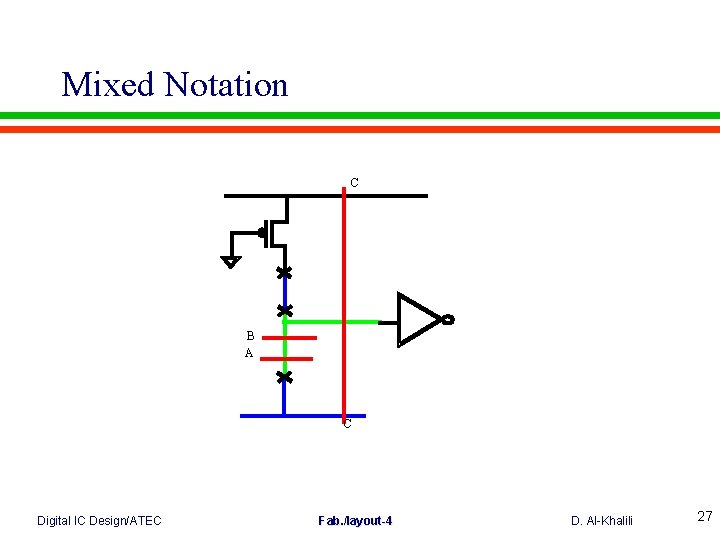

Mixed Notation C B A C Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 27

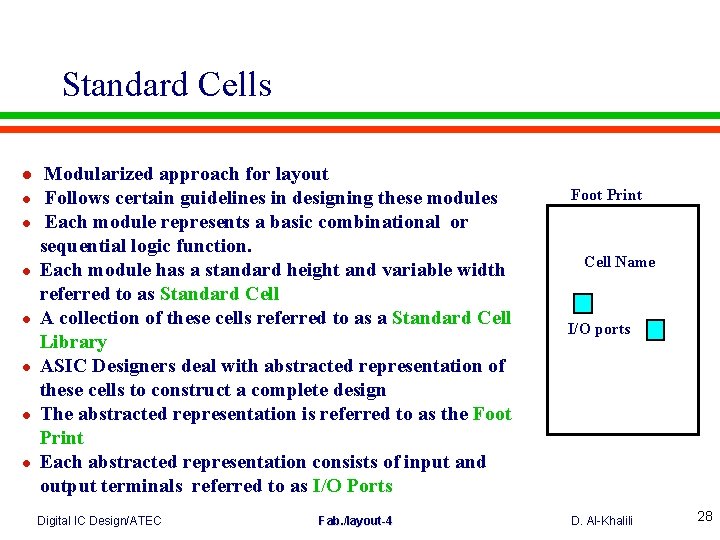

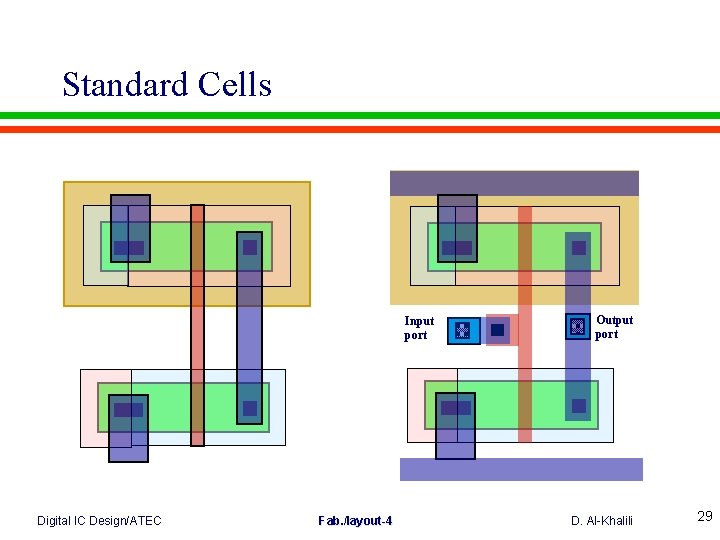

Standard Cells l l l l Modularized approach for layout Follows certain guidelines in designing these modules Each module represents a basic combinational or sequential logic function. Each module has a standard height and variable width referred to as Standard Cell A collection of these cells referred to as a Standard Cell Library ASIC Designers deal with abstracted representation of these cells to construct a complete design The abstracted representation is referred to as the Foot Print Each abstracted representation consists of input and output terminals referred to as I/O Ports I/O ports Digital IC Design/ATEC D. Al-Khalili Fab. /layout-4 Foot Print Cell Name 28

Standard Cells Input port Digital IC Design/ATEC Fab. /layout-4 Output port D. Al-Khalili 29

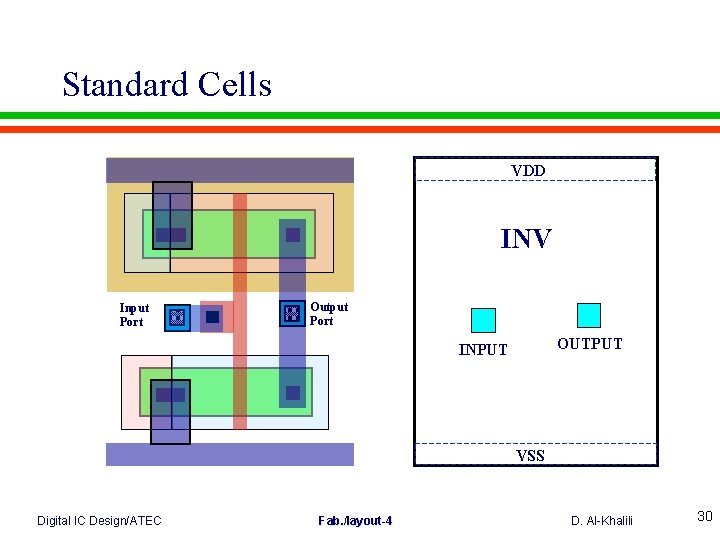

Standard Cells VDD INV Input Port Output Port OUTPUT INPUT VSS Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 30

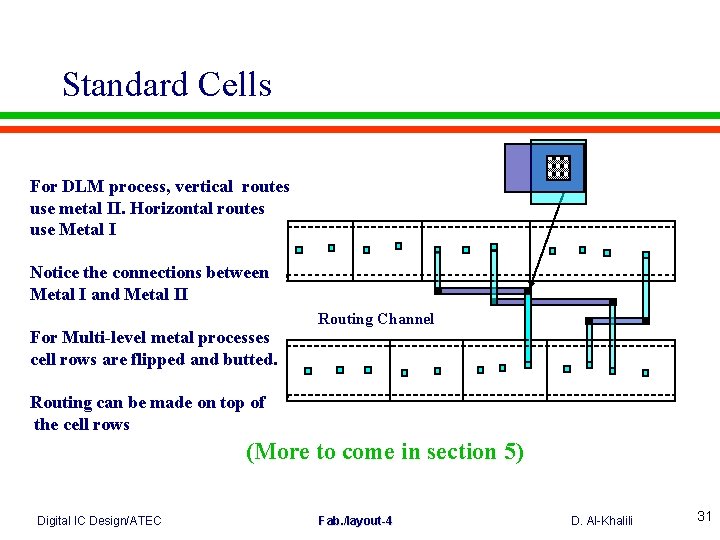

Standard Cells For DLM process, vertical routes use metal II. Horizontal routes use Metal I Notice the connections between Metal I and Metal II For Multi-level metal processes cell rows are flipped and butted. Routing Channel Routing can be made on top of the cell rows (More to come in section 5) Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 31

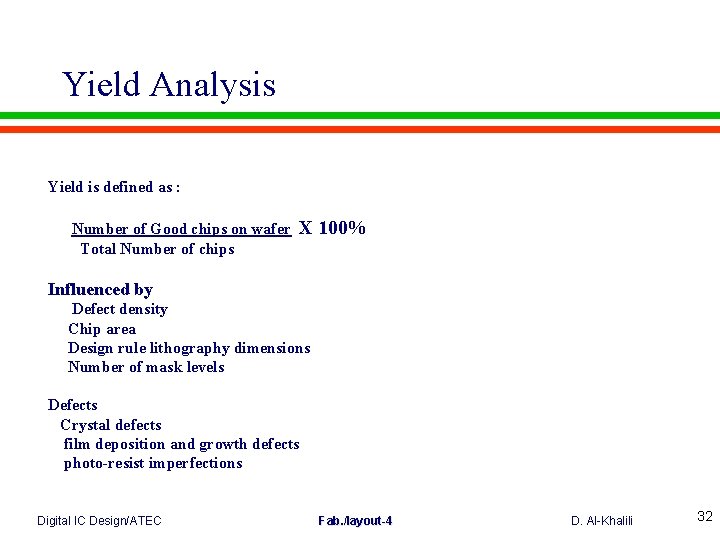

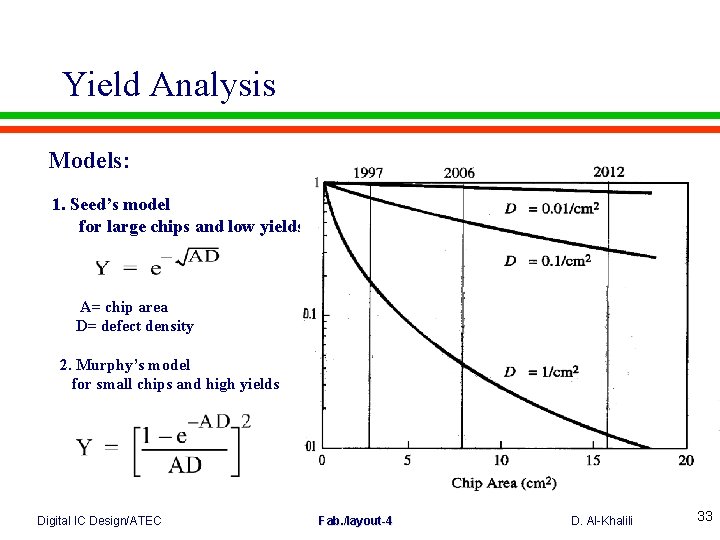

Yield Analysis Yield is defined as : Number of Good chips on wafer Total Number of chips X 100% Influenced by Defect density Chip area Design rule lithography dimensions Number of mask levels Defects Crystal defects film deposition and growth defects photo-resist imperfections Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 32

Yield Analysis Models: 1. Seed’s model for large chips and low yields A= chip area D= defect density 2. Murphy’s model for small chips and high yields Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 33

- Slides: 33