FABRICAO DE CIs EM TECNOLOGIA CMOS Ana Isabela

FABRICAÇÃO DE CI’s EM TECNOLOGIA CMOS Ana Isabela A. Cunha UFBA

SUMÁRIO Ø ETAPAS BÁSICAS DO PROCESSO DE CI’s Ø SEQÜÊNCIA DE PROCESSO CMOS Ø O “LATCH-UP” Ø REFERÊNCIAS

ETAPAS BÁSICAS DO PROCESSO

PONTO DE PARTIDA “Wafer”: bolacha de silício monocristalino diâmetro: 75 mm a 230 mm espessura: < 1 mm • Método de Czochralski: produção de silício monocristalino pela imersão e arraste de uma semente em uma pasta de silício policristalino (alta temperatura), acompanhados de rotação e resfriamento

EPITAXIA Crescimento de filme de silício sobre o “wafer” Temperaturas altas: 1000 a 1200 o. C Ambiente: Si. H 4 Replicação da estrutura cristalina do “wafer” Possibilidade de dopagem não uniforme do substrato

DEPOSIÇÃO DE FILME Filmes utilizados: Função do filme: Dióxido de Silício Separação entre canal e porta (Si. O 2) Isolação entre camadas de conexão Proteção seletiva contra implantação iônica Nitreto de Silício Isolação (Si 3 N 4) Proteção seletiva contra oxidação Polissilício Portas de transistores (“gates”) (silício policristalino) Interconexões Resistores Metal (alumínio ou ligas) Interconexões

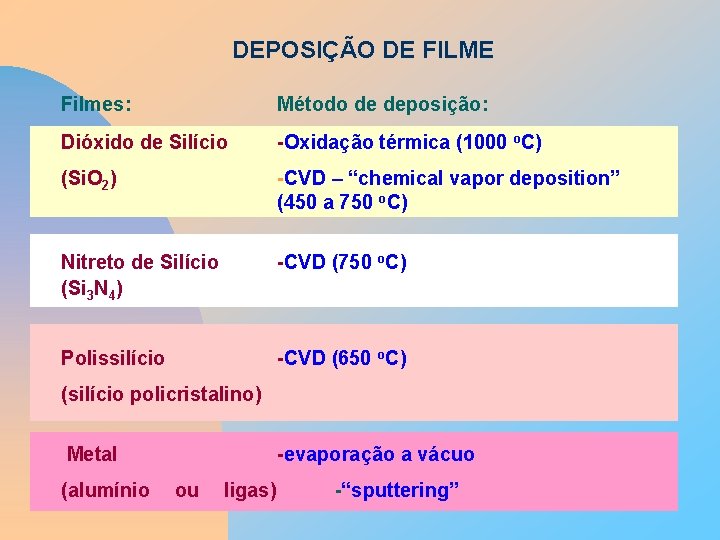

DEPOSIÇÃO DE FILME Filmes: Método de deposição: Dióxido de Silício -Oxidação térmica (1000 o. C) (Si. O 2) -CVD – “chemical vapor deposition” (450 a 750 o. C) Nitreto de Silício (Si 3 N 4) -CVD (750 o. C) Polissilício -CVD (650 o. C) (silício policristalino) Metal -evaporação a vácuo (alumínio ou ligas) -“sputtering”

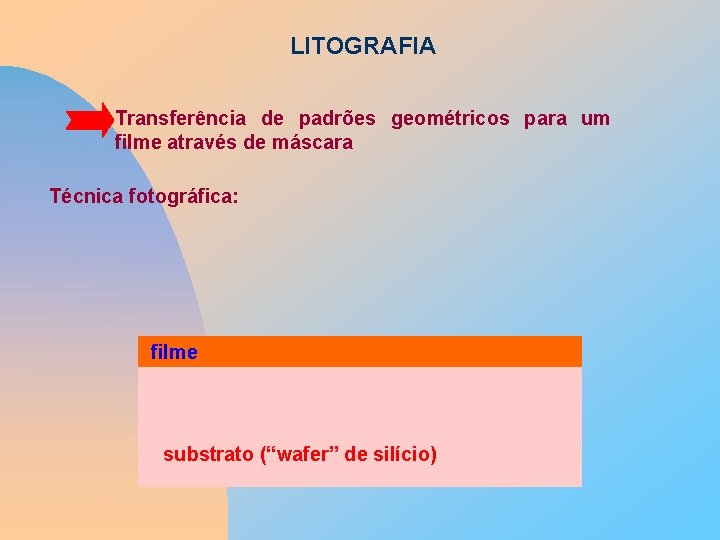

LITOGRAFIA Transferência de padrões geométricos para um filme através de máscara Técnica fotográfica: filme substrato (“wafer” de silício)

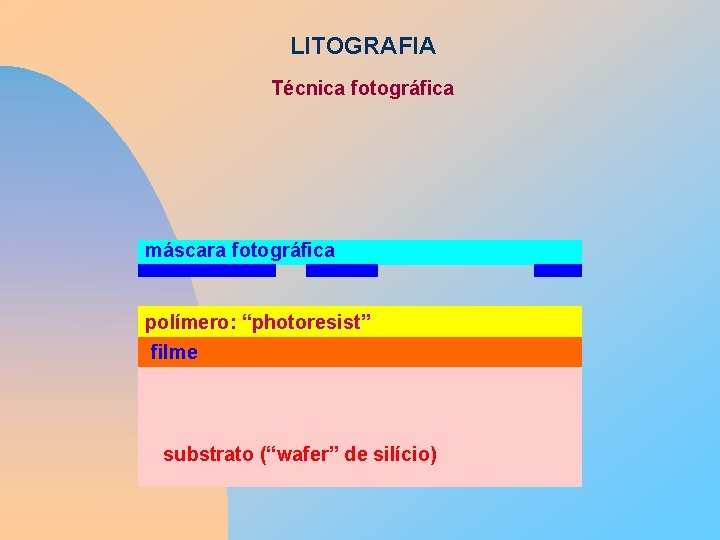

LITOGRAFIA Técnica fotográfica polímero: “photoresist” filme substrato (“wafer” de silício)

LITOGRAFIA Técnica fotográfica máscara fotográfica polímero: “photoresist” filme substrato (“wafer” de silício)

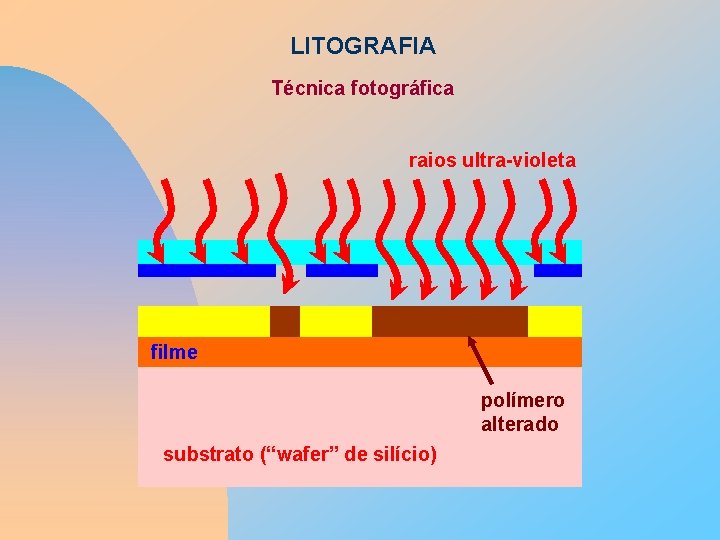

LITOGRAFIA Técnica fotográfica raios ultra-violeta filme polímero alterado substrato (“wafer” de silício)

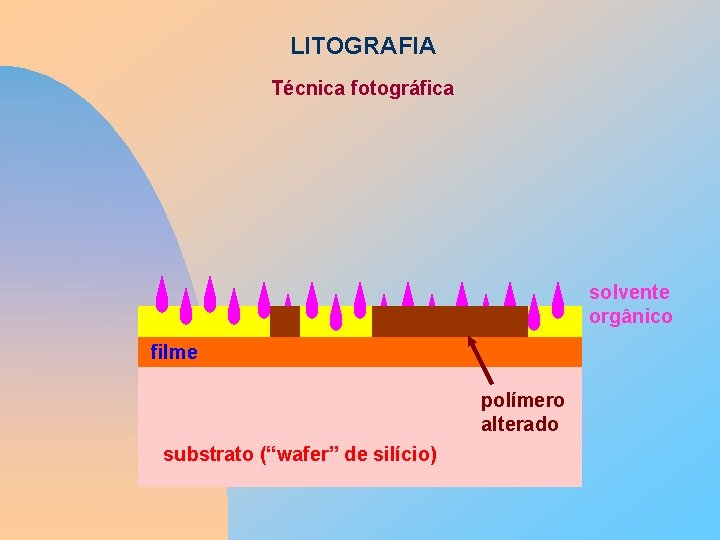

LITOGRAFIA Técnica fotográfica solvente orgânico filme polímero alterado substrato (“wafer” de silício)

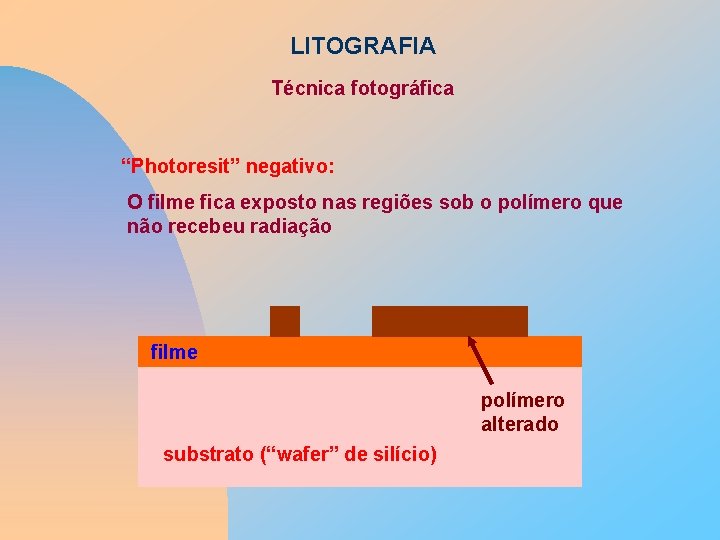

LITOGRAFIA Técnica fotográfica “Photoresit” negativo: O filme fica exposto nas regiões sob o polímero que não recebeu radiação filme polímero alterado substrato (“wafer” de silício)

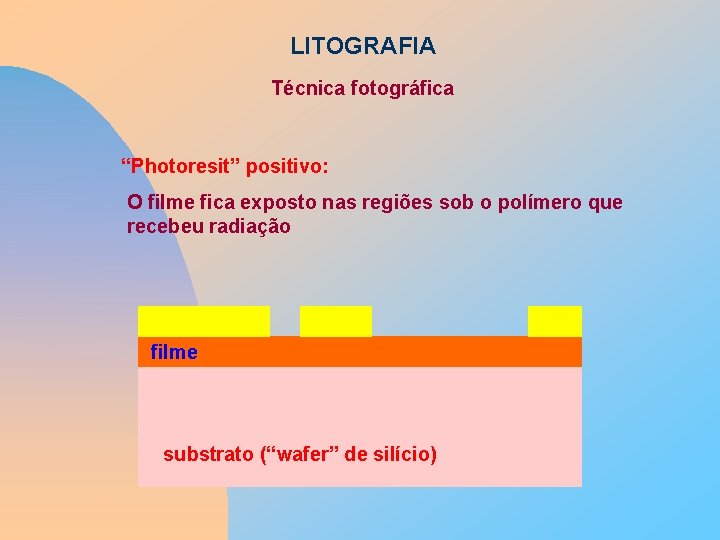

LITOGRAFIA Técnica fotográfica “Photoresit” positivo: O filme fica exposto nas regiões sob o polímero que recebeu radiação filme substrato (“wafer” de silício)

CORROSÃO Remoção seletiva de porções de um filme depositado por exposição a um reagente químico photoresist filme substrato (“wafer” de silício) Anisotropia da corrosão: grau de precisão na reprodução da máscara - maior em ambientes secos que em ambientes úmidos

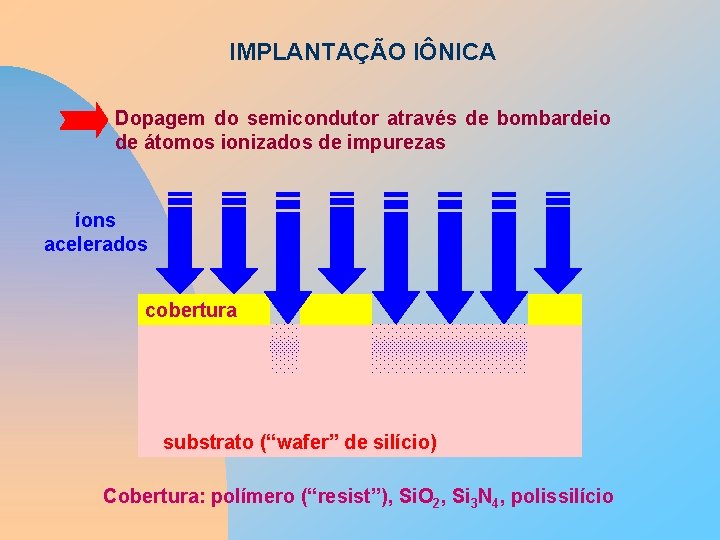

IMPLANTAÇÃO IÔNICA Dopagem do semicondutor através de bombardeio de átomos ionizados de impurezas íons acelerados cobertura substrato (“wafer” de silício) Cobertura: polímero (“resist”), Si. O 2, Si 3 N 4, polissilício

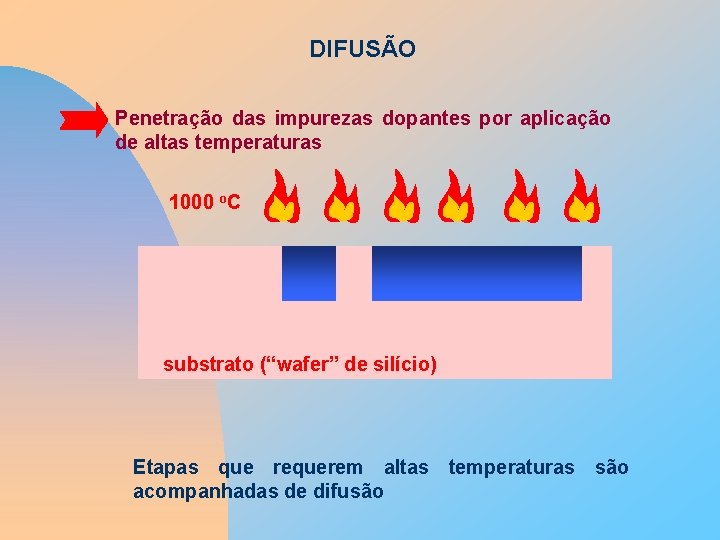

DIFUSÃO Penetração das impurezas dopantes por aplicação de altas temperaturas 1000 o. C substrato (“wafer” de silício) Etapas que requerem altas temperaturas são acompanhadas de difusão

SEQÜÊNCIA DE PROCESSO CMOS

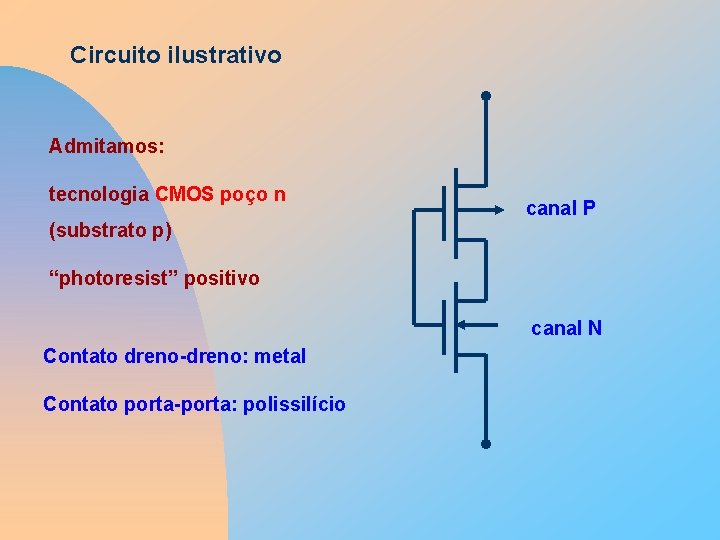

Circuito ilustrativo Admitamos: tecnologia CMOS poço n (substrato p) canal P “photoresist” positivo canal N Contato dreno-dreno: metal Contato porta-porta: polissilício

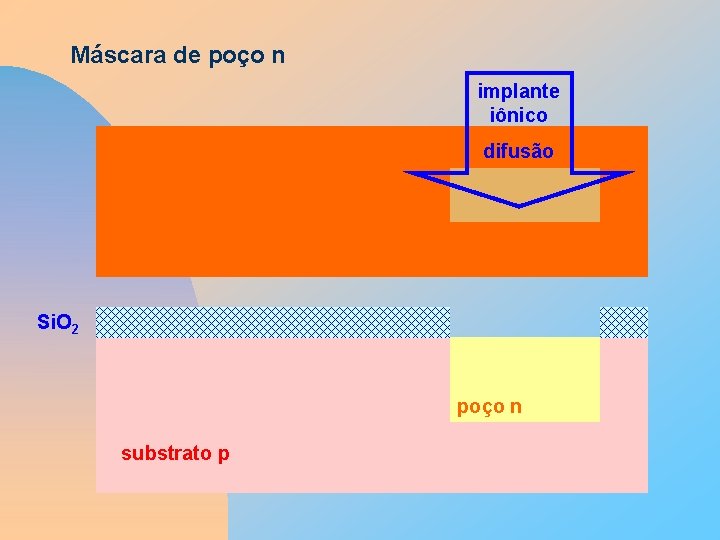

Máscara de poço n implante iônico difusão Si. O 2 poço n substrato p

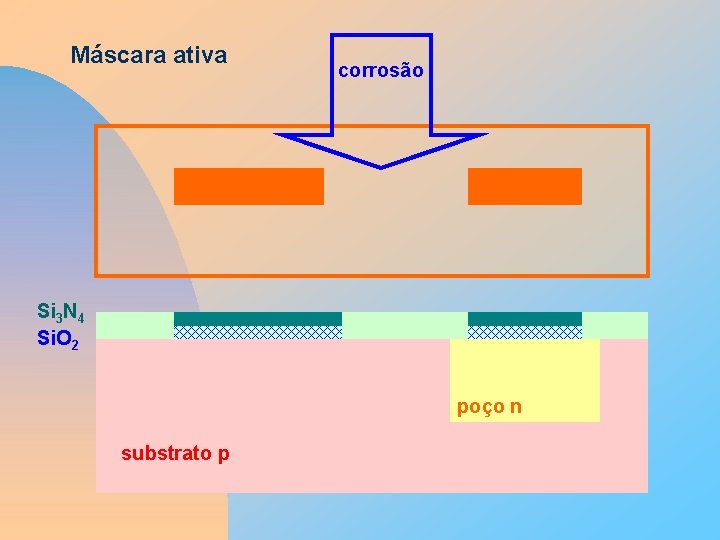

Máscara ativa corrosão Si 3 N 4 Si. O 2 poço n substrato p

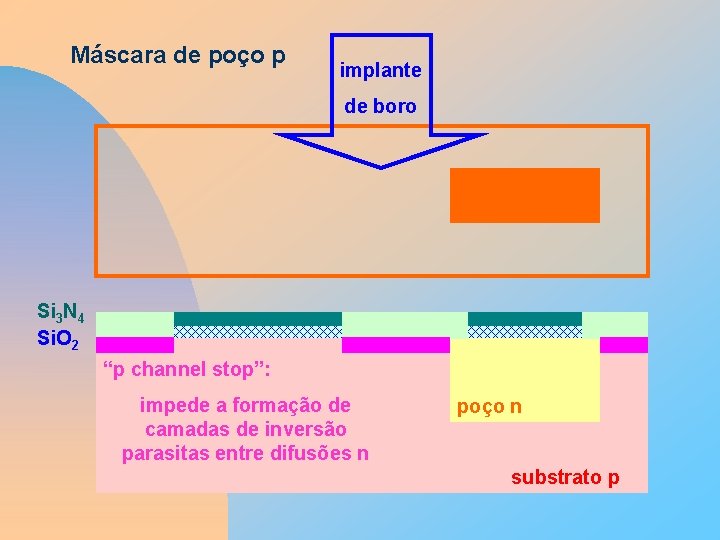

Máscara de poço p implante de boro Si 3 N 4 Si. O 2 “p channel stop”: impede a formação de camadas de inversão parasitas entre difusões n poço n substrato p

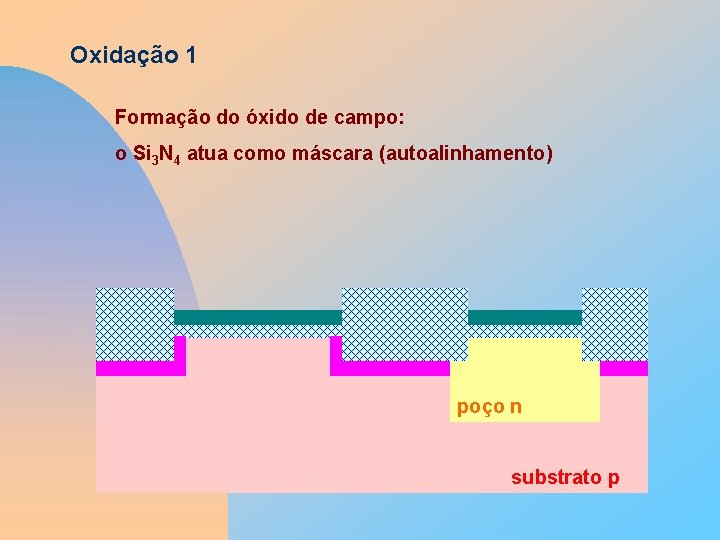

Oxidação 1 Formação do óxido de campo: o Si 3 N 4 atua como máscara (autoalinhamento) poço n substrato p

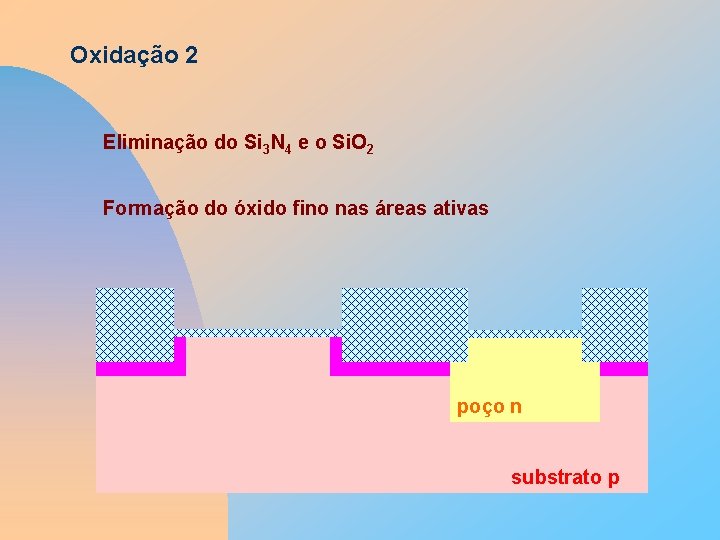

Oxidação 2 Eliminação do Si 3 N 4 e o Si. O 2 Formação do óxido fino nas áreas ativas poço n substrato p

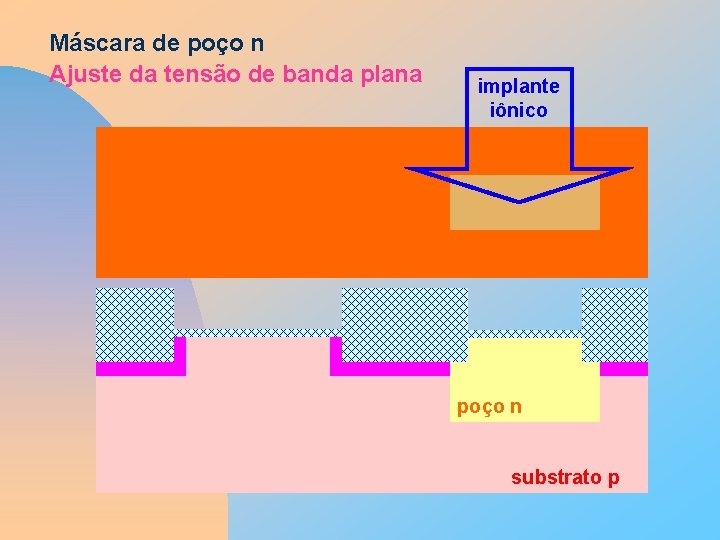

Máscara de poço n Ajuste da tensão de banda plana implante iônico poço n substrato p

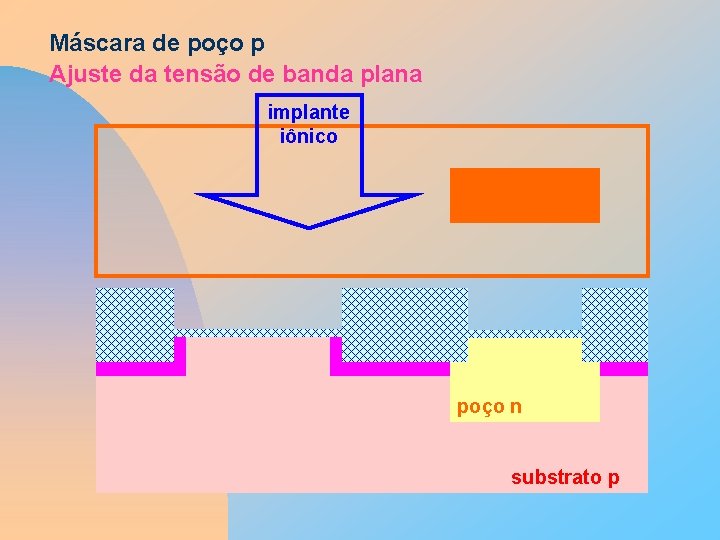

Máscara de poço p Ajuste da tensão de banda plana implante iônico poço n substrato p

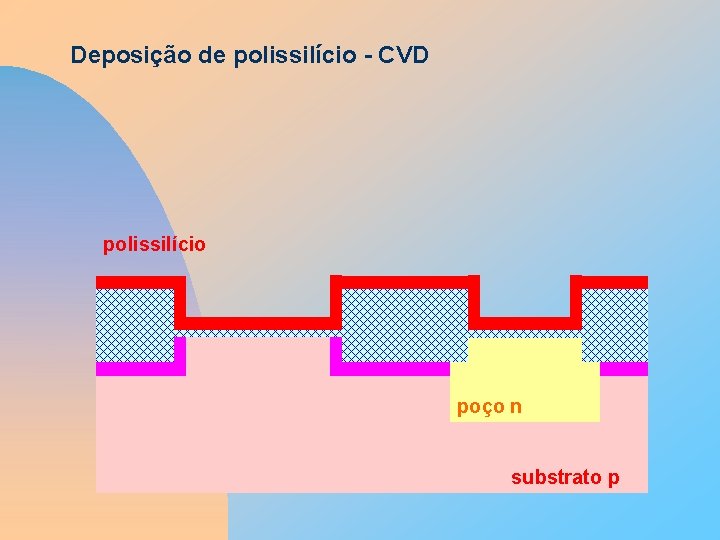

Deposição de polissilício - CVD polissilício poço n substrato p

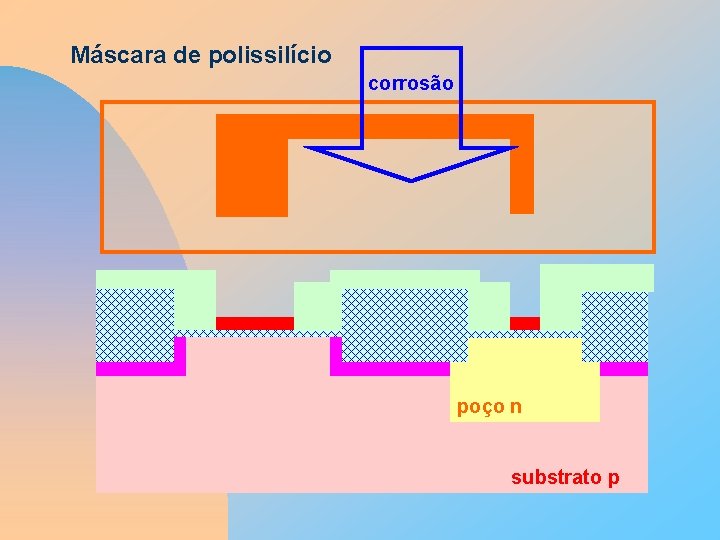

Máscara de polissilício corrosão poço n substrato p

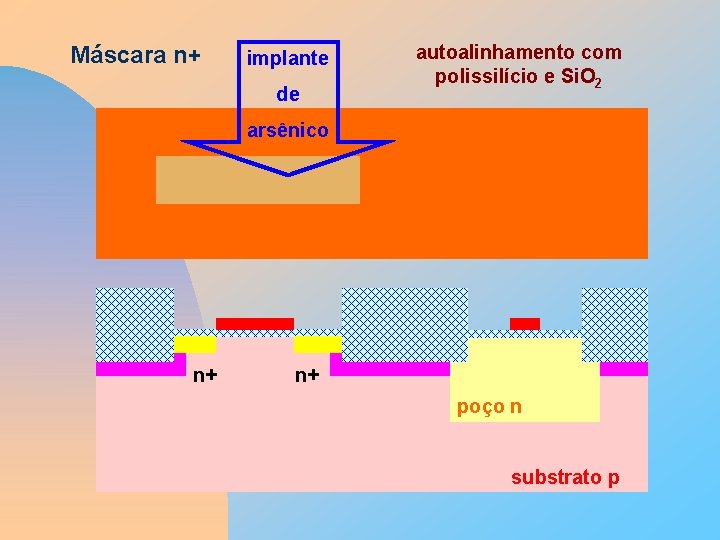

Máscara n+ implante de autoalinhamento com polissilício e Si. O 2 arsênico n+ n+ poço n substrato p

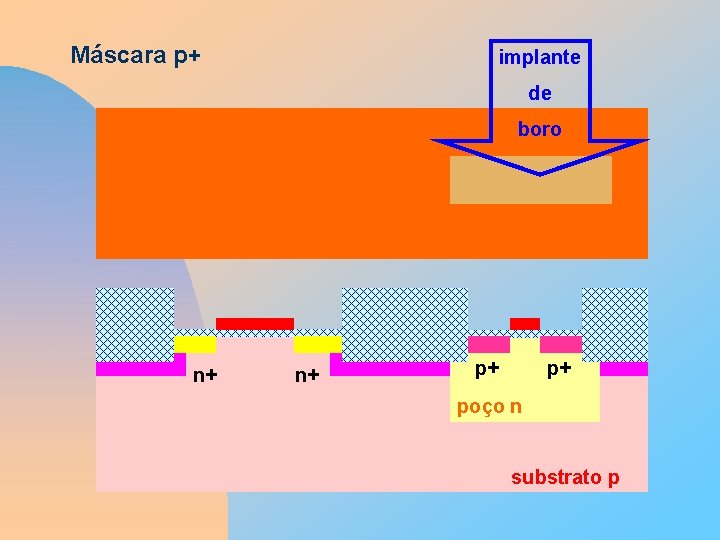

Máscara p+ implante de boro n+ n+ p+ p+ poço n substrato p

Deposição de PSG (“phosilicate glass”) = Si. O 2 dopado com fósforo Isolação: metal n+, polissilício PSG n+ n+ p+ p+ poço n substrato p

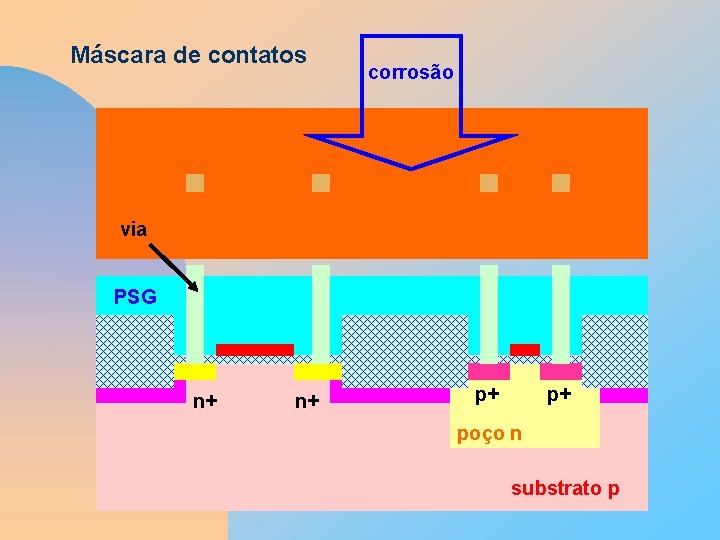

Máscara de contatos corrosão via PSG n+ n+ p+ p+ poço n substrato p

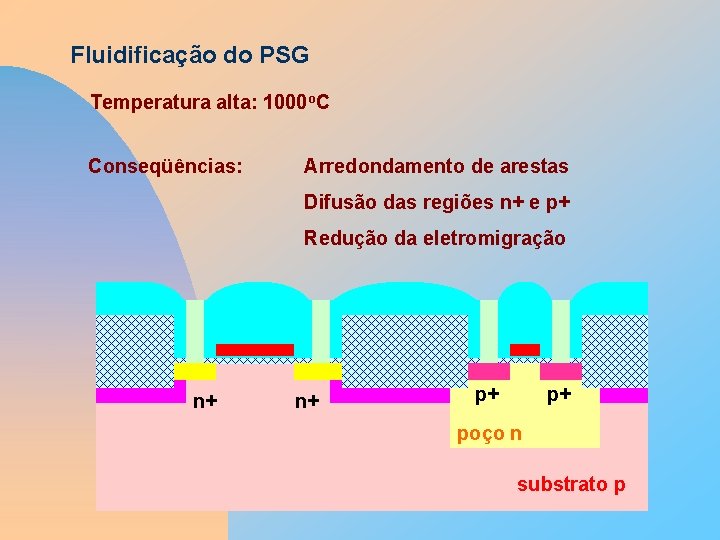

Fluidificação do PSG Temperatura alta: 1000 o. C Conseqüências: Arredondamento de arestas Difusão das regiões n+ e p+ Redução da eletromigração n+ n+ p+ p+ poço n substrato p

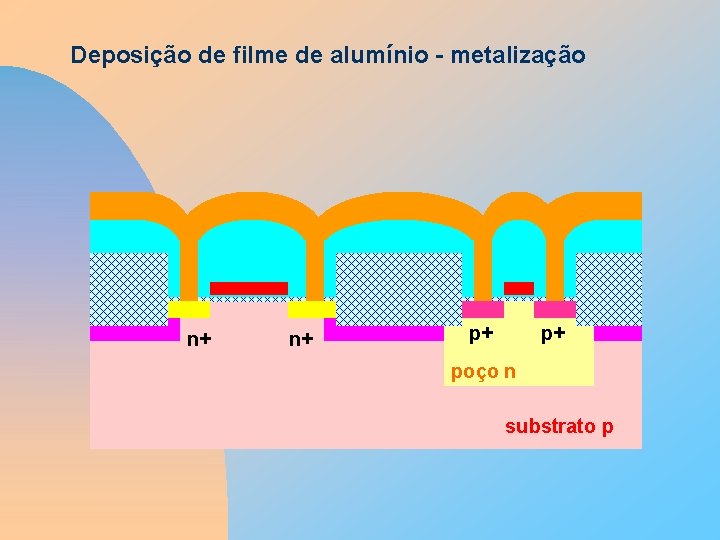

Deposição de filme de alumínio - metalização n+ n+ p+ p+ poço n substrato p

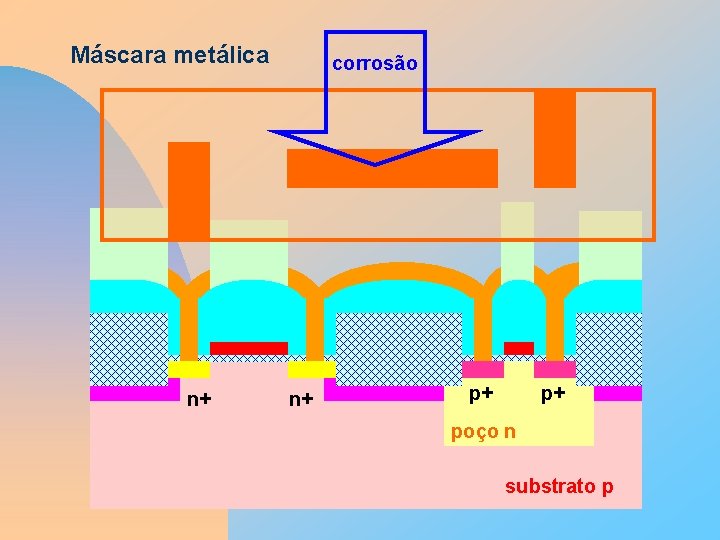

Máscara metálica n+ corrosão n+ p+ p+ poço n substrato p

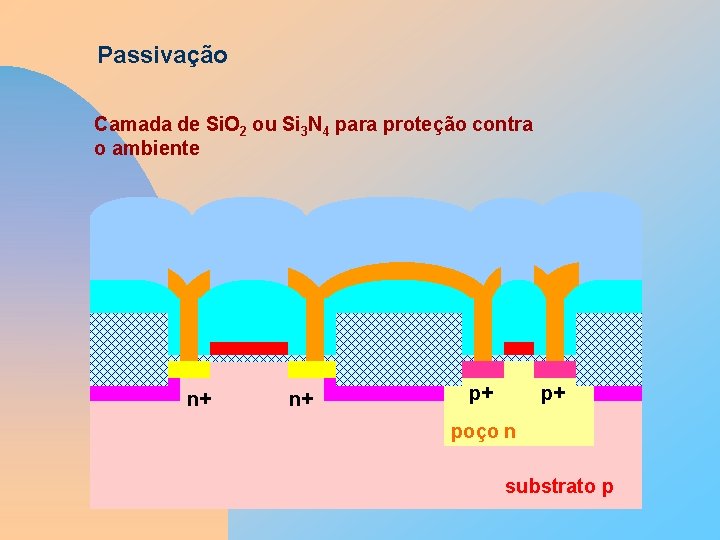

Passivação Camada de Si. O 2 ou Si 3 N 4 para proteção contra o ambiente n+ n+ p+ p+ poço n substrato p

O “LATCH-UP”

Estruturas parasitas num circuito inversor VSS p+ n+ VDD n+ p+ p+ n+ NPN Rsub n- p. VSS = tensão mais negativa VDD = tensão mais positiva PNP Rwell

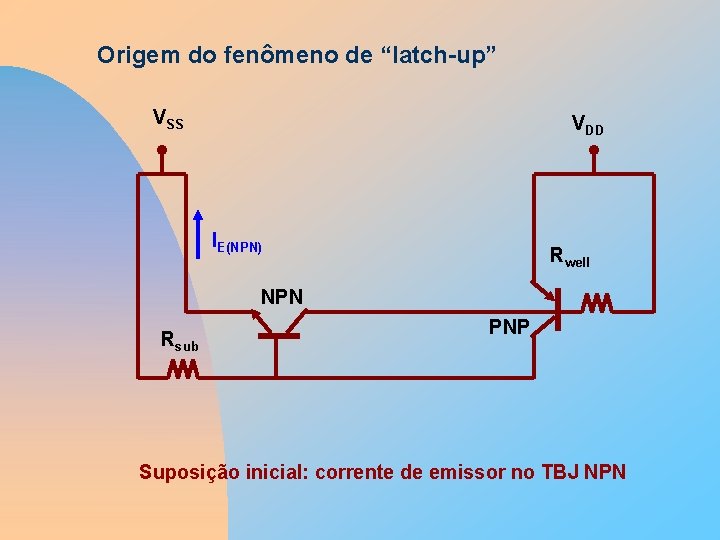

Origem do fenômeno de “latch-up” VSS VDD IE(NPN) Rwell NPN Rsub PNP Suposição inicial: corrente de emissor no TBJ NPN

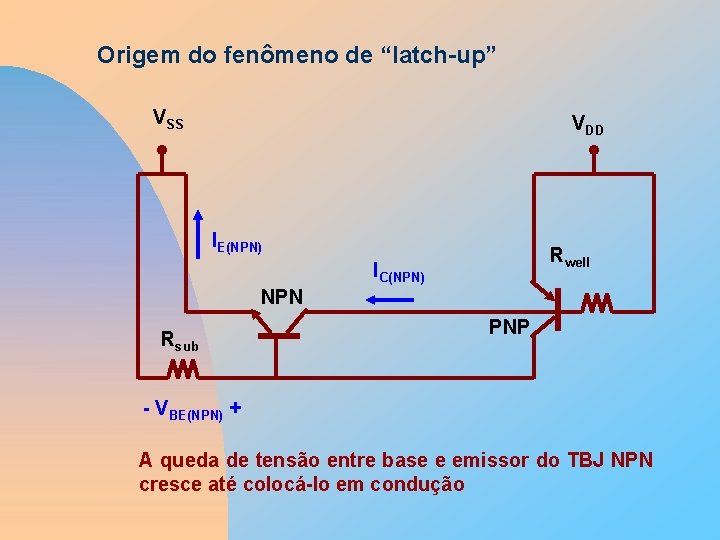

Origem do fenômeno de “latch-up” VSS VDD IE(NPN) Rwell IC(NPN) NPN Rsub PNP - VBE(NPN) + A queda de tensão entre base e emissor do TBJ NPN cresce até colocá-lo em condução

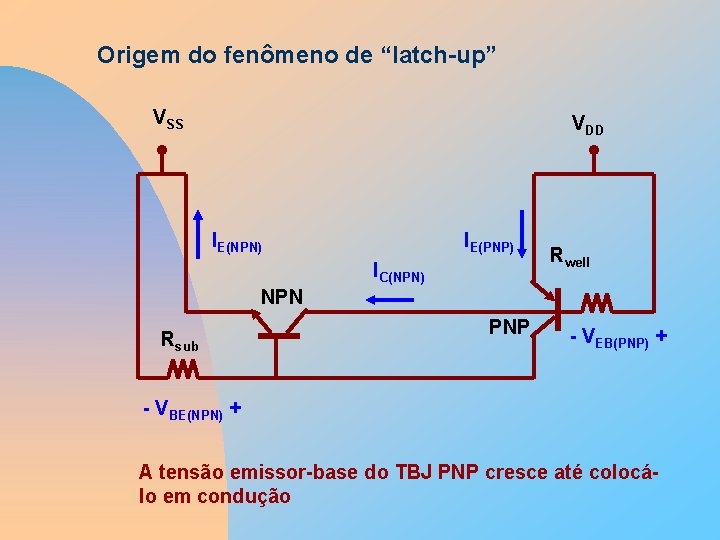

Origem do fenômeno de “latch-up” VSS VDD IE(NPN) IE(PNP) IC(NPN) Rwell NPN Rsub PNP - VEB(PNP) + - VBE(NPN) + A tensão emissor-base do TBJ PNP cresce até colocálo em condução

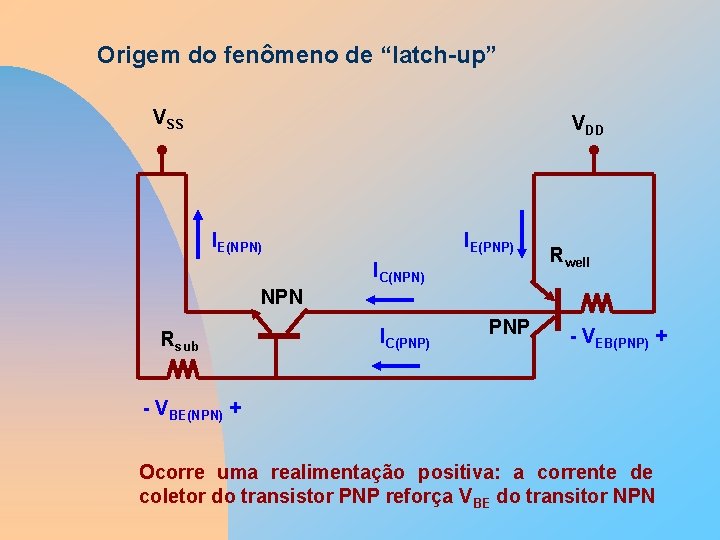

Origem do fenômeno de “latch-up” VSS VDD IE(NPN) IE(PNP) IC(NPN) Rwell NPN Rsub IC(PNP) PNP - VEB(PNP) + - VBE(NPN) + Ocorre uma realimentação positiva: a corrente de coletor do transistor PNP reforça VBE do transitor NPN

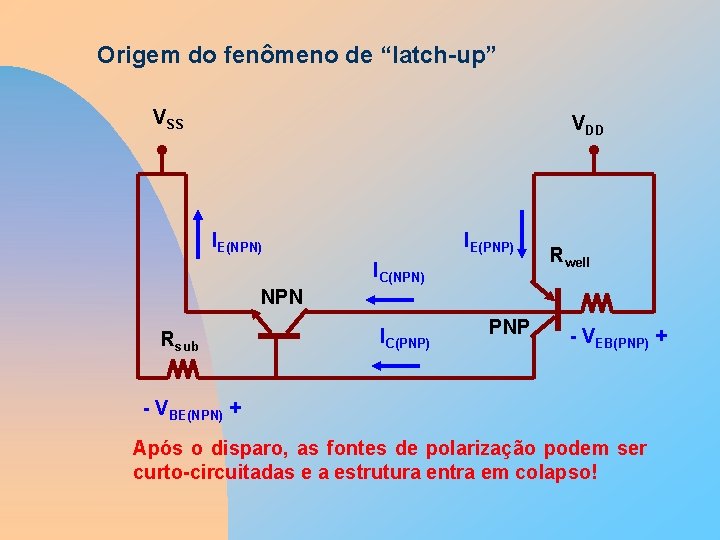

Origem do fenômeno de “latch-up” VSS VDD IE(NPN) IE(PNP) IC(NPN) Rwell NPN Rsub IC(PNP) PNP - VEB(PNP) + - VBE(NPN) + Após o disparo, as fontes de polarização podem ser curto-circuitadas e a estrutura entra em colapso!

Medidas para evitar o “latch-up” Distanciar as regiões n+ (MOSFET canal N) e p+ (MOSFET canal P) para diminuir o ganho b dos TBJ’s Introduzir vários contatos p+ para o substrato, próximos entre si, para diminuir RSUB Introduzir vários contatos n+ para o poço n, próximos entre si, para diminuir RWELL

REFERÊNCIAS N. H. E. Weste, K. Eshraghian, “Principles of CMOS VLSI Design – A Systems Perspective”, Addison Wesley Publishing Company, Reading, 1994. Kaushik Roy, Low Power CMOS VLSI: Circuit Design, Wiley. Interscience, 2000. D. Clein, “CMOS IC Layout : Concepts, Methodologies, and Tools”, Butterworth-Heinemann, 2000. J. A. Borges, E. A. Schmitz, “Projetos de Circuitos Integrados”, Livros Técnicos e Científicos Editora Ltda. 1990. Mead &Conway, “Introduction to VLSI Systems”, Addison Wesle Publishing Company.

- Slides: 45