Exercise Syntax Check entity PROB 1 is port

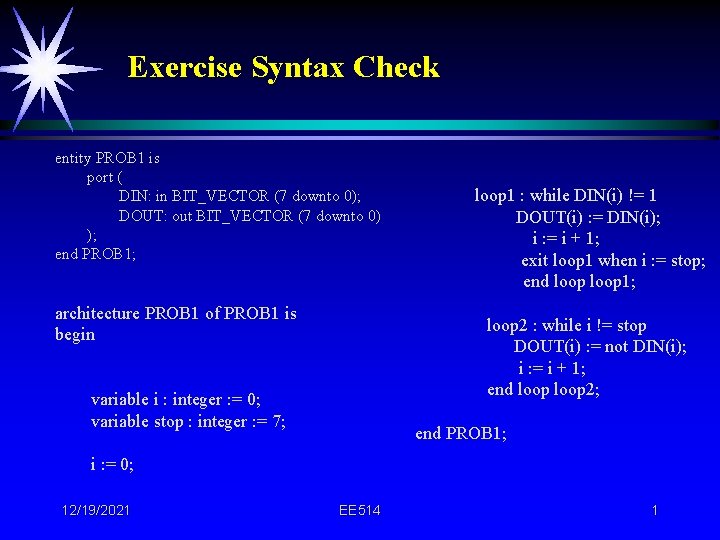

Exercise Syntax Check entity PROB 1 is port ( DIN: in BIT_VECTOR (7 downto 0); DOUT: out BIT_VECTOR (7 downto 0) ); end PROB 1; architecture PROB 1 of PROB 1 is begin loop 1 : while DIN(i) != 1 DOUT(i) : = DIN(i); i : = i + 1; exit loop 1 when i : = stop; end loop 1; loop 2 : while i != stop DOUT(i) : = not DIN(i); i : = i + 1; end loop 2; variable i : integer : = 0; variable stop : integer : = 7; end PROB 1; i : = 0; 12/19/2021 EE 514 1

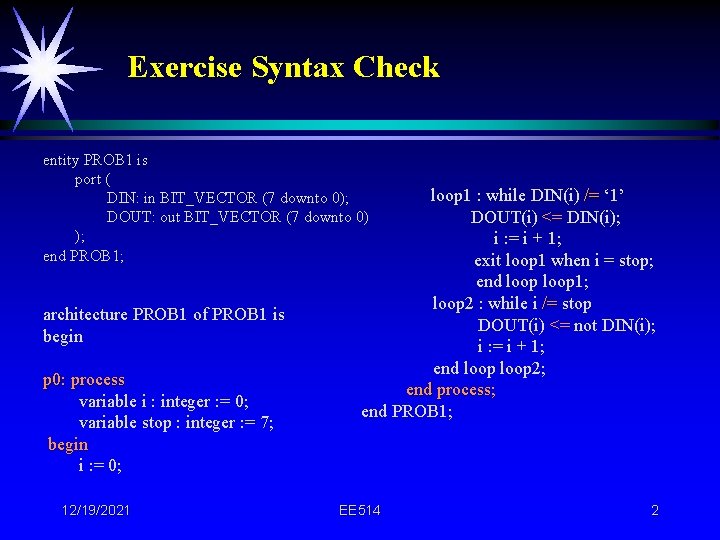

Exercise Syntax Check entity PROB 1 is port ( DIN: in BIT_VECTOR (7 downto 0); DOUT: out BIT_VECTOR (7 downto 0) ); end PROB 1; architecture PROB 1 of PROB 1 is begin p 0: process variable i : integer : = 0; variable stop : integer : = 7; begin i : = 0; 12/19/2021 loop 1 : while DIN(i) /= ‘ 1’ DOUT(i) <= DIN(i); i : = i + 1; exit loop 1 when i = stop; end loop 1; loop 2 : while i /= stop DOUT(i) <= not DIN(i); i : = i + 1; end loop 2; end process; end PROB 1; EE 514 2

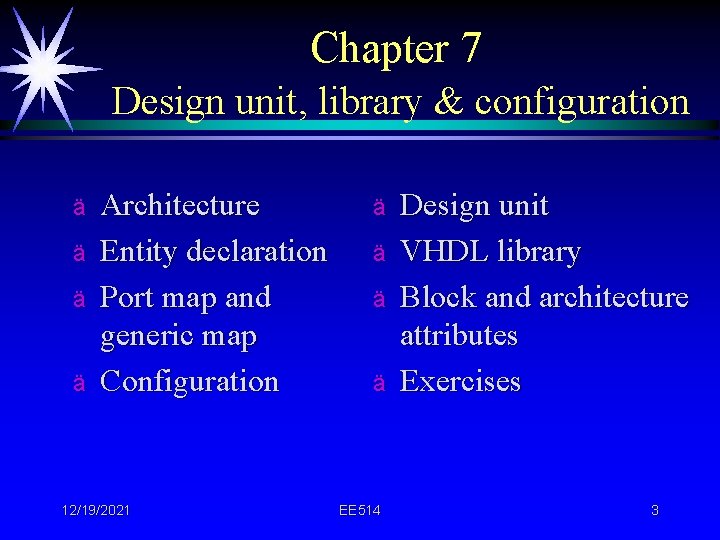

Chapter 7 Design unit, library & configuration ä ä Architecture Entity declaration Port map and generic map Configuration 12/19/2021 ä ä EE 514 Design unit VHDL library Block and architecture attributes Exercises 3

![Architecture_body: : = architecture identifier of entity-name is architecture_declaration_part begin [concurrent statements] end [architecture_simple_name] Architecture_body: : = architecture identifier of entity-name is architecture_declaration_part begin [concurrent statements] end [architecture_simple_name]](http://slidetodoc.com/presentation_image_h2/1ab817efd373432ec99f318546780a67/image-4.jpg)

Architecture_body: : = architecture identifier of entity-name is architecture_declaration_part begin [concurrent statements] end [architecture_simple_name] 12/19/2021 EE 514 4

![Entity declaration Entity_declaration: : = entity identifier is [generic(generic_list); ] [port(port_list); ] entity_declarative_part [begin Entity declaration Entity_declaration: : = entity identifier is [generic(generic_list); ] [port(port_list); ] entity_declarative_part [begin](http://slidetodoc.com/presentation_image_h2/1ab817efd373432ec99f318546780a67/image-5.jpg)

Entity declaration Entity_declaration: : = entity identifier is [generic(generic_list); ] [port(port_list); ] entity_declarative_part [begin entity_statement_part] end[entity_simple_name] 12/19/2021 EE 514 5

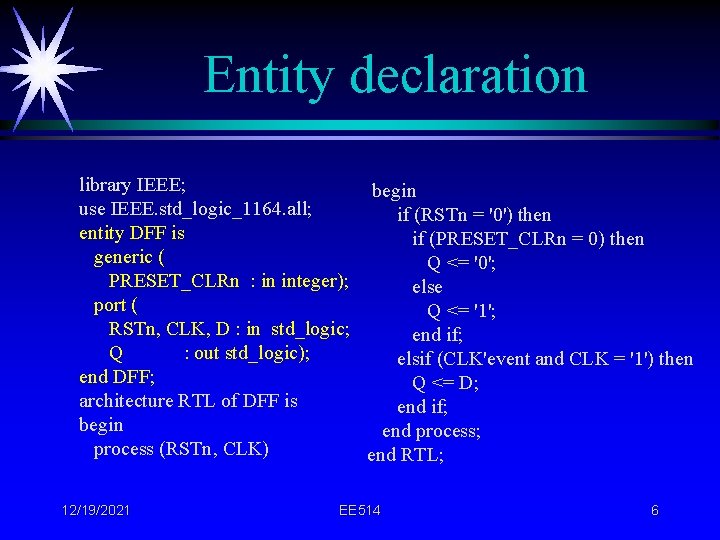

Entity declaration library IEEE; begin use IEEE. std_logic_1164. all; if (RSTn = '0') then entity DFF is if (PRESET_CLRn = 0) then generic ( Q <= '0'; PRESET_CLRn : in integer); else port ( Q <= '1'; RSTn, CLK, D : in std_logic; end if; Q : out std_logic); elsif (CLK'event and CLK = '1') then end DFF; Q <= D; architecture RTL of DFF is end if; begin end process; process (RSTn, CLK) end RTL; 12/19/2021 EE 514 6

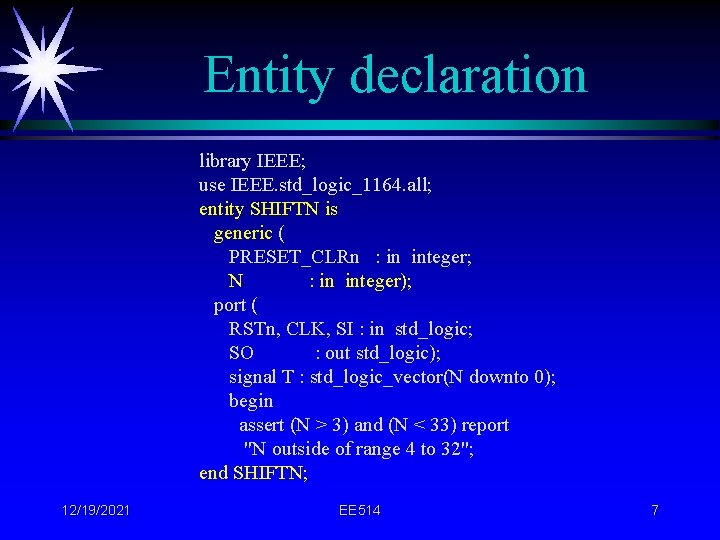

Entity declaration library IEEE; use IEEE. std_logic_1164. all; entity SHIFTN is generic ( PRESET_CLRn : in integer; N : in integer); port ( RSTn, CLK, SI : in std_logic; SO : out std_logic); signal T : std_logic_vector(N downto 0); begin assert (N > 3) and (N < 33) report "N outside of range 4 to 32"; end SHIFTN; 12/19/2021 EE 514 7

![Entity declaration Component_declaration: : = component identifier [generic(generic_list); ] [port(port_list); ] end component; Generic Entity declaration Component_declaration: : = component identifier [generic(generic_list); ] [port(port_list); ] end component; Generic](http://slidetodoc.com/presentation_image_h2/1ab817efd373432ec99f318546780a67/image-8.jpg)

Entity declaration Component_declaration: : = component identifier [generic(generic_list); ] [port(port_list); ] end component; Generic is a good way to pass parameters like bus width, delay, fine name, e. t. c. to a design entity 12/19/2021 EE 514 8

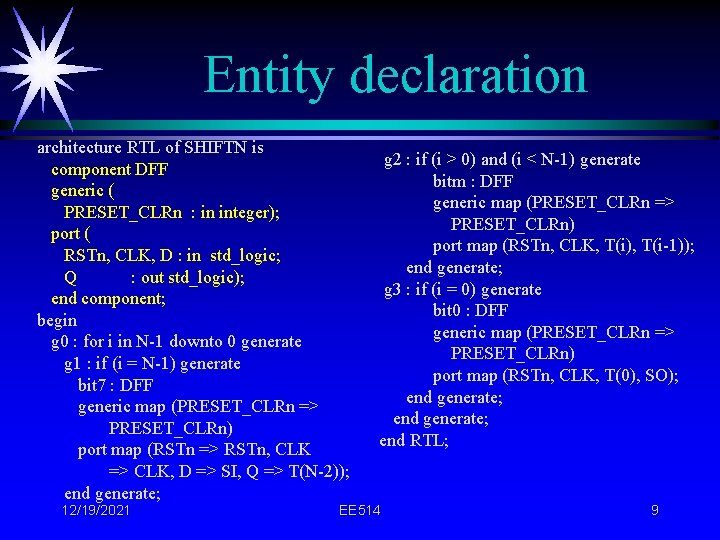

Entity declaration architecture RTL of SHIFTN is component DFF generic ( PRESET_CLRn : in integer); port ( RSTn, CLK, D : in std_logic; Q : out std_logic); end component; begin g 0 : for i in N-1 downto 0 generate g 1 : if (i = N-1) generate bit 7 : DFF generic map (PRESET_CLRn => PRESET_CLRn) port map (RSTn => RSTn, CLK => CLK, D => SI, Q => T(N-2)); end generate; 12/19/2021 g 2 : if (i > 0) and (i < N-1) generate bitm : DFF generic map (PRESET_CLRn => PRESET_CLRn) port map (RSTn, CLK, T(i), T(i-1)); end generate; g 3 : if (i = 0) generate bit 0 : DFF generic map (PRESET_CLRn => PRESET_CLRn) port map (RSTn, CLK, T(0), SO); end generate; end RTL; EE 514 9

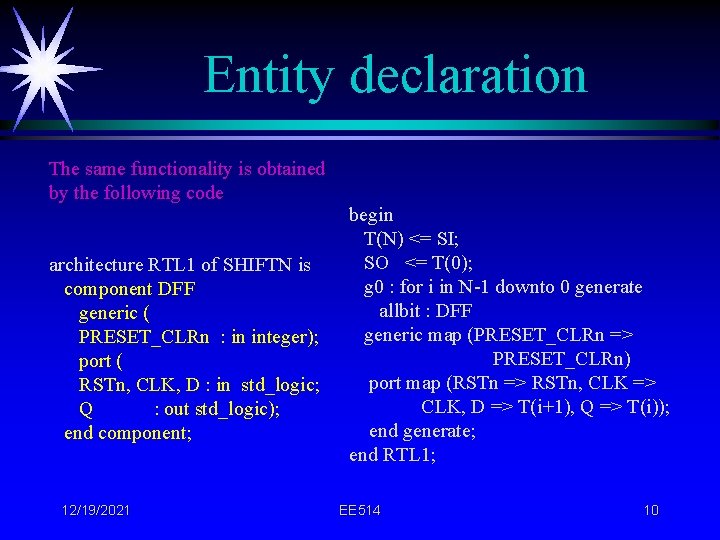

Entity declaration The same functionality is obtained by the following code architecture RTL 1 of SHIFTN is component DFF generic ( PRESET_CLRn : in integer); port ( RSTn, CLK, D : in std_logic; Q : out std_logic); end component; 12/19/2021 begin T(N) <= SI; SO <= T(0); g 0 : for i in N-1 downto 0 generate allbit : DFF generic map (PRESET_CLRn => PRESET_CLRn) port map (RSTn => RSTn, CLK => CLK, D => T(i+1), Q => T(i)); end generate; end RTL 1; EE 514 10

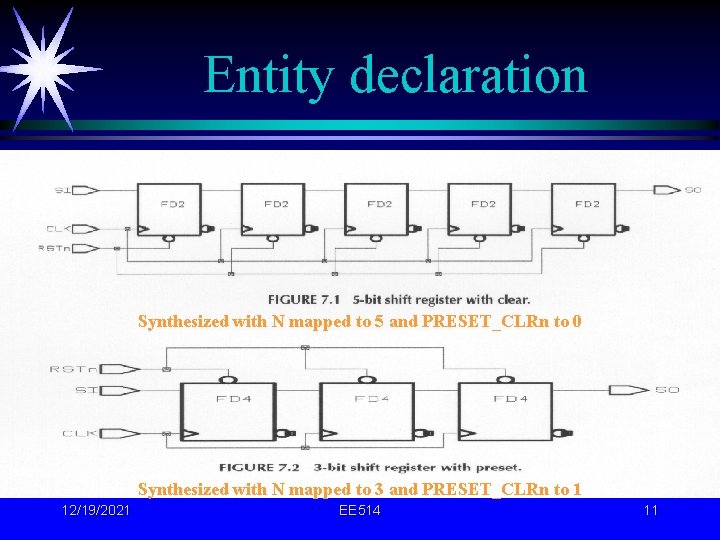

Entity declaration Synthesized with N mapped to 5 and PRESET_CLRn to 0 Synthesized with N mapped to 3 and PRESET_CLRn to 1 12/19/2021 EE 514 11

Dilbert 12/19/2021 EE 514 12

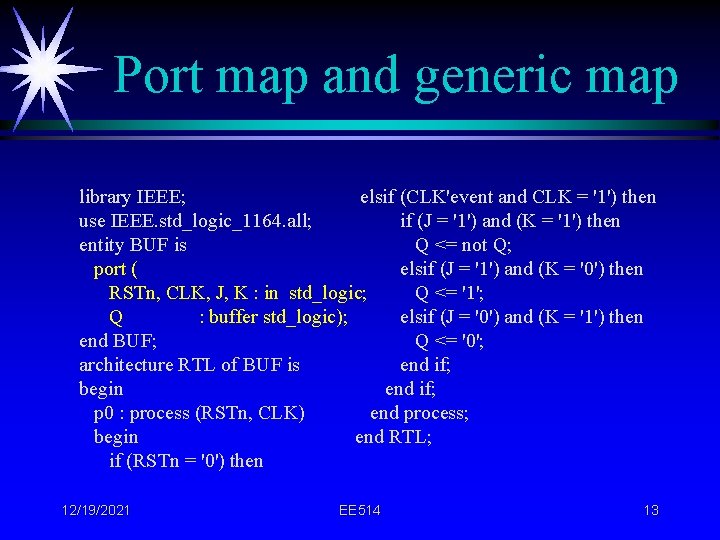

Port map and generic map library IEEE; elsif (CLK'event and CLK = '1') then use IEEE. std_logic_1164. all; if (J = '1') and (K = '1') then entity BUF is Q <= not Q; port ( elsif (J = '1') and (K = '0') then RSTn, CLK, J, K : in std_logic; Q <= '1'; Q : buffer std_logic); elsif (J = '0') and (K = '1') then end BUF; Q <= '0'; architecture RTL of BUF is end if; begin end if; p 0 : process (RSTn, CLK) end process; begin end RTL; if (RSTn = '0') then 12/19/2021 EE 514 13

Port map and generic map library IEEE; RSTn, CLK, J, K : in std_logic; use IEEE. std_logic_1164. all; Q : buffer std_logic); entity BUFMAP is end component; port ( begin RSTn, CLK, DA, DB : in std_logic; buf 0 : BUF DOUT : out std_logic); port map ( end BUFMAP; RSTn => RSTn, CLK => CLK, architecture RTL of BUFMAP is J => DA, K => DB, Q => DOUT); component BUF -- ERROR!! map mode buffer with mode out port ( end RTL; 12/19/2021 EE 514 14

![Configuration configuration_declaration: : =configuration identifier of entity_name is {use_clause|attribute_specification} {block_configuration} end[configuration_simple_name] block_configuration: : = Configuration configuration_declaration: : =configuration identifier of entity_name is {use_clause|attribute_specification} {block_configuration} end[configuration_simple_name] block_configuration: : =](http://slidetodoc.com/presentation_image_h2/1ab817efd373432ec99f318546780a67/image-15.jpg)

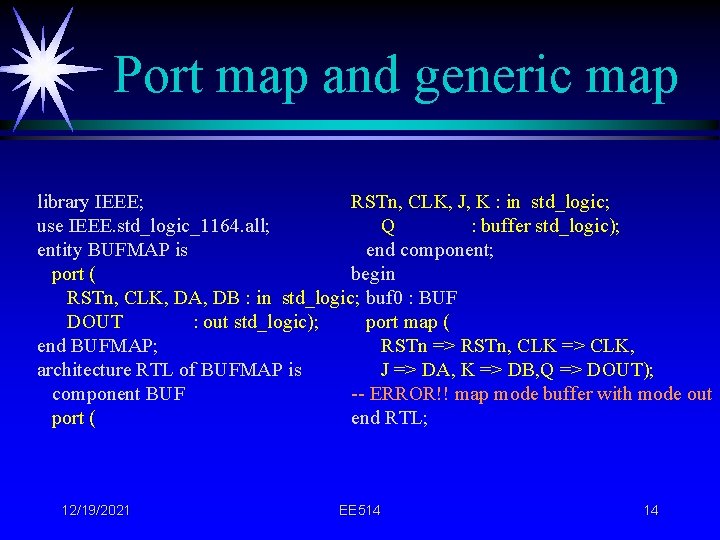

Configuration configuration_declaration: : =configuration identifier of entity_name is {use_clause|attribute_specification} {block_configuration} end[configuration_simple_name] block_configuration: : = for block_specification {use_clause}{block_configuration| component_configuration} end for; block_specification : : = architecture_name [block_statement_label | generate_statement_label[(discrete_range | static_expression )] 12/19/2021 EE 514 15

Configuration Examples of configuration CFG_RTL_DFF of DFF is for RTL block configuration end for; end CFG_RTL_DFF; configuration CFG_RTL 1_SHIFT of SHIFT is for RTL 1 for all : DFF component configuration use entity WORK. DFF(RTL); end for; binding indication end for; end CFG_RTL 1_SHIFT; 12/19/2021 configuration CFG_RTL 2_SHIFT of SHIFT is for RTL 2 for g 0 generate statement labels for g 1 for all : DFF use configuration WORK. CFG_RTL_DFF; end for; instantiation label for g 2 for all : DFF use entity WORK. DFF(RTL); end for; for g 3 for bit 0 : DFF use entity WORK. DFF(RTL); end for; EE 514 16 end CFG_RTL 2_SHIFT;

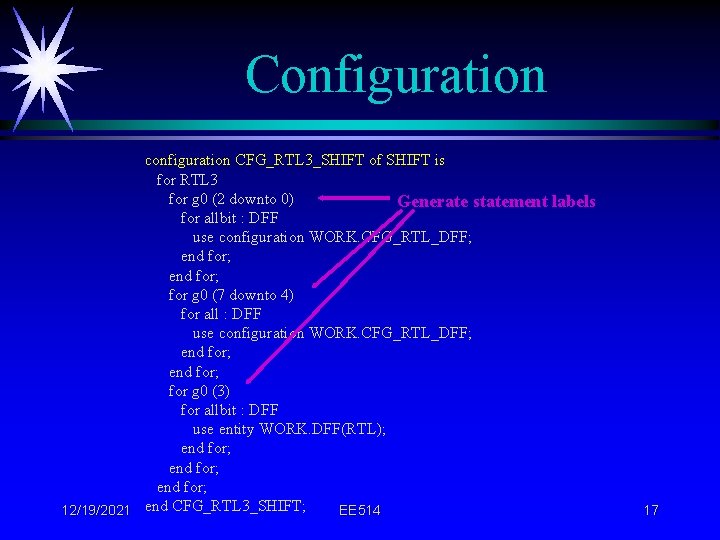

Configuration configuration CFG_RTL 3_SHIFT of SHIFT is for RTL 3 for g 0 (2 downto 0) Generate statement labels for allbit : DFF use configuration WORK. CFG_RTL_DFF; end for; for g 0 (7 downto 4) for all : DFF use configuration WORK. CFG_RTL_DFF; end for; for g 0 (3) for allbit : DFF use entity WORK. DFF(RTL); end for; 12/19/2021 end CFG_RTL 3_SHIFT; EE 514 17

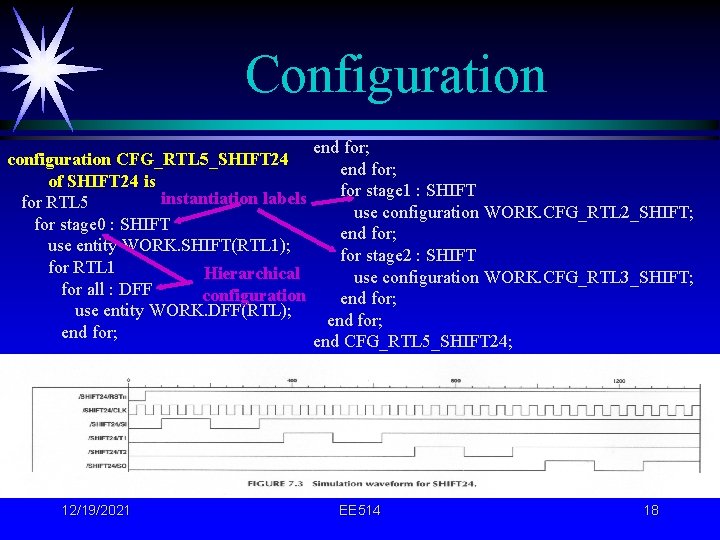

Configuration configuration CFG_RTL 5_SHIFT 24 of SHIFT 24 is instantiation labels for RTL 5 for stage 0 : SHIFT use entity WORK. SHIFT(RTL 1); for RTL 1 Hierarchical for all : DFF configuration use entity WORK. DFF(RTL); end for; 12/19/2021 end for; for stage 1 : SHIFT use configuration WORK. CFG_RTL 2_SHIFT; end for; for stage 2 : SHIFT use configuration WORK. CFG_RTL 3_SHIFT; end for; end CFG_RTL 5_SHIFT 24; EE 514 18

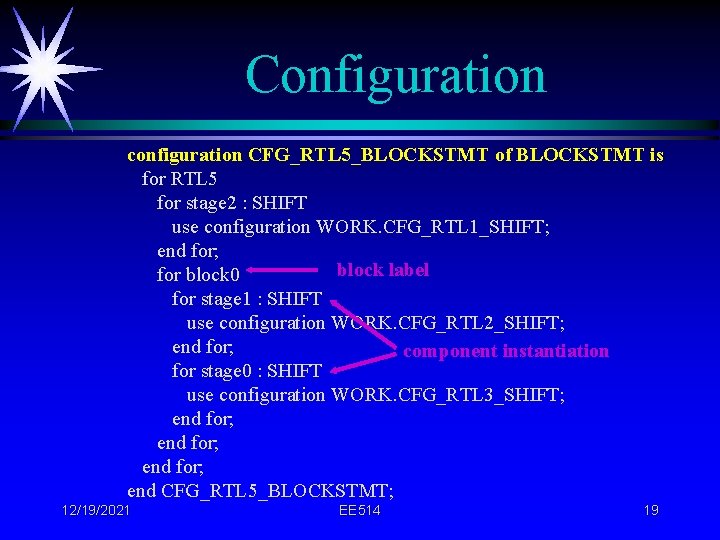

Configuration configuration CFG_RTL 5_BLOCKSTMT of BLOCKSTMT is for RTL 5 for stage 2 : SHIFT use configuration WORK. CFG_RTL 1_SHIFT; end for; block label for block 0 for stage 1 : SHIFT use configuration WORK. CFG_RTL 2_SHIFT; end for; component instantiation for stage 0 : SHIFT use configuration WORK. CFG_RTL 3_SHIFT; end for; end CFG_RTL 5_BLOCKSTMT; 12/19/2021 EE 514 19

Configuration © © © Soft binding by the configuration specification is preferred if several architectures are associated with the same entity Separate configurations using different architecture bindings can be compiled once During simulation different configurations can be selected without recompiling the VHDL source code 12/19/2021 EE 514 20

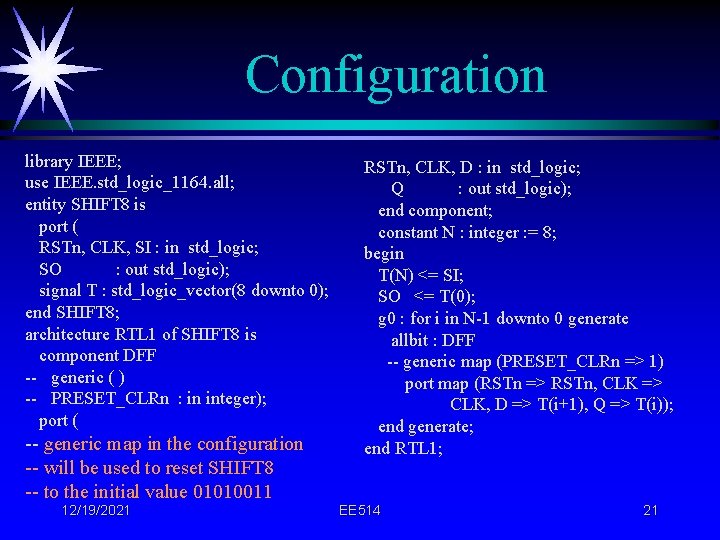

Configuration library IEEE; use IEEE. std_logic_1164. all; entity SHIFT 8 is port ( RSTn, CLK, SI : in std_logic; SO : out std_logic); signal T : std_logic_vector(8 downto 0); end SHIFT 8; architecture RTL 1 of SHIFT 8 is component DFF -- generic ( ) -- PRESET_CLRn : in integer); port ( -- generic map in the configuration -- will be used to reset SHIFT 8 -- to the initial value 01010011 12/19/2021 RSTn, CLK, D : in std_logic; Q : out std_logic); end component; constant N : integer : = 8; begin T(N) <= SI; SO <= T(0); g 0 : for i in N-1 downto 0 generate allbit : DFF -- generic map (PRESET_CLRn => 1) port map (RSTn => RSTn, CLK => CLK, D => T(i+1), Q => T(i)); end generate; end RTL 1; EE 514 21

Configuration configuration CFG_RTL 1_SHIFT 8 of SHIFT 8 is for RTL 1 for g 0 (1 downto 0) for allbit : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 1); end for; for g 0(6) for allbit : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 1); end for; for g 0(4) for allbit : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 1); end for; 12/19/2021 for g 0 (3 downto 2) for all : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 0); end for; for g 0(7) for all : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 0); end for; for g 0(5) for all : DFF use entity WORK. DFF(RTL) generic map (PRESET_CLRn => 0); end for; end CFG_RTL 1_SHIFT 8; EE 514 22

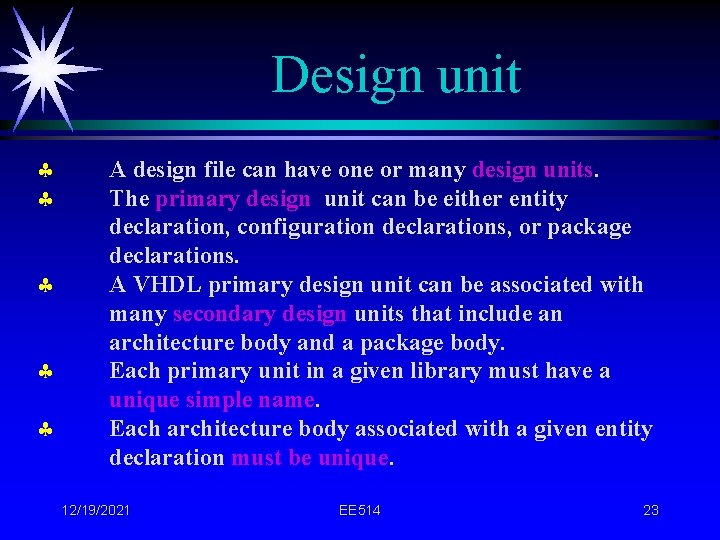

Design unit § § § A design file can have one or many design units. The primary design unit can be either entity declaration, configuration declarations, or package declarations. A VHDL primary design unit can be associated with many secondary design units that include an architecture body and a package body. Each primary unit in a given library must have a unique simple name. Each architecture body associated with a given entity declaration must be unique. 12/19/2021 EE 514 23

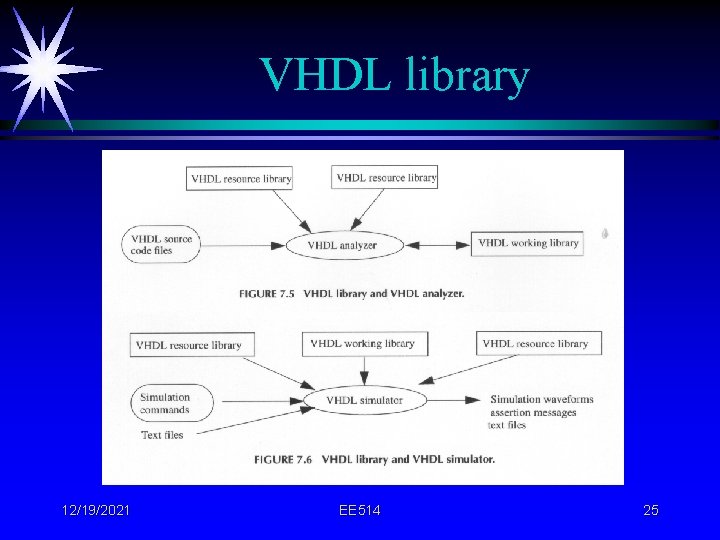

VHDL library Working library WORK is the library in which the design unit is placed Every design unit is assumed to have the following implicit statements: library STD, WORK; use STD. STANDARD. all; 12/19/2021 EE 514 24

VHDL library 12/19/2021 EE 514 25

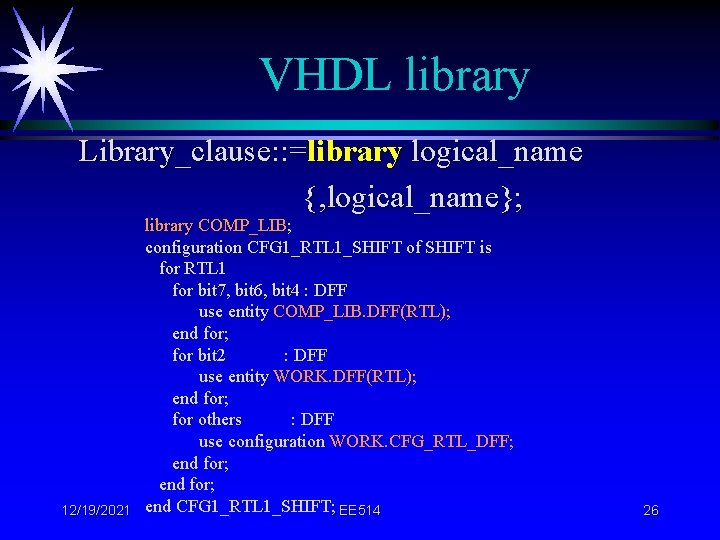

VHDL library Library_clause: : =library logical_name {, logical_name}; 12/19/2021 library COMP_LIB; configuration CFG 1_RTL 1_SHIFT of SHIFT is for RTL 1 for bit 7, bit 6, bit 4 : DFF use entity COMP_LIB. DFF(RTL); end for; for bit 2 : DFF use entity WORK. DFF(RTL); end for; for others : DFF use configuration WORK. CFG_RTL_DFF; end for; end CFG 1_RTL 1_SHIFT; EE 514 26

Block and architecture attributes A predefined attribute BEHAVIOR (ENT’ behavior) is TRUE if there are not component instantiation statements inside the associated block statement or architecture. Attribute STRUCTURE (ENT’structure) is TRUE within the block or architecture if all process statements or equivalent process statements ( concurrent statements) do not contain signal assignment statement. 12/19/2021 EE 514 27

Dilbert 12/19/2021 EE 514 28

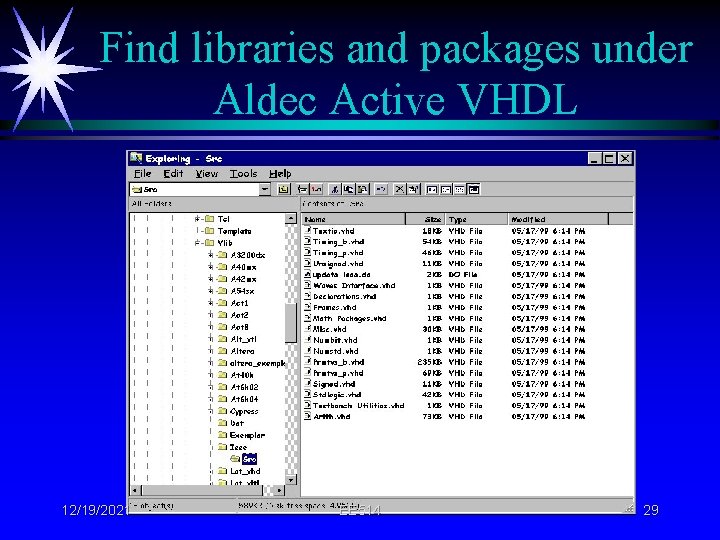

Find libraries and packages under Aldec Active VHDL 12/19/2021 EE 514 29

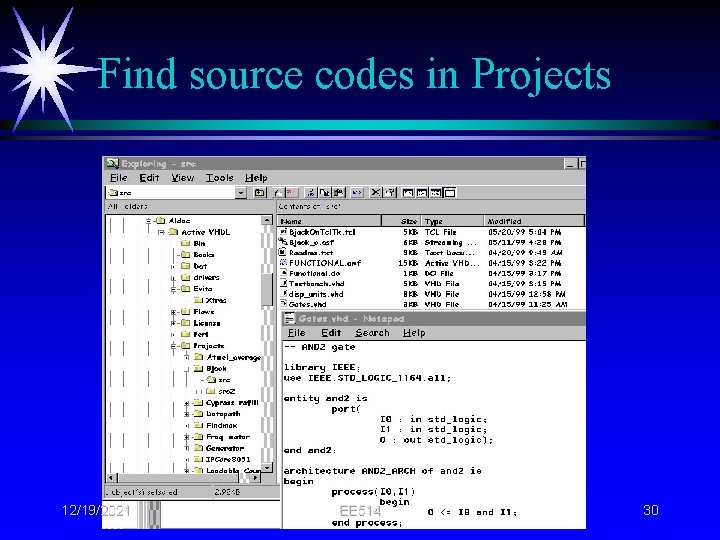

Find source codes in Projects 12/19/2021 EE 514 30

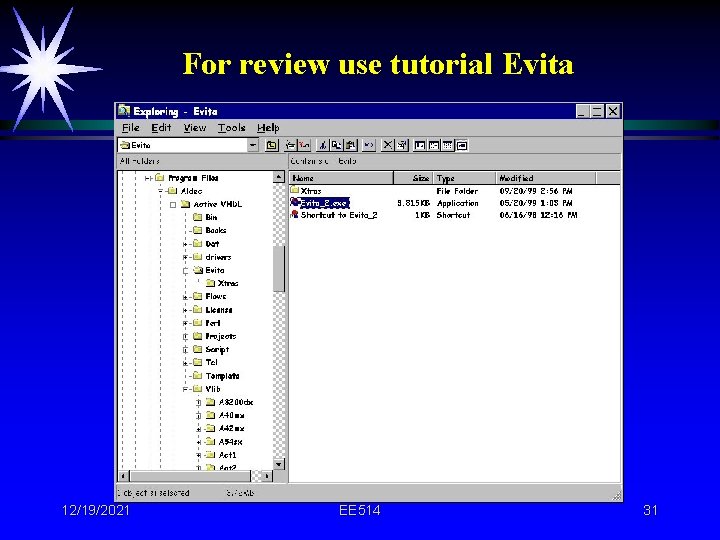

For review use tutorial Evita 12/19/2021 EE 514 31

- Slides: 31