Evolution of the TRT backend and the new

Evolution of the TRT backend and the new TRT-TTC board Presented by LICHARD Peter (CERN) S. BARON (CERN), H. BERTELSEN (NBI), L. CARDIEL (CERN), T. CHANDLER (YALE), P. FARTHOUAT (CERN), C. GAY (YALE), P. KEENER (PENN), M. NEWCOMER (PENN), T. ROGMO (CERN), O. ROHNE (CERN), V. RYJOV (CERN), M. SCHMIDT (YALE), R. VAN BERG (PENN), H. WILLIAMS (PENN) LECC 2005, Heidelberg Peter Lichard, CERN 1

Outline o o o o Introduction Current system Recent system redesign Partitioning TTC module ROD module Patch panels Summary LECC 2005, Heidelberg Peter Lichard, CERN 2

Introduction o Transition Radiation and Tracker (TRT) detector electronics n Frontend comprised of 2 ASICs o o ASDBLR (preamp, shaper, BLR, 2 discri – track, electron) DTMROC n n o o n ~24000 links data ~2000 links control; each BX, command, read-back, reset Patch panels o o n Sampling input each 3. 125 ns L 1 A latency pipeline Stores 3 time slices into derandomizer upon trigger arrival Outputs digitized information in 40 Mbit/s link, 36 AWG shielded twisted pair To refresh the signal and to change cable size More functionality in new architecture Backend o TRT specific n n o ATLAS common n LECC 2005, Heidelberg TTC ROD TTC system (LTP, TTCvi) ROB BUSY Peter Lichard, CERN 3

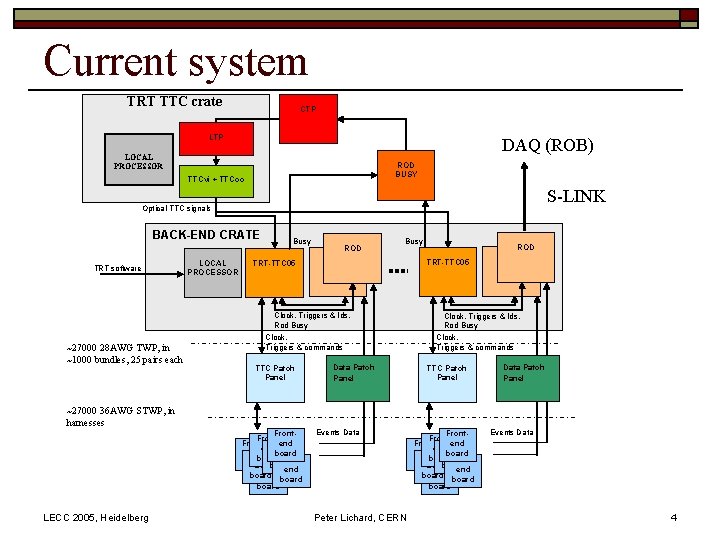

Current system TRT TTC crate CTP LTP DAQ (ROB) LOCAL PROCESSOR ROD BUSY TTCvi + TTCoc S-LINK Optical TTC signals BACK-END CRATE TRT software LOCAL PROCESSOR Busy TRT-TTC 05 ROD Busy ROD Clock, Triggers & Ids, Rod Busy ~27000 28 AWG TWP, in ~1000 bundles, 25 pairs each Clock, Triggers & commands TTC Patch Panel Data Patch Panel ROD TRT-TTC 05 ROD Clock, Triggers & Ids, Rod Busy Clock, Triggers & commands TTC Patch Panel Data Patch Panel ~27000 36 AWG STWP, in harnesses Frontend Front- Frontend board end Frontboard end Frontend board LECC 2005, Heidelberg Events Data Peter Lichard, CERN Frontend Front- Frontend board end Frontboard end Frontend board Events Data 4

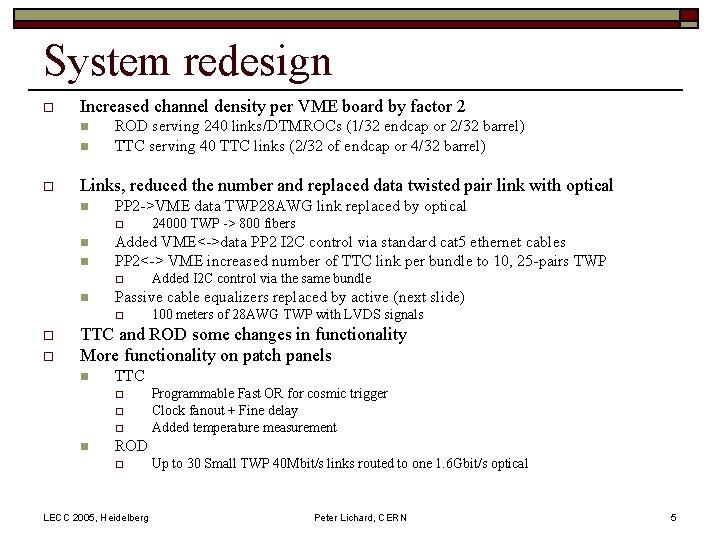

System redesign o Increased channel density per VME board by factor 2 n n o ROD serving 240 links/DTMROCs (1/32 endcap or 2/32 barrel) TTC serving 40 TTC links (2/32 of endcap or 4/32 barrel) Links, reduced the number and replaced data twisted pair link with optical n PP 2 ->VME data TWP 28 AWG link replaced by optical o n n Added VME<->data PP 2 I 2 C control via standard cat 5 ethernet cables PP 2<-> VME increased number of TTC link per bundle to 10, 25 -pairs TWP o n o Added I 2 C control via the same bundle Passive cable equalizers replaced by active (next slide) o o 24000 TWP -> 800 fibers 100 meters of 28 AWG TWP with LVDS signals TTC and ROD some changes in functionality More functionality on patch panels n TTC o o o n Programmable Fast OR for cosmic trigger Clock fanout + Fine delay Added temperature measurement ROD o LECC 2005, Heidelberg Up to 30 Small TWP 40 Mbit/s links routed to one 1. 6 Gbit/s optical Peter Lichard, CERN 5

System redesign – cable filter 100 m Plastica vi passive filter comparator 1 v/5 ns 50 mv/5 ns 100 m Plastica vi active filter 1 v/5 ns small jitter EL 9110 LECC 2005, Heidelberg Peter Lichard, CERN 6

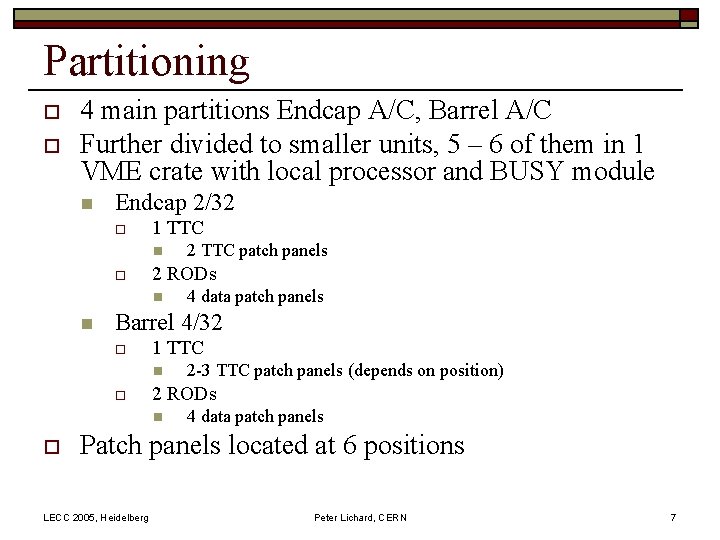

Partitioning o o 4 main partitions Endcap A/C, Barrel A/C Further divided to smaller units, 5 – 6 of them in 1 VME crate with local processor and BUSY module n Endcap 2/32 o 1 TTC n o 2 RODs n n 4 data patch panels Barrel 4/32 o 1 TTC n o 2 -3 TTC patch panels (depends on position) 2 RODs n o 2 TTC patch panels 4 data patch panels Patch panels located at 6 positions LECC 2005, Heidelberg Peter Lichard, CERN 7

Partitioning (2) One side of TRT 8 Patch-Panel Boxes 8/32 nd • 1 EC TTC PP • 2 EC DATA PP • 1 B TTC PP • 1 B DATA PP • 1 EC power • 1 B power 8/32 nd 5 Patch-Panel Boxes 5/32 nd 3/32 nd ½ BARREL 3/32 nd 6 WHEELS A 8 WHEELS B 3 Patch-Panel Boxes LECC 2005, Heidelberg 3 Patch-Panel Boxes Peter Lichard, CERN 8

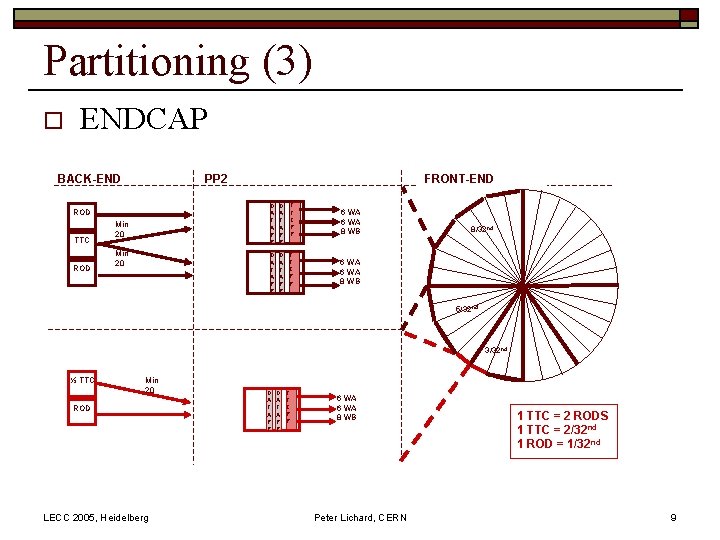

Partitioning (3) o ENDCAP BACK-END PP 2 ROD TTC ROD Min 20 FRONT-END D A T A P P T T C P P 6 WA 8 WB 8/32 nd 5/32 nd 3/32 nd ½ TTC Min 20 ROD LECC 2005, Heidelberg D A T A P P T T C P P 6 WA 8 WB Peter Lichard, CERN 1 TTC = 2 RODS 1 TTC = 2/32 nd 1 ROD = 1/32 nd 9

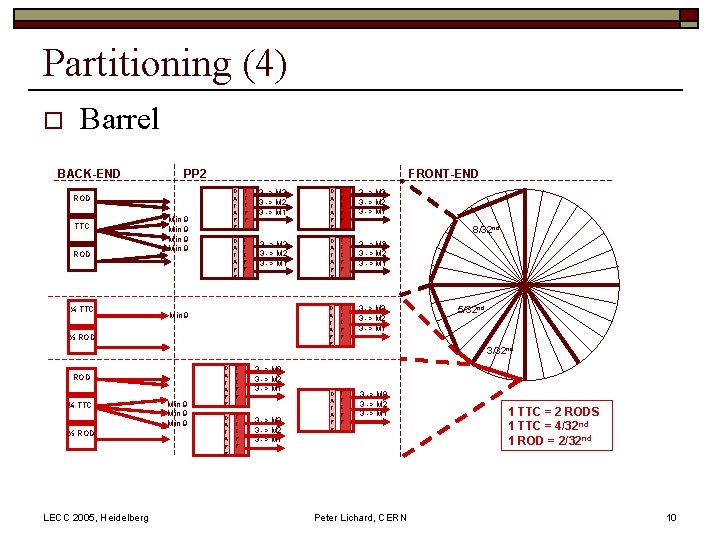

Partitioning (4) o Barrel BACK-END PP 2 FRONT-END ROD TTC ROD ¼ TTC Min 9 D A T A P P T T C P P 3 -> M 3 3 -> M 2 3 -> M 1 D A T A P P T T C P P Min 9 ½ ROD ¾ TTC ½ ROD LECC 2005, Heidelberg Min 9 D A T A P P T T C P P 3 -> M 3 3 -> M 2 3 -> M 1 8/32 nd 5/32 nd 3 -> M 3 3 -> M 2 3 -> M 1 Peter Lichard, CERN 1 TTC = 2 RODS 1 TTC = 4/32 nd 1 ROD = 2/32 nd 10

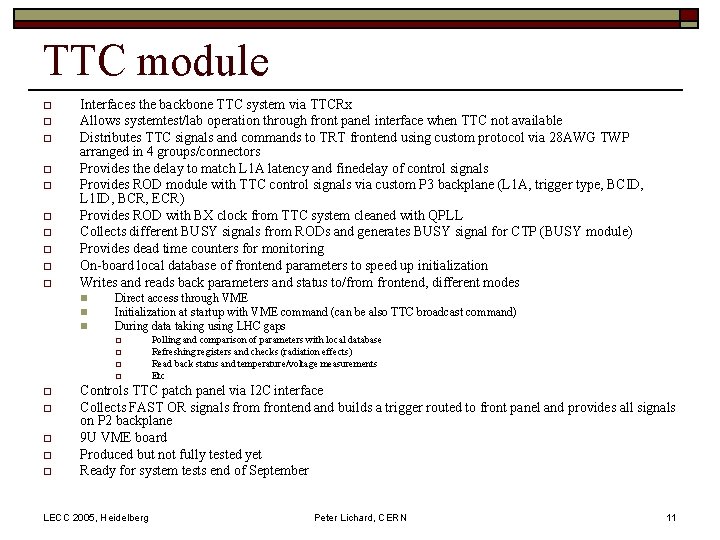

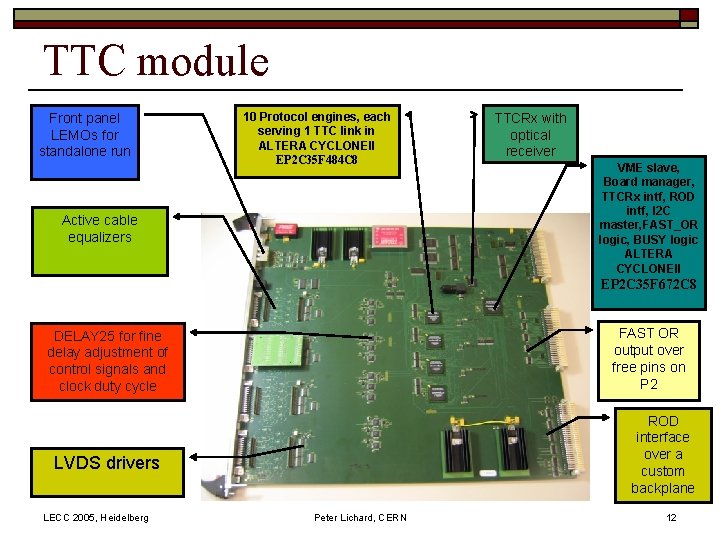

TTC module o o o o o Interfaces the backbone TTC system via TTCRx Allows systemtest/lab operation through front panel interface when TTC not available Distributes TTC signals and commands to TRT frontend using custom protocol via 28 AWG TWP arranged in 4 groups/connectors Provides the delay to match L 1 A latency and finedelay of control signals Provides ROD module with TTC control signals via custom P 3 backplane (L 1 A, trigger type, BCID, L 1 ID, BCR, ECR) Provides ROD with BX clock from TTC system cleaned with QPLL Collects different BUSY signals from RODs and generates BUSY signal for CTP (BUSY module) Provides dead time counters for monitoring On-board local database of frontend parameters to speed up initialization Writes and reads back parameters and status to/from frontend, different modes n n n Direct access through VME Initialization at startup with VME command (can be also TTC broadcast command) During data taking using LHC gaps o o o o o Polling and comparison of parameters with local database Refreshing registers and checks (radiation effects) Read back status and temperature/voltage measurements Etc Controls TTC patch panel via I 2 C interface Collects FAST OR signals from frontend and builds a trigger routed to front panel and provides all signals on P 2 backplane 9 U VME board Produced but not fully tested yet Ready for system tests end of September LECC 2005, Heidelberg Peter Lichard, CERN 11

TTC module Front panel LEMOs for standalone run 10 Protocol engines, each serving 1 TTC link in ALTERA CYCLONEII EP 2 C 35 F 484 C 8 Active cable equalizers TTCRx with optical receiver VME slave, Board manager, TTCRx intf, ROD intf, I 2 C master, FAST_OR logic, BUSY logic ALTERA CYCLONEII EP 2 C 35 F 672 C 8 FAST OR output over free pins on P 2 DELAY 25 for fine delay adjustment of control signals and clock duty cycle ROD interface over a custom backplane LVDS drivers LECC 2005, Heidelberg Peter Lichard, CERN 12

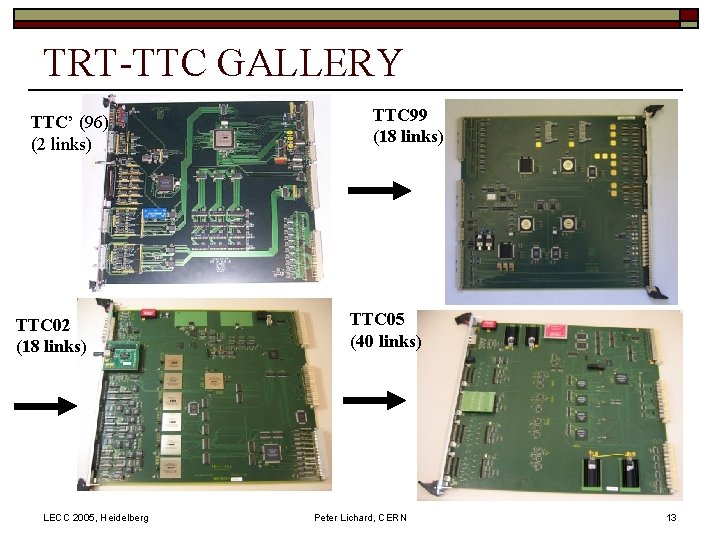

TRT-TTC GALLERY TTC’ (96) (2 links) TTC 02 (18 links) LECC 2005, Heidelberg TTC 99 (18 links) TTC 05 (40 links) Peter Lichard, CERN 13

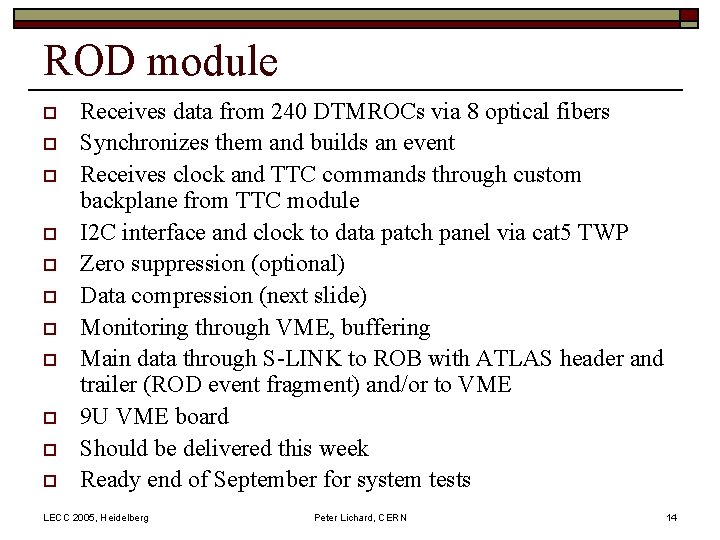

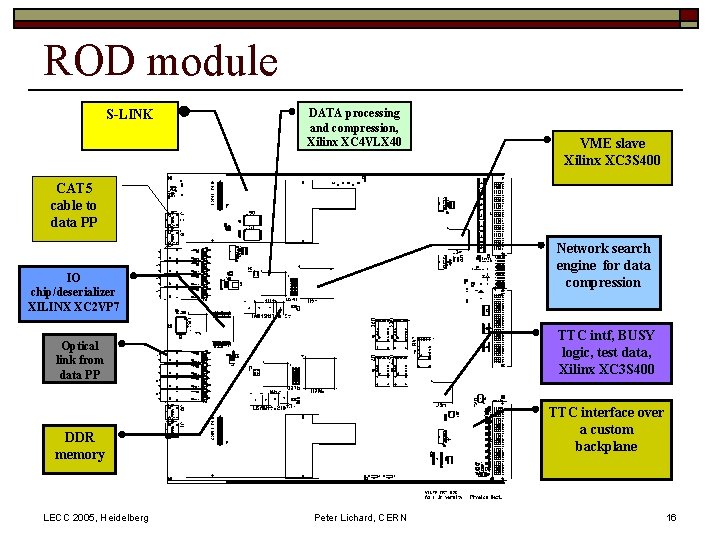

ROD module o o o Receives data from 240 DTMROCs via 8 optical fibers Synchronizes them and builds an event Receives clock and TTC commands through custom backplane from TTC module I 2 C interface and clock to data patch panel via cat 5 TWP Zero suppression (optional) Data compression (next slide) Monitoring through VME, buffering Main data through S-LINK to ROB with ATLAS header and trailer (ROD event fragment) and/or to VME 9 U VME board Should be delivered this week Ready end of September for system tests LECC 2005, Heidelberg Peter Lichard, CERN 14

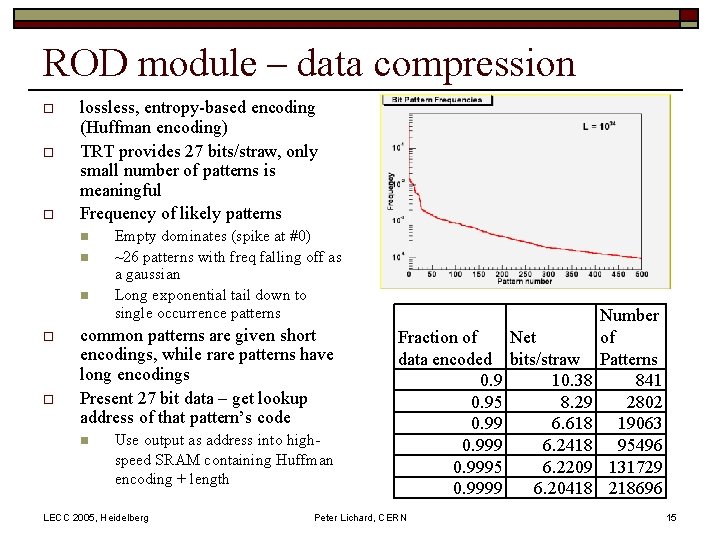

ROD module – data compression o o o lossless, entropy-based encoding (Huffman encoding) TRT provides 27 bits/straw, only small number of patterns is meaningful Frequency of likely patterns n n n o o Empty dominates (spike at #0) ~26 patterns with freq falling off as a gaussian Long exponential tail down to single occurrence patterns common patterns are given short encodings, while rare patterns have long encodings Present 27 bit data – get lookup address of that pattern’s code n Use output as address into highspeed SRAM containing Huffman encoding + length LECC 2005, Heidelberg Fraction of Net data encoded bits/straw 0. 9 10. 38 0. 95 8. 29 0. 99 6. 618 0. 999 6. 2418 0. 9995 6. 2209 0. 9999 6. 20418 Peter Lichard, CERN Number of Patterns 841 2802 19063 95496 131729 218696 15

ROD module S-LINK DATA processing and compression, Xilinx XC 4 VLX 40 VME slave Xilinx XC 3 S 400 CAT 5 cable to data PP Network search engine for data compression IO chip/deserializer XILINX XC 2 VP 7 TTC intf, BUSY logic, test data, Xilinx XC 3 S 400 Optical link from data PP TTC interface over a custom backplane DDR memory LECC 2005, Heidelberg Peter Lichard, CERN 16

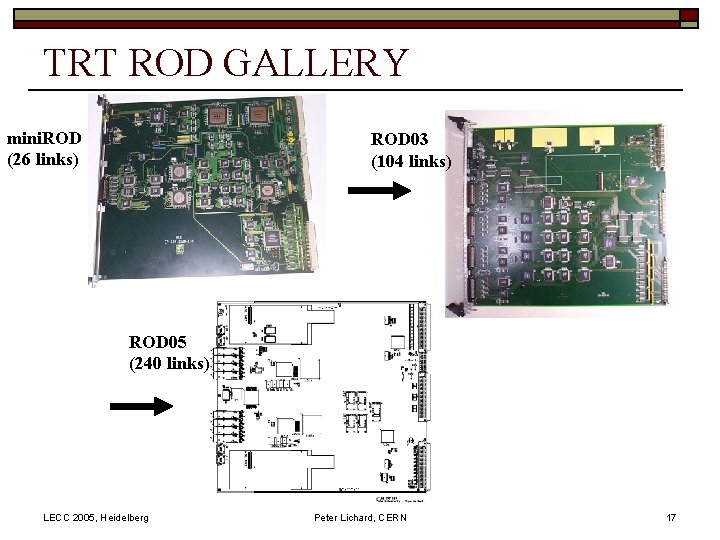

TRT ROD GALLERY mini. ROD (26 links) ROD 03 (104 links) ROD 05 (240 links) LECC 2005, Heidelberg Peter Lichard, CERN 17

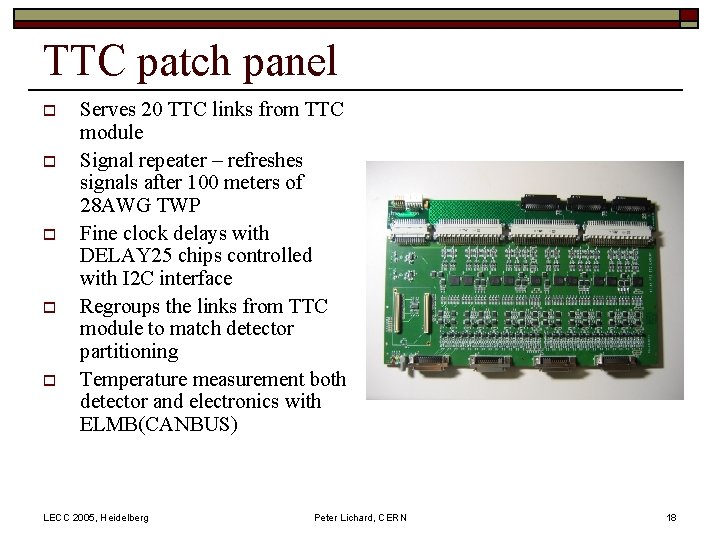

TTC patch panel o o o Serves 20 TTC links from TTC module Signal repeater – refreshes signals after 100 meters of 28 AWG TWP Fine clock delays with DELAY 25 chips controlled with I 2 C interface Regroups the links from TTC module to match detector partitioning Temperature measurement both detector and electronics with ELMB(CANBUS) LECC 2005, Heidelberg Peter Lichard, CERN 18

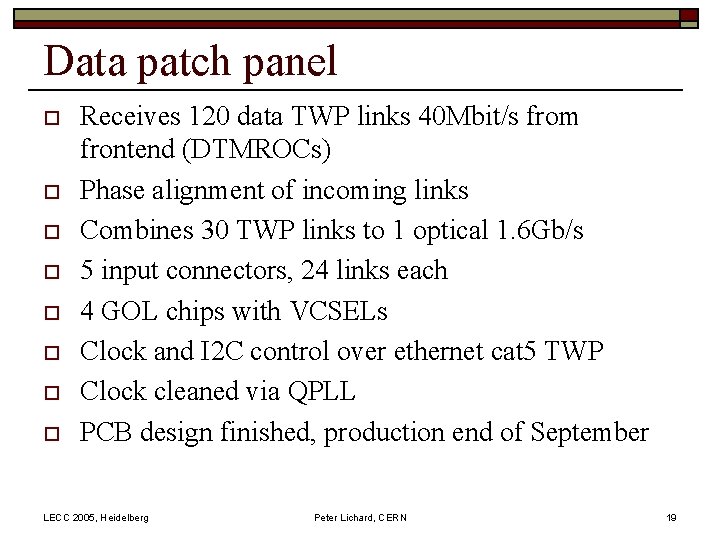

Data patch panel o o o o Receives 120 data TWP links 40 Mbit/s from frontend (DTMROCs) Phase alignment of incoming links Combines 30 TWP links to 1 optical 1. 6 Gb/s 5 input connectors, 24 links each 4 GOL chips with VCSELs Clock and I 2 C control over ethernet cat 5 TWP Clock cleaned via QPLL PCB design finished, production end of September LECC 2005, Heidelberg Peter Lichard, CERN 19

SUMMARY o o o New TRT backend should be ready for system tests end of September Non-negligible changes leading to the reduction of number of VME boards by factor 2 Big part of TWP readout cables from PP 2 to USA 15 replaced by optical links (24000 -> 800) Modular design Partitioning for ATLAS LECC 2005, Heidelberg Peter Lichard, CERN 20

- Slides: 20