ETRAX CRIS architecture and Xilinx FPGA Peter Zumbruch

ETRAX CRIS architecture and Xilinx FPGA Peter Zumbruch Experiment control systems group GSI (KS/EE) March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI

Overview • Embedded Target Platforms – ETRAX CRIS – Xilinx FPGA - Virtex 4/5 • Summary March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 2

EPICS embedded • Aiming at two architectures – ETRAX based CRIS architecture • HADControl (aka: HADSHOPOMO) • TRBv 2 • Experiments: HADES, CBM, Panda, … – Xilinx FGPA: Virtex 4 (5) • Sys. Core based Boards • Experiment(s): CBM, … March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 3

HADControl based on ETRAX 100 LX MCM by AXIS Development of GSI’s Experimental Digital Electronic group (M. Traxler) HADControl (aka HADSHOPOMO (HA DES SHOWER POWER MONITOR) ) “Multi-purpose control/monitor device developed for HADES […] is based on the ETRAX 100 LX MCM 4+16 and runs the "Experimental Physics and Industrial Control System, EPICS”. http: //developer. axis. com/showroom March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 4

TRBv 2 (multi purpose DAQ board) based on ETRAX FS by AXIS Current Applications: HADES complete DAQ upgrade, PET Readout Coimbra, PANDA, KVI, … http: //www-linux. gsi. de/~traxler/GSIScientific. Report 2006_TRB/TRBv 2_2006. pdf March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – EPICS-Shanghai, SSRF - Peter Zumbruch, GSI 5

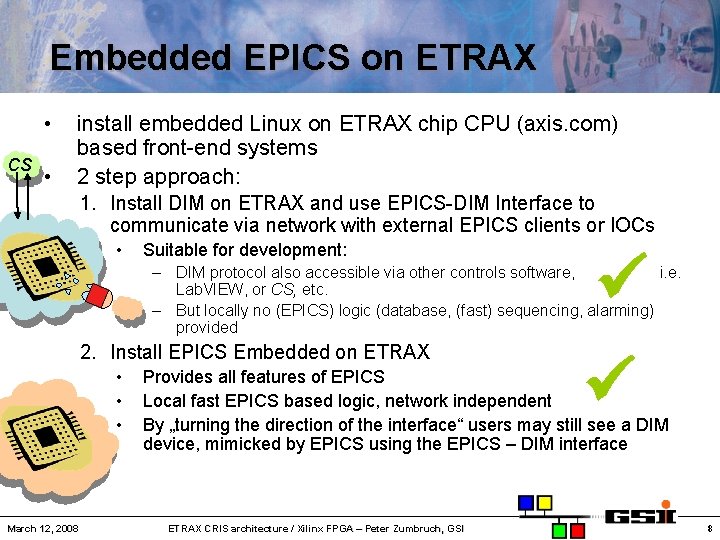

Embedded EPICS on ETRAX • CS • install embedded Linux on ETRAX chip CPU (axis. com) based front-end systems 2 step approach: 1. Install DIM on ETRAX and use EPICS-DIM Interface to communicate via network with external EPICS clients or IOCs • Suitable for development: – DIM protocol also accessible via other controls software, i. e. Lab. VIEW, or CS, etc. – But locally no (EPICS) logic (database, (fast) sequencing, alarming) provided March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 6

What is DIM? “DIM is a communication system for distributed / mixed environments. It provides a network transparent inter-process communication layer. ” • • Protocol Distributed Information Management System Originally built for DELPHI http: //dim. web. cern. ch/dim/ Some Properties: • • • name based publisher/subscriber mechanism for services and commands Small / Tiny Many platforms No (not yet) inherent access security No logic Dynamic Used as network protocol for Lab. VIEW based CS Control system (GSI) … another Gateway to Lab. VIEW March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 7

Embedded EPICS on ETRAX • CS • install embedded Linux on ETRAX chip CPU (axis. com) based front-end systems 2 step approach: 1. Install DIM on ETRAX and use EPICS-DIM Interface to communicate via network with external EPICS clients or IOCs • Suitable for development: – DIM protocol also accessible via other controls software, i. e. Lab. VIEW, or CS, etc. – But locally no (EPICS) logic (database, (fast) sequencing, alarming) provided 2. Install EPICS Embedded on ETRAX • • • March 12, 2008 Provides all features of EPICS Local fast EPICS based logic, network independent By „turning the direction of the interface“ users may still see a DIM device, mimicked by EPICS using the EPICS – DIM interface ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 8

ETRAX Applications • HADControl Board (ETRAX 100 LX MCM – linux-cris_v 10) – Temperature Sensor 1 -Wire Bus – Drift chamber HV-Interlock Control – development: CAN-Bus Controller • TRB (ETRAX FS – linux-cris_v 32) – Resistive Plate Counter – Threshold settings via SPI protocol – Development: DAQ monitoring, FEE controls March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 9

EPICS on Xilinx Virtex 4/5 • Basis – Environment Platform (KIP (University of Heidelberg)) providing several soft cores (PPC/Micro. Blaze) with Linux (up-to-know µClinux) on it. • based on VMware image, ready to use March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 10

Outlook on EPICS on Xilinx Virtex 4/5 • Future Milestones – Software milestones • Implementation of gnu ppc cross compiler into EPICS build system (preferred) • or implement EPICS IOC build into Xilinx Build Process • or build EPICS on FPGA running gcc/make/perl on front-end – Hardware milestones: • Xilinx Evaluation Board ml 403 – Soft IOC with Inter-process communication Run-Control • Nxyter / Sys. Core based board – DAQ Board (CBM) – Soft IOC (incl. IPC) – IOC with access to “external” Hardware on-Board – Configuration of Setups via EPICS March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 11

Summary • Axis’ ETRAX http: //wiki. gsi. de/Epics – EPICS on ETRAX’ cris architecture – Connection to EPICS via ‘ 2 step approach’ • ETRAX-DIM – EPICS-DIM-Interface – EPICS • also suitable for other architectures (i. e. XYZ-DIM – EPICS) • Outlook on Xilinx’ Virtex 4/5 – Different software solutions – Hardware • ml 403 • Nxyter / Sys. Core March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 12

Thank you for your attention. March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 13

March 12, 2008 ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 14

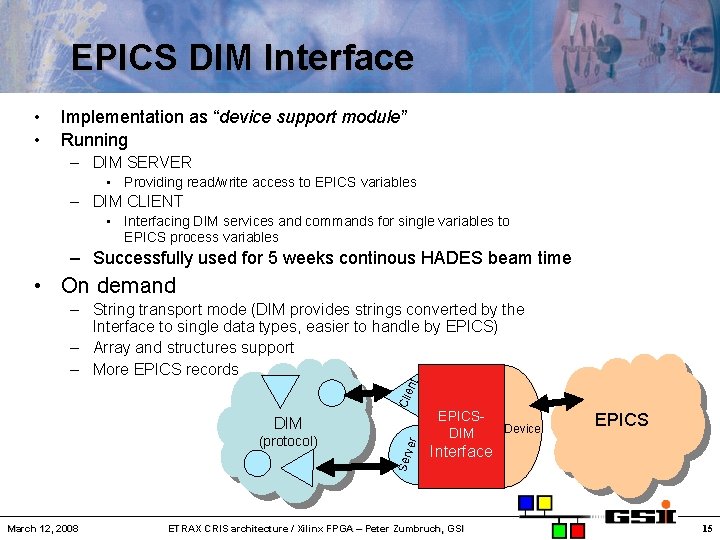

EPICS DIM Interface • • Implementation as “device support module” Running – DIM SERVER • Providing read/write access to EPICS variables – DIM CLIENT • Interfacing DIM services and commands for single variables to EPICS process variables – Successfully used for 5 weeks continous HADES beam time • On demand Clie nt – String transport mode (DIM provides strings converted by the Interface to single data types, easier to handle by EPICS) – Array and structures support – More EPICS records Serv (protocol) er DIM March 12, 2008 EPICSDIM Device EPICS Interface ETRAX CRIS architecture / Xilinx FPGA – Peter Zumbruch, GSI 15

- Slides: 15