ESS 180 RH An 180 nm digital library

“ESS 180 RH: An 180 nm digital library addressing Single Event Latch-up based on X-FAB XH 018” D. Mitrovgenis, T. Athanassopoulos, P. Broutas, A. Depastas, K. Spiropoulou, S. Filippas, E. Zervakis, D. Zaxarias, S. Polymenakos, P. Vlagopoulos June, 20 th AMICSA 2018 LEUVEN, BELGIUM

Presentation Outline • • • The Company profile The Context of the activity The X-FAB XH 018 technology The ASIC Architecture The ESS 180 RH development SEL tests www. esenssys. com AMICSA 2018 2/15

Company Profile • Privately owned company located in Athens, Greece • Developer and manufacturer of high quality sensors based on MEMS • Has advanced design and development capabilities, offers flexibility and customer tailored services • Adopts the fabless model investing in R&D while maintaining high production volumes • Has test infrastructure to characterize sensors and electronics in wafer and system level Sensors Design www. esenssys. com ASIC Design AMICSA 2018 Mechanical Design 3/15

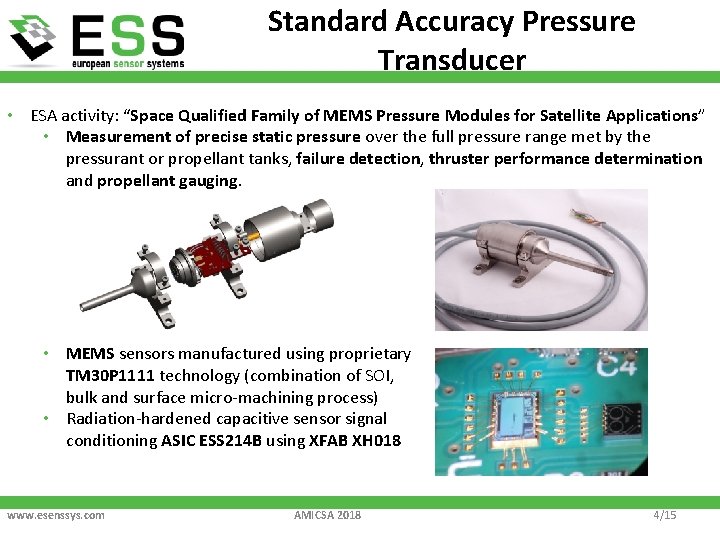

Standard Accuracy Pressure Transducer • ESA activity: “Space Qualified Family of MEMS Pressure Modules for Satellite Applications” • Measurement of precise static pressure over the full pressure range met by the pressurant or propellant tanks, failure detection, thruster performance determination and propellant gauging. • MEMS sensors manufactured using proprietary TM 30 P 1111 technology (combination of SOI, bulk and surface micro-machining process) • Radiation-hardened capacitive sensor signal conditioning ASIC ESS 214 B using XFAB XH 018 www. esenssys. com AMICSA 2018 4/15

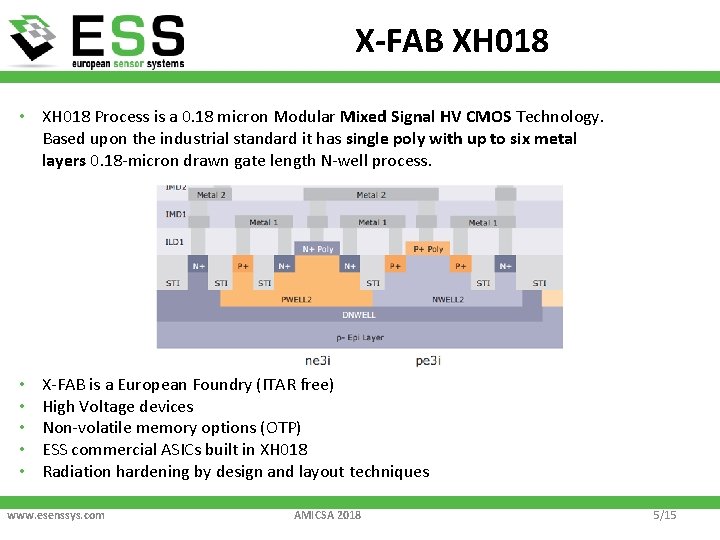

X-FAB XH 018 • XH 018 Process is a 0. 18 micron Modular Mixed Signal HV CMOS Technology. Based upon the industrial standard it has single poly with up to six metal layers 0. 18 -micron drawn gate length N-well process. • • • X-FAB is a European Foundry (ITAR free) High Voltage devices Non-volatile memory options (OTP) ESS commercial ASICs built in XH 018 Radiation hardening by design and layout techniques www. esenssys. com AMICSA 2018 5/15

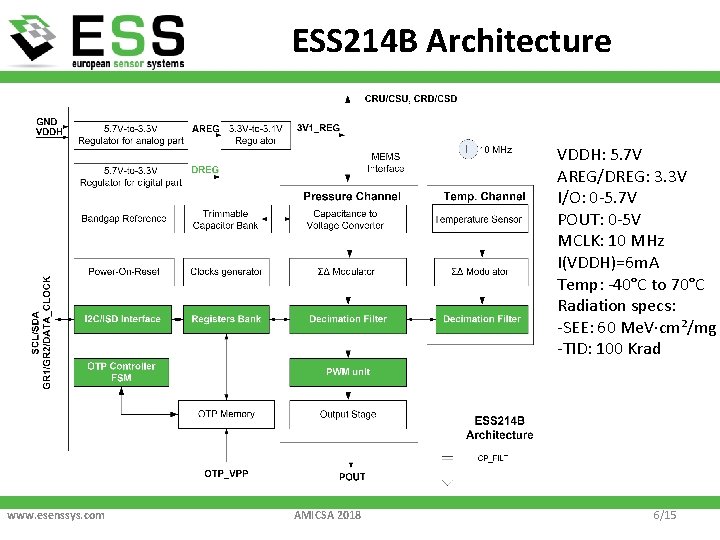

ESS 214 B Architecture VDDH: 5. 7 V AREG/DREG: 3. 3 V I/O: 0 -5. 7 V POUT: 0 -5 V MCLK: 10 MHz I(VDDH)=6 m. A Temp: -40°C to 70°C Radiation specs: -SEE: 60 Me. V∙cm²/mg -TID: 100 Krad www. esenssys. com AMICSA 2018 6/15

SEL mitigation strategy • At the course of the ESA funded activity “Accelerometer Component to TRL 5” the read-out ASIC was designed and manufactured using X-FAB XH 018 without any special precautions against SEL at the digital part. • The components under test had been found to be SEL sensitive with a LET threshold between 6. 4 Me. V∙cm 2/mg and 15. 9 Me. V∙cm 2/mg • Selecting an inherently SEL immune SOI technology was not an attractive choice • IMEC DARE 180 X was under development and not fully tested (2014) • SEL in the analog part: • Increase the distance between the two parasitic complementary transistors where possible • Reduce parasitic well and substrate resistors by using low resistance ground contacts • Surround MOS transistors with guard rings. • SEL in the digital part • Development of ESS 180 RH www. esenssys. com AMICSA 2018 7/15

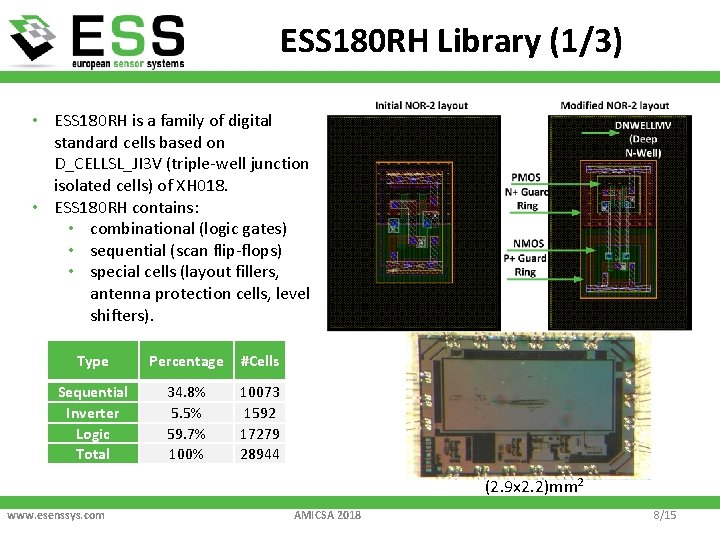

ESS 180 RH Library (1/3) • ESS 180 RH is a family of digital standard cells based on D_CELLSL_JI 3 V (triple-well junction isolated cells) of XH 018. • ESS 180 RH contains: • combinational (logic gates) • sequential (scan flip-flops) • special cells (layout fillers, antenna protection cells, level shifters). Type Percentage #Cells Sequential Inverter Logic Total 34. 8% 5. 5% 59. 7% 10073 1592 17279 28944 (2. 9 x 2. 2)mm 2 www. esenssys. com AMICSA 2018 8/15

ESS 180 RH Library (2/3) • Custom cell layout • Post-layout RC parasitic extraction (modelling of RC interconnects and Layout Dependent Effects) • Post-extraction analog simulation • Generation of. lef database (design rules and abstract information) • Modification of the Liberty™ library files (. lib), which is an ASCII representation of the timing and power parameters of each cell by simulating the cells for PVT corners • The characterization is performed for three corners: • typical (3. 3 V/25 °C) • worst speed (2. 6 V/175 °C) • worst power (3. 6 V/-40 °C). www. esenssys. com AMICSA 2018 9/15

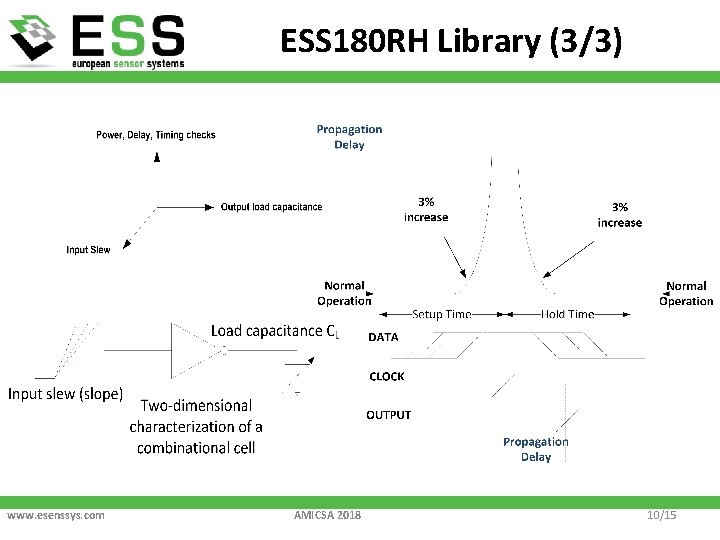

ESS 180 RH Library (3/3) www. esenssys. com AMICSA 2018 10/15

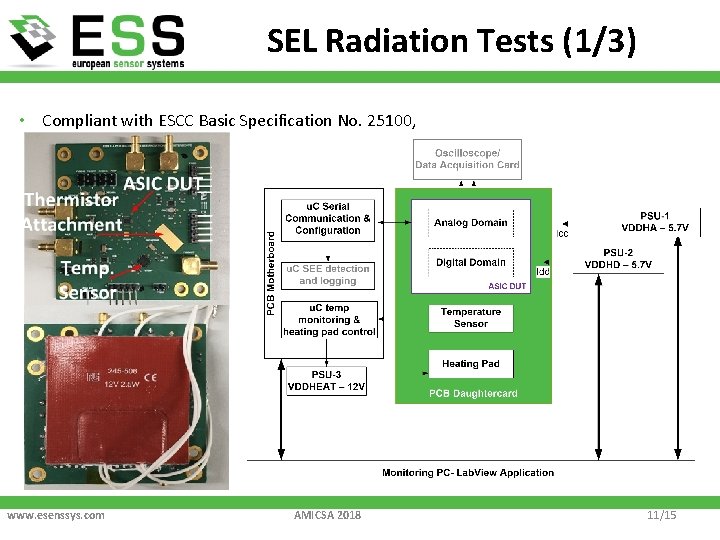

SEL Radiation Tests (1/3) • Compliant with ESCC Basic Specification No. 25100, www. esenssys. com AMICSA 2018 11/15

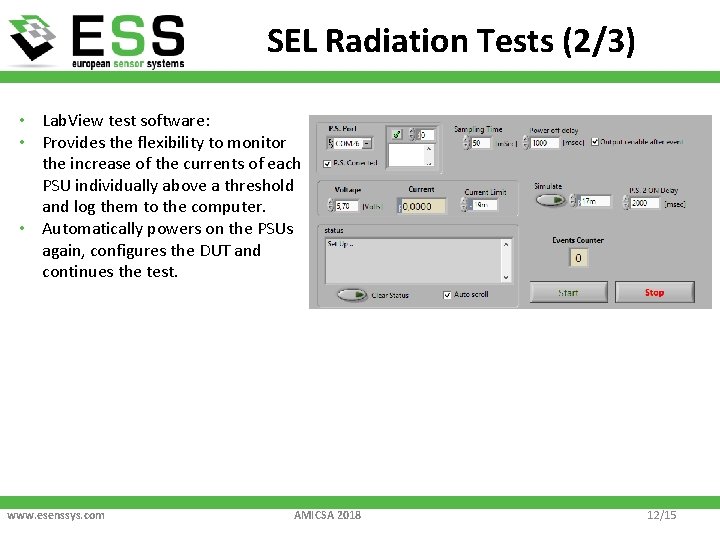

SEL Radiation Tests (2/3) • Lab. View test software: • Provides the flexibility to monitor the increase of the currents of each PSU individually above a threshold and log them to the computer. • Automatically powers on the PSUs again, configures the DUT and continues the test. www. esenssys. com AMICSA 2018 12/15

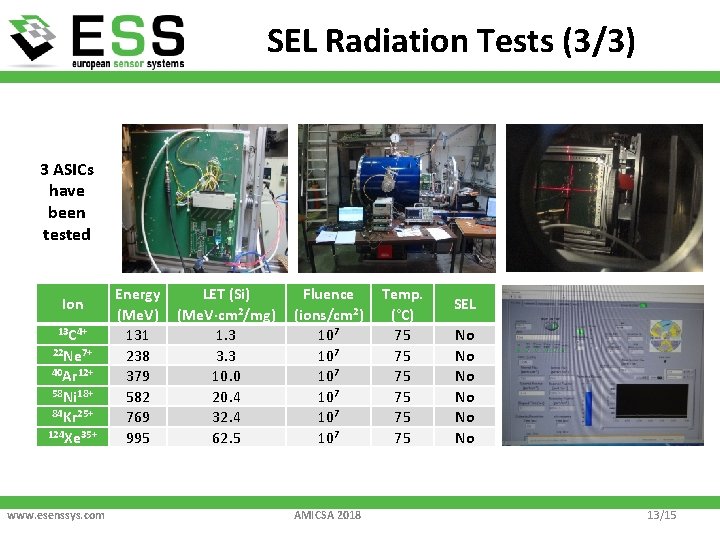

SEL Radiation Tests (3/3) 3 ASICs have been tested Ion 13 C 4+ 22 Ne 7+ 40 Ar 12+ 58 Ni 18+ 84 Kr 25+ 124 Xe 35+ www. esenssys. com Energy (Me. V) 131 238 379 582 769 995 LET (Si) (Me. V∙cm 2/mg) 1. 3 3. 3 10. 0 20. 4 32. 4 62. 5 Fluence (ions/cm 2) 107 107 107 AMICSA 2018 Temp. (°C) 75 75 75 SEL No No No 13/15

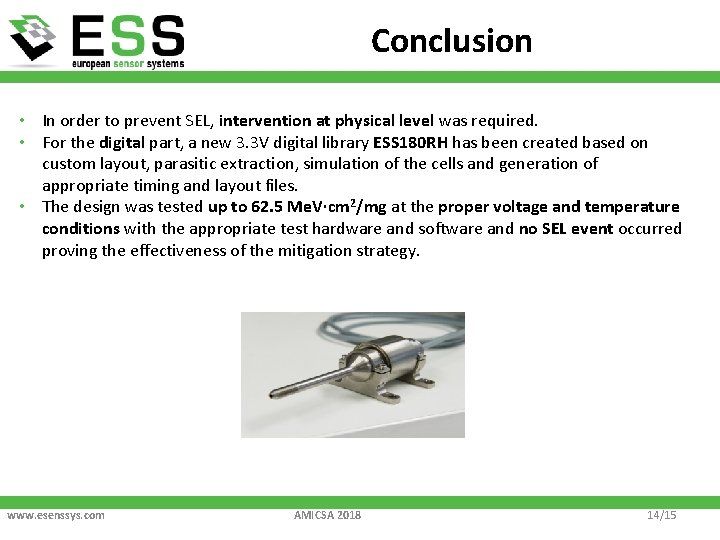

Conclusion • In order to prevent SEL, intervention at physical level was required. • For the digital part, a new 3. 3 V digital library ESS 180 RH has been created based on custom layout, parasitic extraction, simulation of the cells and generation of appropriate timing and layout files. • The design was tested up to 62. 5 Me. V∙cm 2/mg at the proper voltage and temperature conditions with the appropriate test hardware and software and no SEL event occurred proving the effectiveness of the mitigation strategy. www. esenssys. com AMICSA 2018 14/15

Contact us! Contact Person: Dimitris Mitrovgenis, IC design engineer Email: mitrovgenis@esenssys. com Contact Person: Emmanuil Zervakis, General Director Email: zervakis@esenssys. com www. esenssys. com AMICSA 2018 EUROPEAN SENSOR SYSTEMS S. A. Address: 48, Konstantinoupoleos St. , 19441, Koropi, Attiki, Greece Tel. : +30 216 2000 500 Fax: +30 216 2000 555 Url: http: //www. esenssys. com 15/15

- Slides: 15