ESE 532 SystemonaChip Architecture Day 9 October 1

ESE 532: System-on-a-Chip Architecture Day 9: October 1, 2018 Real Time Preclass 6 d Retiming Solution Penn ESE 532 Fall 2018 -- De. Hon 1

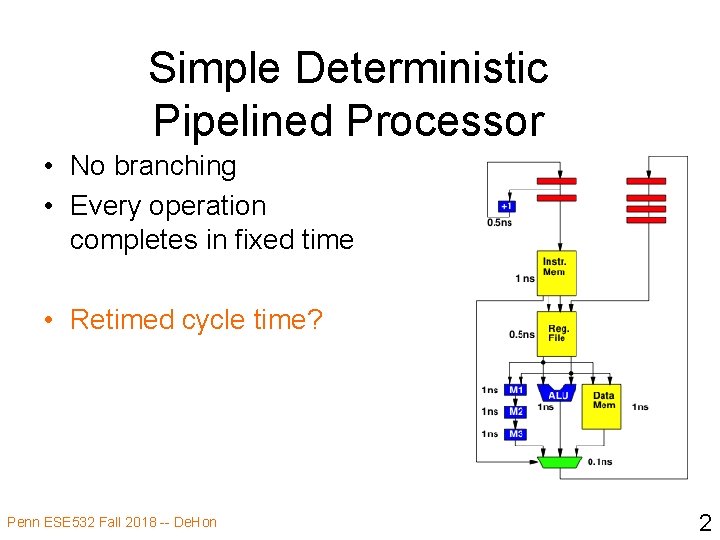

Simple Deterministic Pipelined Processor • No branching • Every operation completes in fixed time • Retimed cycle time? Penn ESE 532 Fall 2018 -- De. Hon 2

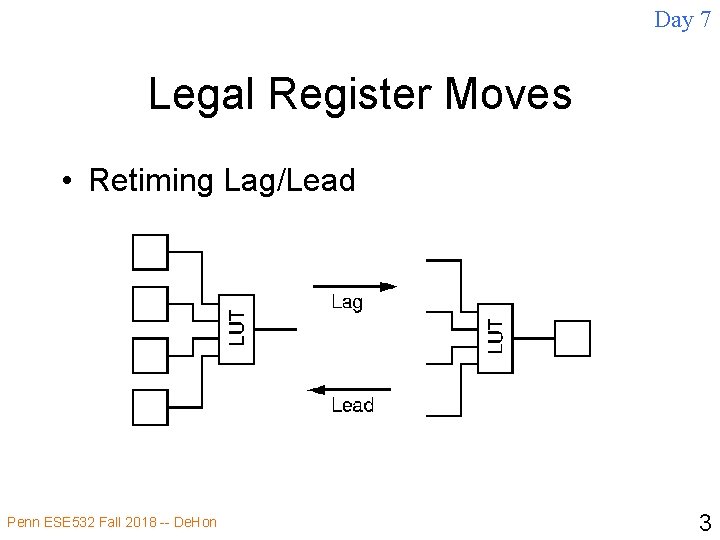

Day 7 Legal Register Moves • Retiming Lag/Lead Penn ESE 532 Fall 2018 -- De. Hon 3

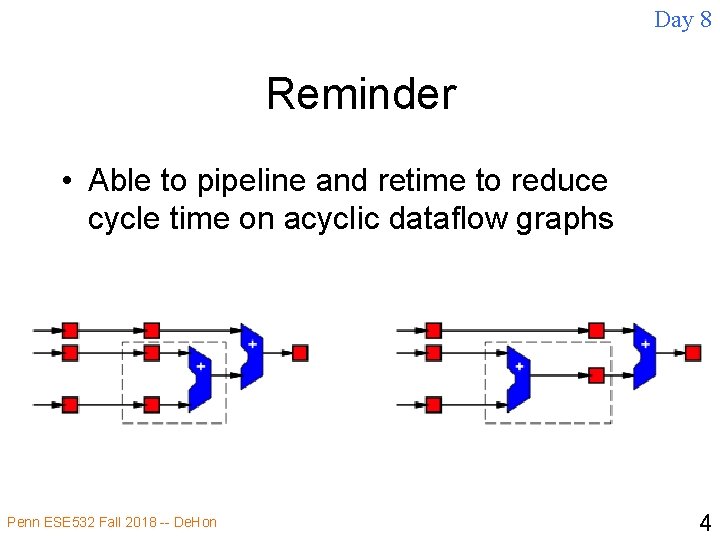

Day 8 Reminder • Able to pipeline and retime to reduce cycle time on acyclic dataflow graphs Penn ESE 532 Fall 2018 -- De. Hon 4

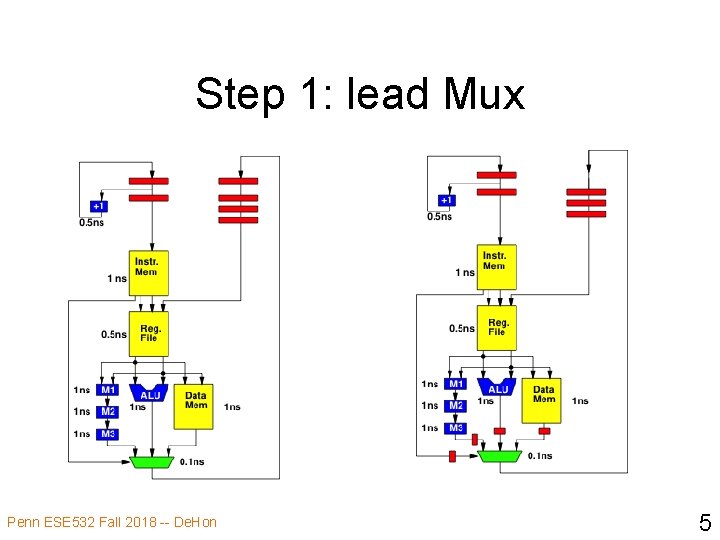

Step 1: lead Mux Penn ESE 532 Fall 2018 -- De. Hon 5

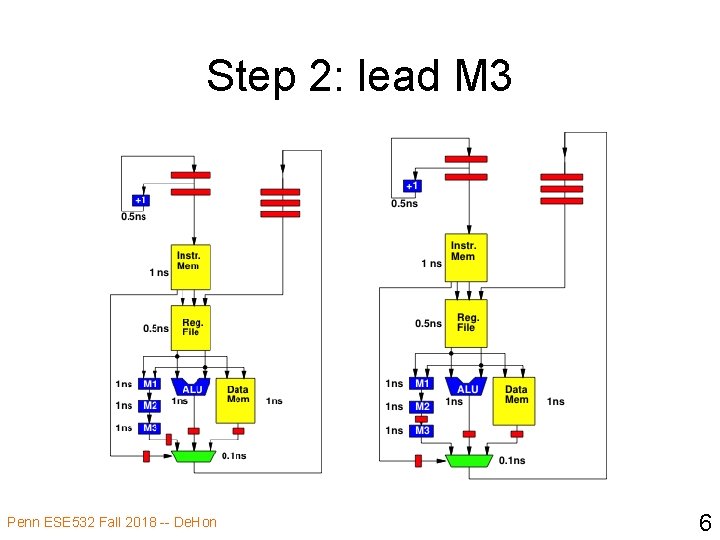

Step 2: lead M 3 Penn ESE 532 Fall 2018 -- De. Hon 6

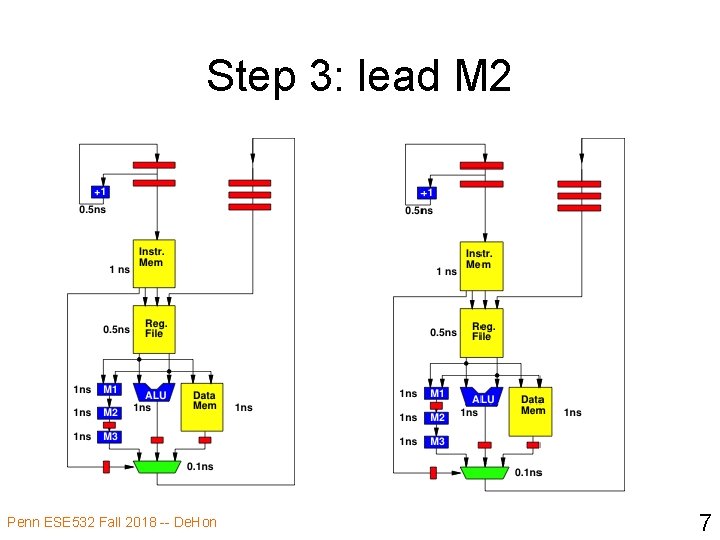

Step 3: lead M 2 Penn ESE 532 Fall 2018 -- De. Hon 7

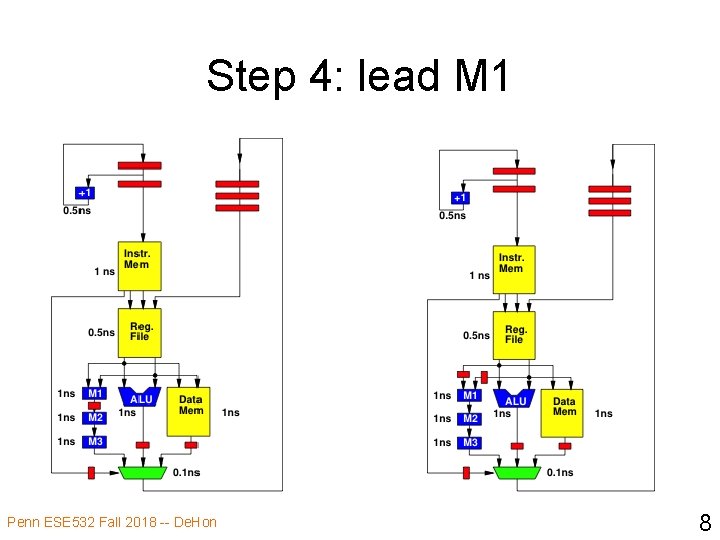

Step 4: lead M 1 Penn ESE 532 Fall 2018 -- De. Hon 8

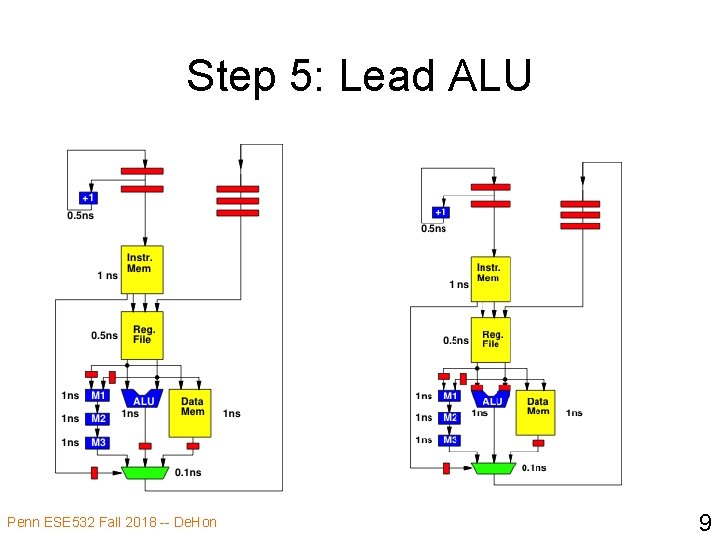

Step 5: Lead ALU Penn ESE 532 Fall 2018 -- De. Hon 9

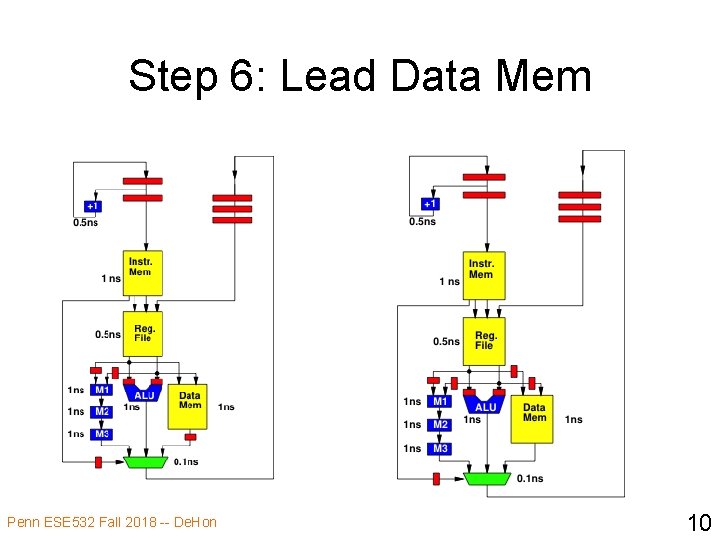

Step 6: Lead Data Mem Penn ESE 532 Fall 2018 -- De. Hon 10

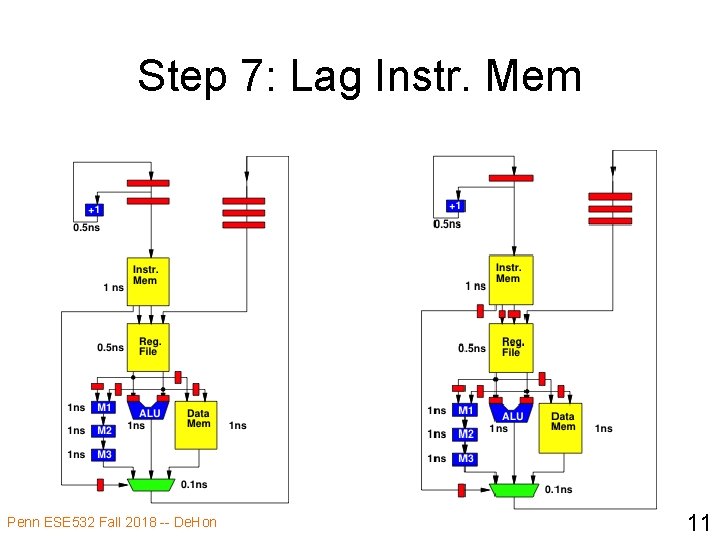

Step 7: Lag Instr. Mem Penn ESE 532 Fall 2018 -- De. Hon 11

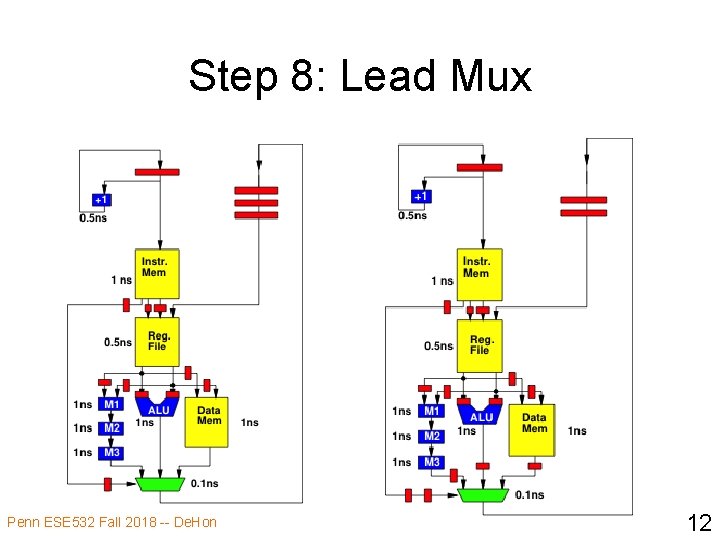

Step 8: Lead Mux Penn ESE 532 Fall 2018 -- De. Hon 12

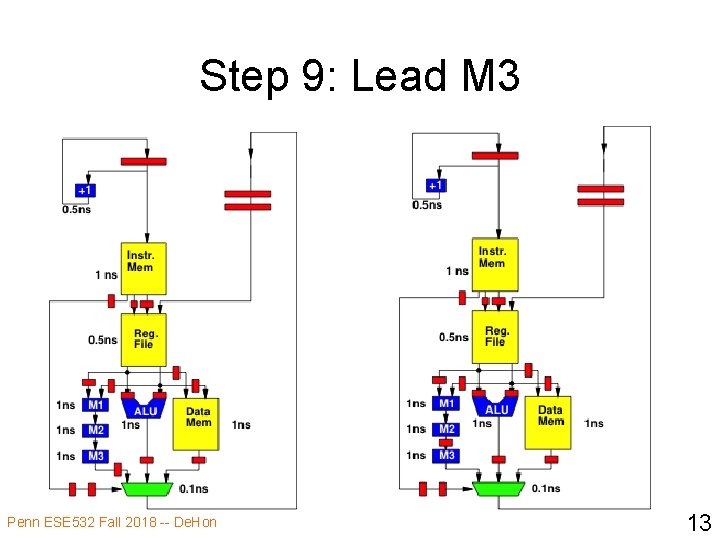

Step 9: Lead M 3 Penn ESE 532 Fall 2018 -- De. Hon 13

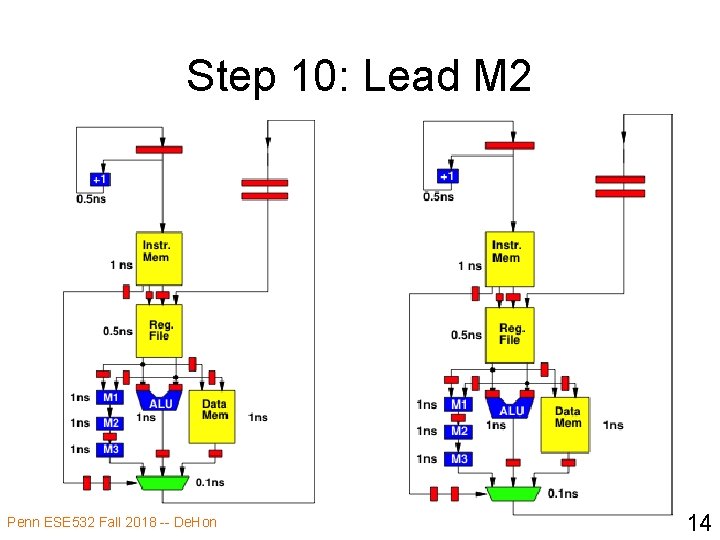

Step 10: Lead M 2 Penn ESE 532 Fall 2018 -- De. Hon 14

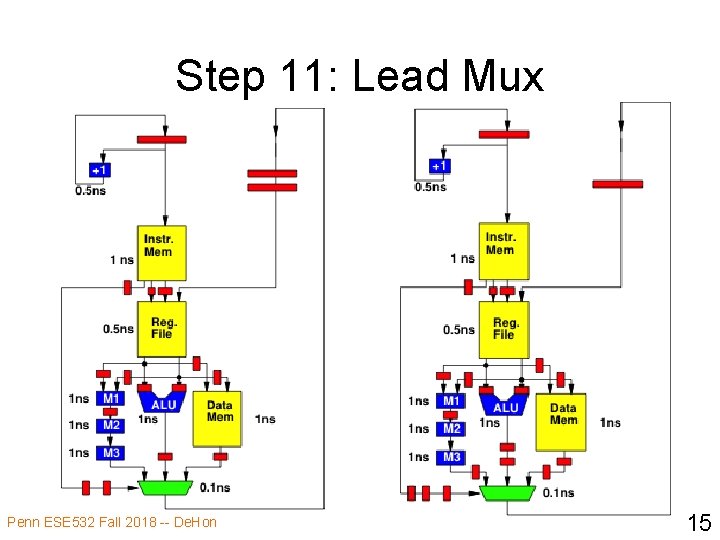

Step 11: Lead Mux Penn ESE 532 Fall 2018 -- De. Hon 15

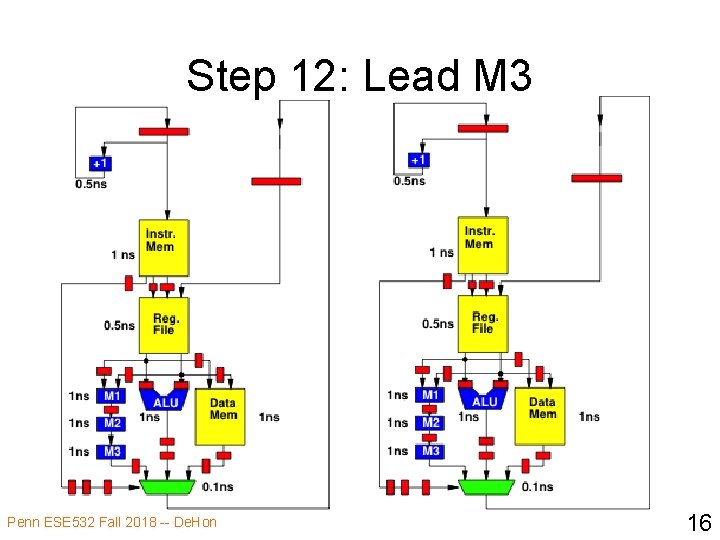

Step 12: Lead M 3 Penn ESE 532 Fall 2018 -- De. Hon 16

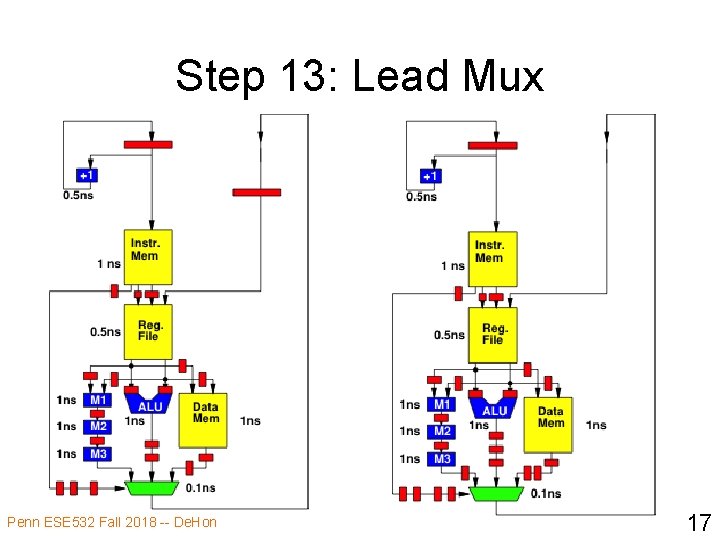

Step 13: Lead Mux Penn ESE 532 Fall 2018 -- De. Hon 17

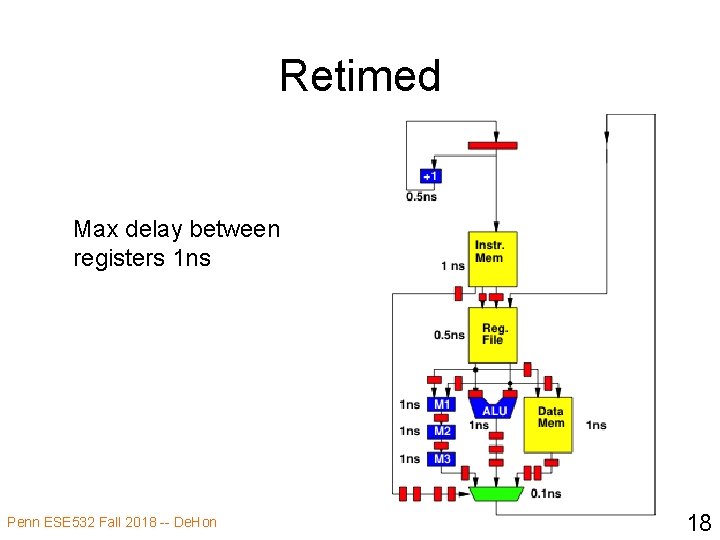

Retimed Max delay between registers 1 ns Penn ESE 532 Fall 2018 -- De. Hon 18

- Slides: 18