ESE 370 CircuitLevel Modeling Design and Optimization for

- Slides: 27

ESE 370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 27: November 5, 2014 Dynamic Logic Midterm 2 Avg: 58 Std Dev. : 15 Penn ESE 370 Fall 2014 -- De. Hon 1

Today • Clocking • Dynamic (Clocked) Logic – Strategy – Form – Compare CMOS Penn ESE 370 Fall 2014 -- De. Hon 2

Penn ESE 370 Fall 2014 -- De. Hon 3

Clocking Penn ESE 370 Fall 2014 -- De. Hon 4

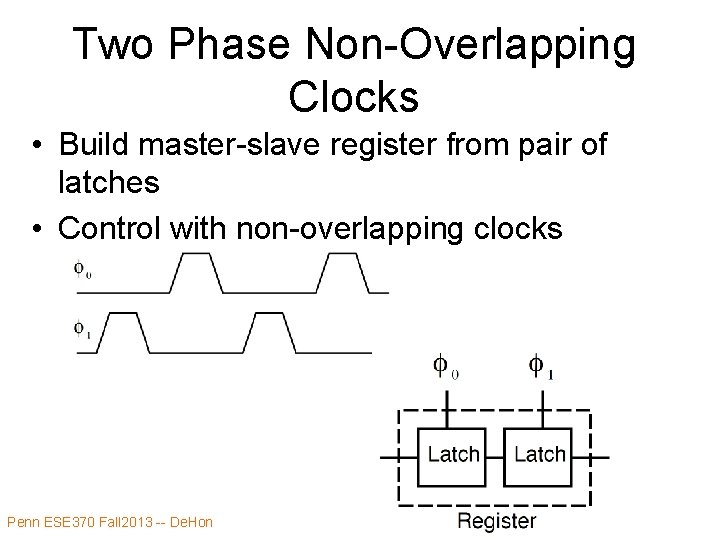

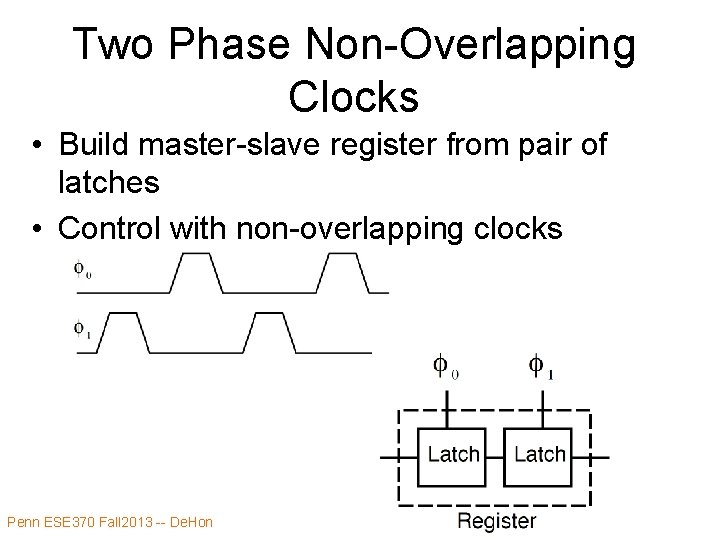

Two Phase Non-Overlapping Clocks • Build master-slave register from pair of latches • Control with non-overlapping clocks Penn ESE 370 Fall 2013 -- De. Hon 5

Clocking Highlights • Clock discipline simplifies logic composition – Abstracts many internal timing details – Just concerned with making clock period long enough • Breaking logic up with registers allows to run at high frequency – reuse logic • Discipline – keeping data stable around clock edge – Setup, hold time – determined by circuit – Clk Q delay for data come out of register Penn ESE 370 Fall 2014 -- De. Hon 6

Clocking • Circuits typically operate in a clocked environment • Gives some additional structure we can exploit Penn ESE 370 Fall 2014 -- De. Hon 7

Dynamic Logic Penn ESE 370 Fall 2014 -- De. Hon 8

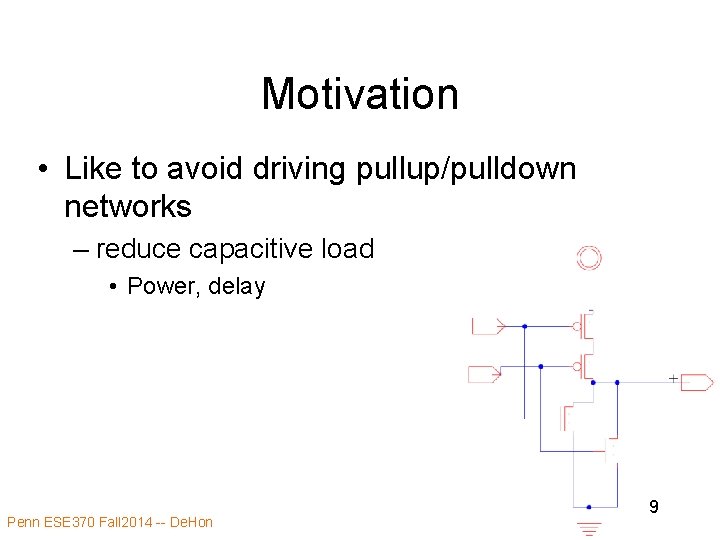

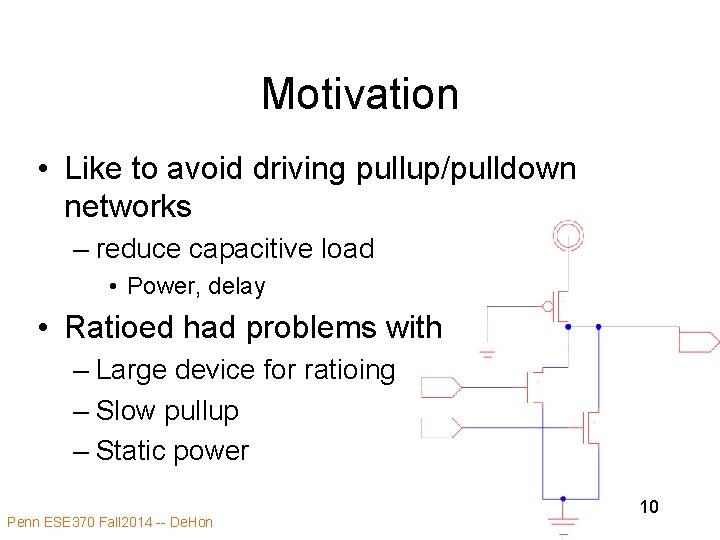

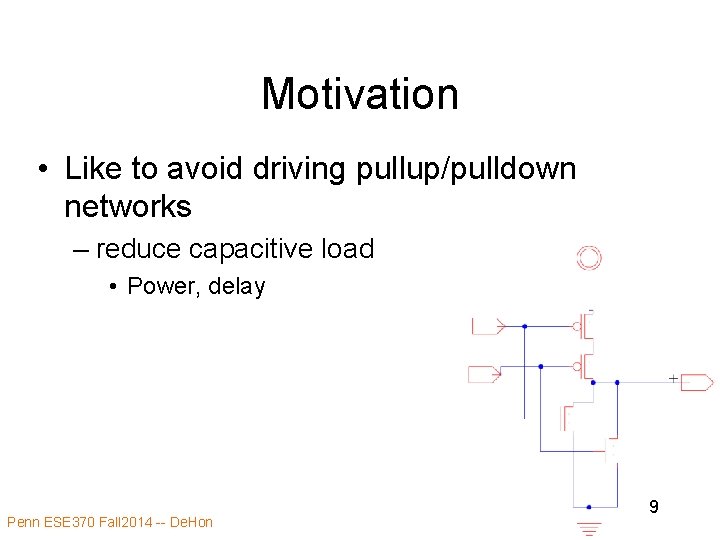

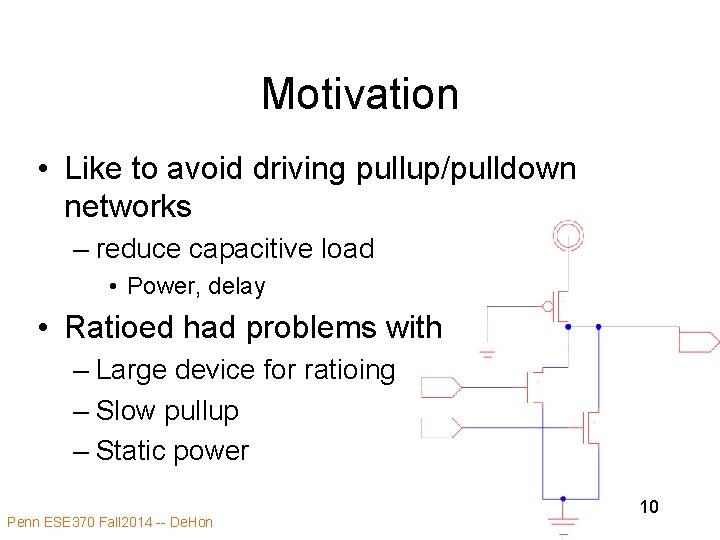

Motivation • Like to avoid driving pullup/pulldown networks – reduce capacitive load • Power, delay Penn ESE 370 Fall 2014 -- De. Hon 9

Motivation • Like to avoid driving pullup/pulldown networks – reduce capacitive load • Power, delay • Ratioed had problems with – Large device for ratioing – Slow pullup – Static power Penn ESE 370 Fall 2014 -- De. Hon 10

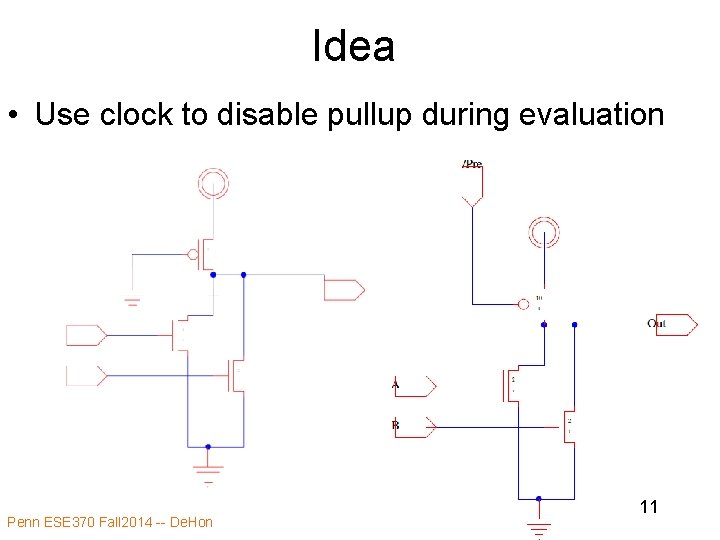

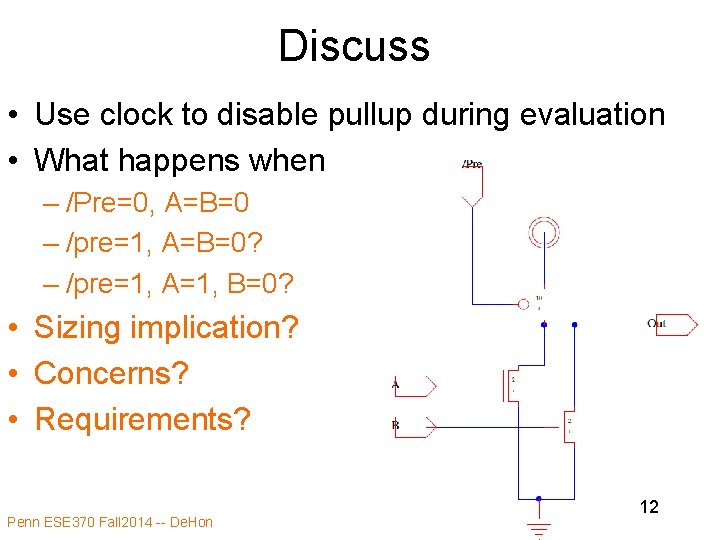

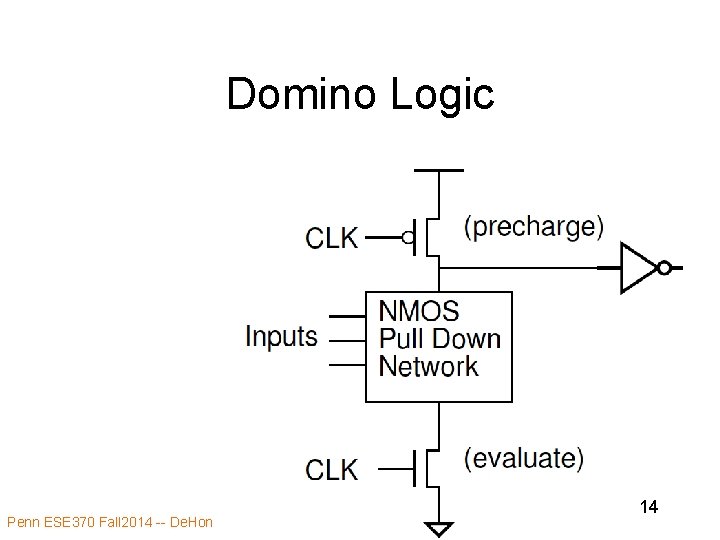

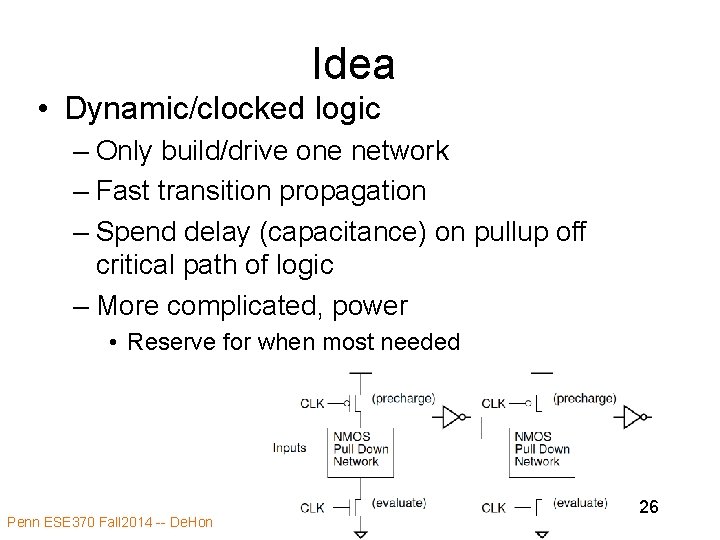

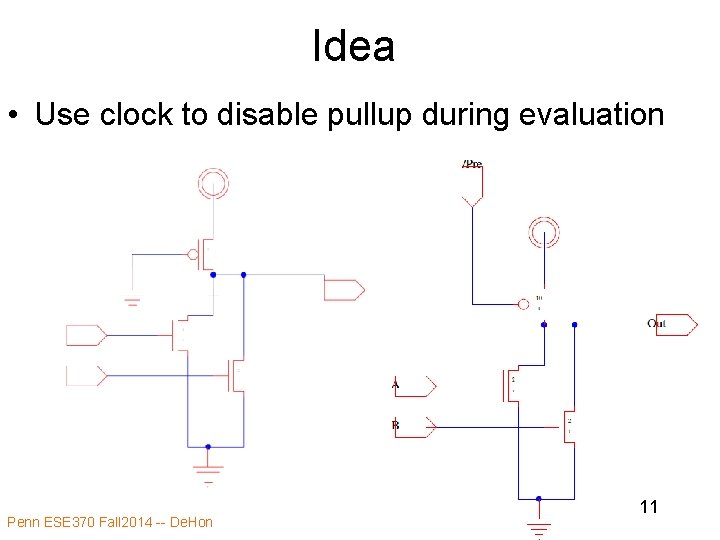

Idea • Use clock to disable pullup during evaluation Penn ESE 370 Fall 2014 -- De. Hon 11

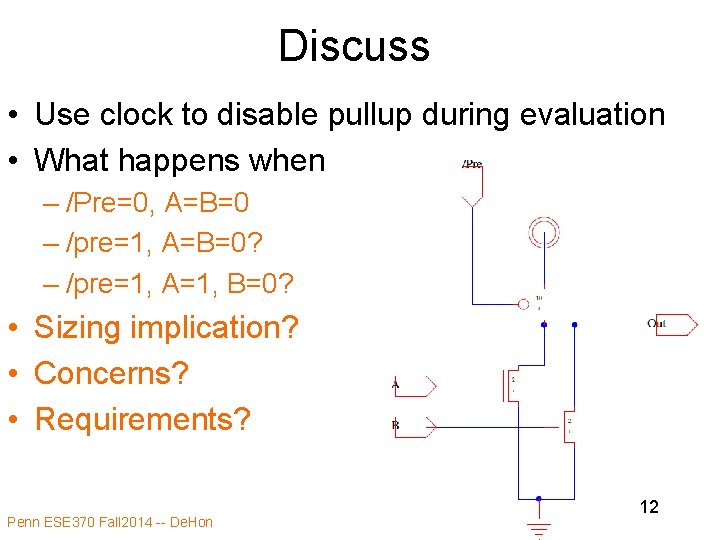

Discuss • Use clock to disable pullup during evaluation • What happens when – /Pre=0, A=B=0 – /pre=1, A=B=0? – /pre=1, A=1, B=0? • Sizing implication? • Concerns? • Requirements? Penn ESE 370 Fall 2014 -- De. Hon 12

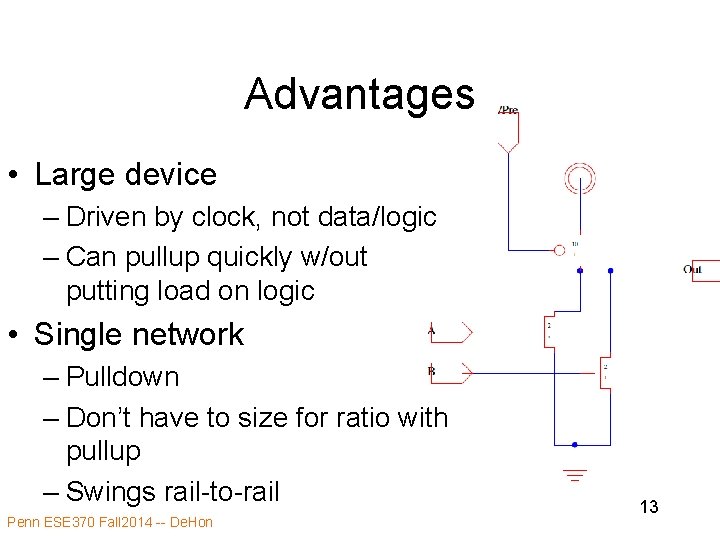

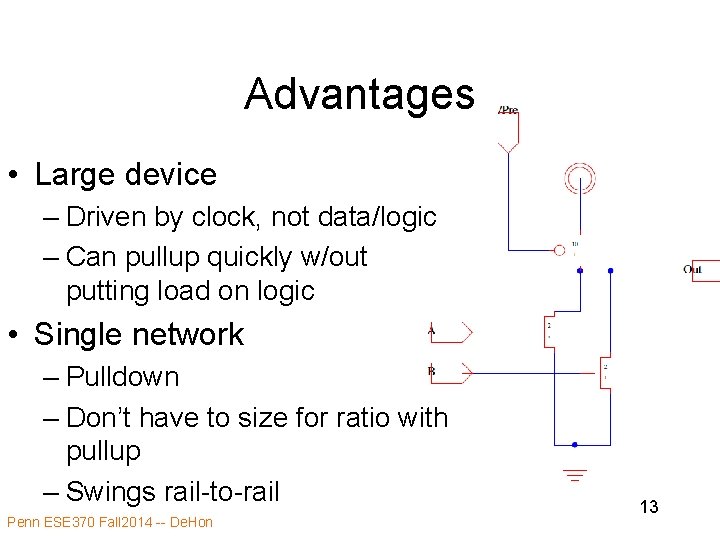

Advantages • Large device – Driven by clock, not data/logic – Can pullup quickly w/out putting load on logic • Single network – Pulldown – Don’t have to size for ratio with pullup – Swings rail-to-rail Penn ESE 370 Fall 2014 -- De. Hon 13

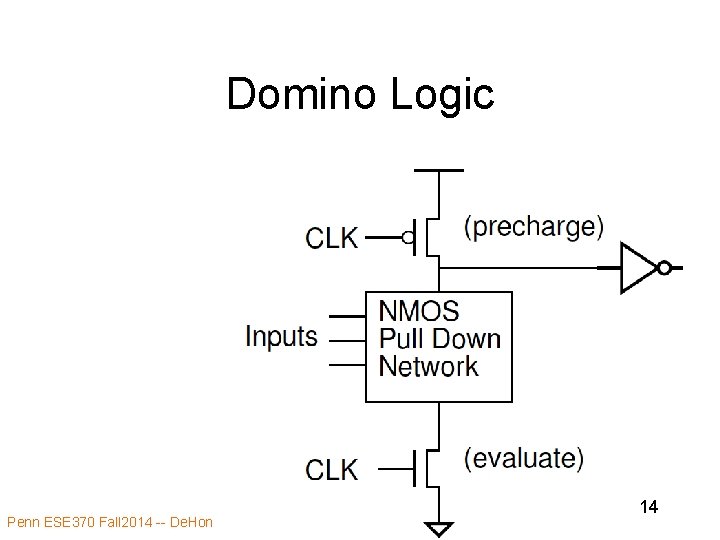

Domino Logic Penn ESE 370 Fall 2014 -- De. Hon 14

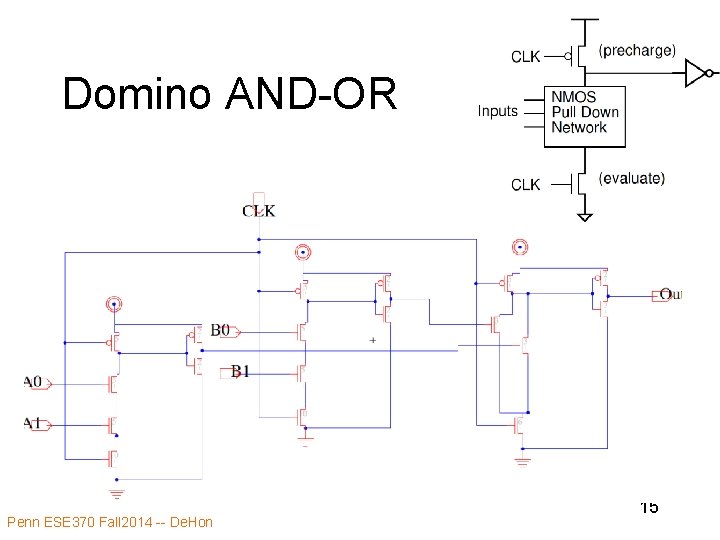

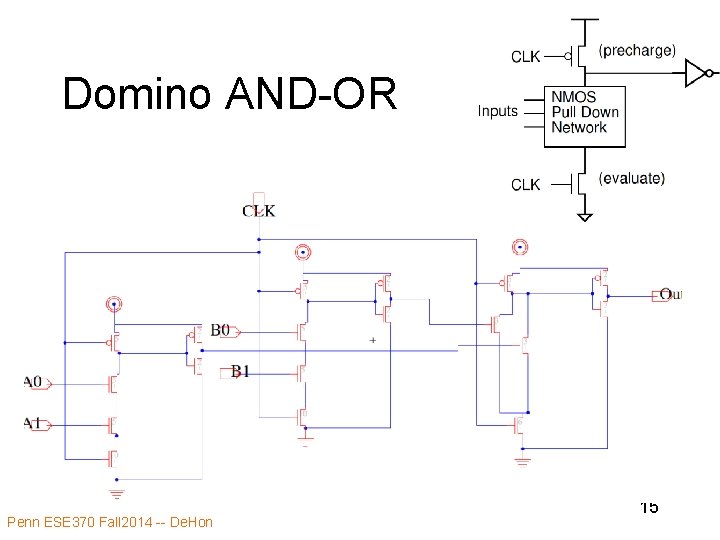

Domino AND-OR Penn ESE 370 Fall 2014 -- De. Hon 15

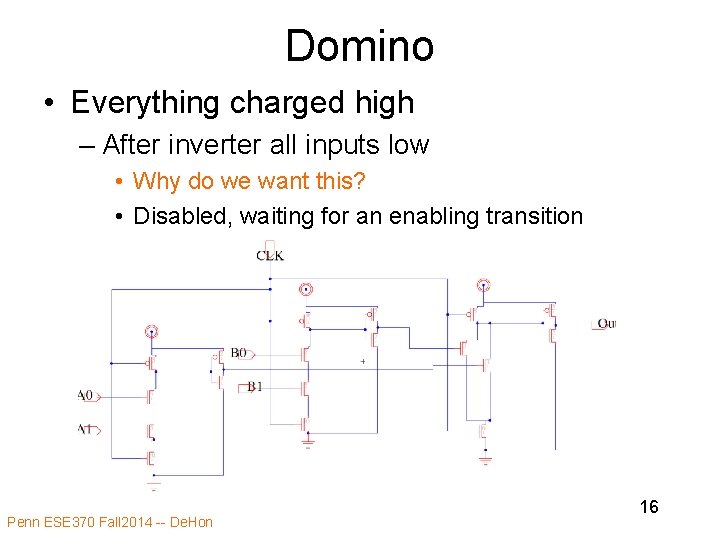

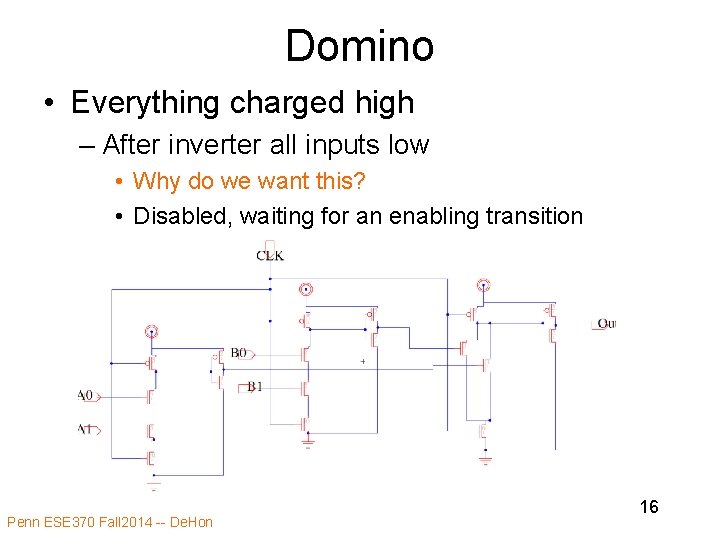

Domino • Everything charged high – After inverter all inputs low • Why do we want this? • Disabled, waiting for an enabling transition Penn ESE 370 Fall 2014 -- De. Hon 16

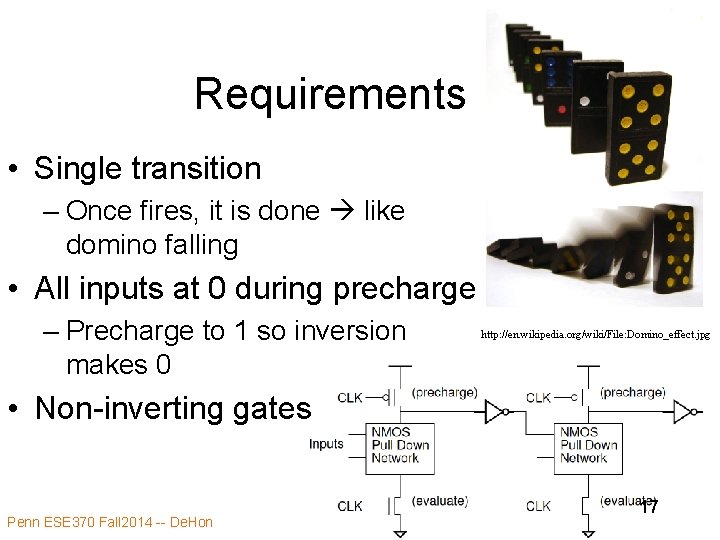

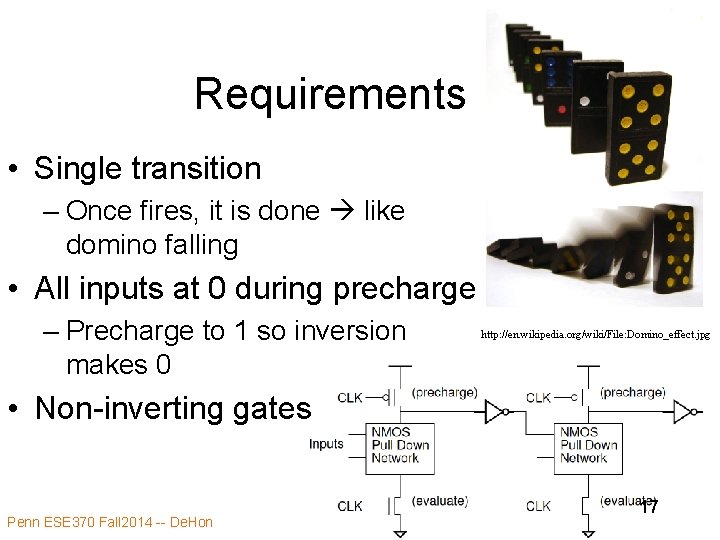

Requirements • Single transition – Once fires, it is done like domino falling • All inputs at 0 during precharge – Precharge to 1 so inversion makes 0 http: //en. wikipedia. org/wiki/File: Domino_effect. jpg • Non-inverting gates Penn ESE 370 Fall 2014 -- De. Hon 17

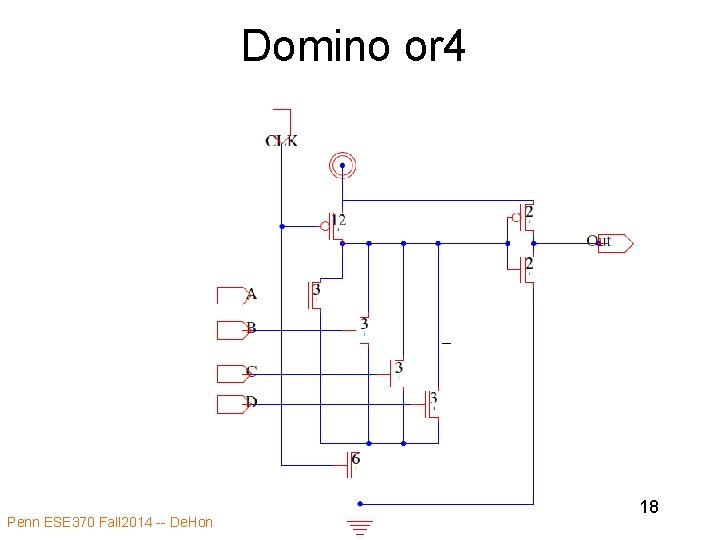

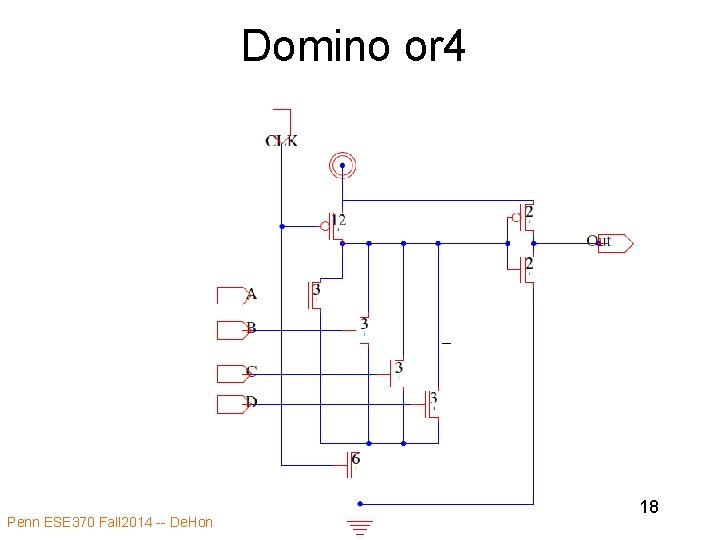

Domino or 4 Penn ESE 370 Fall 2014 -- De. Hon 18

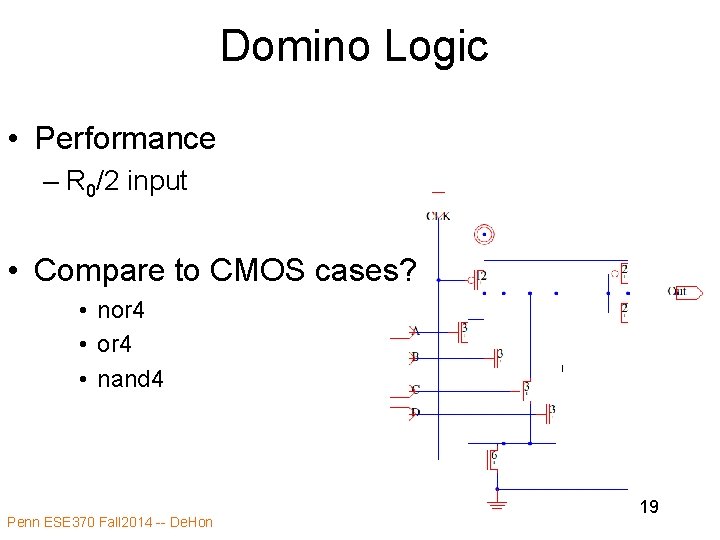

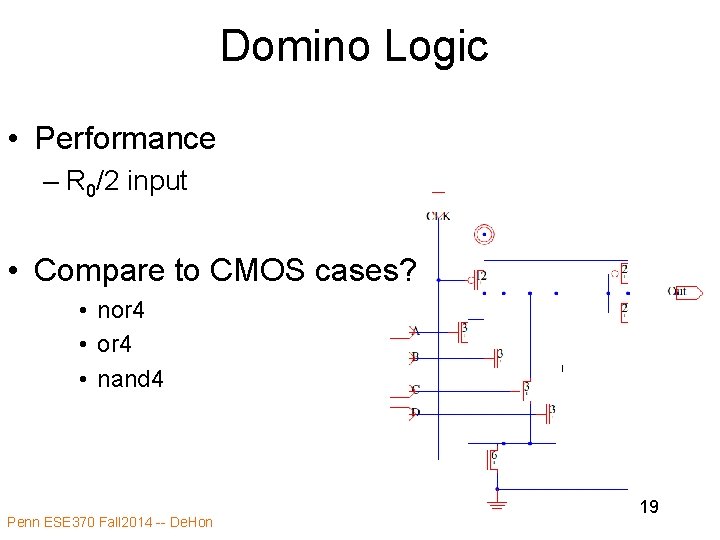

Domino Logic • Performance – R 0/2 input • Compare to CMOS cases? • nor 4 • nand 4 Penn ESE 370 Fall 2014 -- De. Hon 19

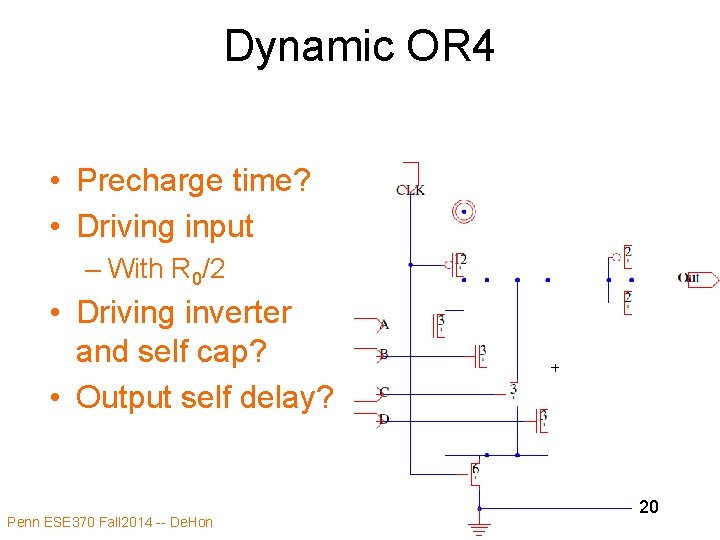

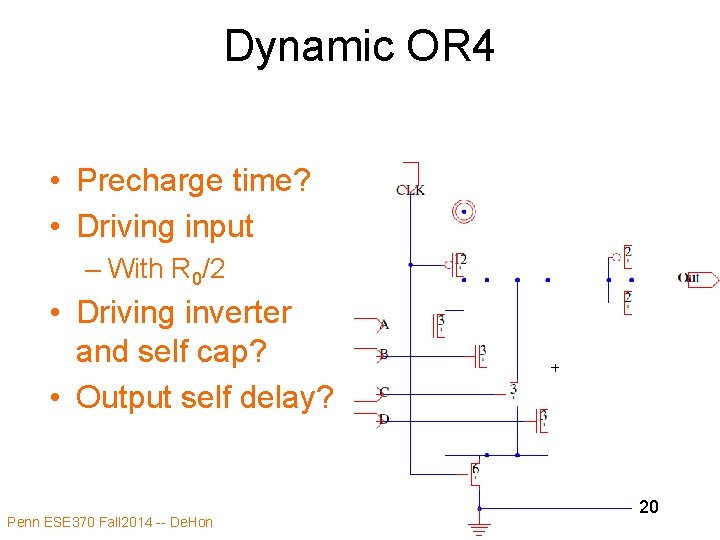

Dynamic OR 4 • Precharge time? • Driving input – With R 0/2 • Driving inverter and self cap? • Output self delay? Penn ESE 370 Fall 2014 -- De. Hon 20

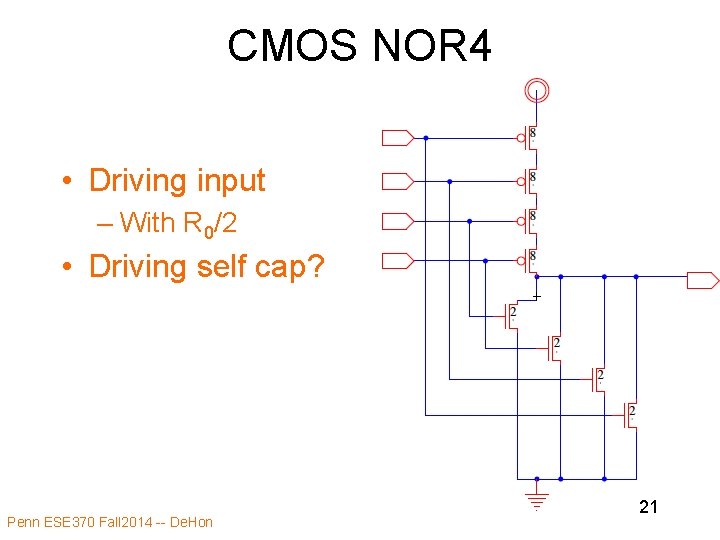

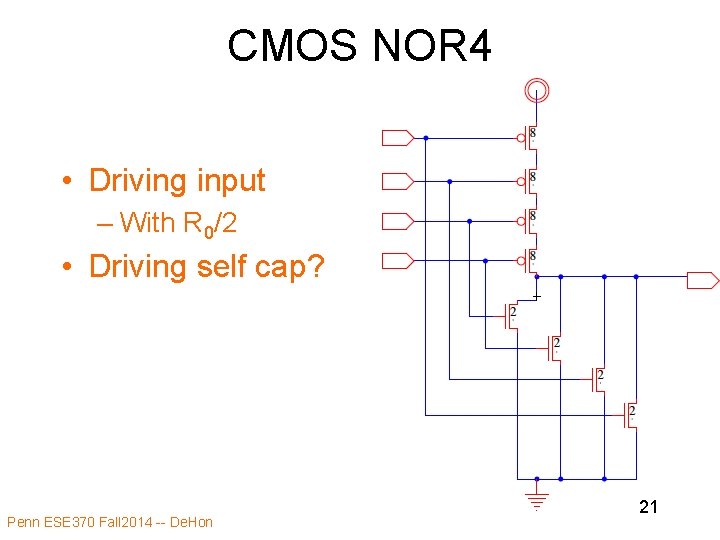

CMOS NOR 4 • Driving input – With R 0/2 • Driving self cap? Penn ESE 370 Fall 2014 -- De. Hon 21

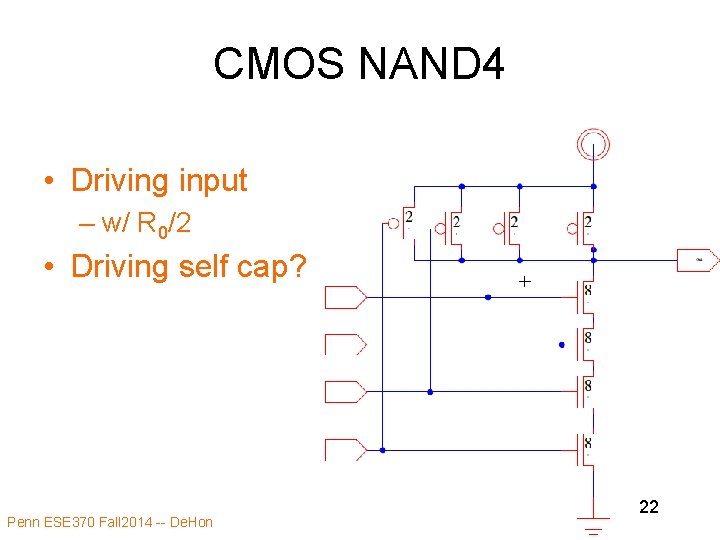

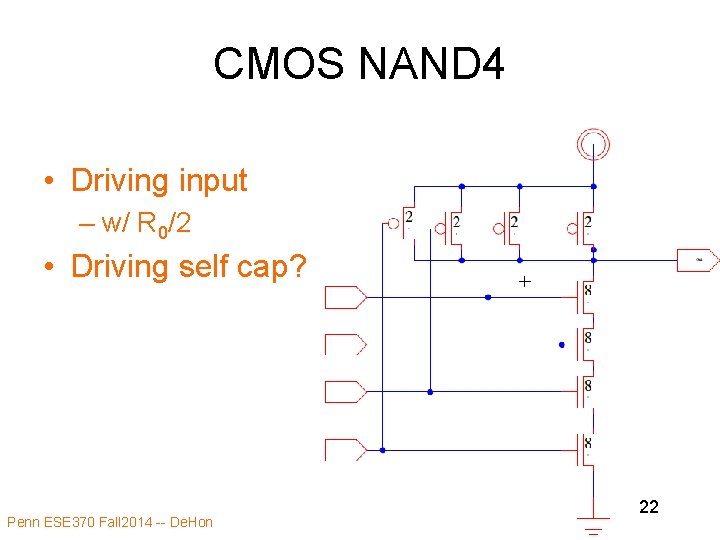

CMOS NAND 4 • Driving input – w/ R 0/2 • Driving self cap? Penn ESE 370 Fall 2014 -- De. Hon 22

Issues • Noise sensitive • Power? • Activity? Penn ESE 370 Fall 2014 -- De. Hon 23

Discuss (time permit) • Avoid inversion? • Converting from CMOS? • Post-charge Penn ESE 370 Fall 2014 -- De. Hon 24

Observe • Better (lower) ratio of input capacitance to drive strength • Particularly good for – Driving large loads – Large fanin gates • Harder to design with – Timing and polarity restrictions – Avoiding noise • Especially with today’s high variation tech. • Can consume more energy/op Penn ESE 370 Fall 2014 -- De. Hon 25

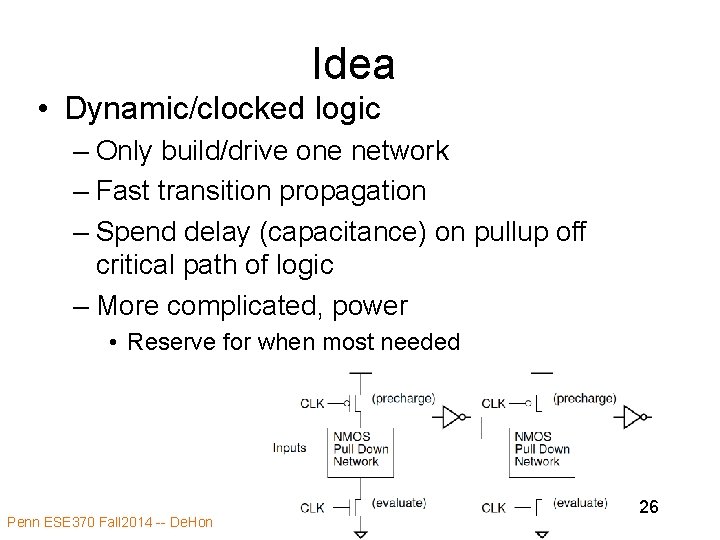

Idea • Dynamic/clocked logic – Only build/drive one network – Fast transition propagation – Spend delay (capacitance) on pullup off critical path of logic – More complicated, power • Reserve for when most needed Penn ESE 370 Fall 2014 -- De. Hon 26

Admin • Homework 7 out – …and due on Tuesday • Withdraw date Friday Penn ESE 370 Fall 2014 -- De. Hon 27