ESE 370 CircuitLevel Modeling Design and Optimization for

- Slides: 33

ESE 370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 20: October 17, 2014 Ratioed Logic Penn ESE 370 Fall 2014 -- De. Hon 1

Previously • Restoration and Noise Margins • CMOS Gates – Drive rail-to-rail – Only one transistor turned on in steady state • Only subthreshold current in steady state Penn ESE 370 Fall 2014 -- De. Hon 2

Today • Ratioed Gates – Break all the rules… (nice properties) • Not rail-to-rail, steady-state-current… – Correctness – Performance – Power – Implications Penn ESE 370 Fall 2014 -- De. Hon 3

Note on what about to see • Not clear win • Should be able to analyze – Chance to exercise analysis – Kind of thing you want to be able to analyze • Pattern should recognize • Stepping stone to more interesting things to come… Penn ESE 370 Fall 2014 -- De. Hon 4

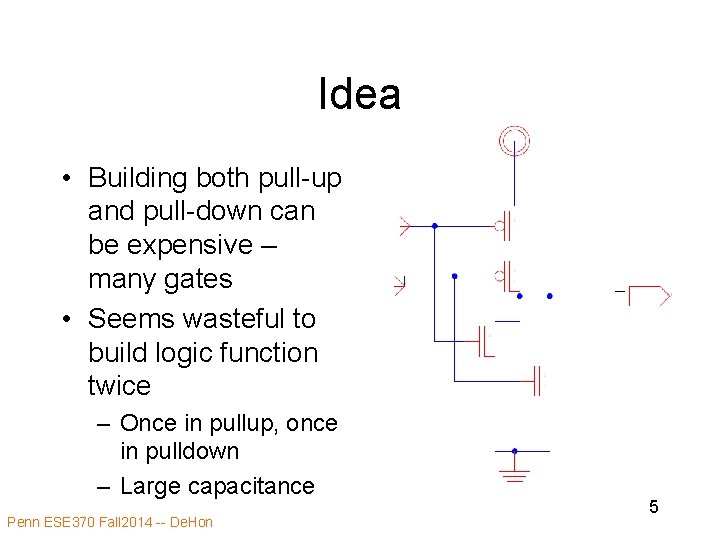

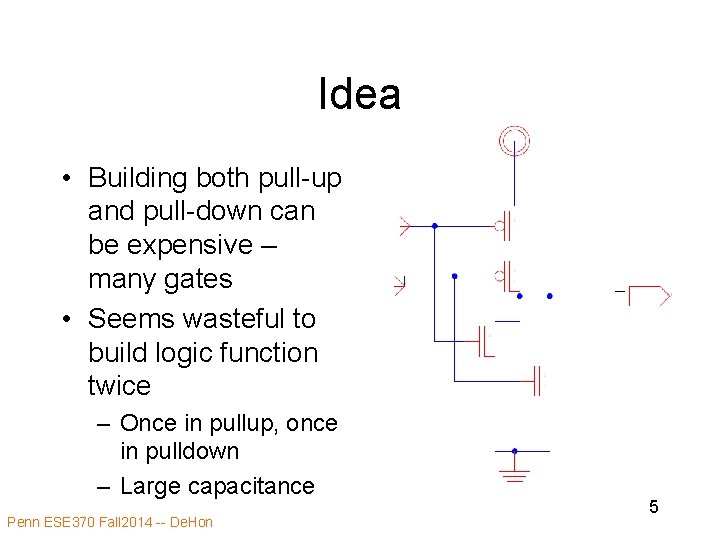

Idea • Building both pull-up and pull-down can be expensive – many gates • Seems wasteful to build logic function twice – Once in pullup, once in pulldown – Large capacitance Penn ESE 370 Fall 2014 -- De. Hon 5

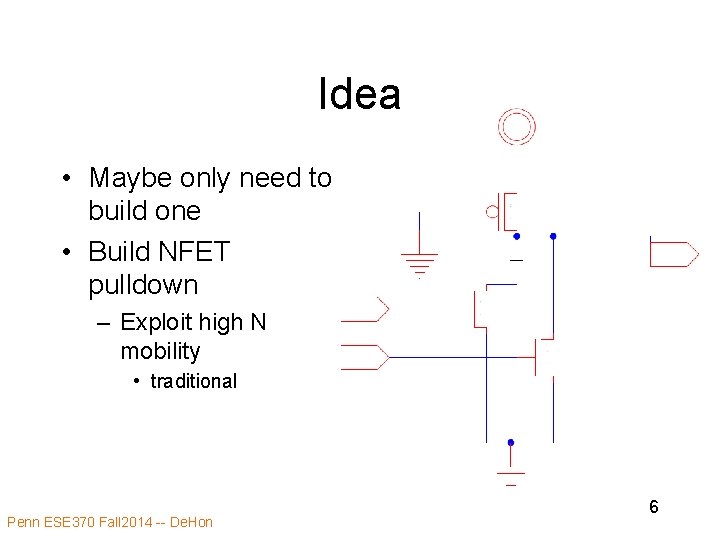

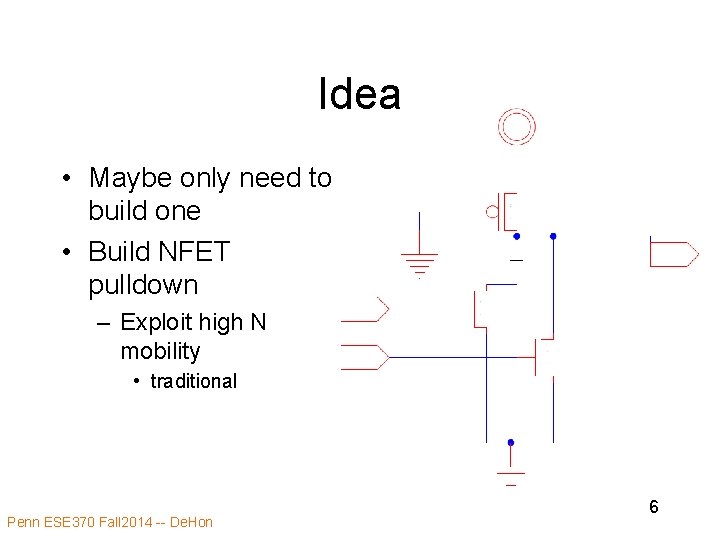

Idea • Maybe only need to build one • Build NFET pulldown – Exploit high N mobility • traditional Penn ESE 370 Fall 2014 -- De. Hon 6

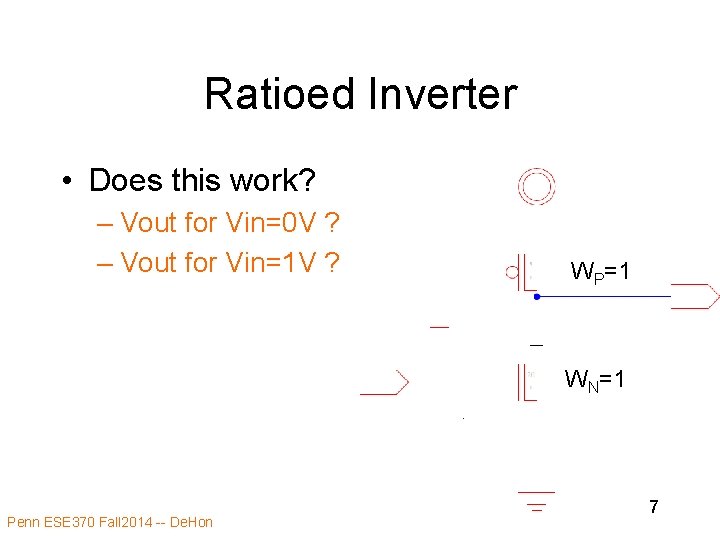

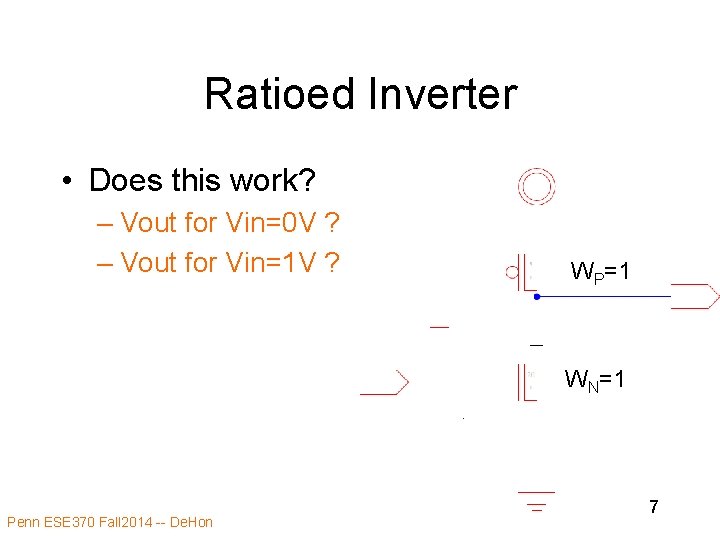

Ratioed Inverter • Does this work? – Vout for Vin=0 V ? – Vout for Vin=1 V ? WP=1 WN=1 Penn ESE 370 Fall 2014 -- De. Hon 7

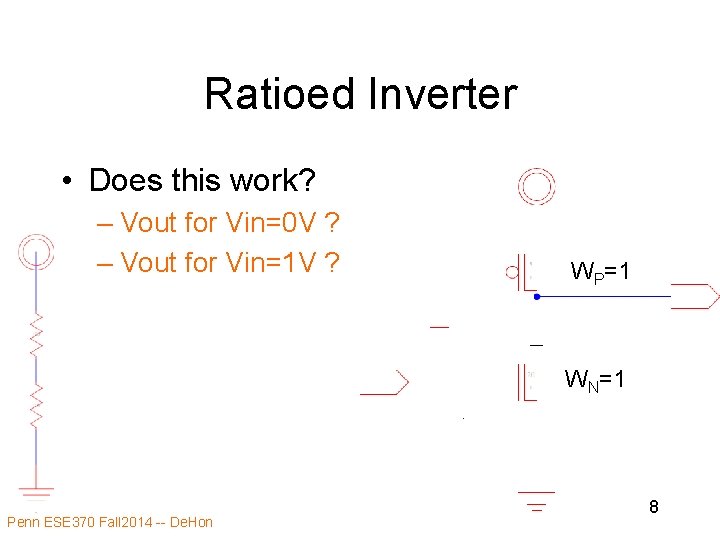

Ratioed Inverter • Does this work? – Vout for Vin=0 V ? – Vout for Vin=1 V ? WP=1 WN=1 Penn ESE 370 Fall 2014 -- De. Hon 8

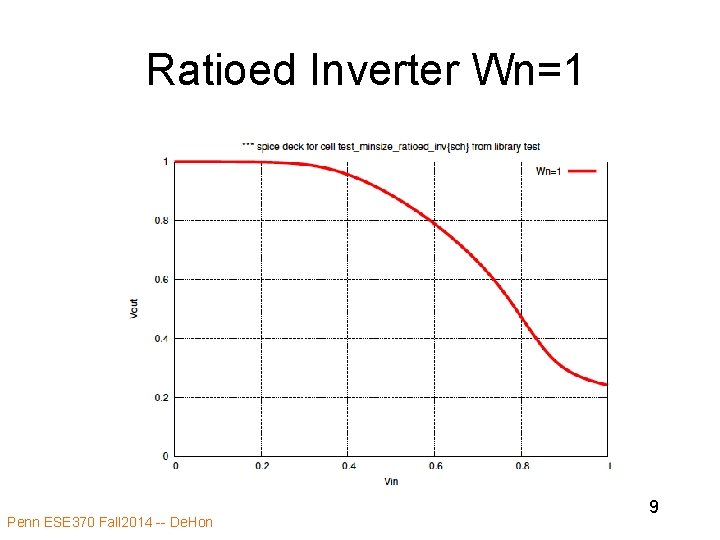

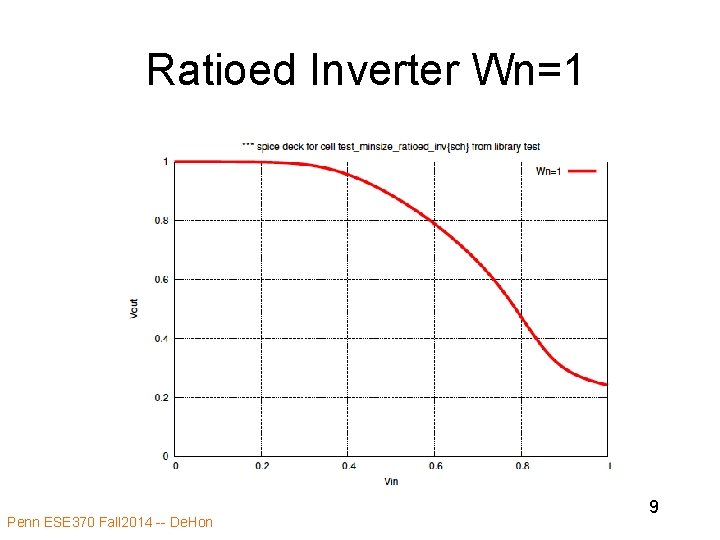

Ratioed Inverter Wn=1 Penn ESE 370 Fall 2014 -- De. Hon 9

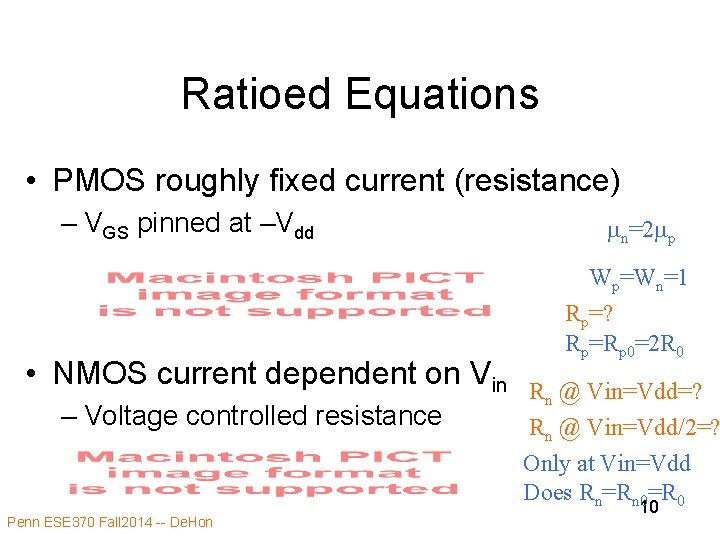

Ratioed Equations • PMOS roughly fixed current (resistance) – VGS pinned at –Vdd • NMOS current dependent on Vin – Voltage controlled resistance Penn ESE 370 Fall 2014 -- De. Hon mn=2 mp Wp=Wn=1 Rp=? Rp=Rp 0=2 R 0 Rn @ Vin=Vdd=? Rn @ Vin=Vdd/2=? Only at Vin=Vdd Does Rn=Rn 0=R 0 10

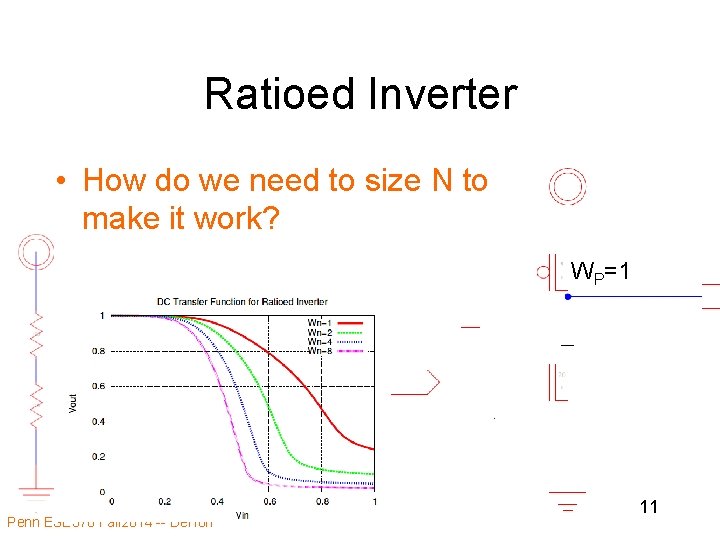

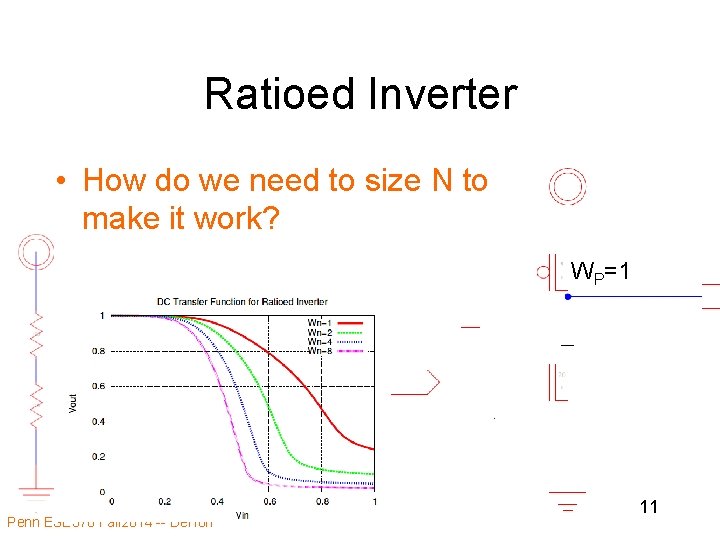

Ratioed Inverter • How do we need to size N to make it work? WP=1 Penn ESE 370 Fall 2014 -- De. Hon 11

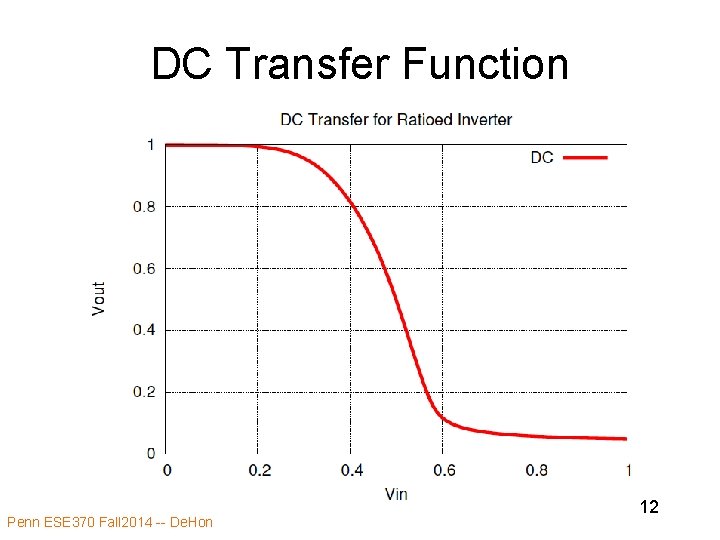

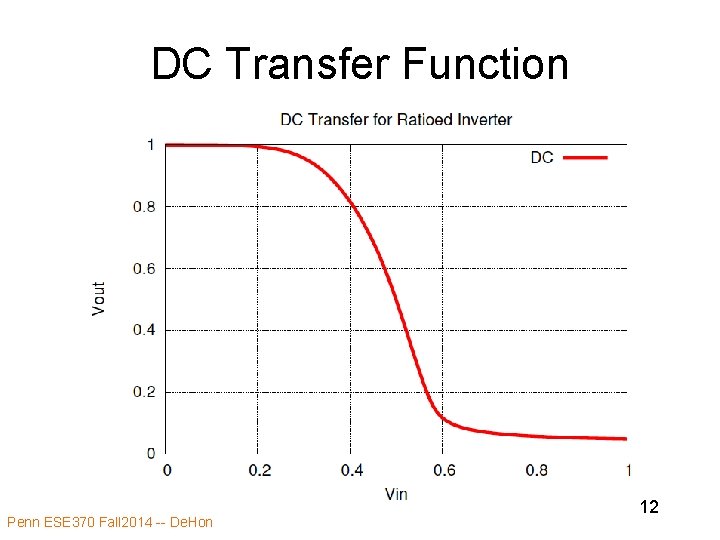

DC Transfer Function Penn ESE 370 Fall 2014 -- De. Hon 12

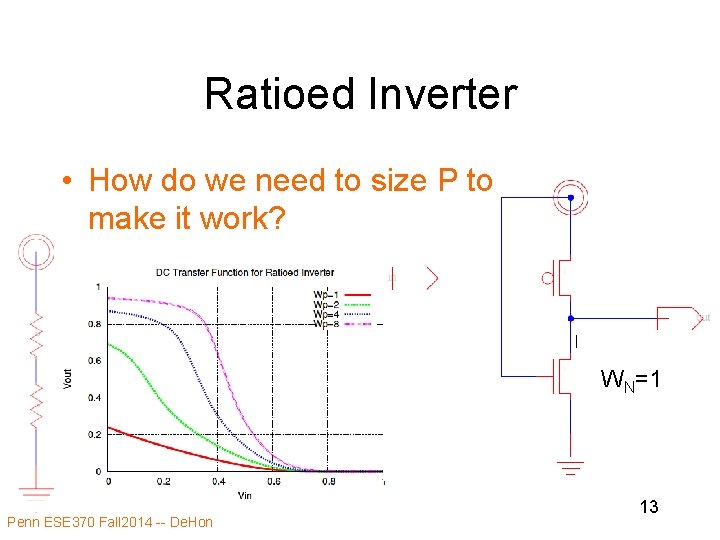

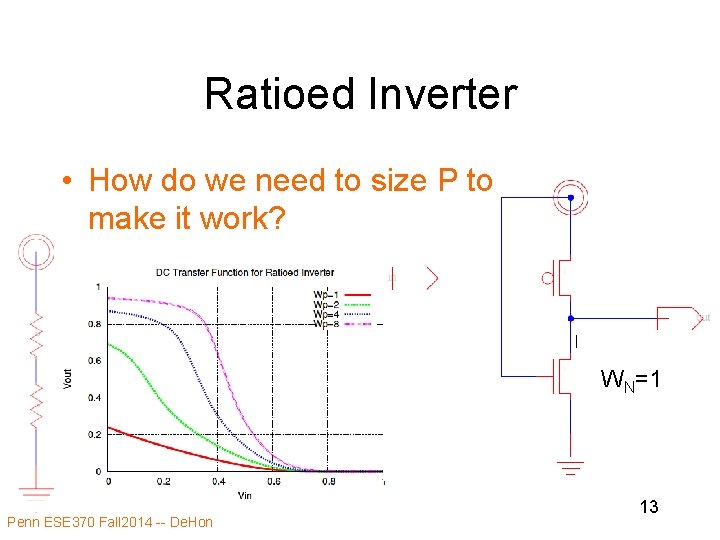

Ratioed Inverter • How do we need to size P to make it work? WN=1 Penn ESE 370 Fall 2014 -- De. Hon 13

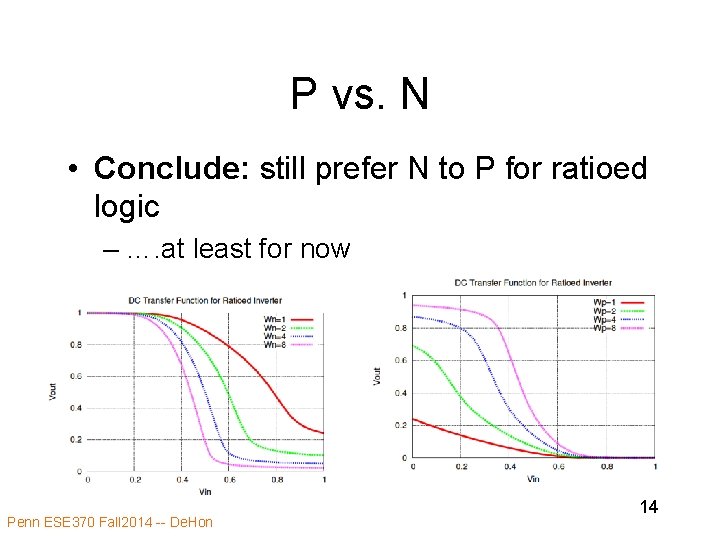

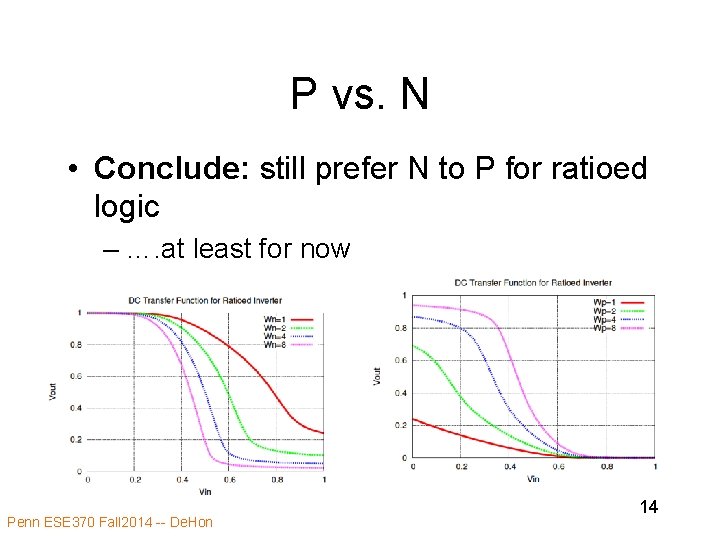

P vs. N • Conclude: still prefer N to P for ratioed logic – …. at least for now Penn ESE 370 Fall 2014 -- De. Hon 14

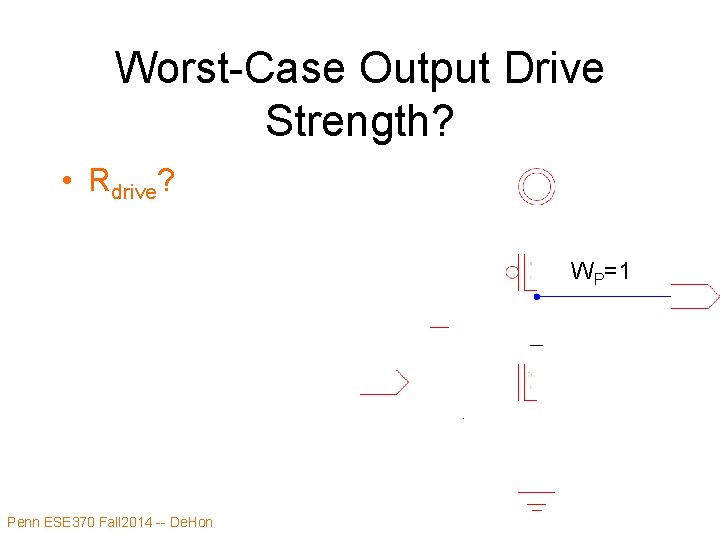

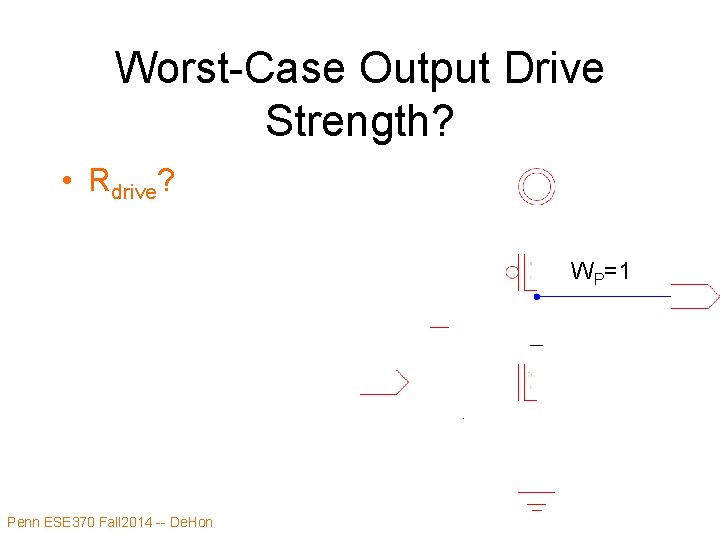

Worst-Case Output Drive Strength? • Rdrive? WP=1 Penn ESE 370 Fall 2014 -- De. Hon 15

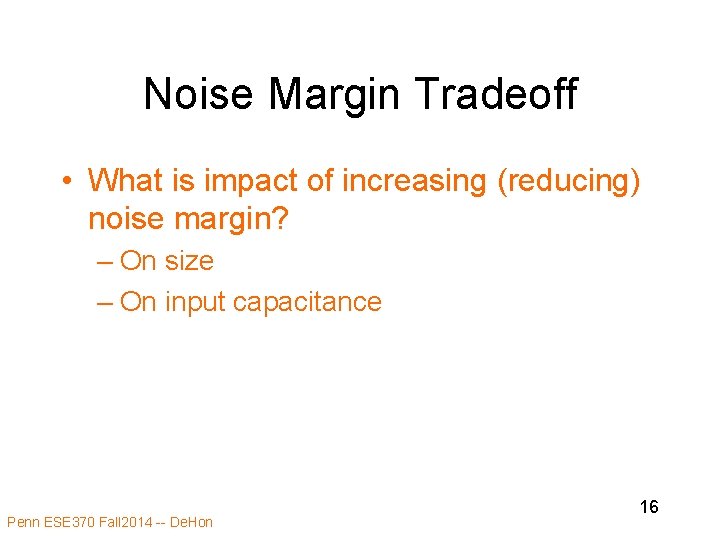

Noise Margin Tradeoff • What is impact of increasing (reducing) noise margin? – On size – On input capacitance Penn ESE 370 Fall 2014 -- De. Hon 16

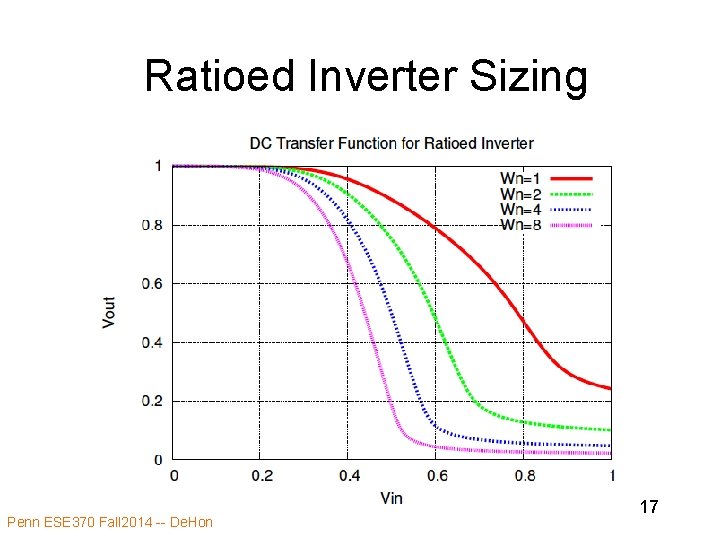

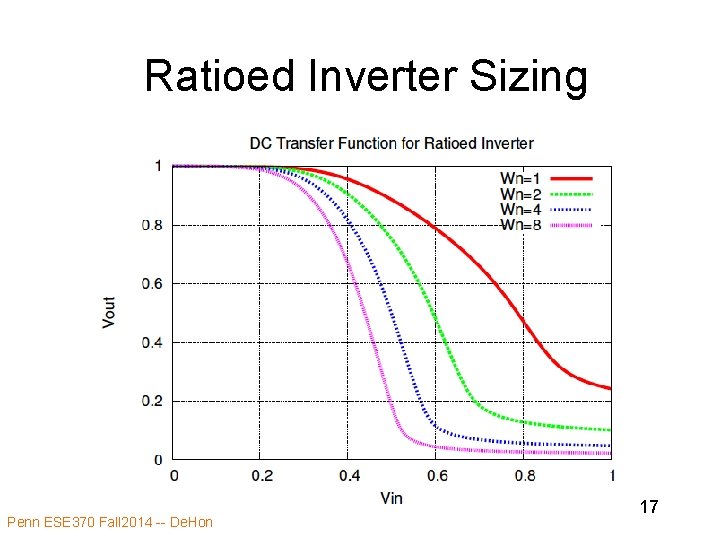

Ratioed Inverter Sizing Penn ESE 370 Fall 2014 -- De. Hon 17

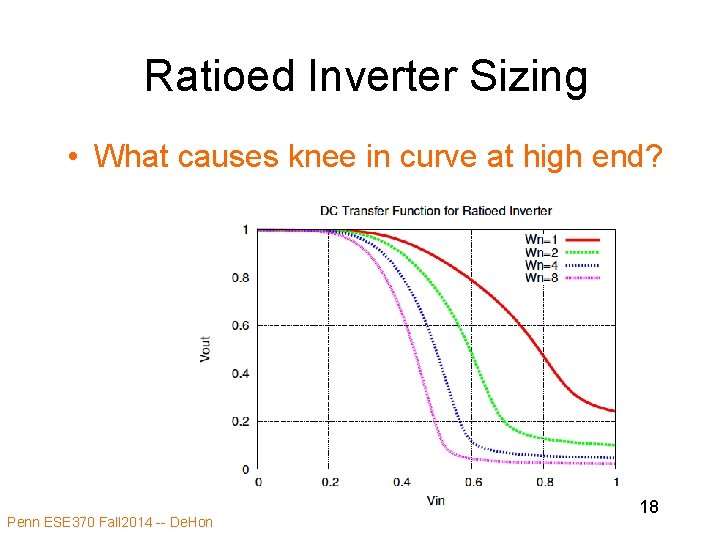

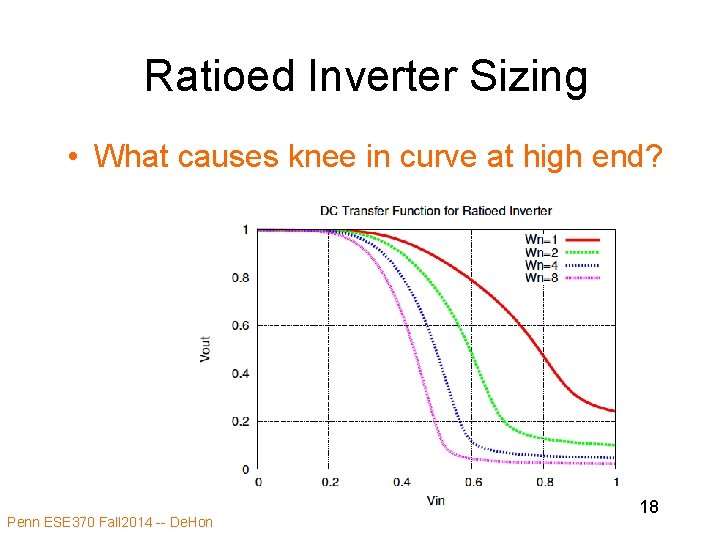

Ratioed Inverter Sizing • What causes knee in curve at high end? Penn ESE 370 Fall 2014 -- De. Hon 18

Non-VSAT Equations Penn ESE 370 Fall 2014 -- De. Hon S 19 D

Non-VSAT Equations S • P looks roughly like current source • Must Match current with N – Determine Vds – How does Wn effect Vds? Penn ESE 370 Fall 2014 -- De. Hon 20 D

Non-VSAT Equations S • Isdp constant = Idsn • Once drop into linear region – Vds < Vgs-Vt – Constant = (Vgs-Vt) Vds – Vds α 1/ (Vgs-Vt) Penn ESE 370 Fall 2014 -- De. Hon 21 D

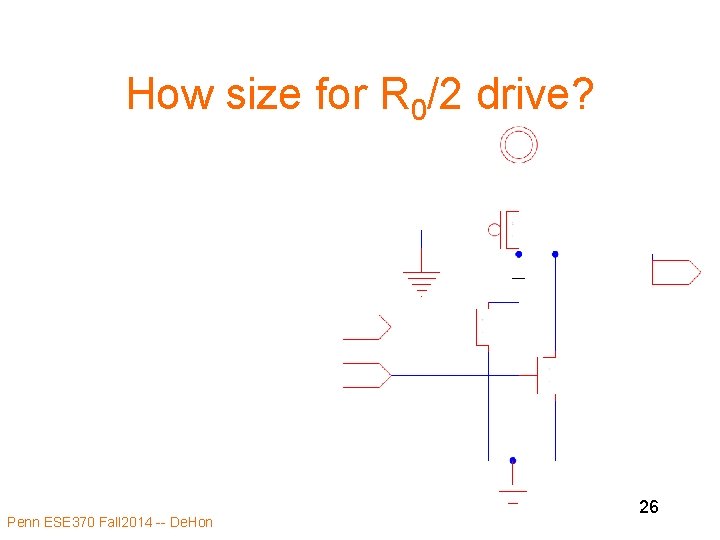

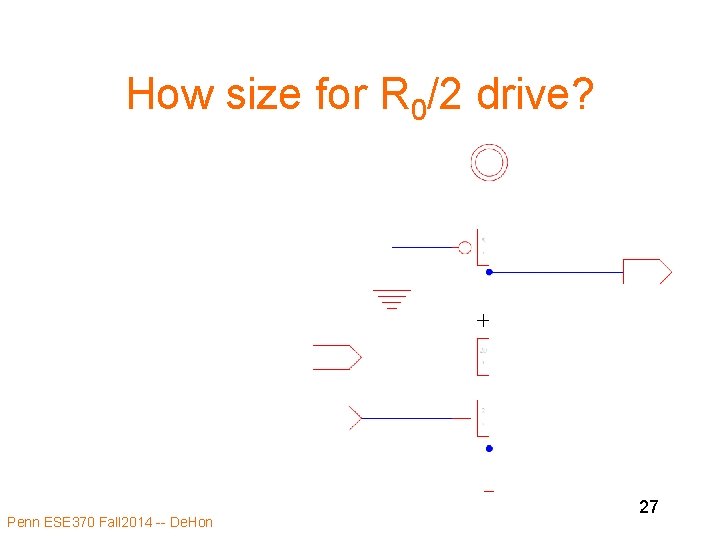

Size for R 0/2 drive? • How do we size for R 0/2 drive? Penn ESE 370 Fall 2014 -- De. Hon 22

Compare Static CMOS For Rdrive=R 0/2 inverter • Total Transistor Width? • Input capacitance load? Penn ESE 370 Fall 2014 -- De. Hon 23

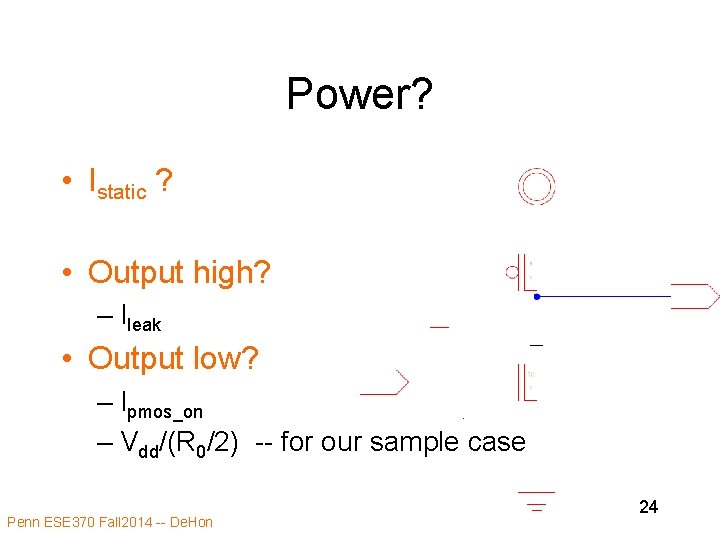

Power? • Istatic ? • Output high? – Ileak • Output low? – Ipmos_on – Vdd/(R 0/2) -- for our sample case Penn ESE 370 Fall 2014 -- De. Hon 24

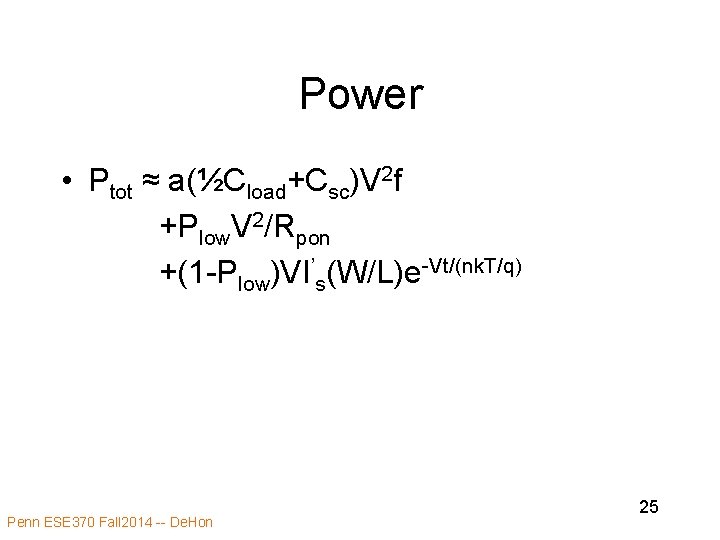

Power • Ptot ≈ a(½Cload+Csc)V 2 f +Plow. V 2/Rpon +(1 -Plow)VI’s(W/L)e-Vt/(nk. T/q) Penn ESE 370 Fall 2014 -- De. Hon 25

How size for R 0/2 drive? Penn ESE 370 Fall 2014 -- De. Hon 26

How size for R 0/2 drive? Penn ESE 370 Fall 2014 -- De. Hon 27

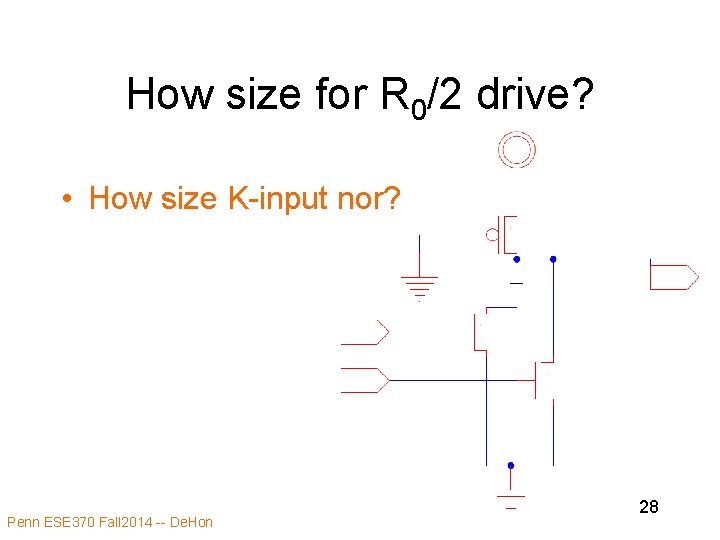

How size for R 0/2 drive? • How size K-input nor? Penn ESE 370 Fall 2014 -- De. Hon 28

When better than CMOS nor-k? • Better = smaller, lower input capacitance Penn ESE 370 Fall 2014 -- De. Hon 29

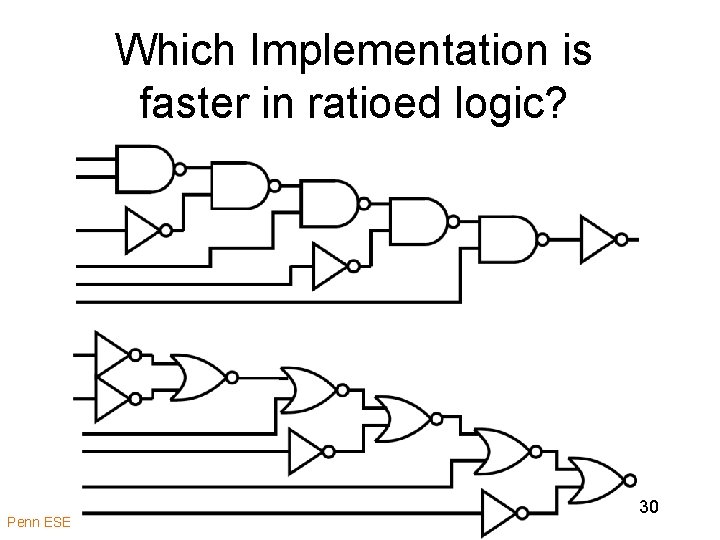

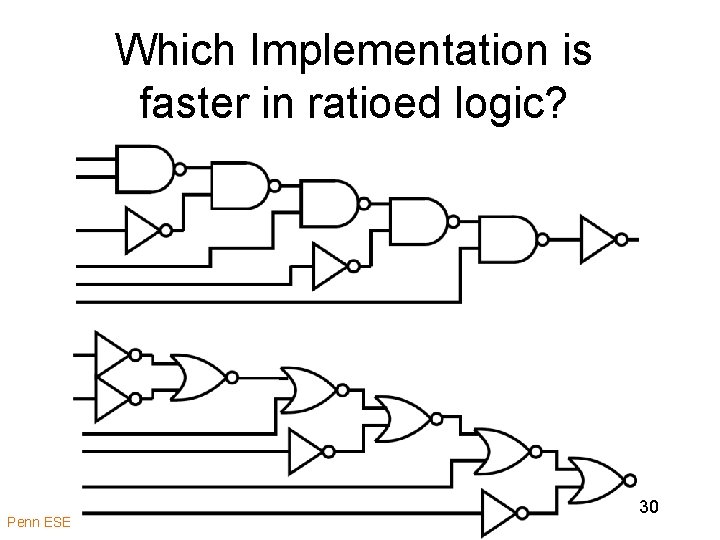

Which Implementation is faster in ratioed logic? Penn ESE 370 Fall 2014 -- De. Hon 30

Illustrates • Preferred gate changes Penn ESE 370 Fall 2014 -- De. Hon 31

Ideas • There are other logic disciplines • We have the tools to analyze • Ratioed Logic – Tradeoff noise margin for • Reduced area? Capacitive load? – Dissipates static power in one mode Penn ESE 370 Fall 2014 -- De. Hon 32

Admin • Project – Should have read it – Build and simulated baseline over weekend – Start list of optimizations to try • If don’t have list talk with Ron or André during office hours Penn ESE 370 Fall 2014 -- De. Hon 33