ESE 370 CircuitLevel Modeling Design and Optimization for

- Slides: 40

ESE 370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 31: November 23, 2011 Crosstalk Penn ESE 370 Fall 2011 -- De. Hon 1

Today • Crosstalk – How arise – Consequences – Magnitude – Avoiding Penn ESE 370 Fall 2011 -- De. Hon 2

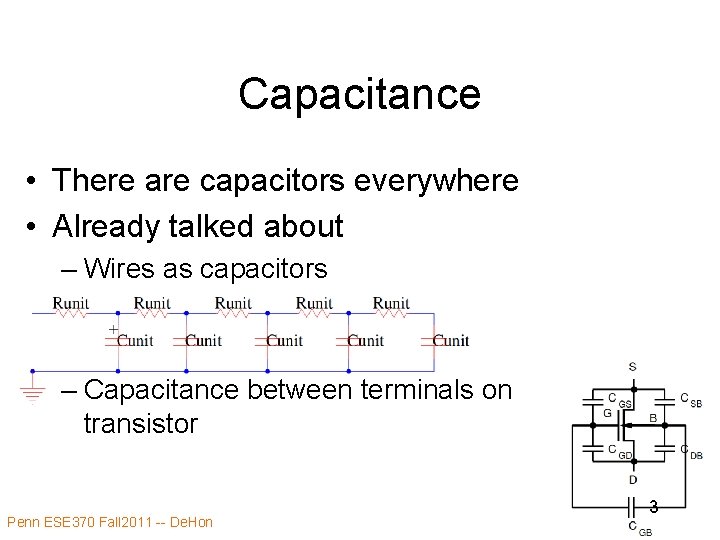

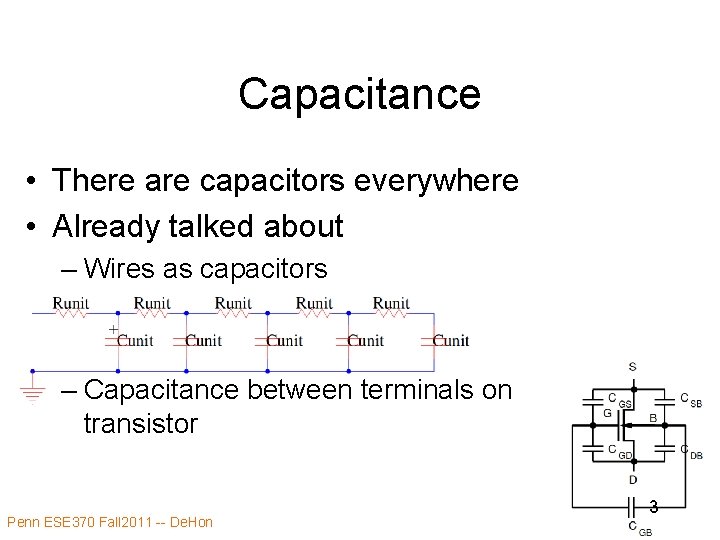

Capacitance • There are capacitors everywhere • Already talked about – Wires as capacitors – Capacitance between terminals on transistor Penn ESE 370 Fall 2011 -- De. Hon 3

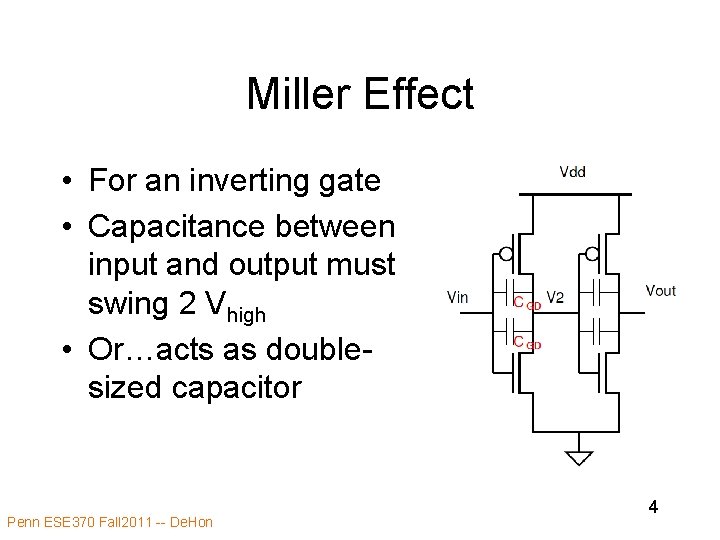

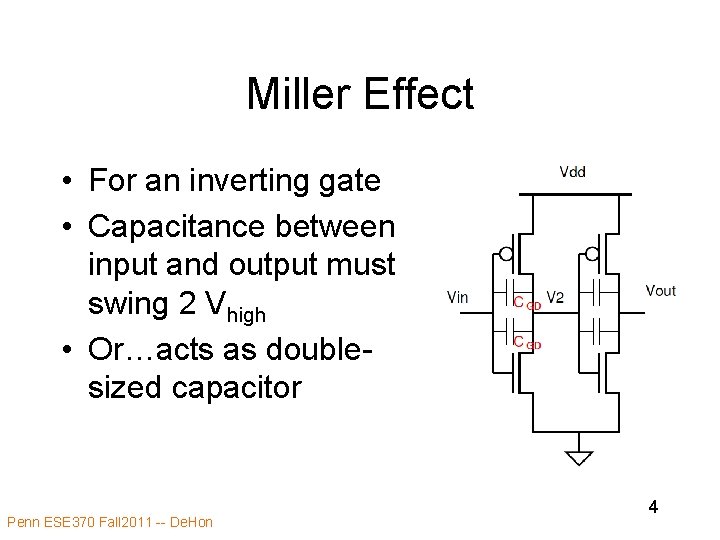

Miller Effect • For an inverting gate • Capacitance between input and output must swing 2 Vhigh • Or…acts as doublesized capacitor Penn ESE 370 Fall 2011 -- De. Hon 4

Capacitance Everywhere • Potentially a capacitor between any two conductors – On the chip – On the package – On the board • All wires – – Package pins PCB traces Cable wires Bit lines Penn ESE 370 Fall 2011 -- De. Hon 5

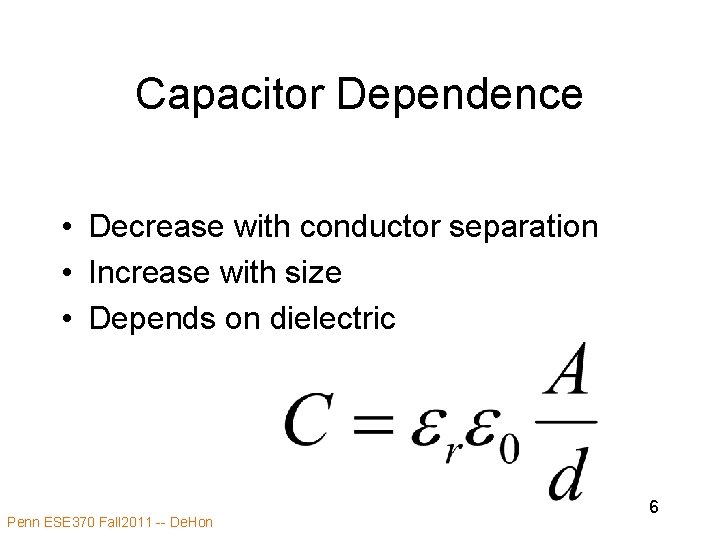

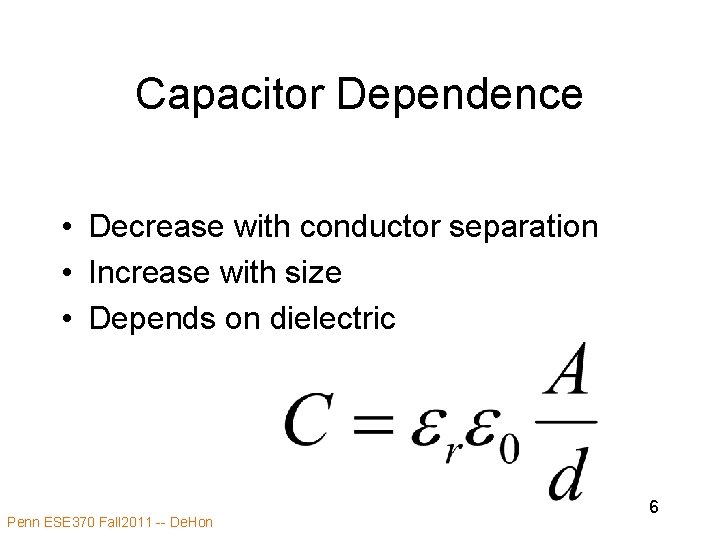

Capacitor Dependence • Decrease with conductor separation • Increase with size • Depends on dielectric Penn ESE 370 Fall 2011 -- De. Hon 6

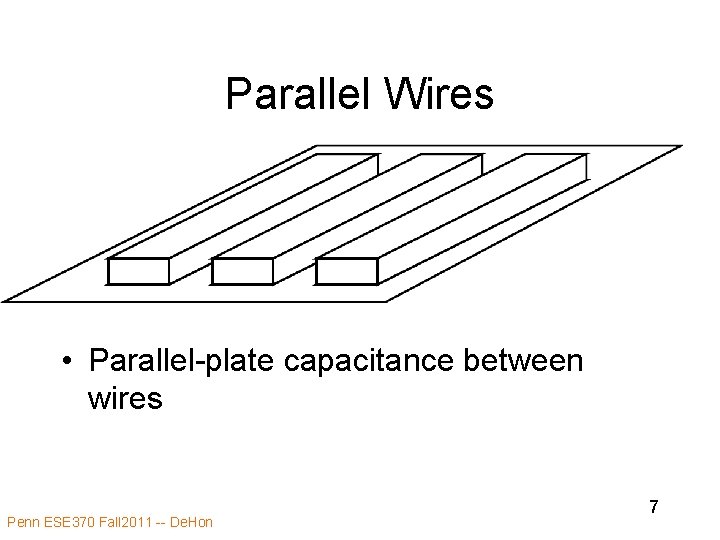

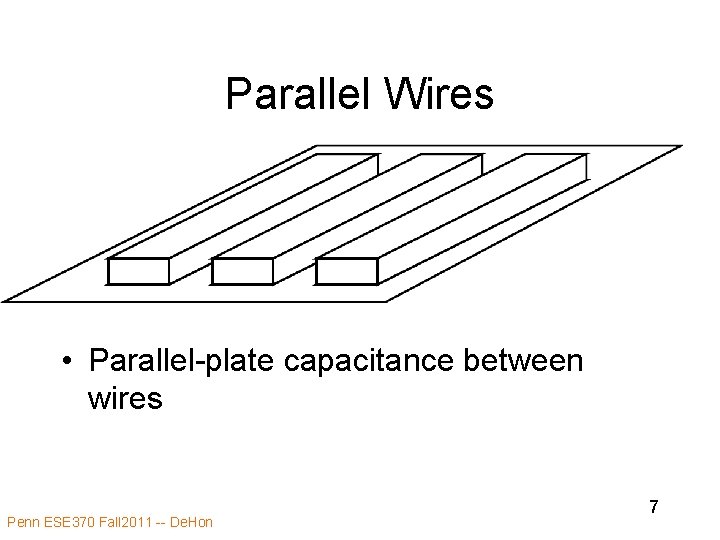

Parallel Wires • Parallel-plate capacitance between wires Penn ESE 370 Fall 2011 -- De. Hon 7

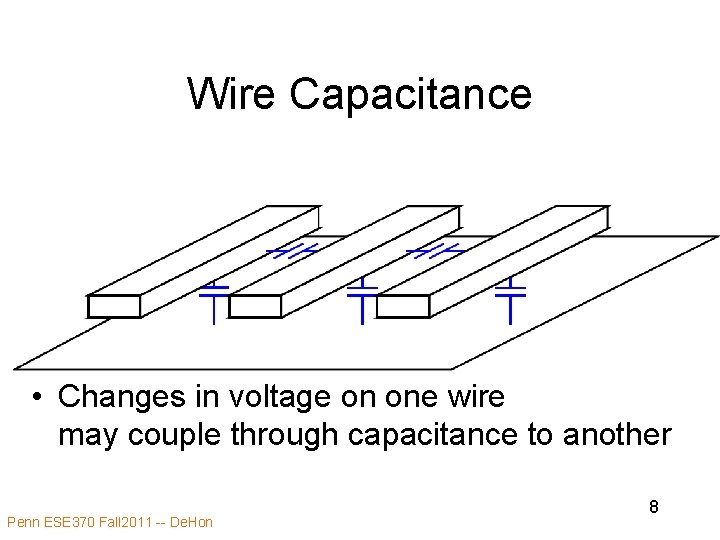

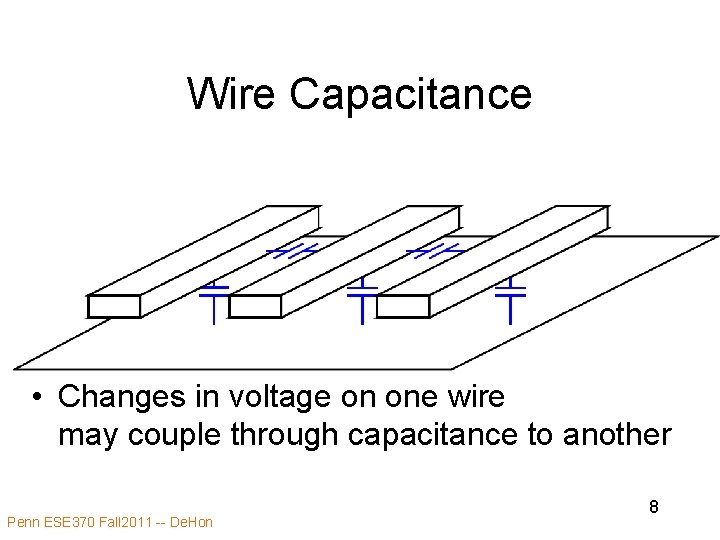

Wire Capacitance • Changes in voltage on one wire may couple through capacitance to another Penn ESE 370 Fall 2011 -- De. Hon 8

Consequences Qualitative First Penn ESE 370 Fall 2011 -- De. Hon 9

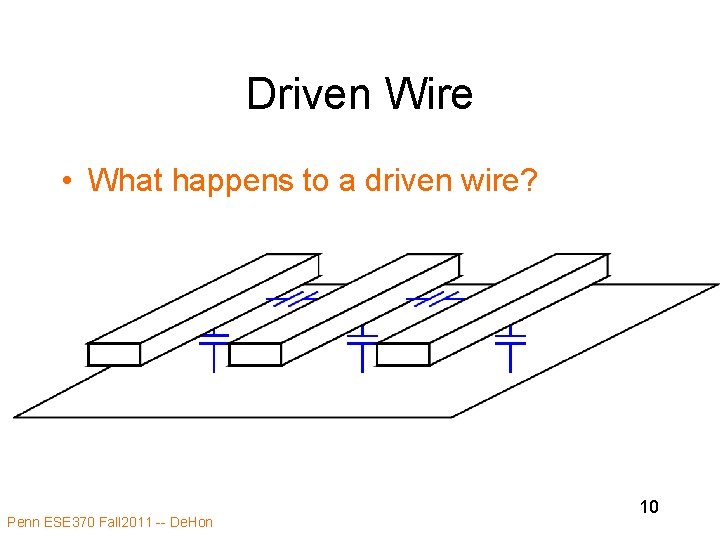

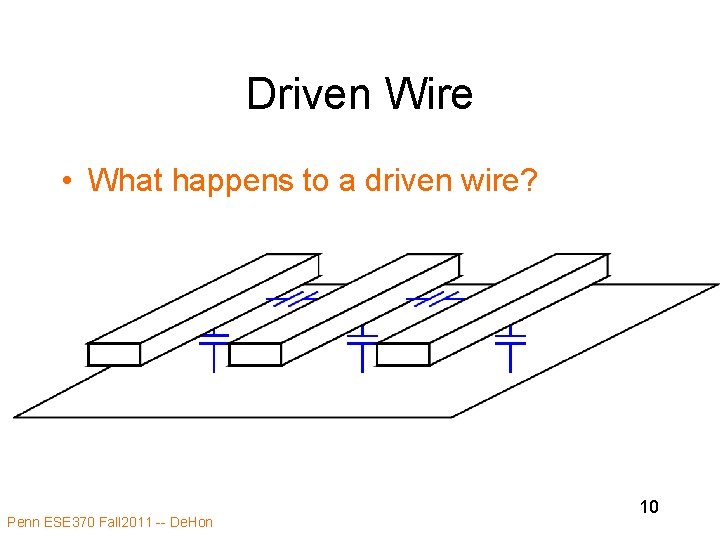

Driven Wire • What happens to a driven wire? Penn ESE 370 Fall 2011 -- De. Hon 10

Driven Wire • Can this be a problem? • Victim – Clock line – Asynchronous control – Non-clock used in synchronous system • Outputs sampled at clock edge Penn ESE 370 Fall 2011 -- De. Hon 11

Undriven Wire • What happens to undriven wire? • Where do we have undriven wires? Penn ESE 370 Fall 2011 -- De. Hon 12

Clocked Logic • CMOS driven lines • Clocked logic • Willing to wait to settle • Impact is solely on delay – May increase delay of transitions Penn ESE 370 Fall 2011 -- De. Hon 13

Magnitude Quantitative Penn ESE 370 Fall 2011 -- De. Hon 14

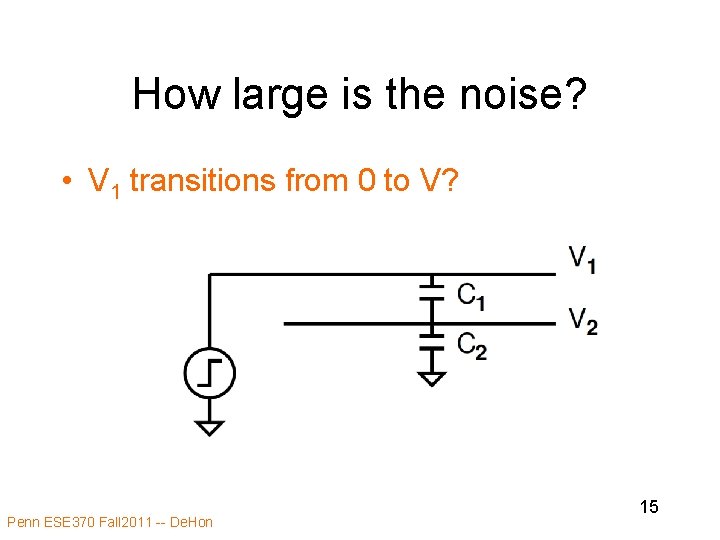

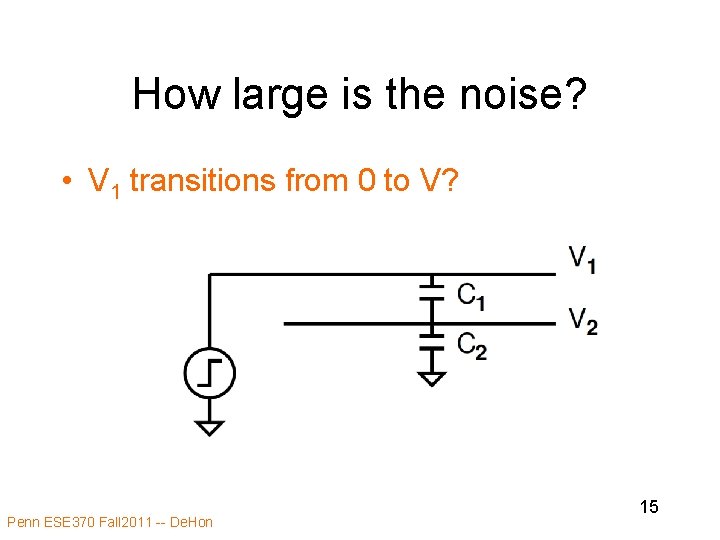

How large is the noise? • V 1 transitions from 0 to V? Penn ESE 370 Fall 2011 -- De. Hon 15

How large is the noise? • V 1 transitions from 0 to V Penn ESE 370 Fall 2011 -- De. Hon 16

Noise Magnitude Penn ESE 370 Fall 2011 -- De. Hon 17

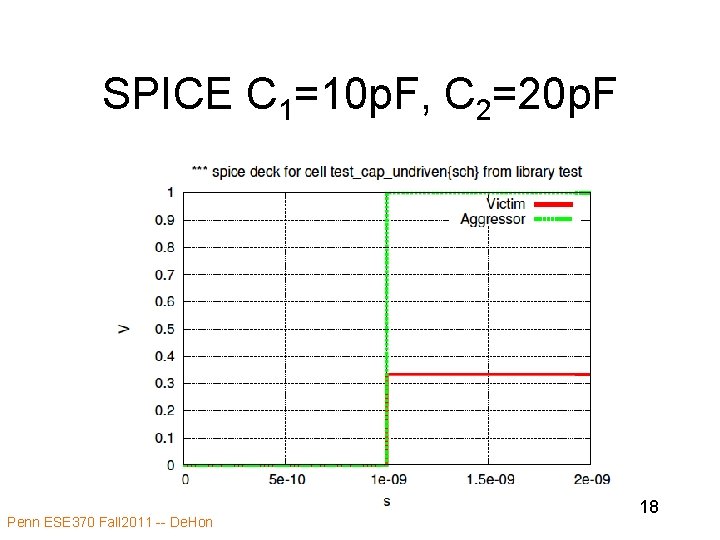

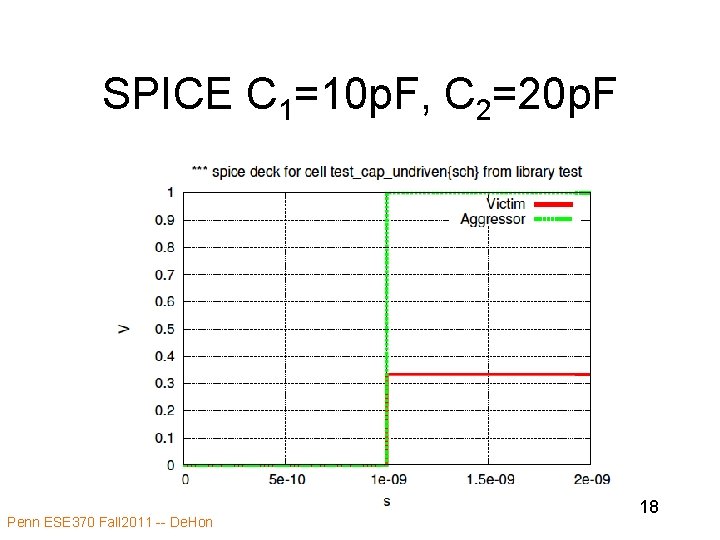

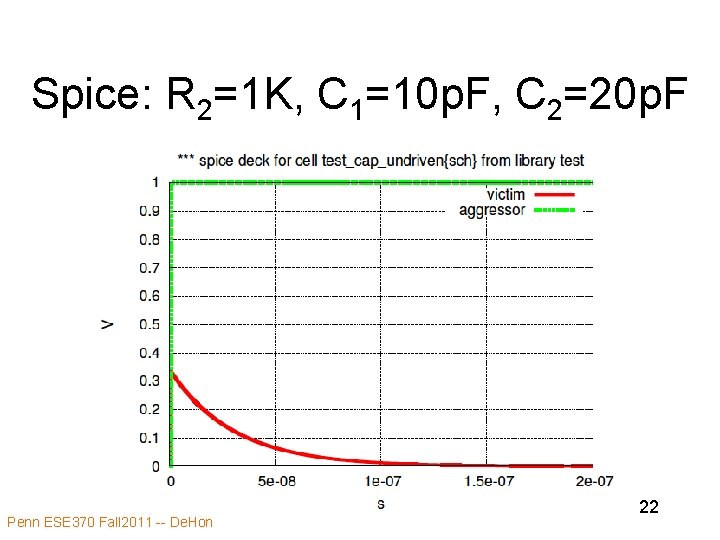

SPICE C 1=10 p. F, C 2=20 p. F Penn ESE 370 Fall 2011 -- De. Hon 18

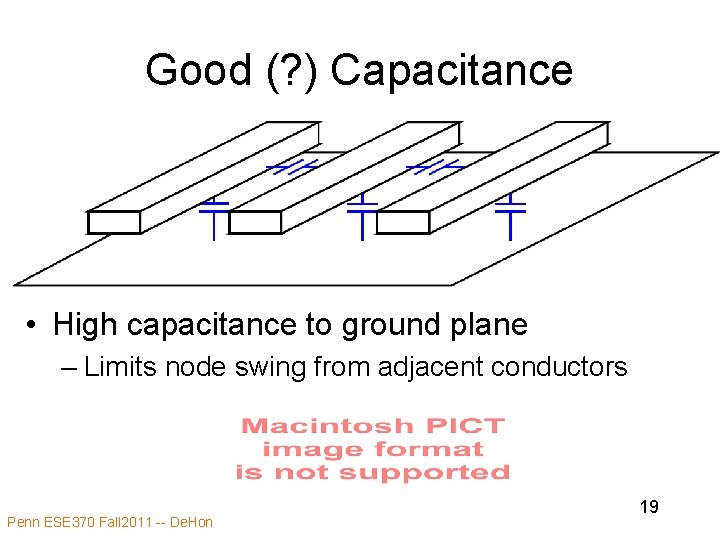

Good (? ) Capacitance • High capacitance to ground plane – Limits node swing from adjacent conductors Penn ESE 370 Fall 2011 -- De. Hon 19

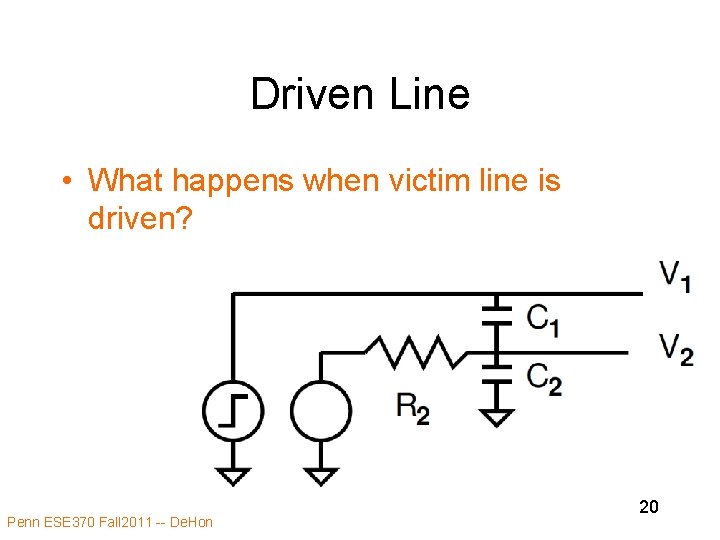

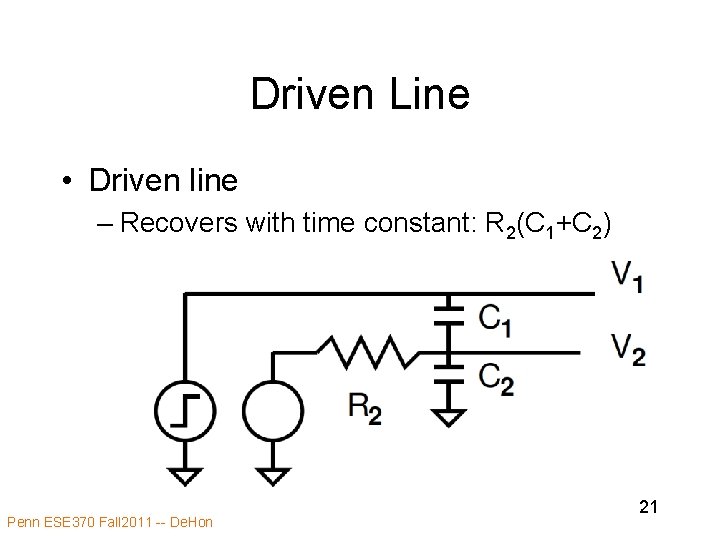

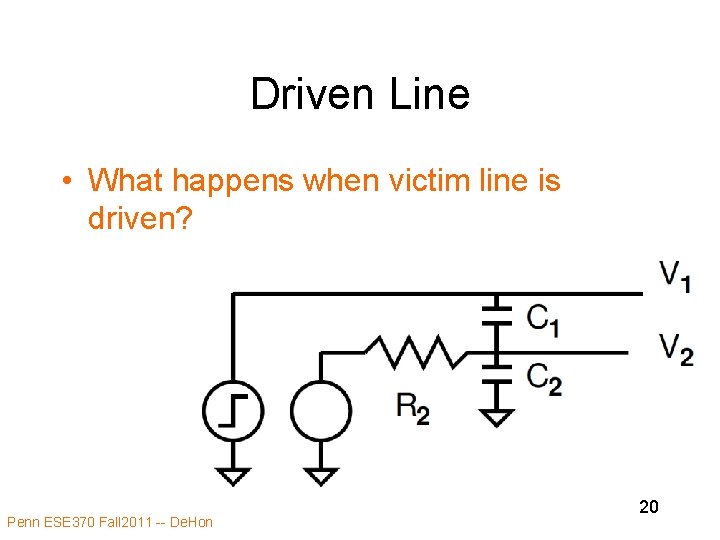

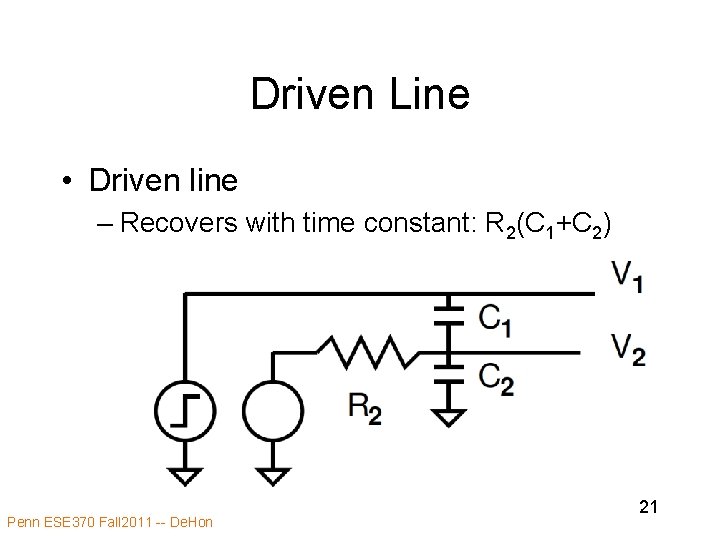

Driven Line • What happens when victim line is driven? Penn ESE 370 Fall 2011 -- De. Hon 20

Driven Line • Driven line – Recovers with time constant: R 2(C 1+C 2) Penn ESE 370 Fall 2011 -- De. Hon 21

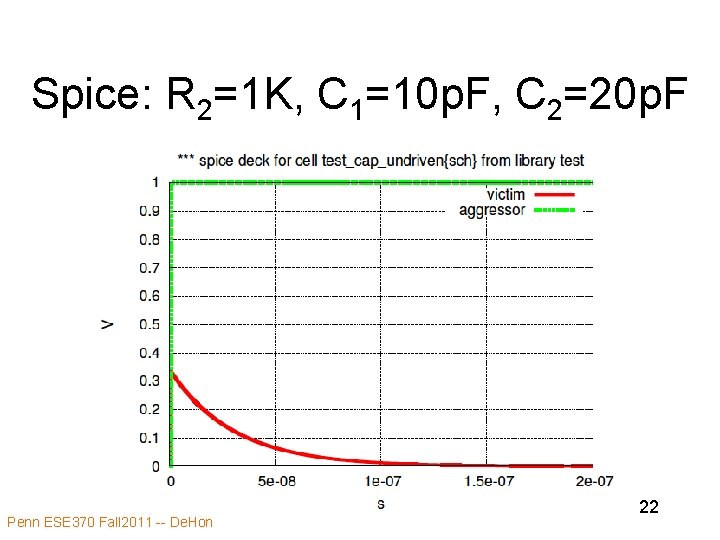

Spice: R 2=1 K, C 1=10 p. F, C 2=20 p. F Penn ESE 370 Fall 2011 -- De. Hon 22

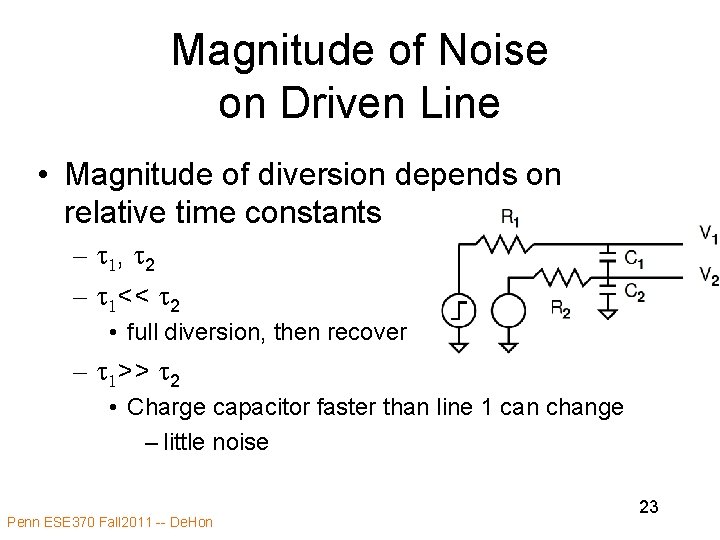

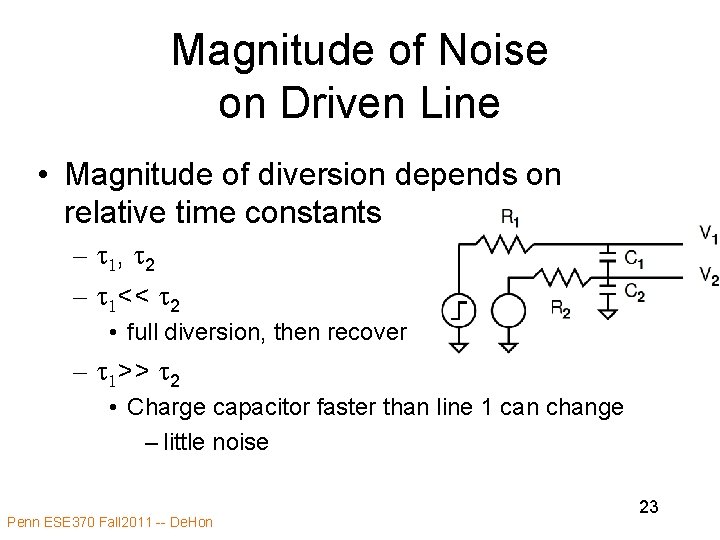

Magnitude of Noise on Driven Line • Magnitude of diversion depends on relative time constants – t 1, t 2 – t 1<< t 2 • full diversion, then recover – t 1>> t 2 • Charge capacitor faster than line 1 can change – little noise Penn ESE 370 Fall 2011 -- De. Hon 23

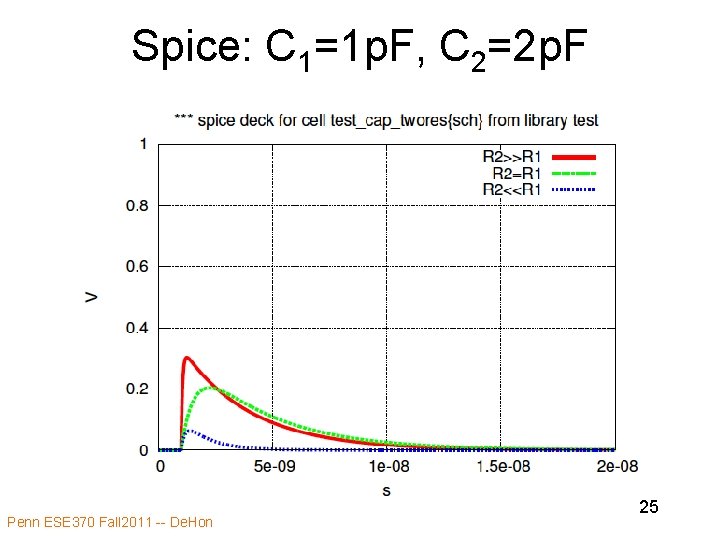

Magnitude of Noise on Driven Line • Magnitude of diversion depends on relative time constants – t 1, t 2 – t 1<< t 2 – t 1>> t 2 Penn ESE 370 Fall 2011 -- De. Hon 24

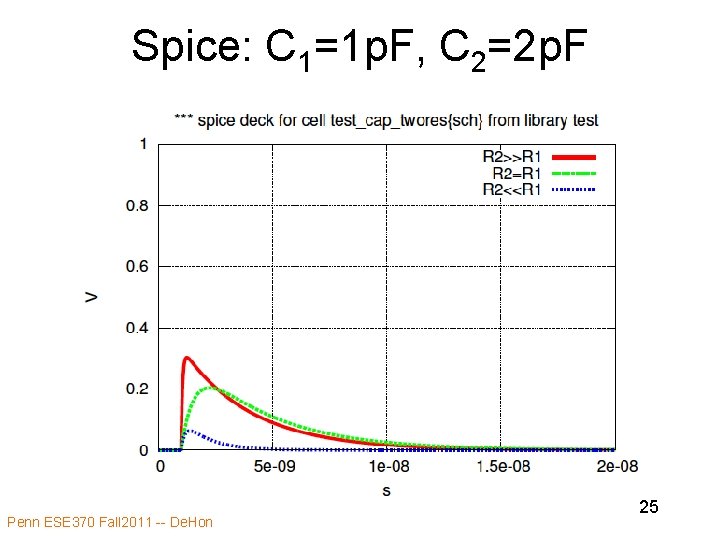

Spice: C 1=1 p. F, C 2=2 p. F Penn ESE 370 Fall 2011 -- De. Hon 25

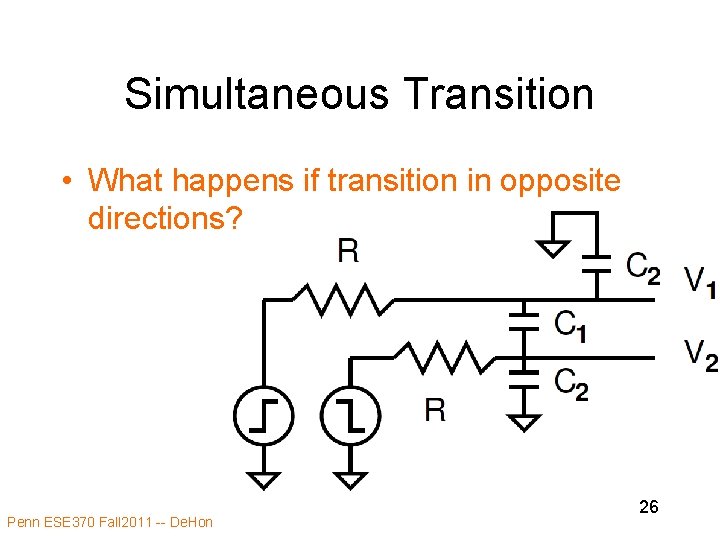

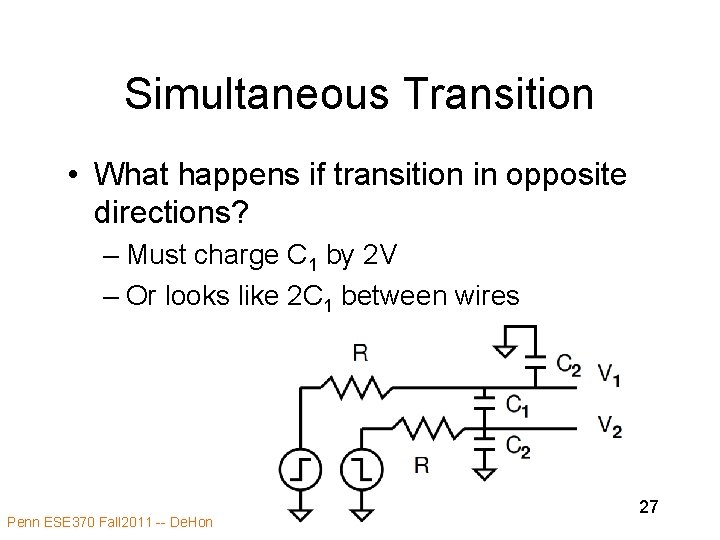

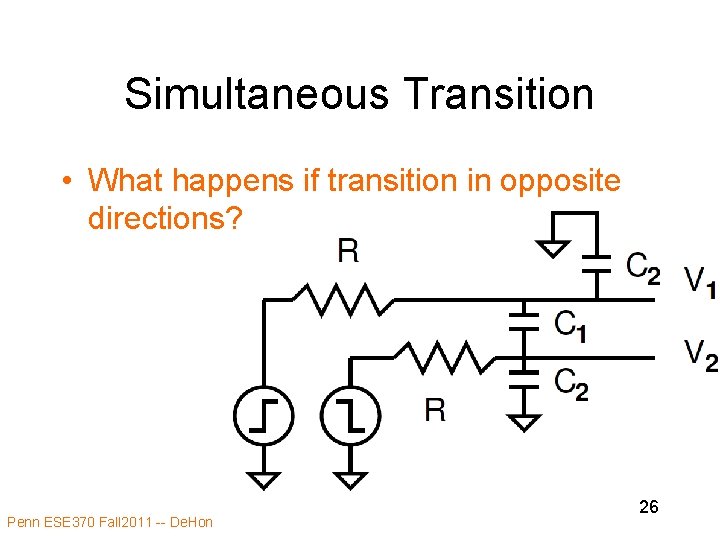

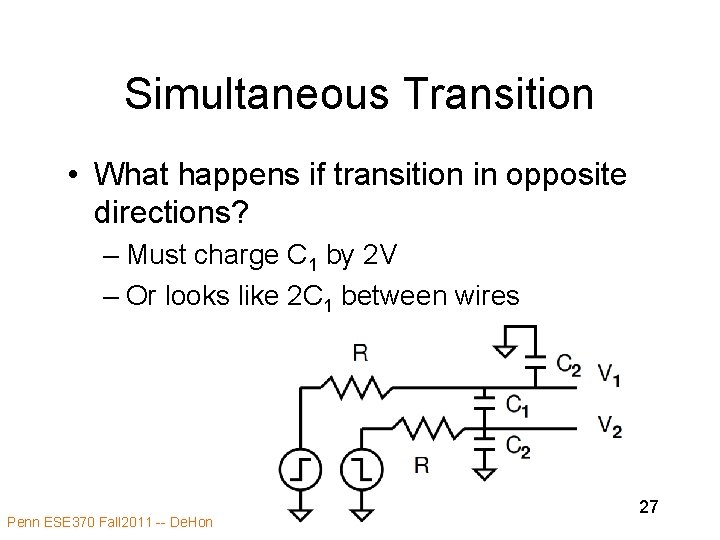

Simultaneous Transition • What happens if transition in opposite directions? Penn ESE 370 Fall 2011 -- De. Hon 26

Simultaneous Transition • What happens if transition in opposite directions? – Must charge C 1 by 2 V – Or looks like 2 C 1 between wires Penn ESE 370 Fall 2011 -- De. Hon 27

Where Arise Penn ESE 370 Fall 2011 -- De. Hon 28

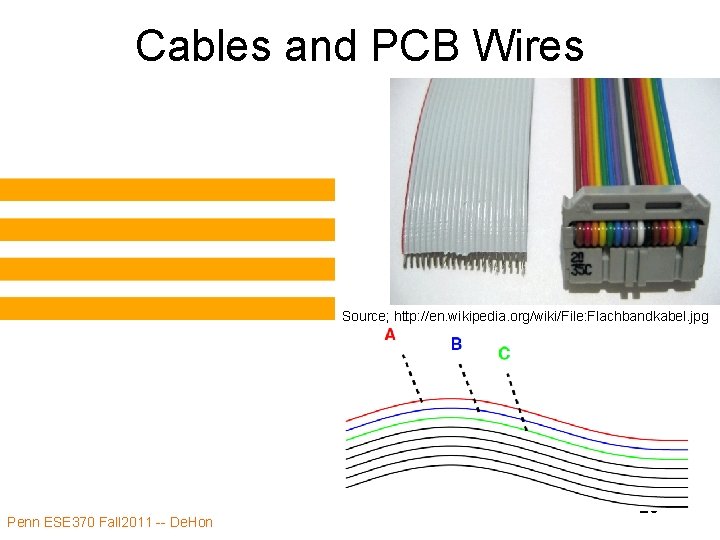

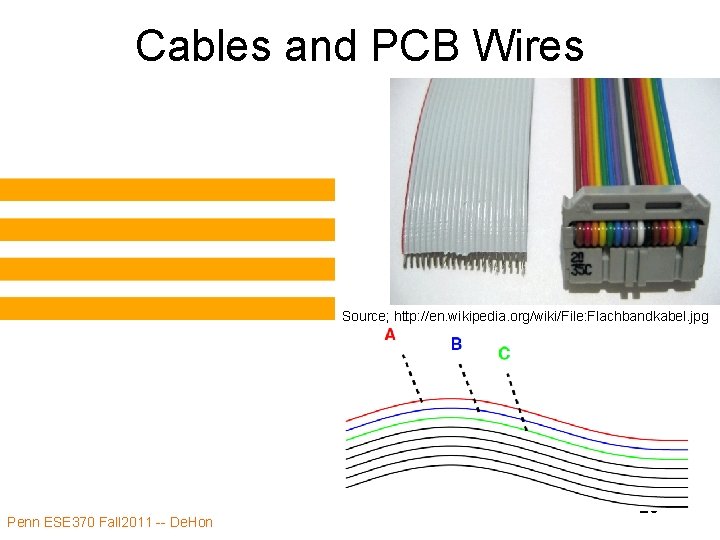

Cables and PCB Wires Source; http: //en. wikipedia. org/wiki/File: Flachbandkabel. jpg Penn ESE 370 Fall 2011 -- De. Hon 29

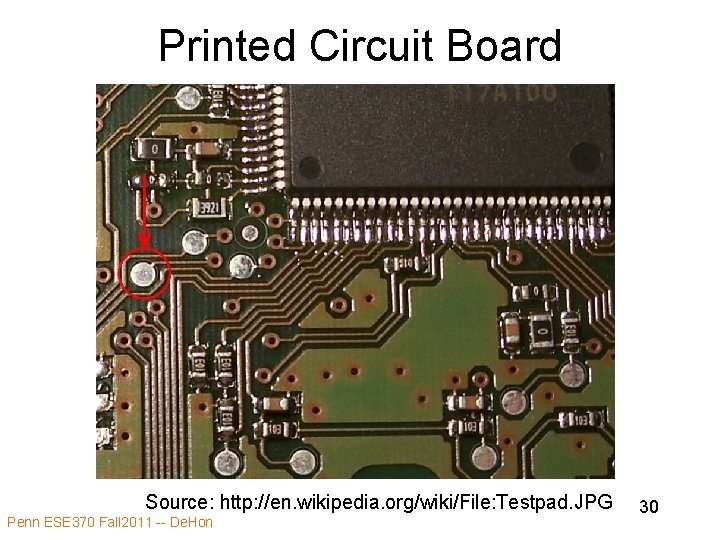

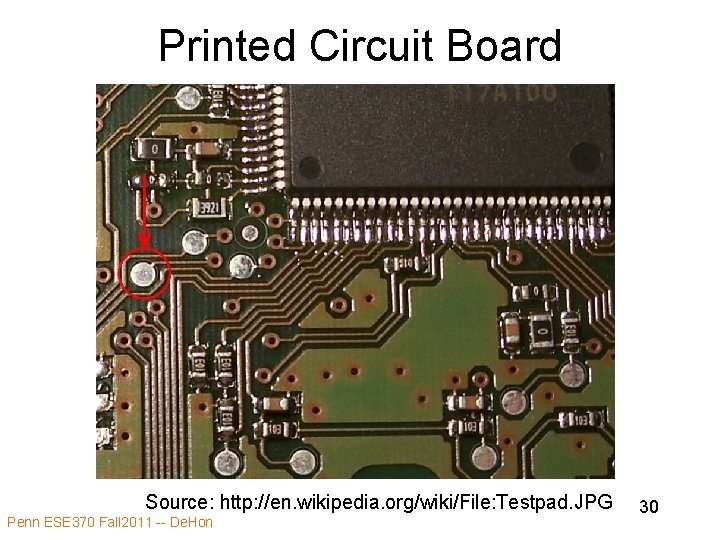

Printed Circuit Board Source: http: //en. wikipedia. org/wiki/File: Testpad. JPG Penn ESE 370 Fall 2011 -- De. Hon 30

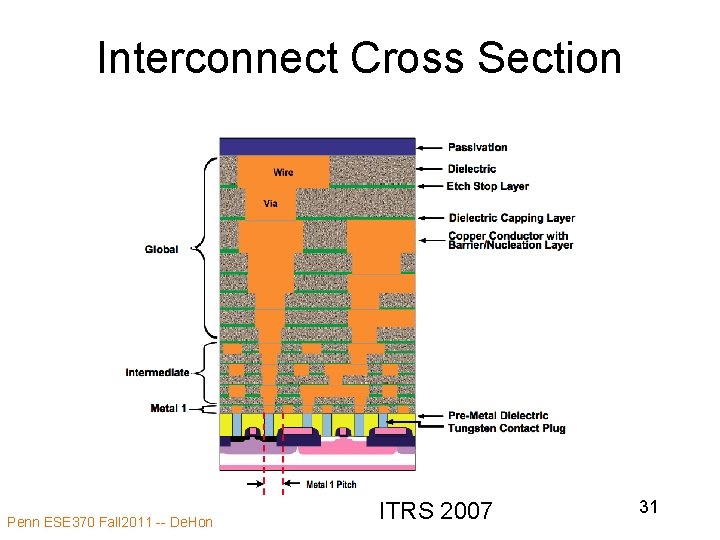

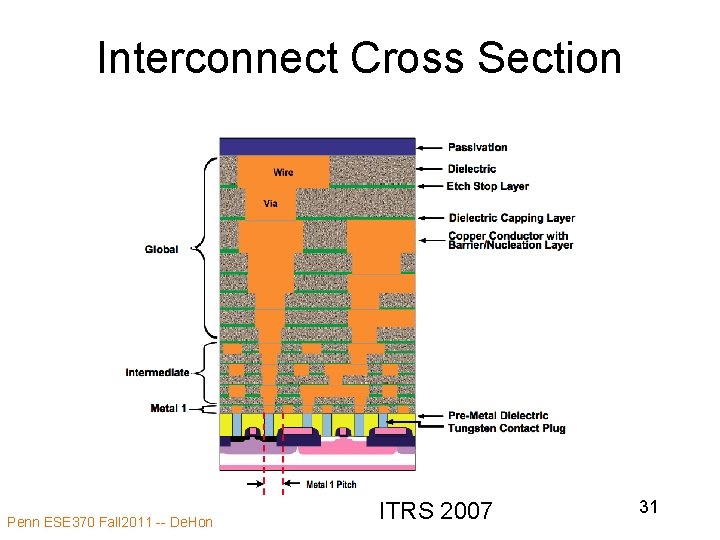

Interconnect Cross Section Penn ESE 370 Fall 2011 -- De. Hon ITRS 2007 31

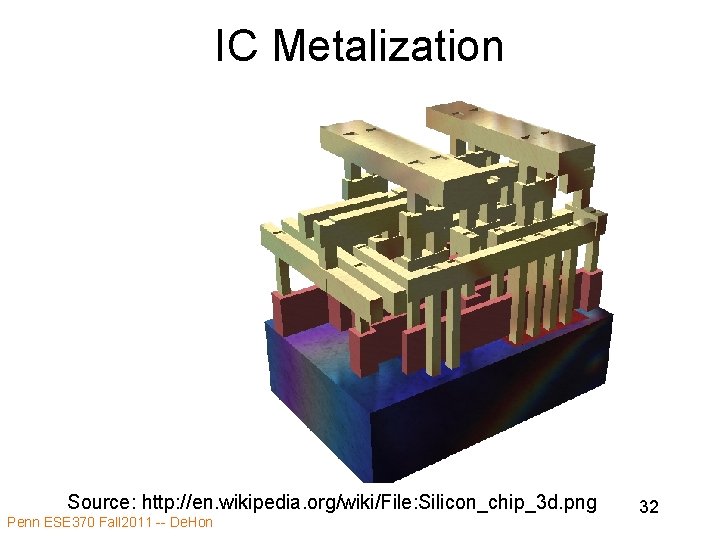

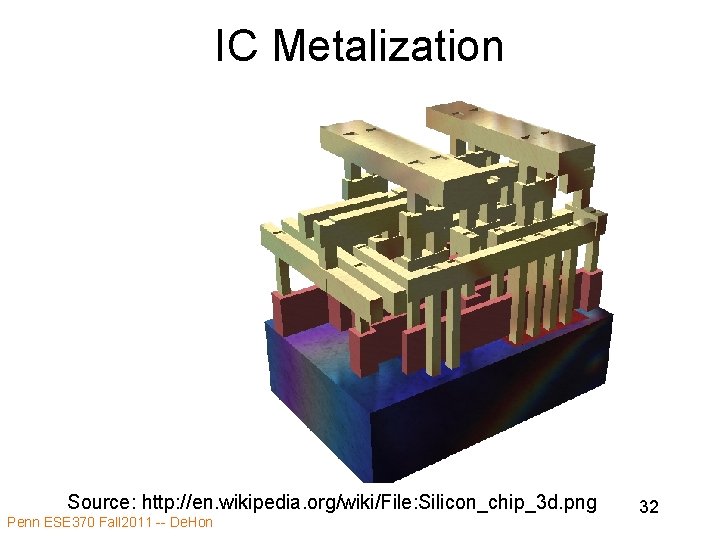

IC Metalization Source: http: //en. wikipedia. org/wiki/File: Silicon_chip_3 d. png Penn ESE 370 Fall 2011 -- De. Hon 32

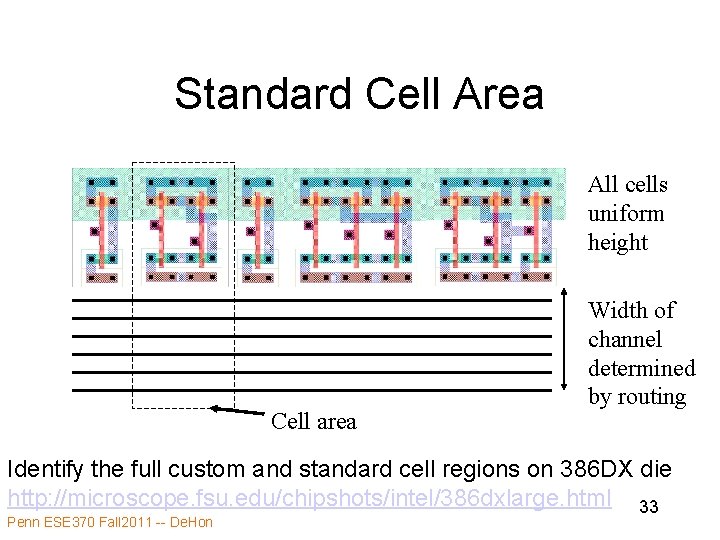

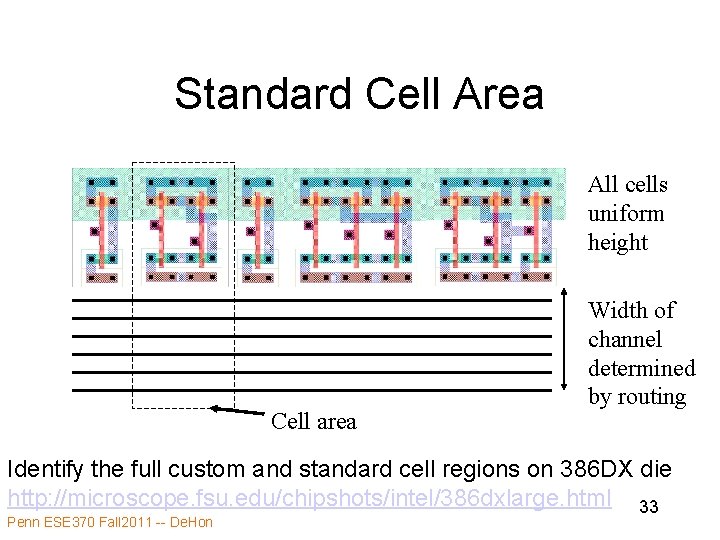

Standard Cell Area All cells uniform height inv nand 3 Cell area Width of channel determined by routing Identify the full custom and standard cell regions on 386 DX die http: //microscope. fsu. edu/chipshots/intel/386 dxlarge. html 33 Penn ESE 370 Fall 2011 -- De. Hon

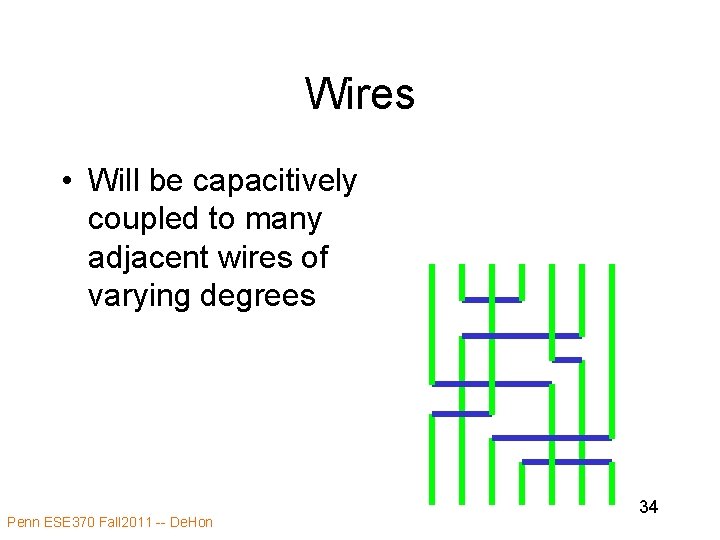

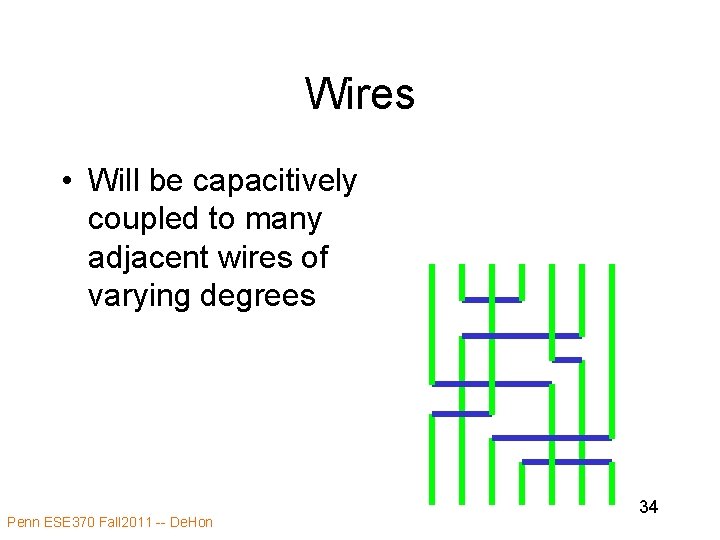

Wires • Will be capacitively coupled to many adjacent wires of varying degrees Penn ESE 370 Fall 2011 -- De. Hon 34

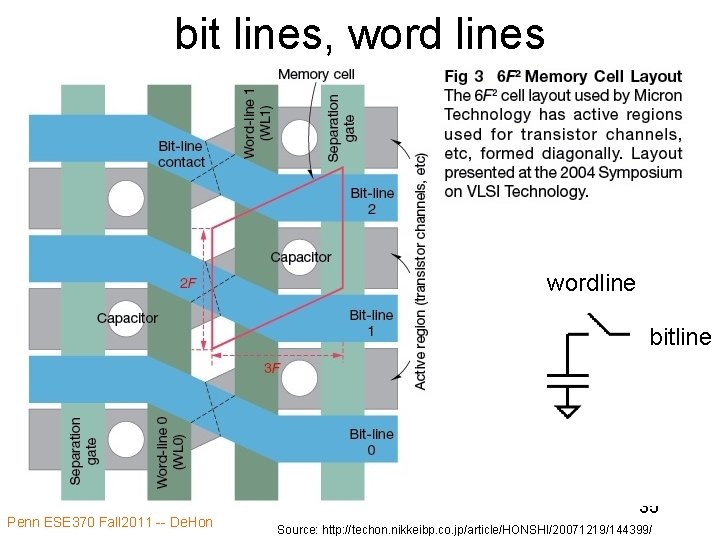

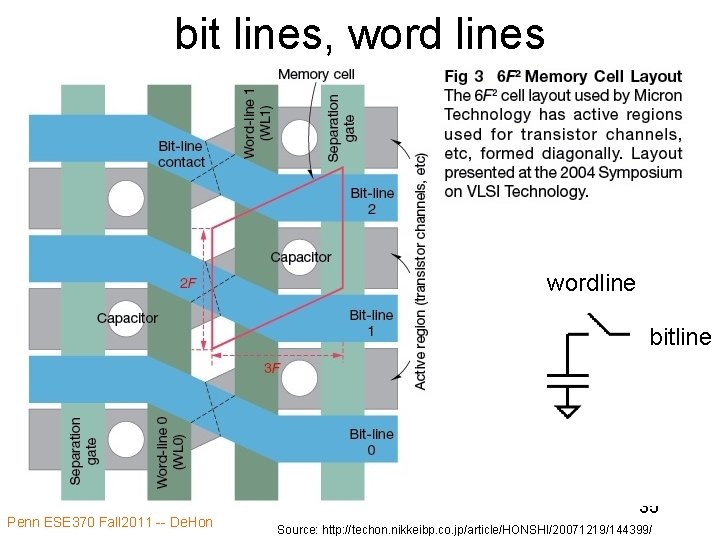

bit lines, word lines wordline bitline Penn ESE 370 Fall 2011 -- De. Hon 35 Source: http: //techon. nikkeibp. co. jp/article/HONSHI/20071219/144399/

Addressing Penn ESE 370 Fall 2011 -- De. Hon 36

What can we do? • How can we reduce? Penn ESE 370 Fall 2011 -- De. Hon 37

What can we do? • Orthogonal routing layers – Avoid parallel coupling vertically • Widen spacing between wires – Particularly critical path wires • Limit length two wires run in parallel • Separate with power planes • Separate with ground/power wires Penn ESE 370 Fall 2011 -- De. Hon 38

Admin • HW 6 Out by time return from break • Next week – Project 3 out – Lecture Monday and Wednesday – Lab on Friday Penn ESE 370 Fall 2011 -- De. Hon 39

Idea • • Capacitance is everywhere Especially between adjacent wires Will get “noise” from crosstalk Clocked and driven wires – Slow down transitions • Undriven wires voltage changed • Can cause spurious transitions Penn ESE 370 Fall 2011 -- De. Hon 40