ESE 370 CircuitLevel Modeling Design and Optimization for

- Slides: 59

ESE 370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 2: September 10, 2010 Transistor Introduction Penn ESE 370 Fall 2010 -- De. Hon 1

Today • MOSFET • Capacitive and resistive loads • Simplified models – Zero-th order model • Good enough for ? ? ? – First order model • There always Rs and Cs Penn ESE 370 Fall 2010 -- De. Hon 2

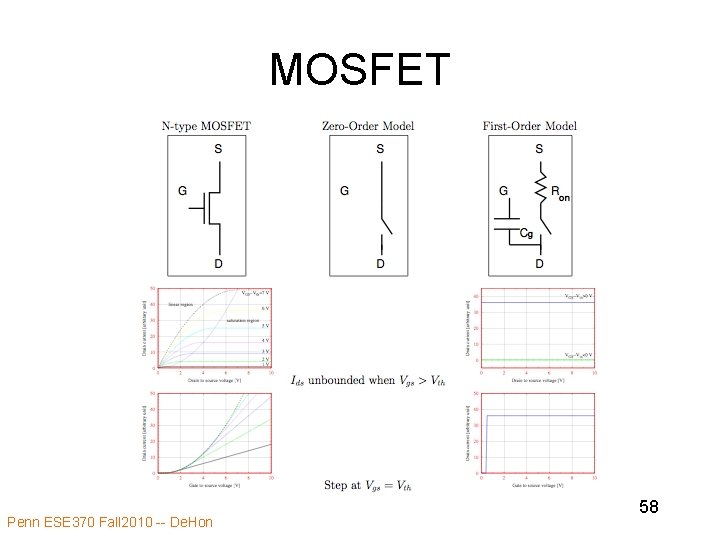

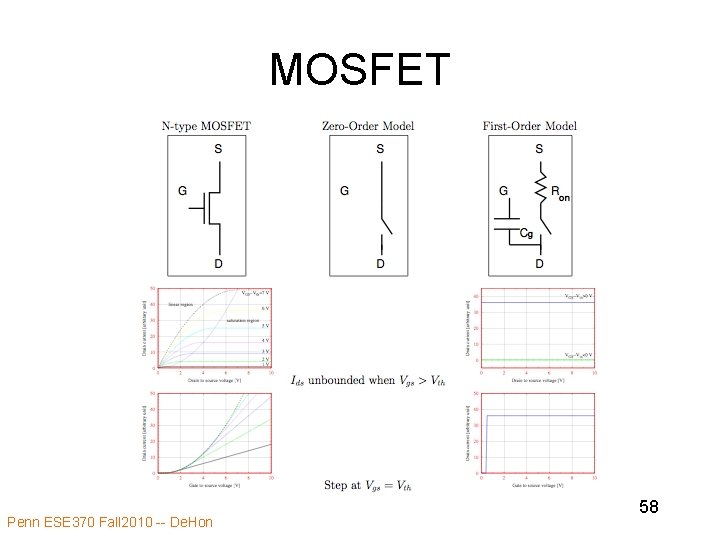

MOSFET • Metal Oxide Semiconductor Field Effect Transistor – New device – Primary active component for the term – Three terminal device • Voltage at gate controls conduction between two other terminals (source, drain) Penn ESE 370 Fall 2010 -- De. Hon 3

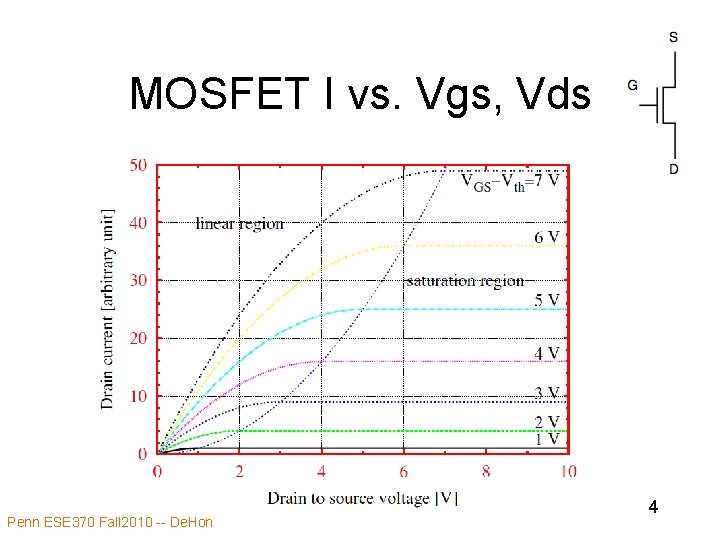

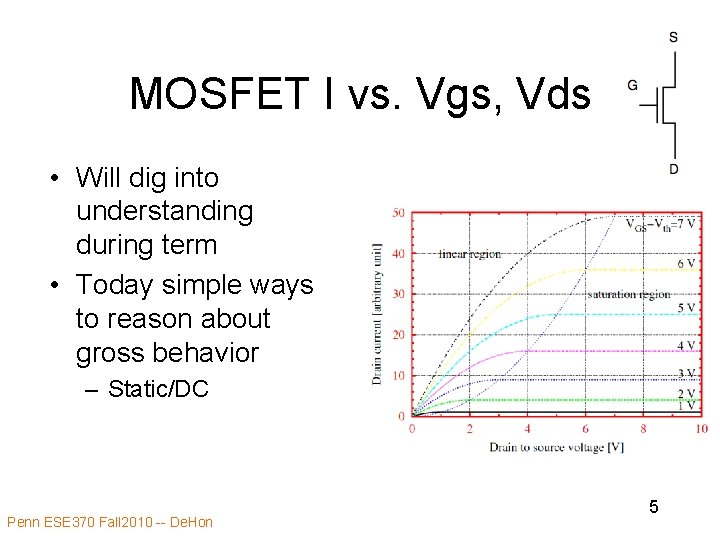

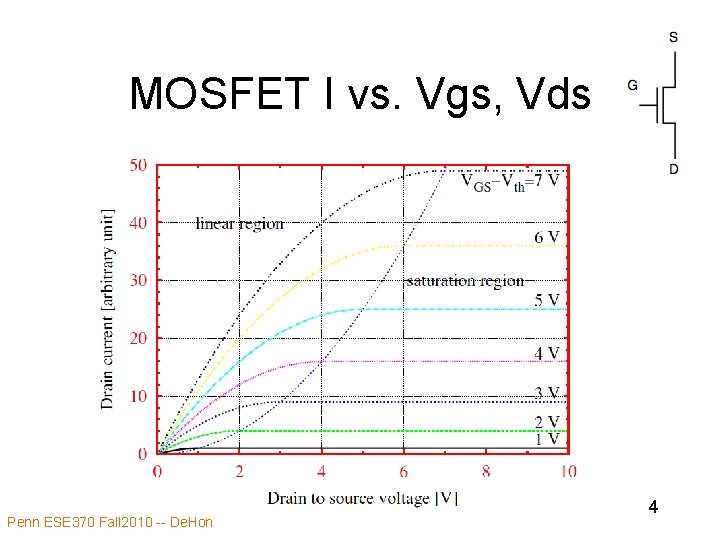

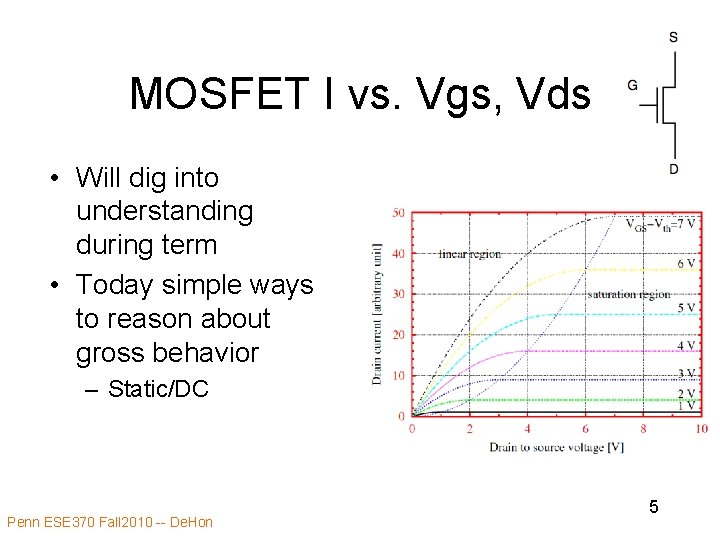

MOSFET I vs. Vgs, Vds Penn ESE 370 Fall 2010 -- De. Hon 4

MOSFET I vs. Vgs, Vds • Will dig into understanding during term • Today simple ways to reason about gross behavior – Static/DC Penn ESE 370 Fall 2010 -- De. Hon 5

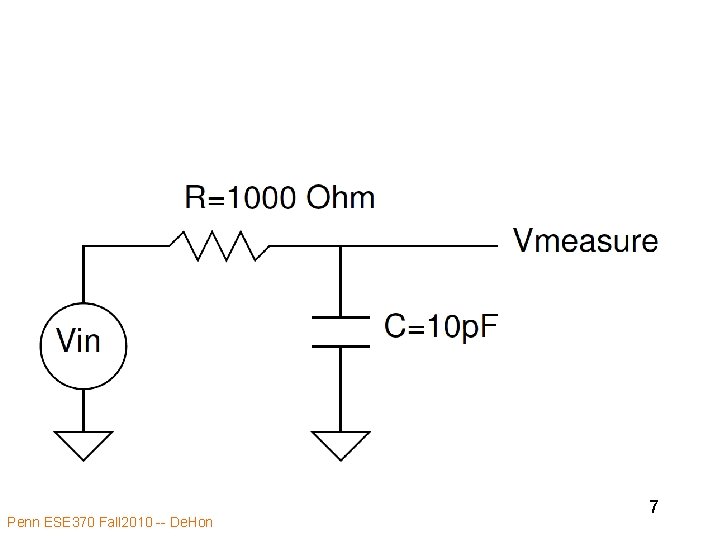

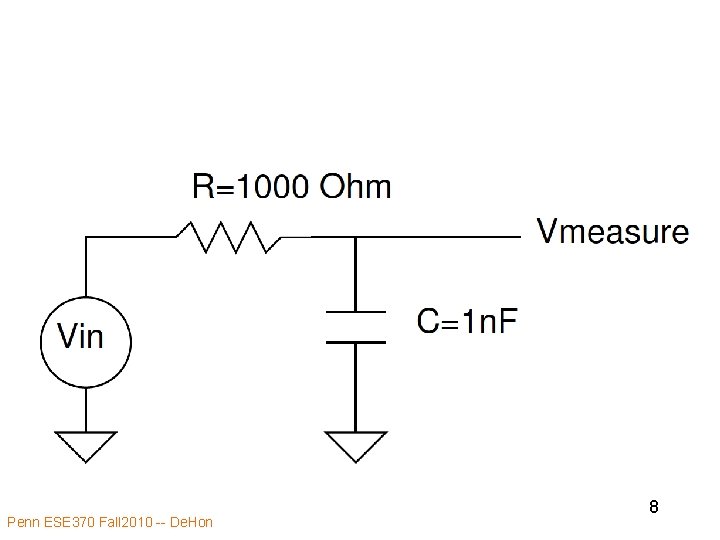

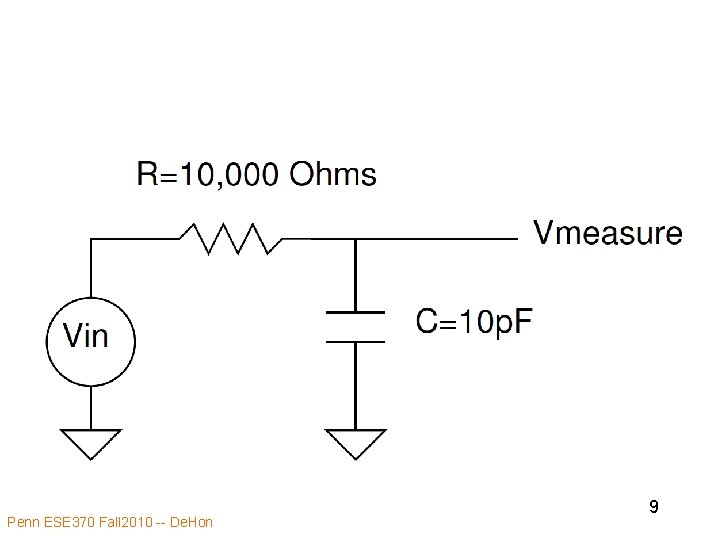

Preclass • What voltage do the cases converge to? Penn ESE 370 Fall 2010 -- De. Hon 6

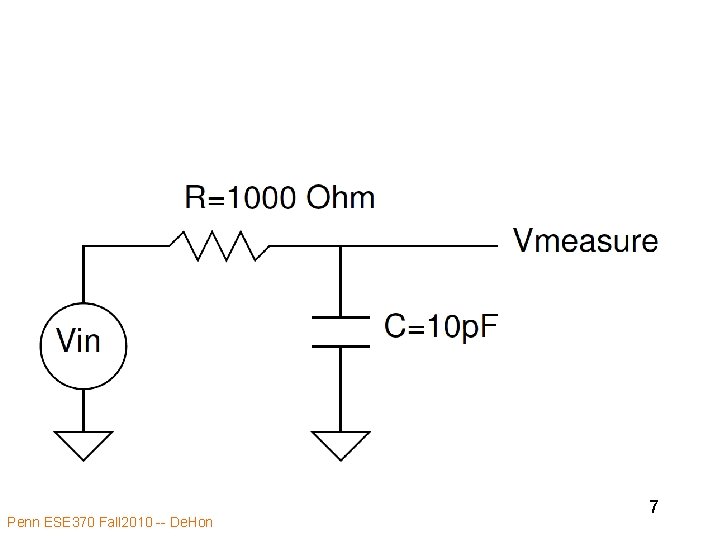

Penn ESE 370 Fall 2010 -- De. Hon 7

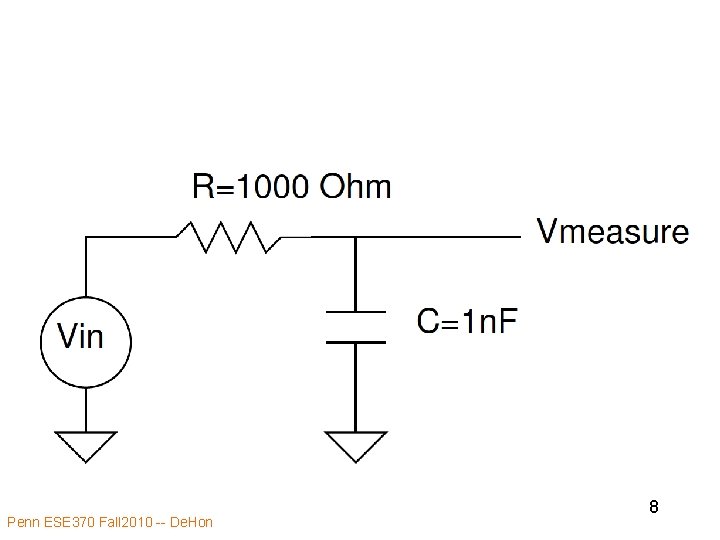

Penn ESE 370 Fall 2010 -- De. Hon 8

Penn ESE 370 Fall 2010 -- De. Hon 9

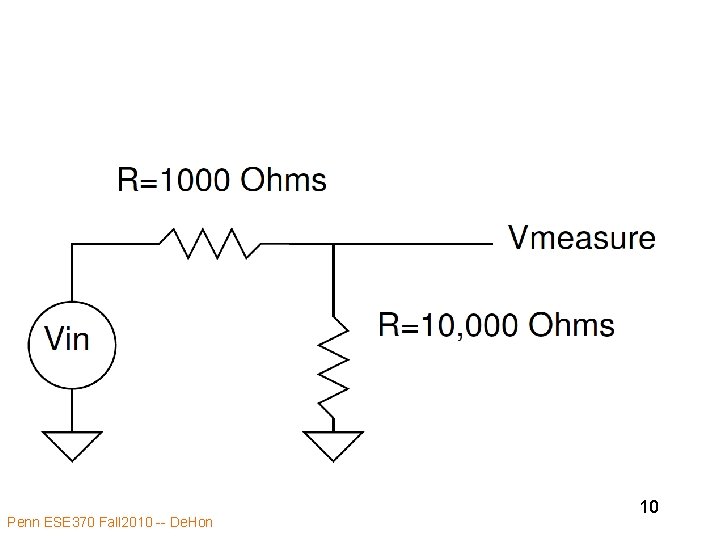

Penn ESE 370 Fall 2010 -- De. Hon 10

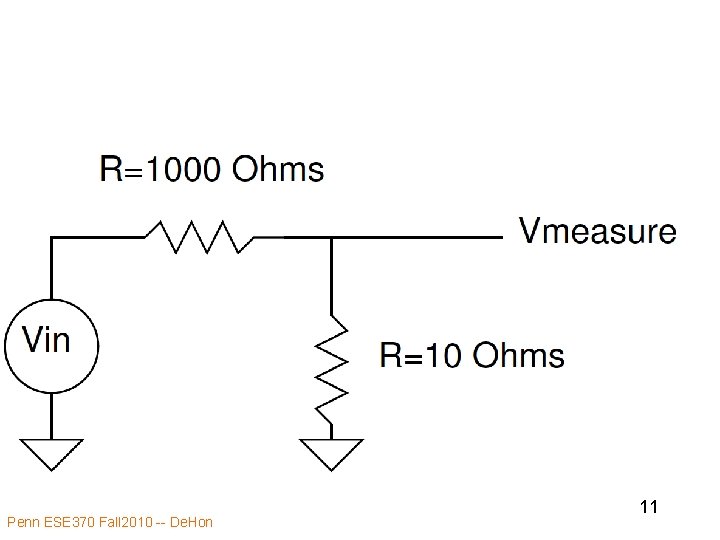

Penn ESE 370 Fall 2010 -- De. Hon 11

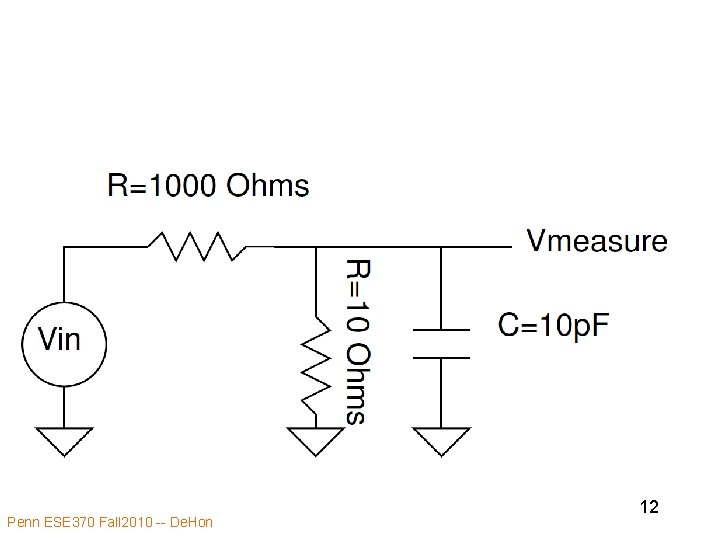

Penn ESE 370 Fall 2010 -- De. Hon 12

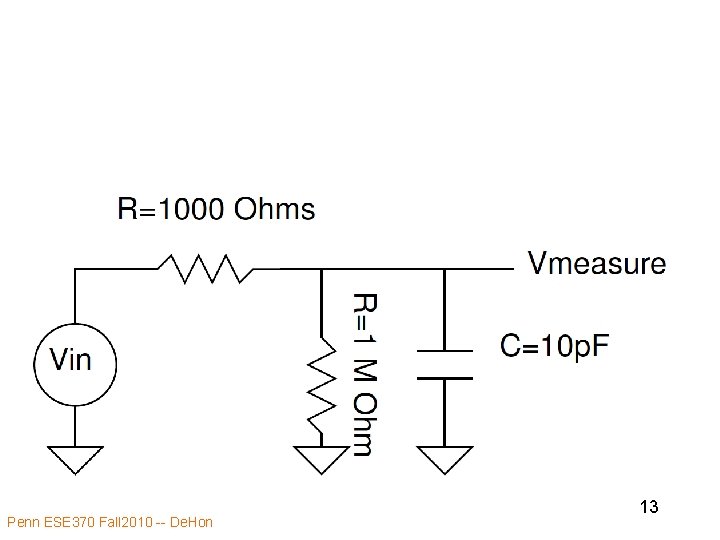

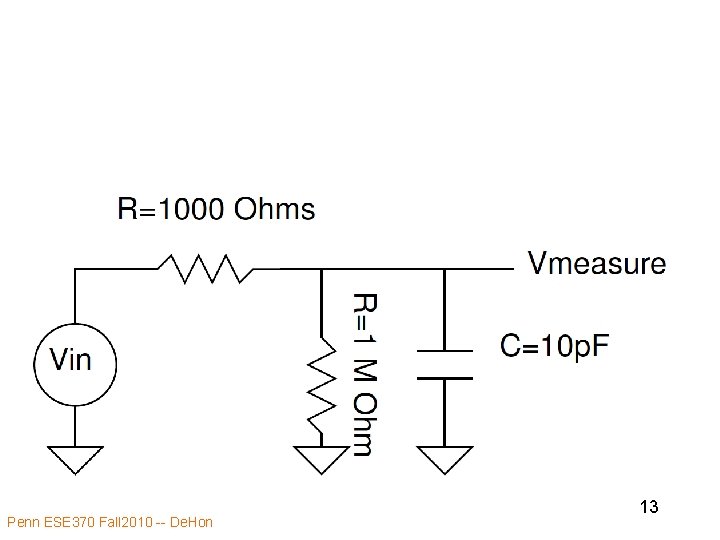

Penn ESE 370 Fall 2010 -- De. Hon 13

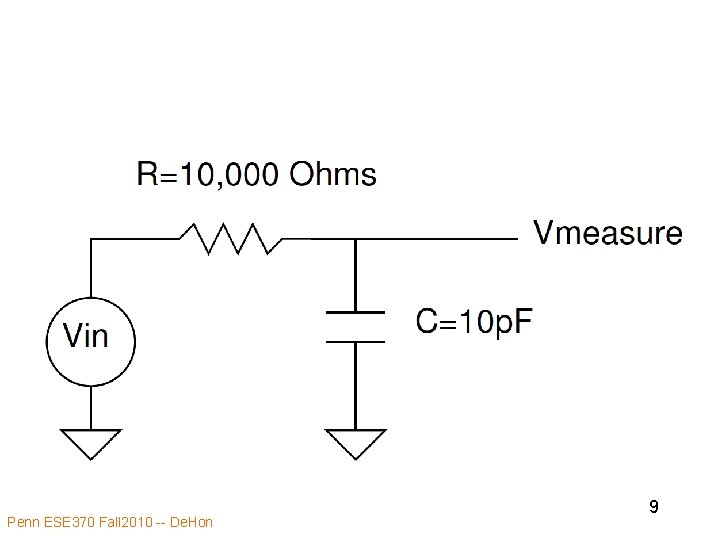

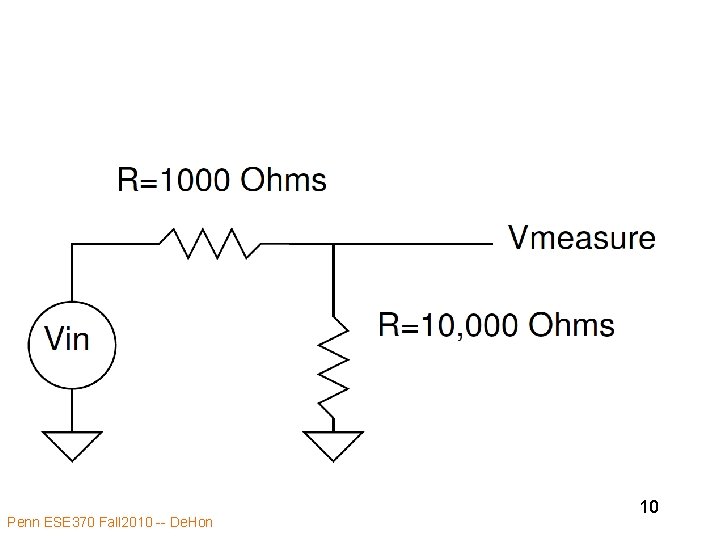

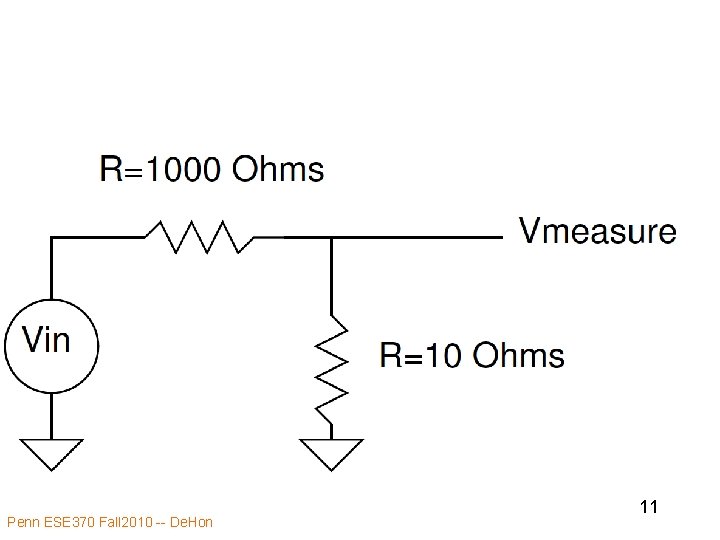

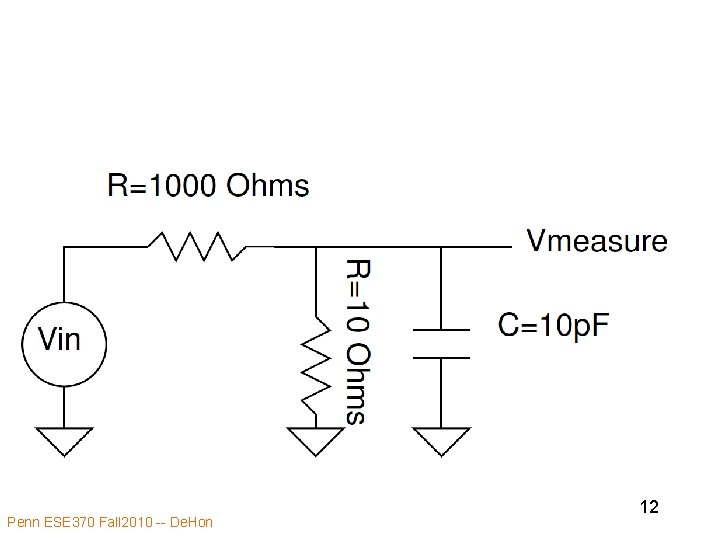

Conclude? • DC/Steady-State – Ignore the capacitors Penn ESE 370 Fall 2010 -- De. Hon 14

Quasistatic • Static – inputs (and circuit) unchanging, how does it settle? • Dynamic – what happens when things change • Quasi-Static – inputs transition, circuit responds, and settles – Dynamic transition to roughly static states Penn ESE 370 Fall 2010 -- De. Hon 15

Quasistatic Relevance? • How relevant to a combinational digital circuit? • How relevant to a clocked digital circuit? Penn ESE 370 Fall 2010 -- De. Hon 16

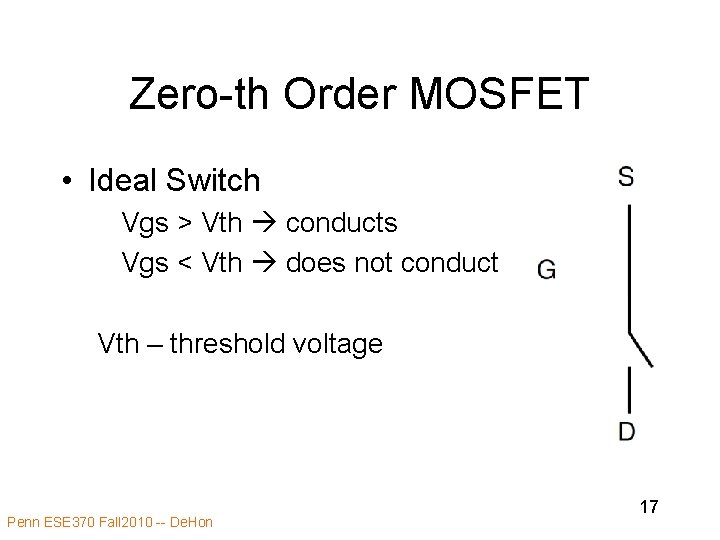

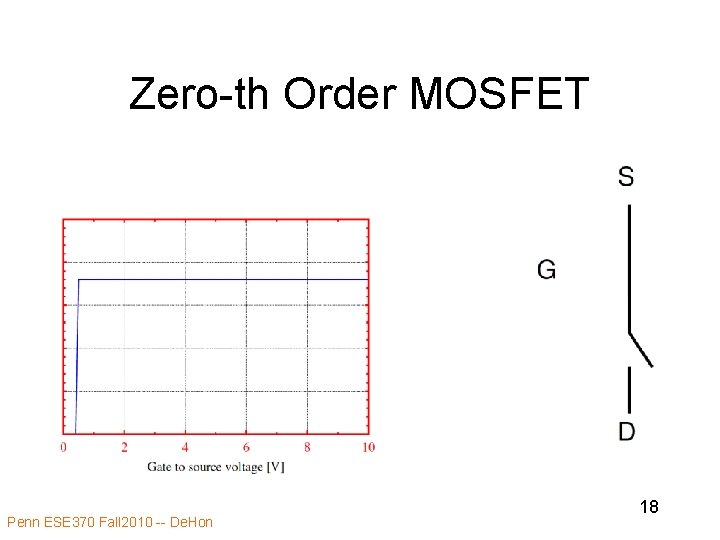

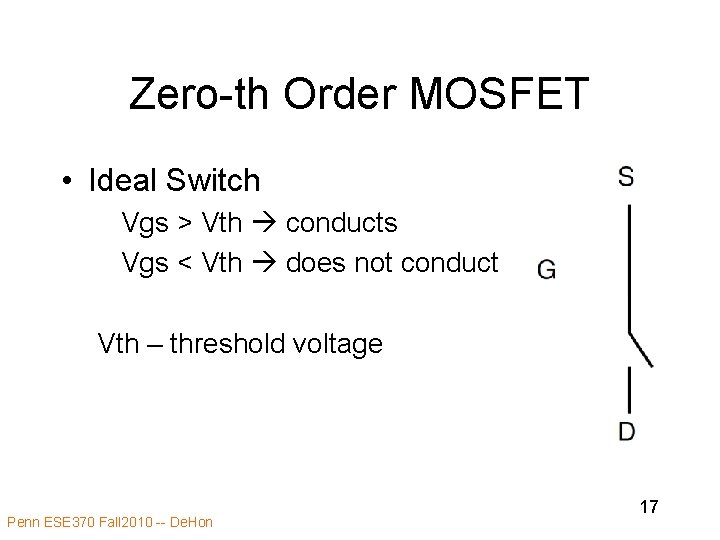

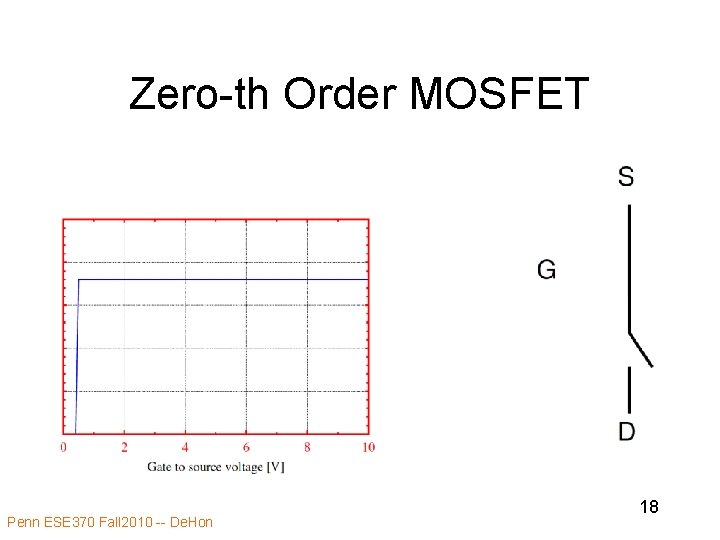

Zero-th Order MOSFET • Ideal Switch Vgs > Vth conducts Vgs < Vth does not conduct Vth – threshold voltage Penn ESE 370 Fall 2010 -- De. Hon 17

Zero-th Order MOSFET Penn ESE 370 Fall 2010 -- De. Hon 18

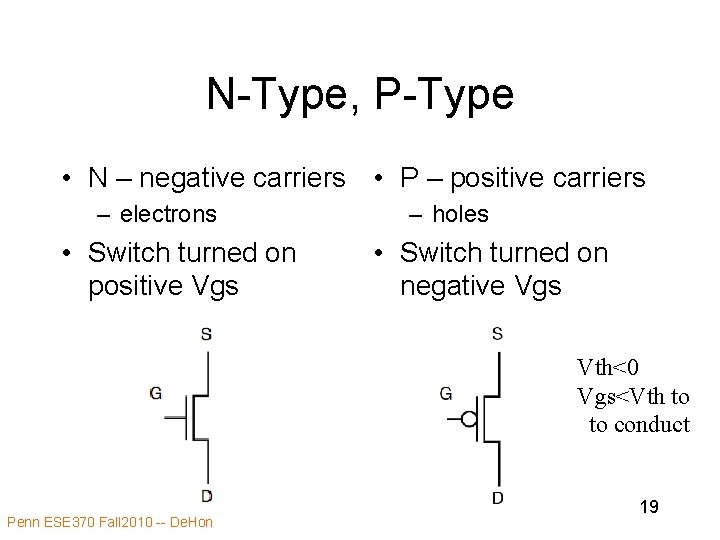

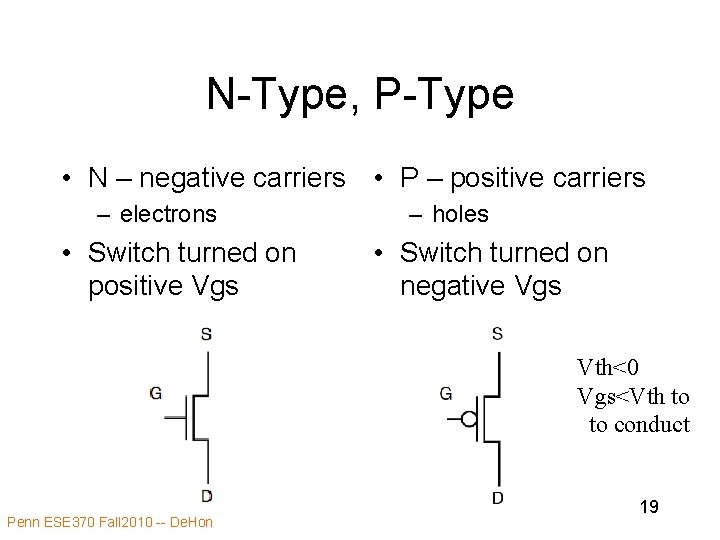

N-Type, P-Type • N – negative carriers • P – positive carriers – electrons • Switch turned on positive Vgs – holes • Switch turned on negative Vgs Vth<0 Vgs<Vth to to conduct Penn ESE 370 Fall 2010 -- De. Hon 19

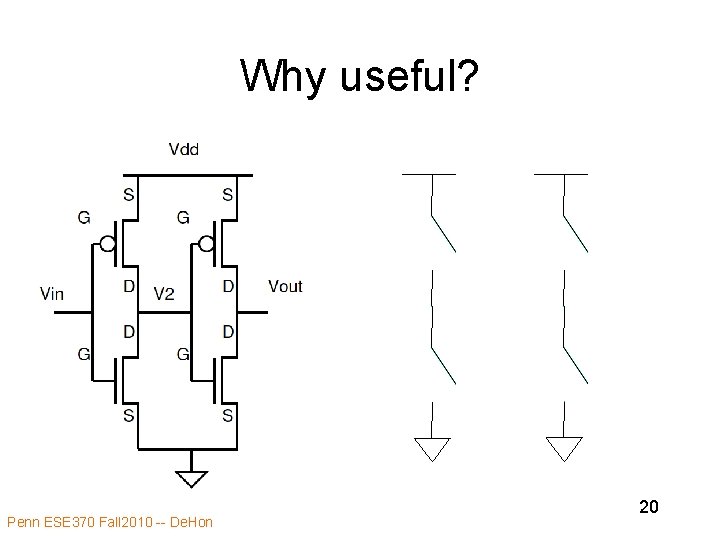

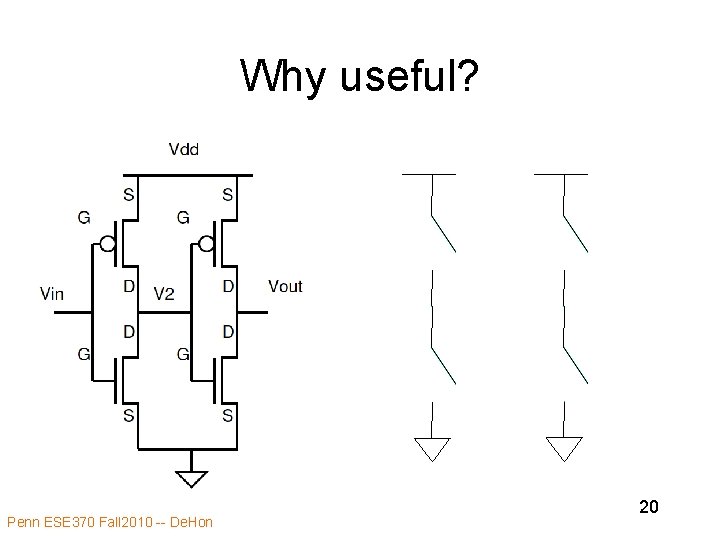

Why useful? Penn ESE 370 Fall 2010 -- De. Hon 20

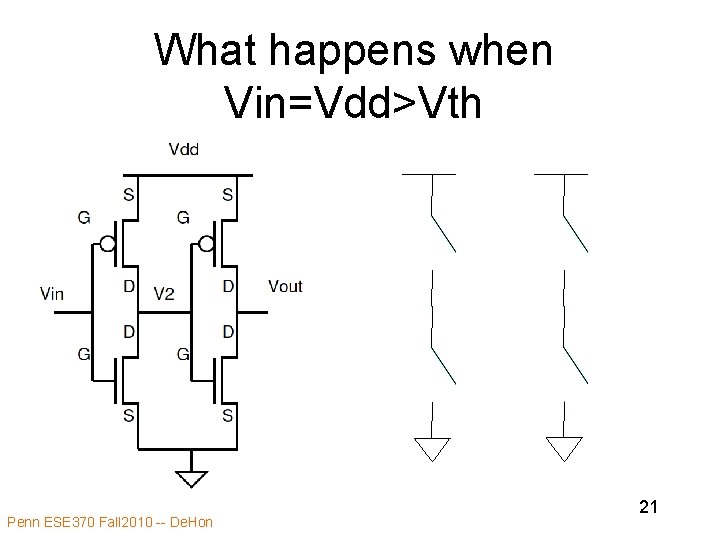

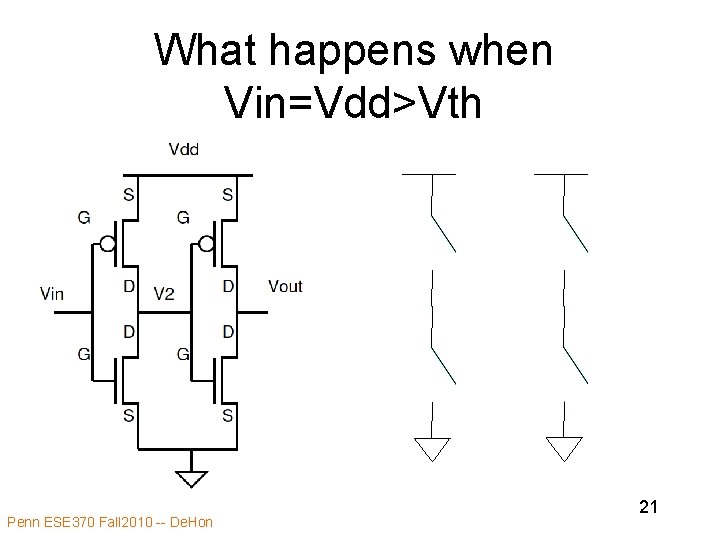

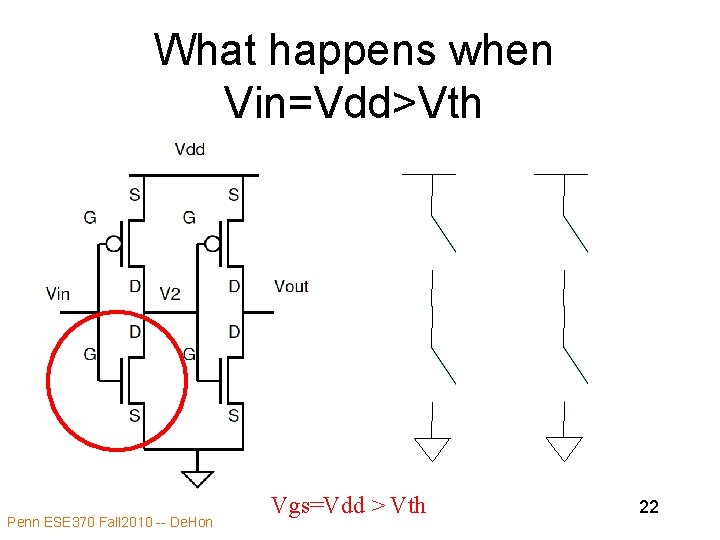

What happens when Vin=Vdd>Vth Penn ESE 370 Fall 2010 -- De. Hon 21

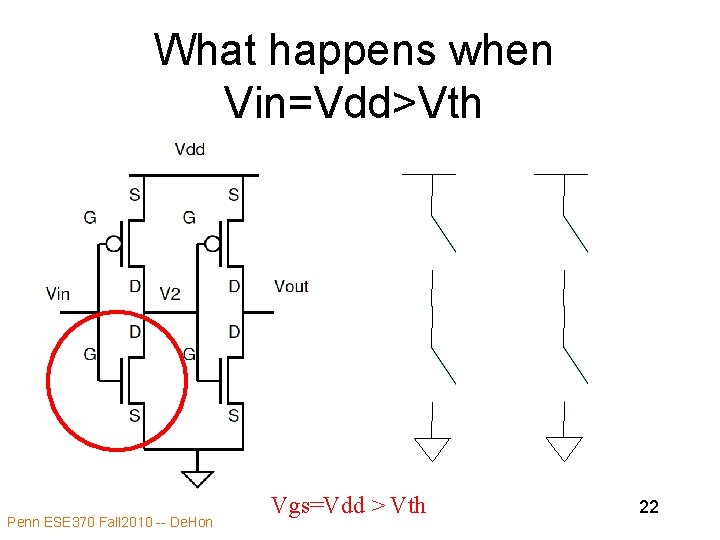

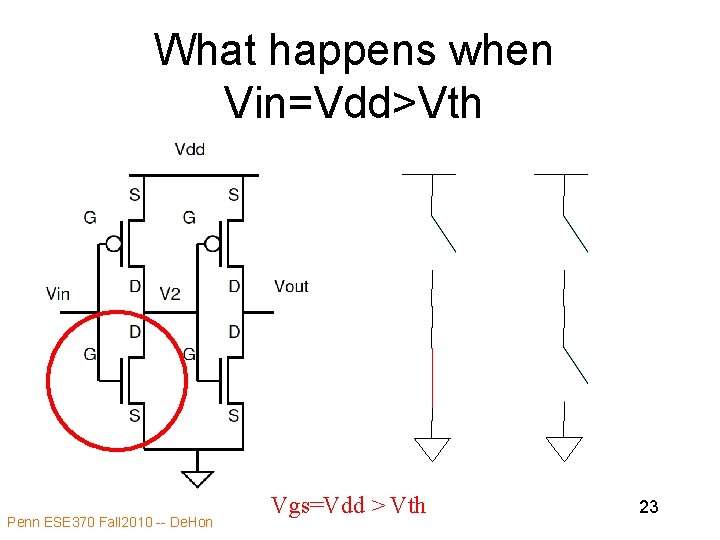

What happens when Vin=Vdd>Vth Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth 22

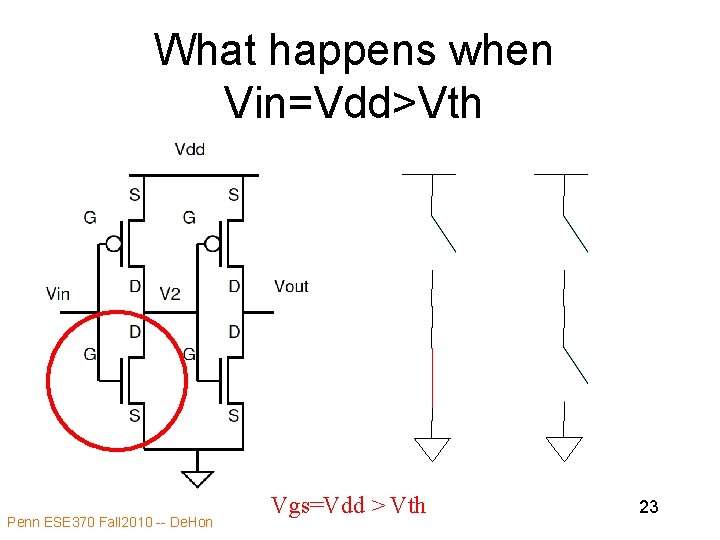

What happens when Vin=Vdd>Vth Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth 23

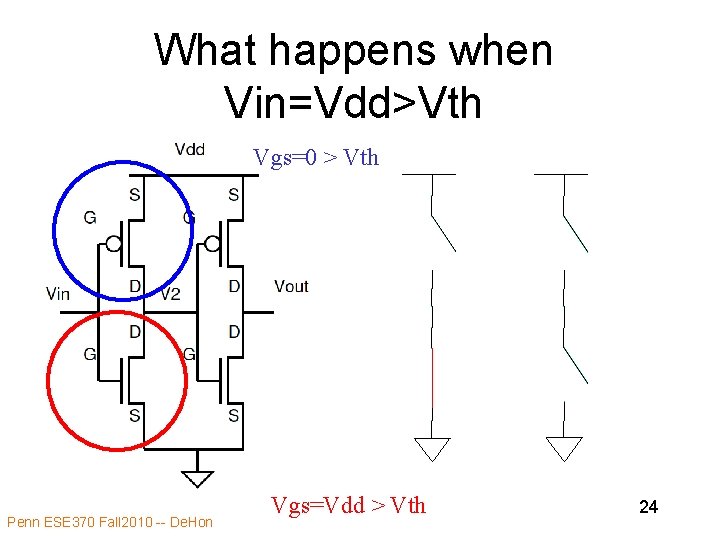

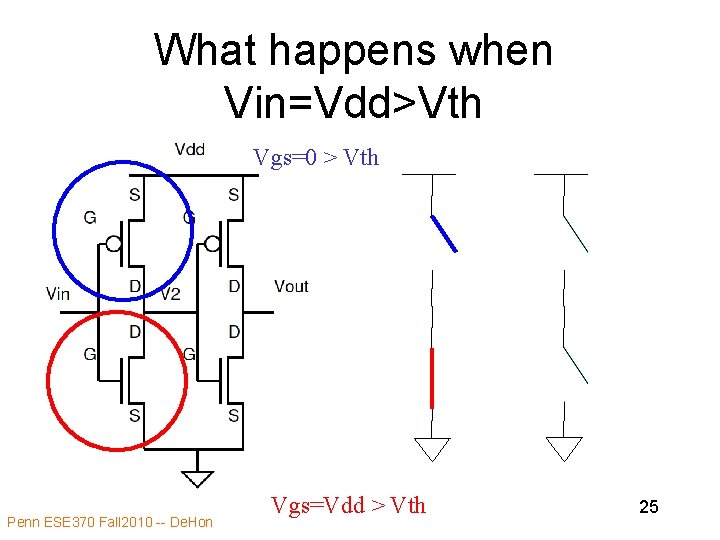

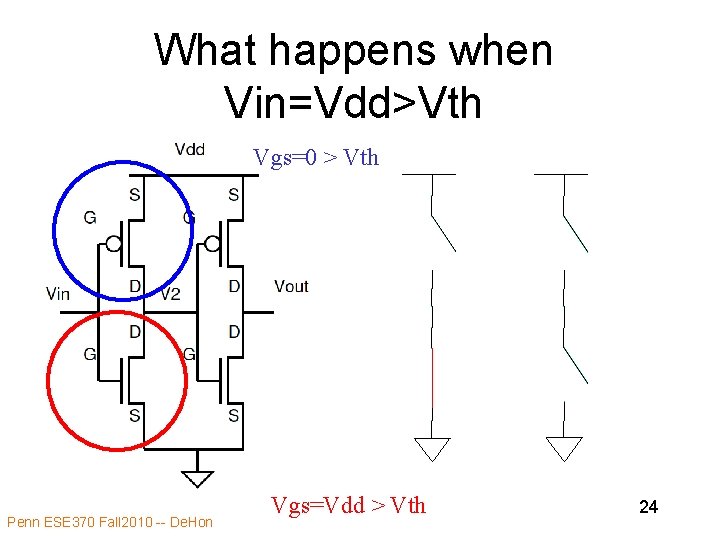

What happens when Vin=Vdd>Vth Vgs=0 > Vth Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth 24

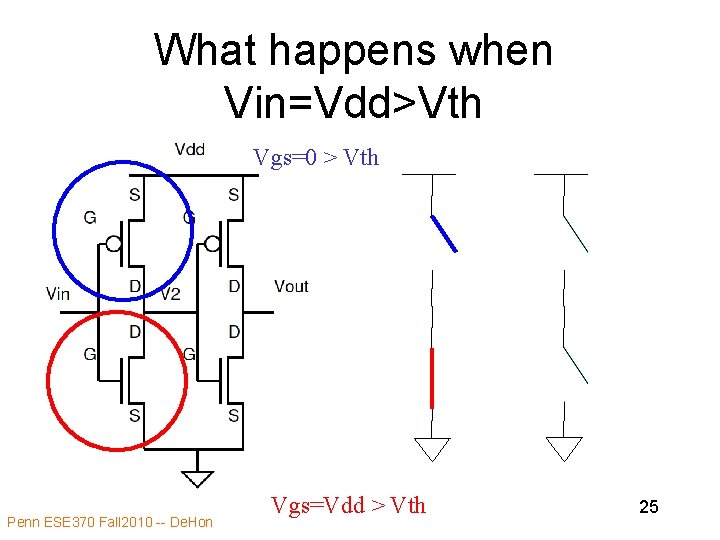

What happens when Vin=Vdd>Vth Vgs=0 > Vth Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth 25

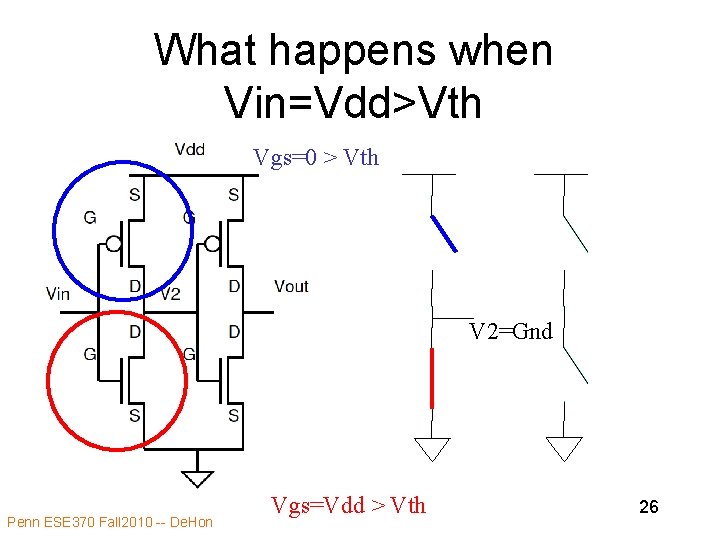

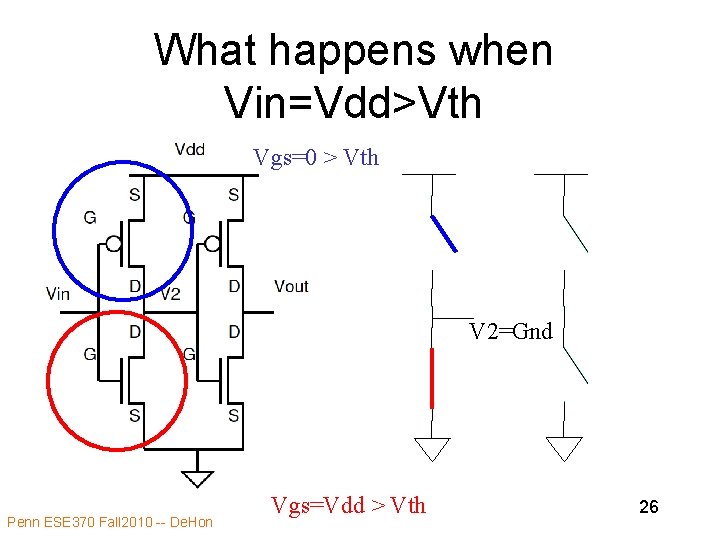

What happens when Vin=Vdd>Vth Vgs=0 > Vth V 2=Gnd Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth 26

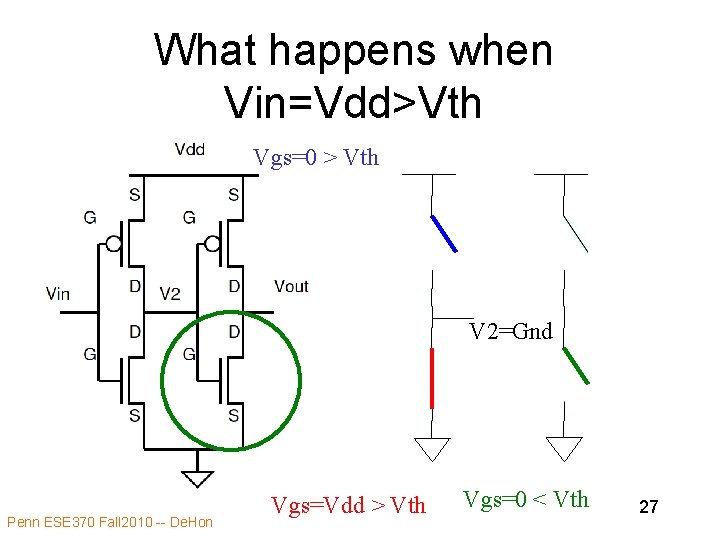

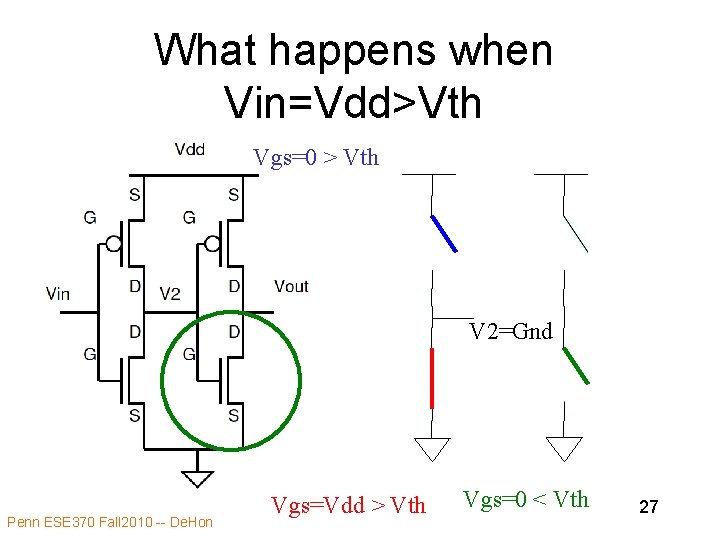

What happens when Vin=Vdd>Vth Vgs=0 > Vth V 2=Gnd Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth Vgs=0 < Vth 27

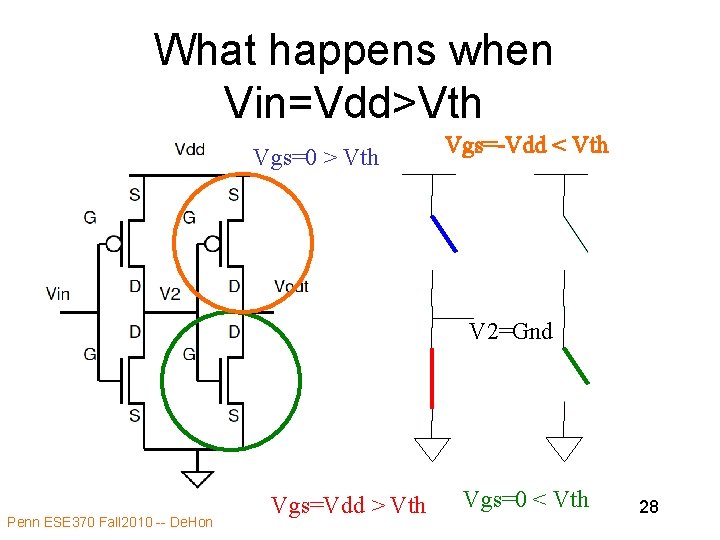

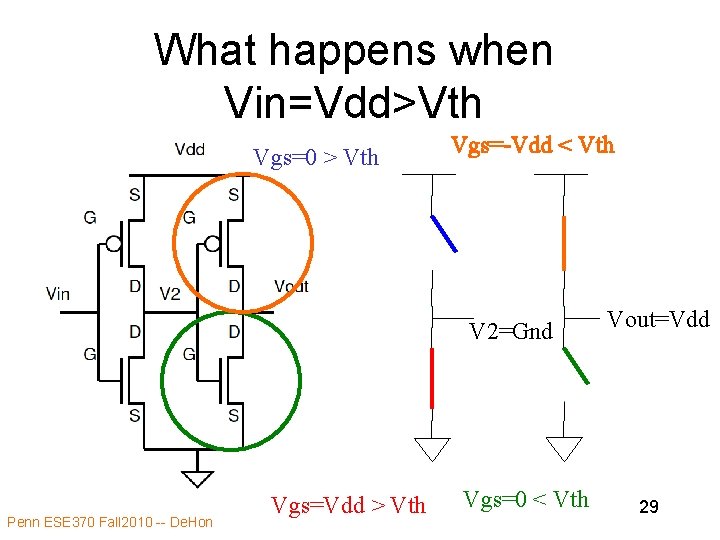

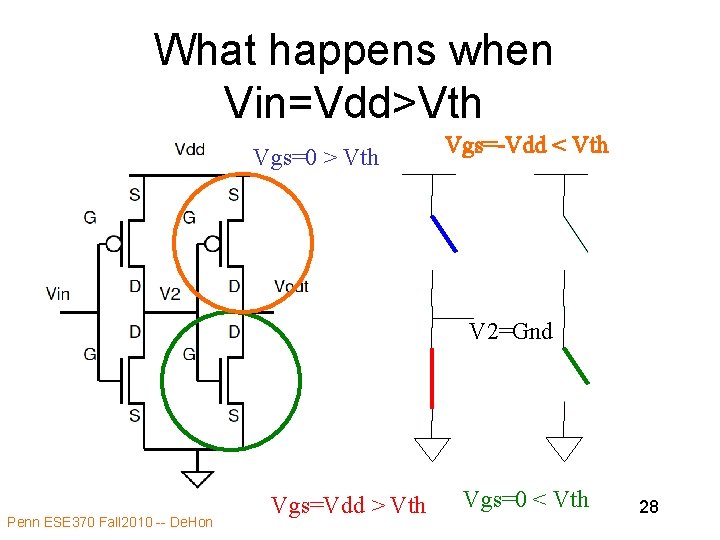

What happens when Vin=Vdd>Vth Vgs=0 > Vth Vgs=-Vdd < Vth V 2=Gnd Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth Vgs=0 < Vth 28

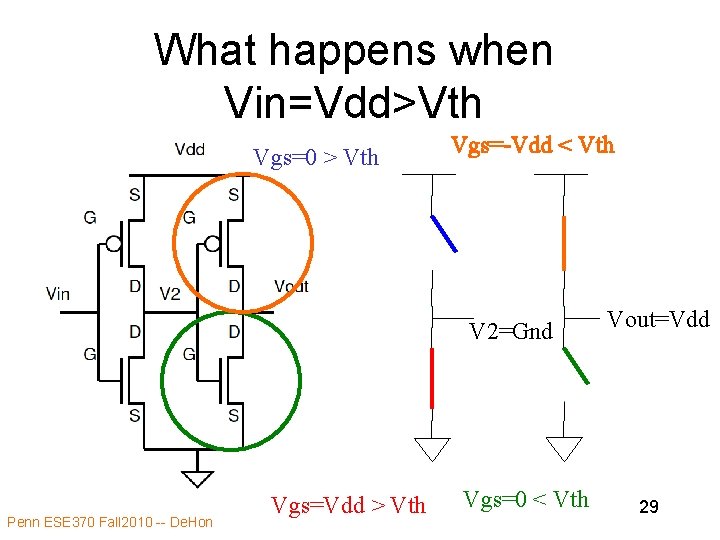

What happens when Vin=Vdd>Vth Vgs=0 > Vth Vgs=-Vdd < Vth V 2=Gnd Penn ESE 370 Fall 2010 -- De. Hon Vgs=Vdd > Vth Vgs=0 < Vth Vout=Vdd 29

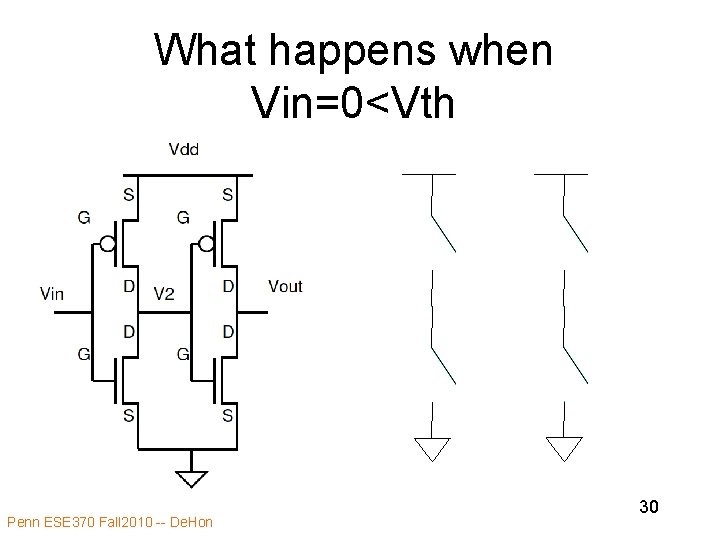

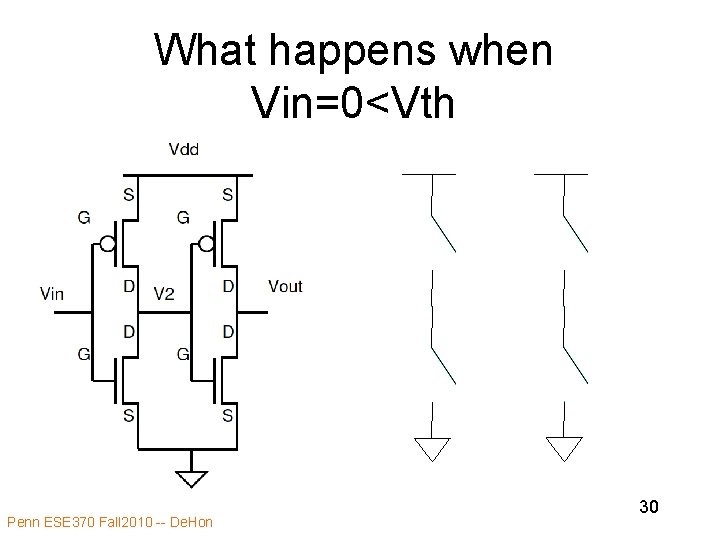

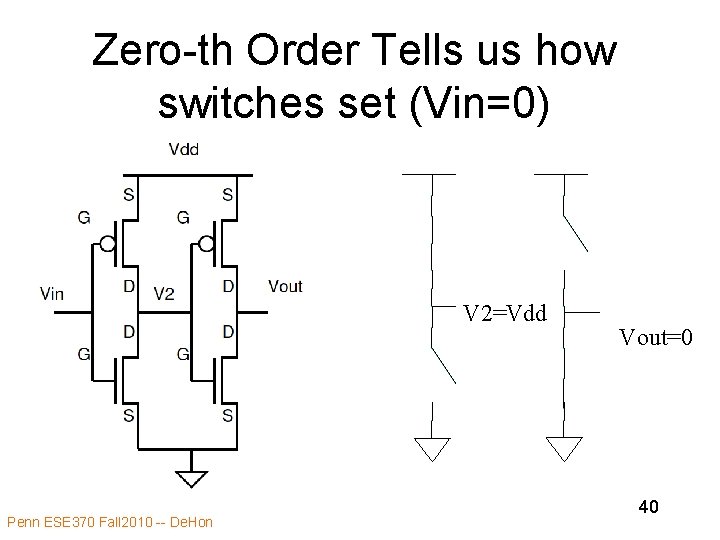

What happens when Vin=0<Vth Penn ESE 370 Fall 2010 -- De. Hon 30

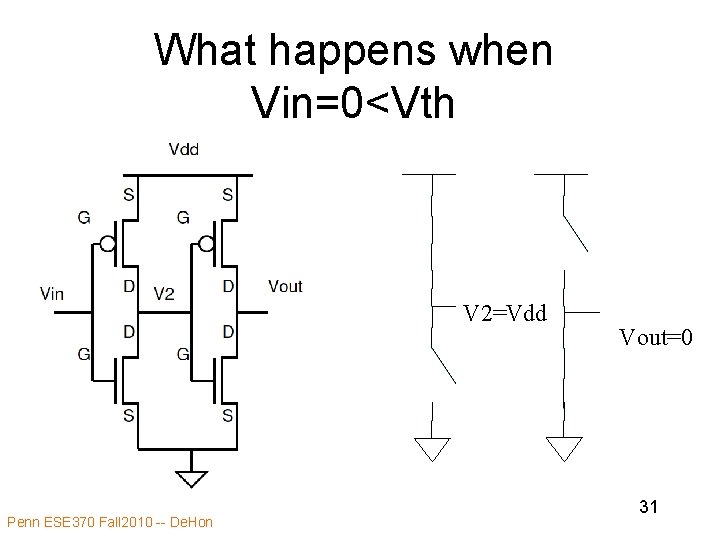

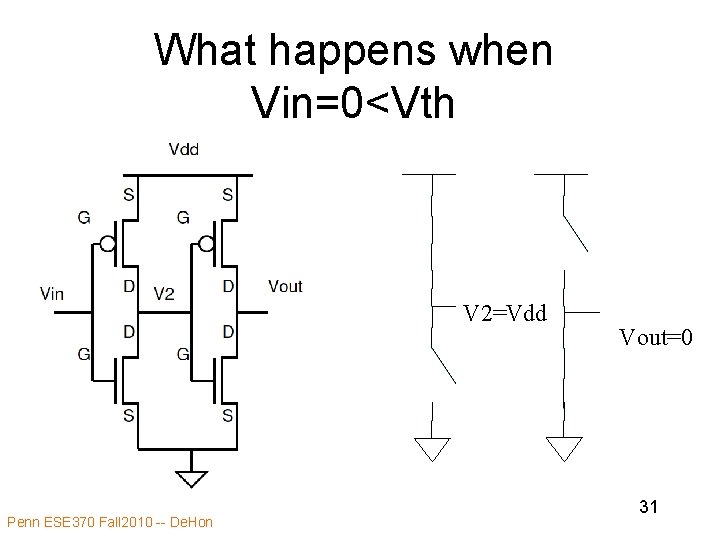

What happens when Vin=0<Vth V 2=Vdd Penn ESE 370 Fall 2010 -- De. Hon Vout=0 31

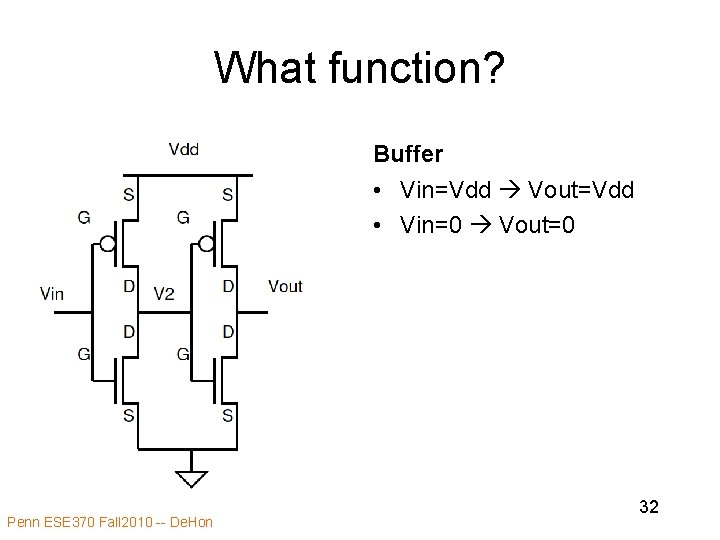

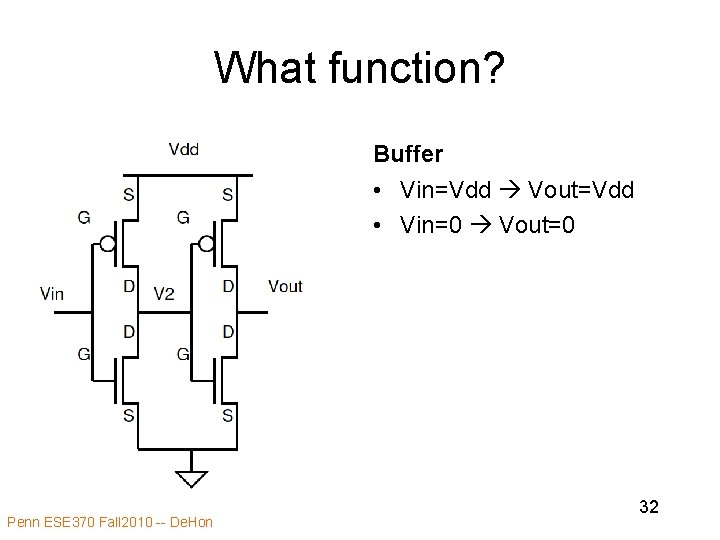

What function? Buffer • Vin=Vdd Vout=Vdd • Vin=0 Vout=0 Penn ESE 370 Fall 2010 -- De. Hon 32

Why Useful? • Allows us to reason (mostly) at logic level about steady-state functionality of typical gate circuits Penn ESE 370 Fall 2010 -- De. Hon 33

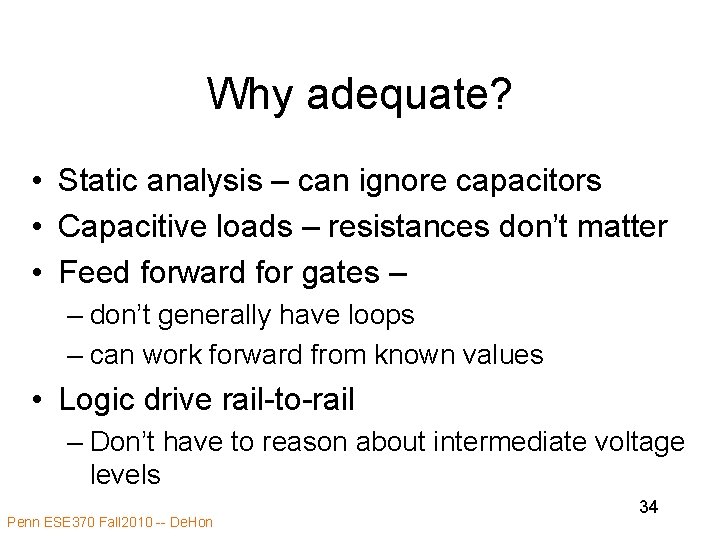

Why adequate? • Static analysis – can ignore capacitors • Capacitive loads – resistances don’t matter • Feed forward for gates – – don’t generally have loops – can work forward from known values • Logic drive rail-to-rail – Don’t have to reason about intermediate voltage levels Penn ESE 370 Fall 2010 -- De. Hon 34

What not tell us? • Delay • Dynamics • Behavior if not – Capacitively loaded – Loops Penn ESE 370 Fall 2010 -- De. Hon 35

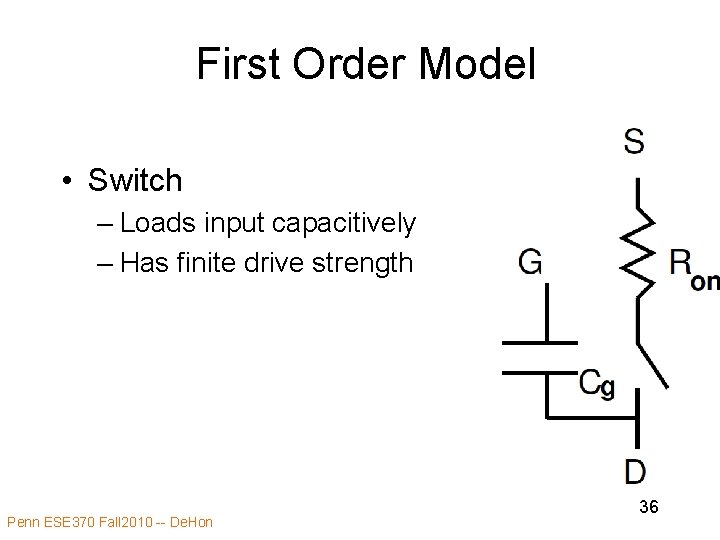

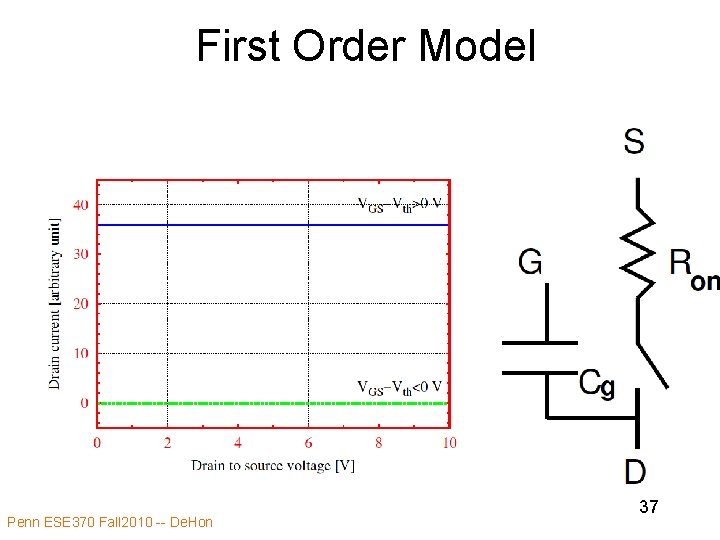

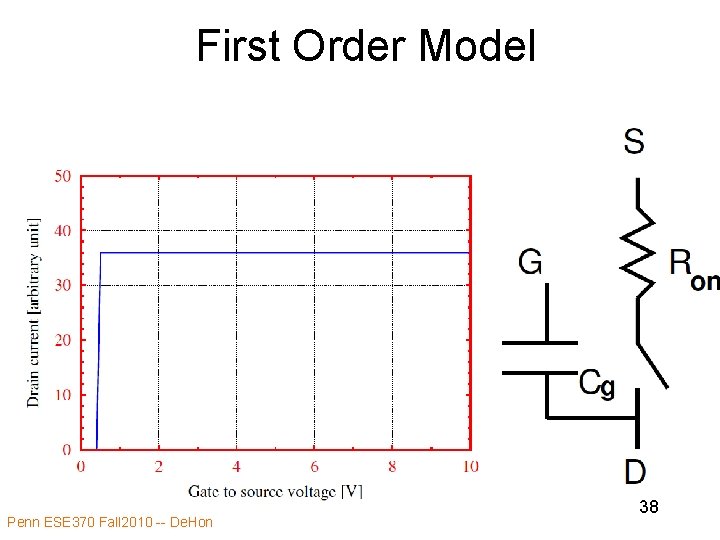

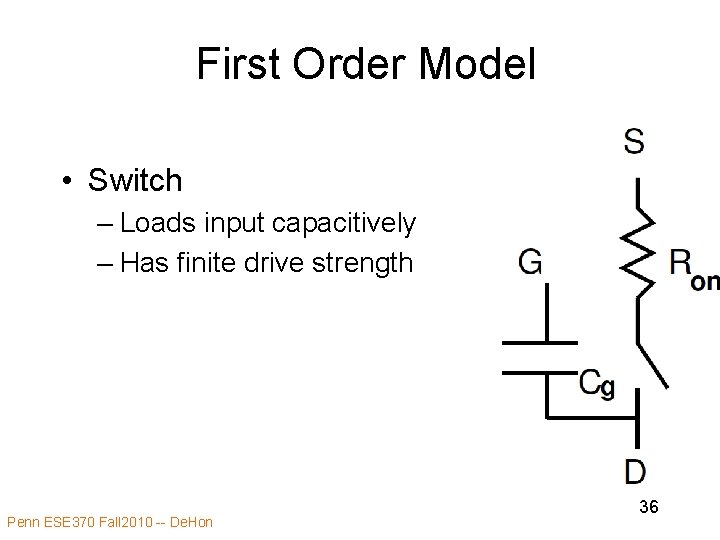

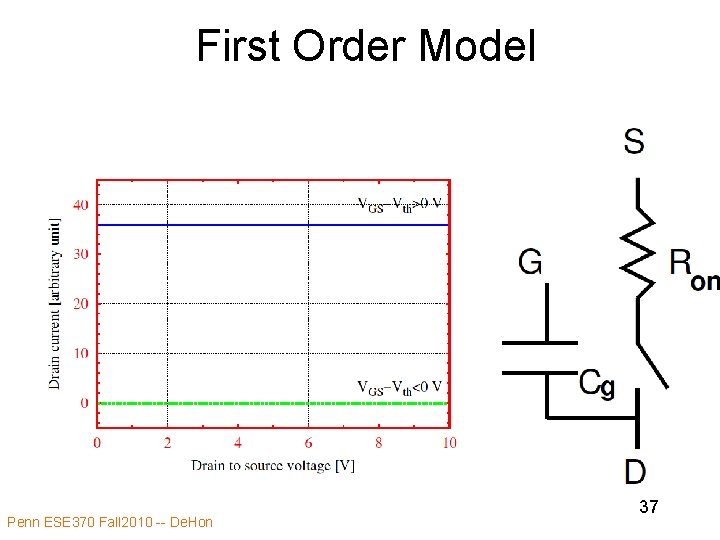

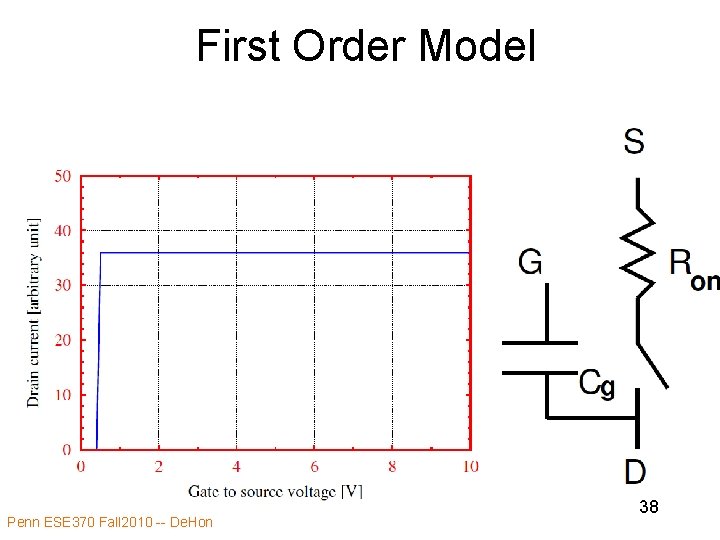

First Order Model • Switch – Loads input capacitively – Has finite drive strength Penn ESE 370 Fall 2010 -- De. Hon 36

First Order Model Penn ESE 370 Fall 2010 -- De. Hon 37

First Order Model Penn ESE 370 Fall 2010 -- De. Hon 38

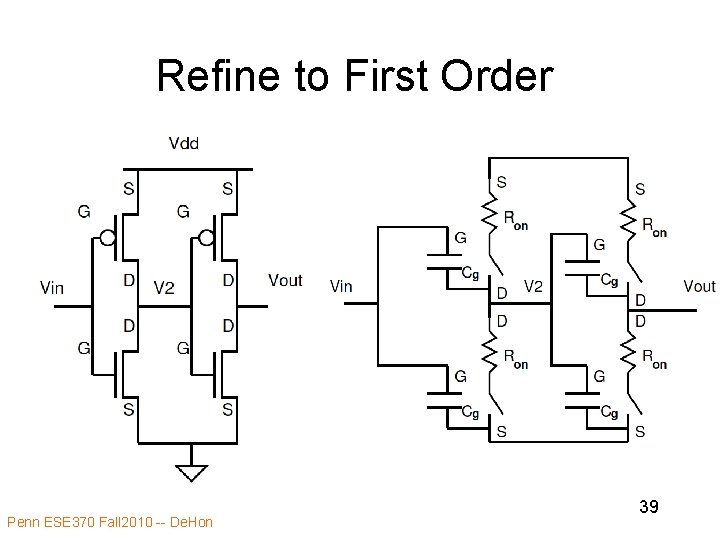

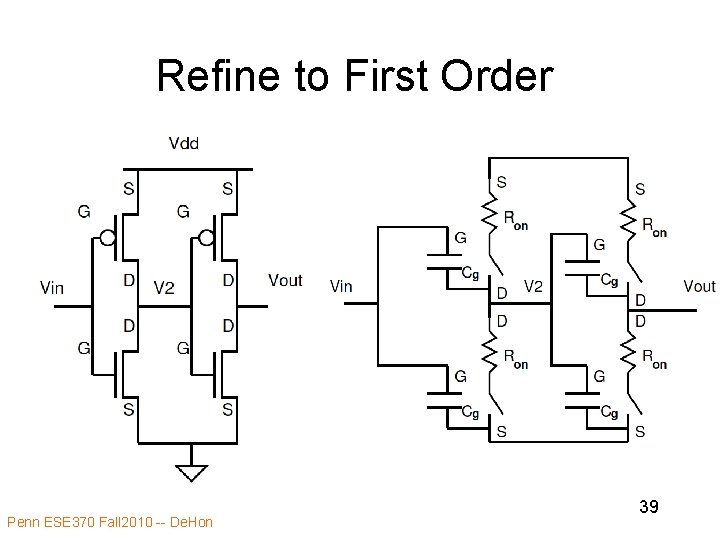

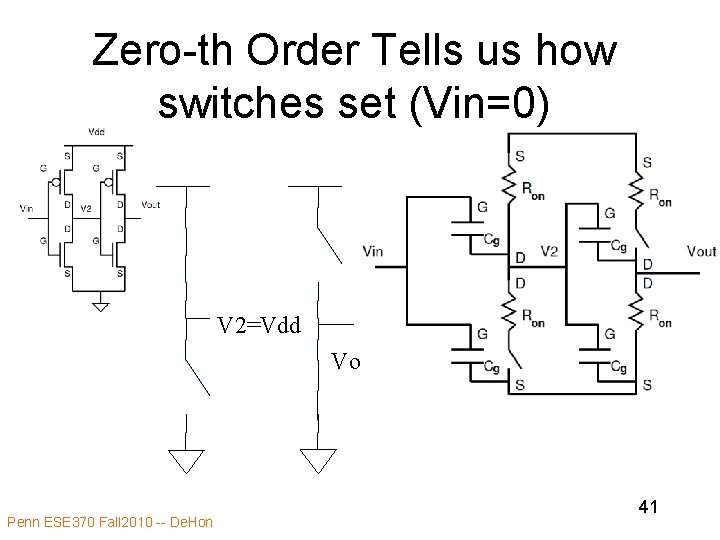

Refine to First Order Penn ESE 370 Fall 2010 -- De. Hon 39

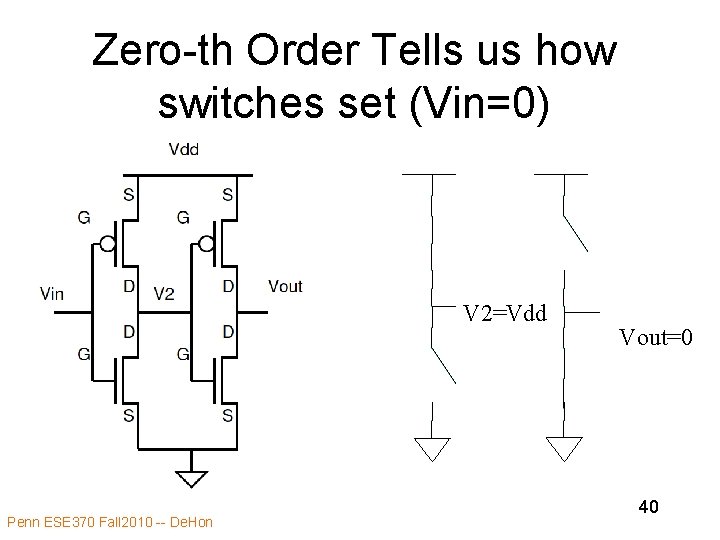

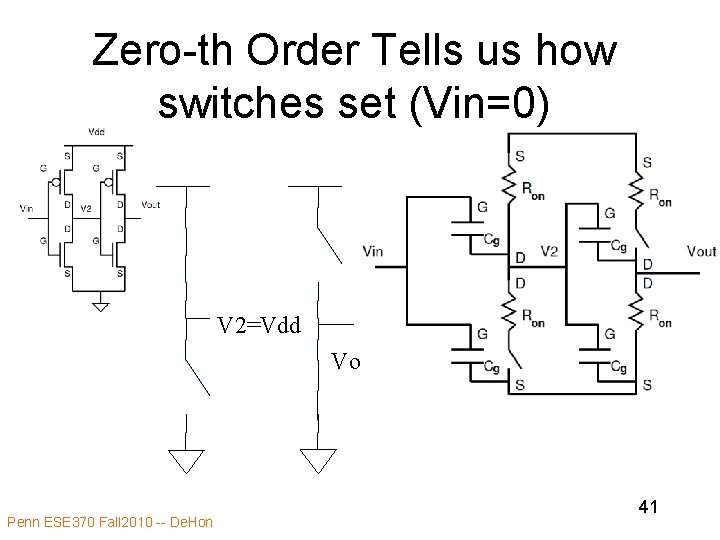

Zero-th Order Tells us how switches set (Vin=0) V 2=Vdd Penn ESE 370 Fall 2010 -- De. Hon Vout=0 40

Zero-th Order Tells us how switches set (Vin=0) V 2=Vdd Vout=0 Penn ESE 370 Fall 2010 -- De. Hon 41

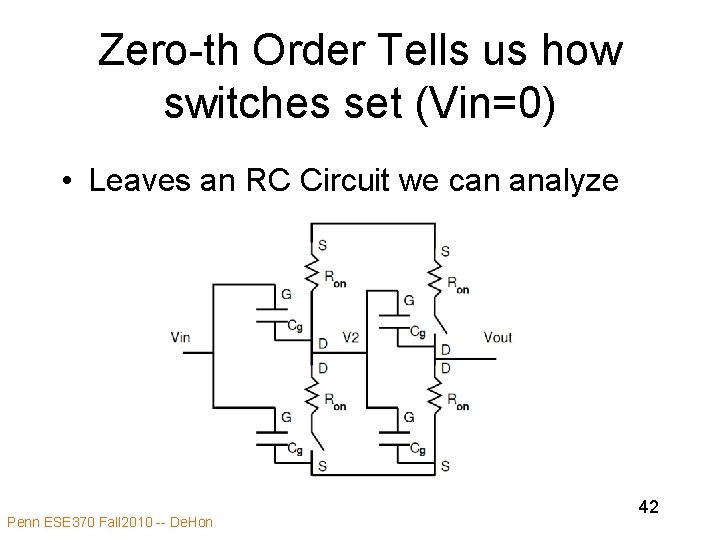

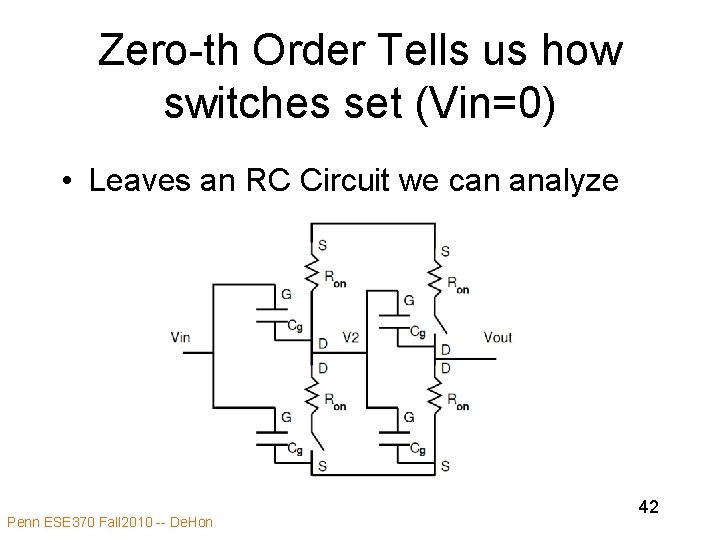

Zero-th Order Tells us how switches set (Vin=0) • Leaves an RC Circuit we can analyze Penn ESE 370 Fall 2010 -- De. Hon 42

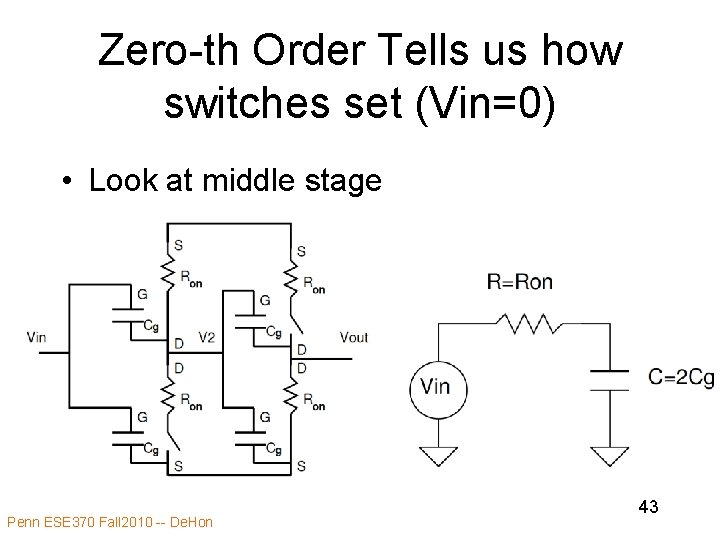

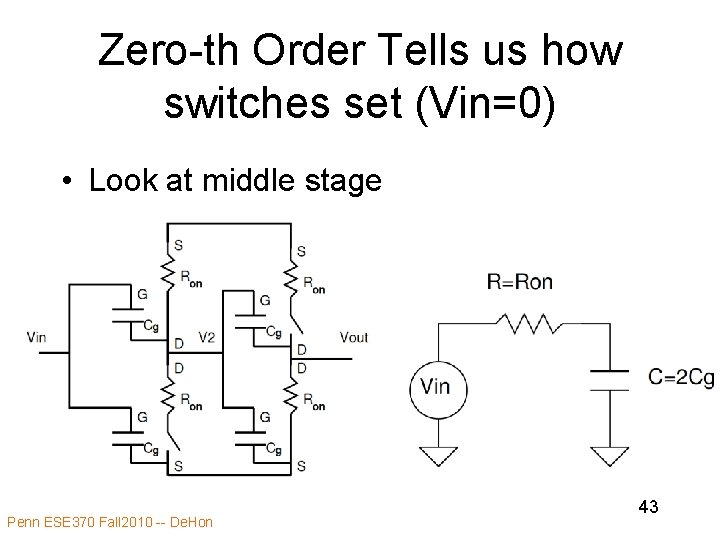

Zero-th Order Tells us how switches set (Vin=0) • Look at middle stage Penn ESE 370 Fall 2010 -- De. Hon 43

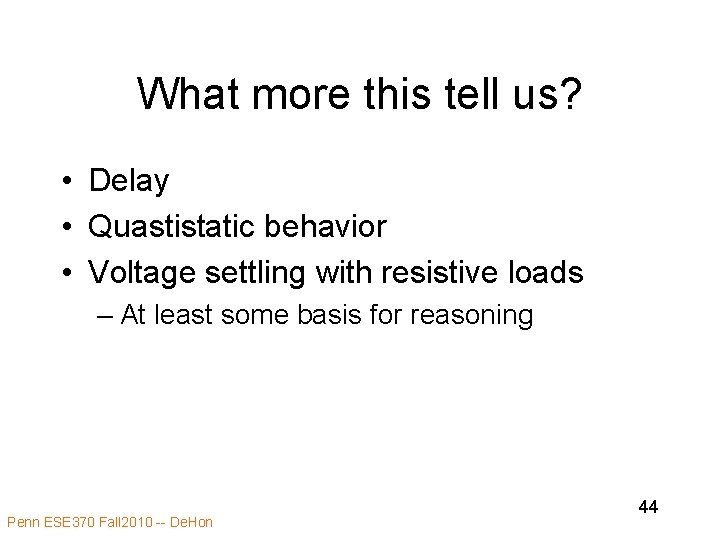

What more this tell us? • Delay • Quastistatic behavior • Voltage settling with resistive loads – At least some basis for reasoning Penn ESE 370 Fall 2010 -- De. Hon 44

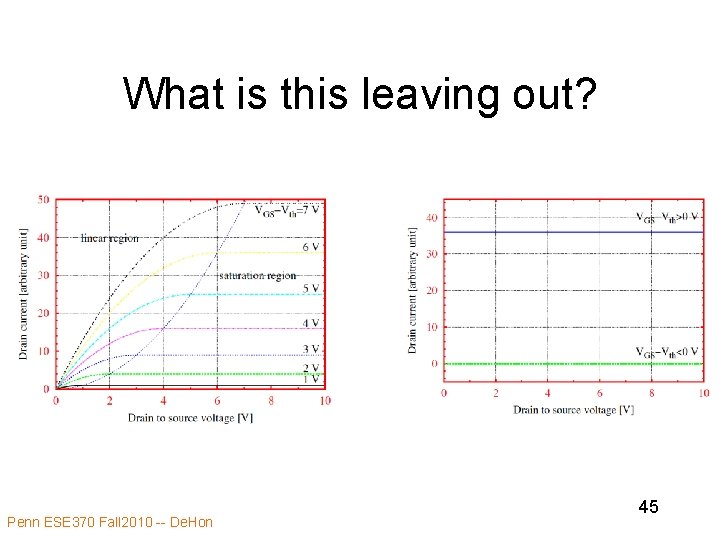

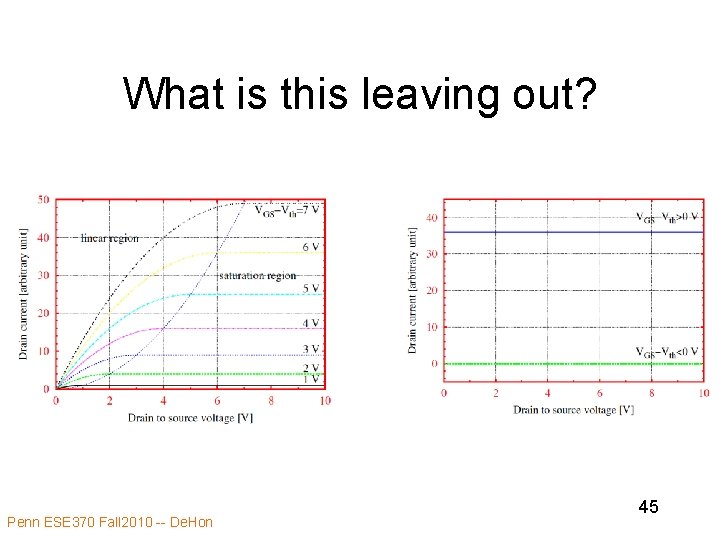

What is this leaving out? Penn ESE 370 Fall 2010 -- De. Hon 45

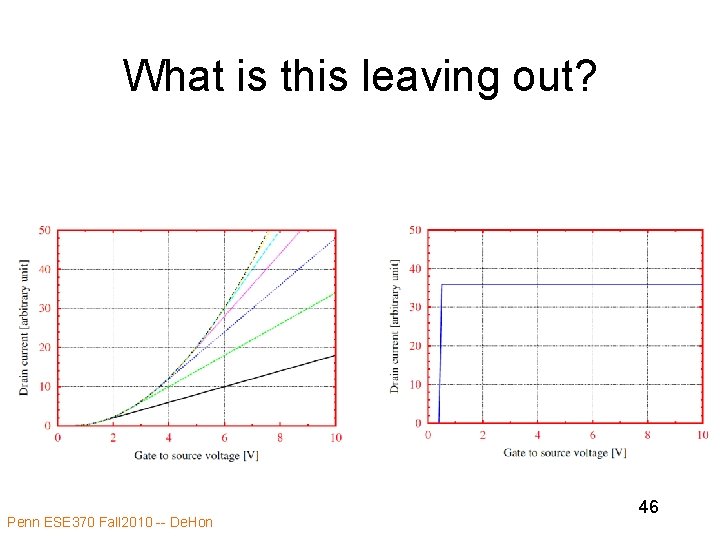

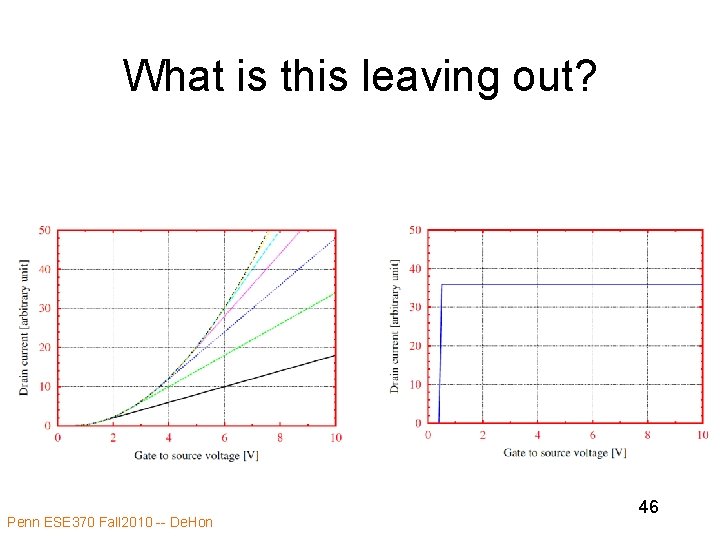

What is this leaving out? Penn ESE 370 Fall 2010 -- De. Hon 46

What leaving out? • What happens at intermediate voltages – Not rail-to-rail • Details of dynamics, including… – Input not transition as step – Intermediate drive strengths change with Vgs – As output charges Vds changes, changing drive strenght • Isn’t really 0 current below threshold Penn ESE 370 Fall 2010 -- De. Hon 47

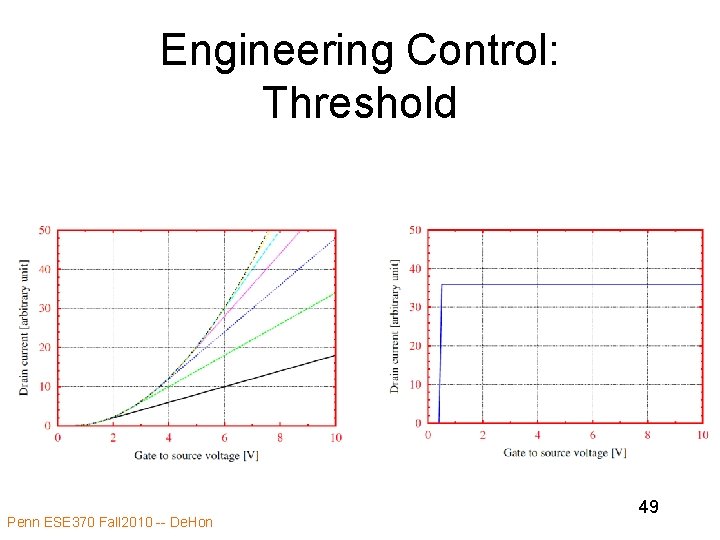

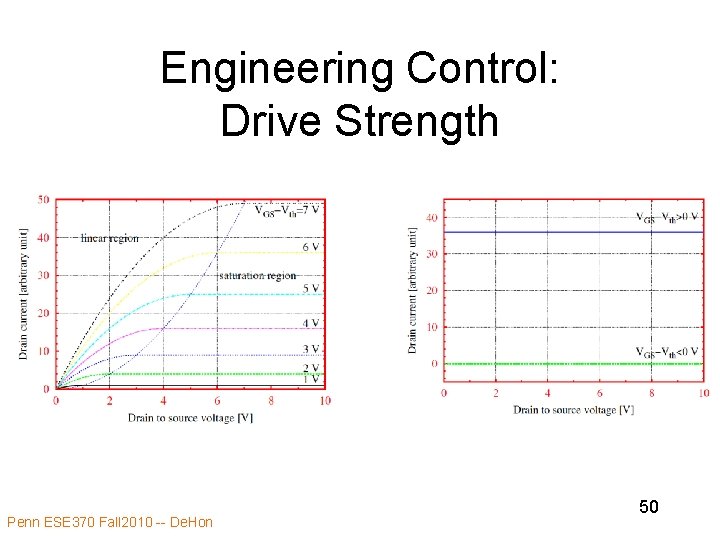

Engineering Control • Vth – process engineer • Drive strength – circuit engineer control with sizing • Supply voltages – range set by process, detail use by circuit design Penn ESE 370 Fall 2010 -- De. Hon 48

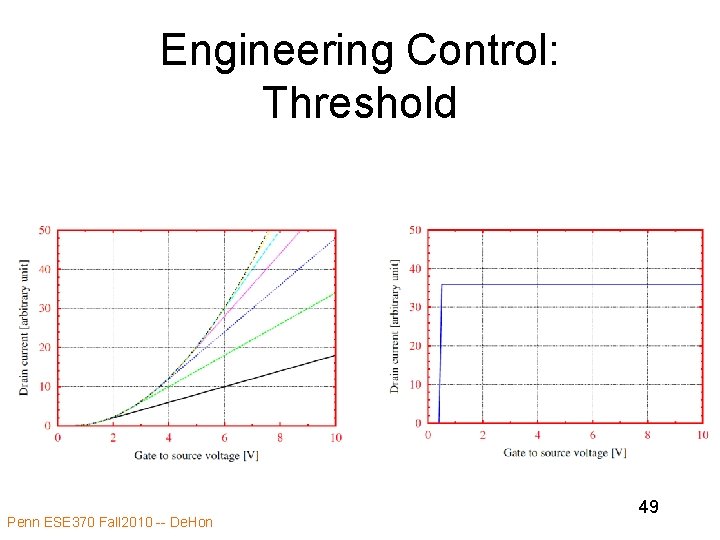

Engineering Control: Threshold Penn ESE 370 Fall 2010 -- De. Hon 49

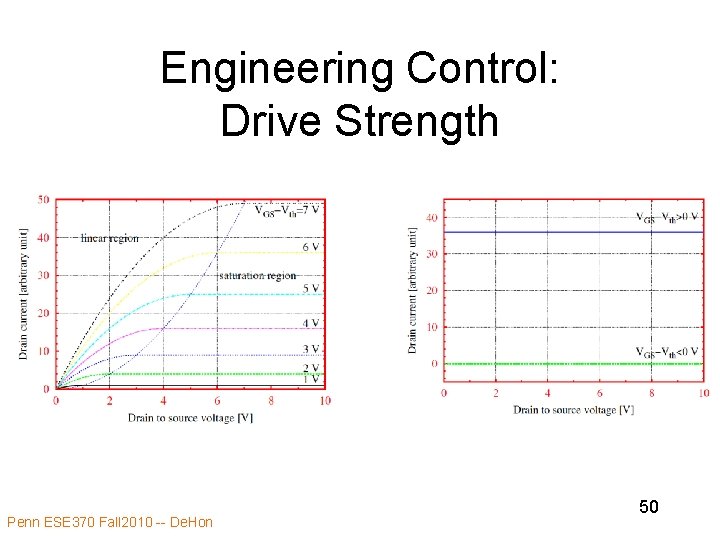

Engineering Control: Drive Strength Penn ESE 370 Fall 2010 -- De. Hon 50

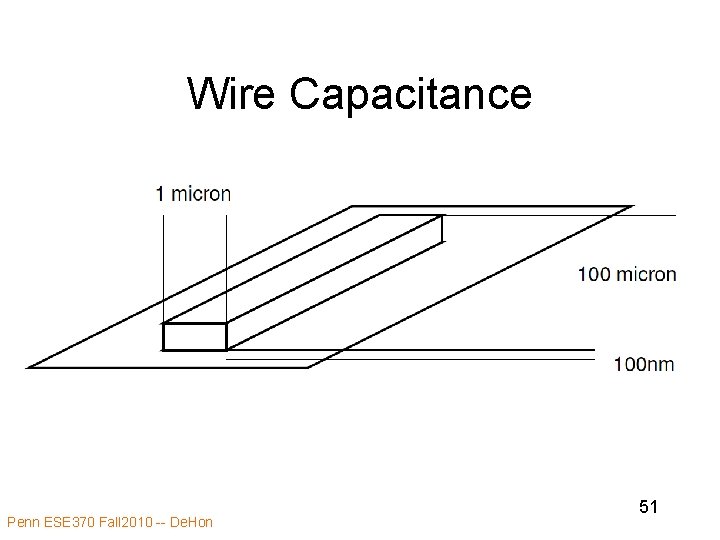

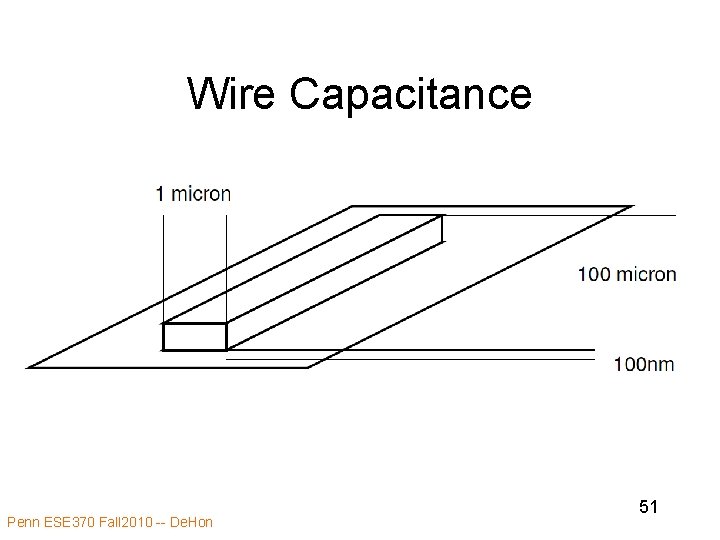

Wire Capacitance Penn ESE 370 Fall 2010 -- De. Hon 51

Wire Capacitance Penn ESE 370 Fall 2010 -- De. Hon 52

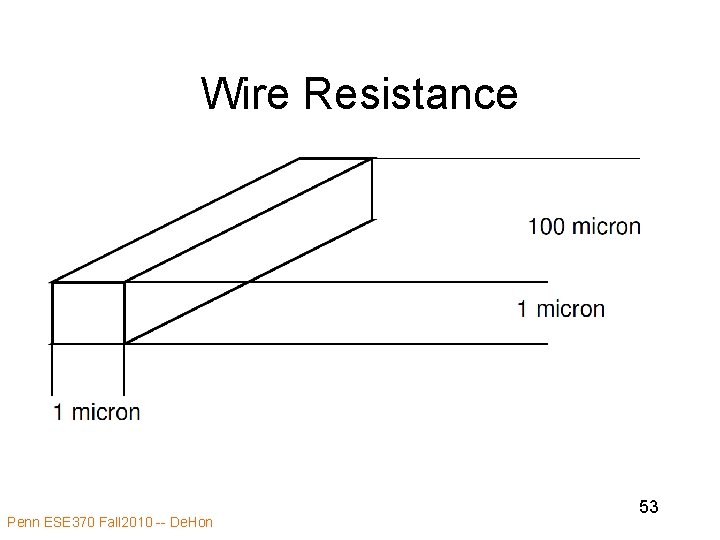

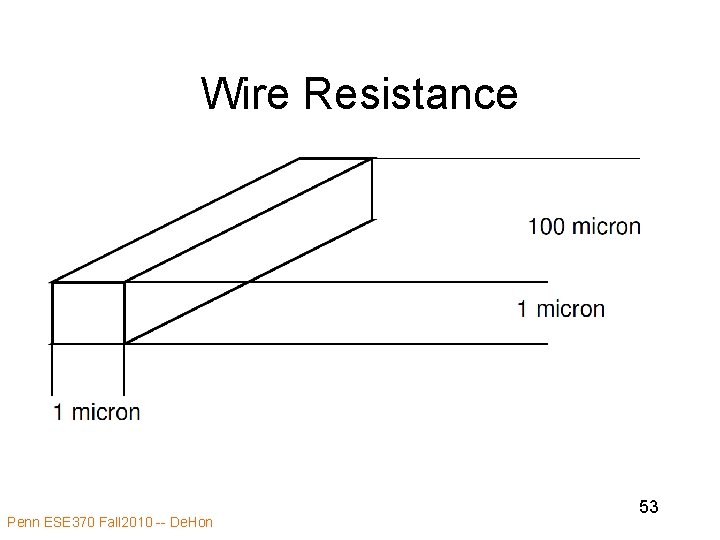

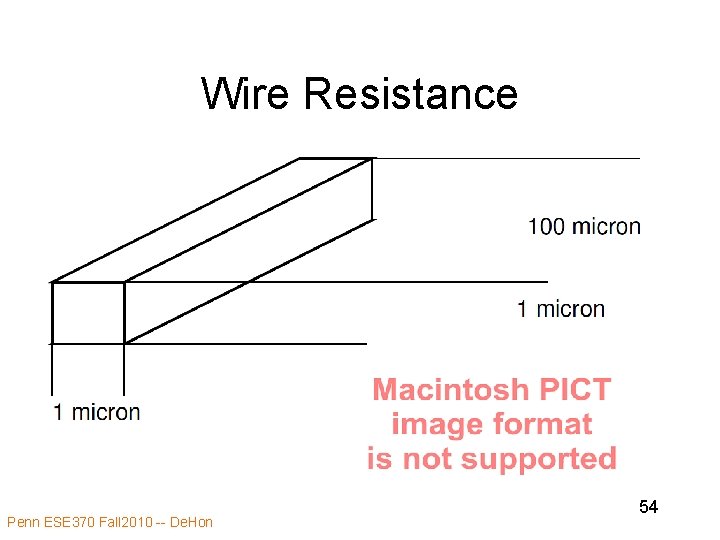

Wire Resistance Penn ESE 370 Fall 2010 -- De. Hon 53

Wire Resistance Penn ESE 370 Fall 2010 -- De. Hon 54

Wire Resistance • Sanity check – Wire twice as long = resistors in series – Wire twice as wide = resistors in parallel Penn ESE 370 Fall 2010 -- De. Hon 55

There always Rs and Cs • Modeling vs. discrete components • Dominant effects – Rbig + Rsmall ≈ Rbig – Cbig || Csmall ≈ Csmall Penn ESE 370 Fall 2010 -- De. Hon 56

Admin • TA: Andrew Townley – Email: atownley – Office Hours: seas • Lecture Monday: building gates – Reading • Lab on Wednesday Penn ESE 370 Fall 2010 -- De. Hon 57

MOSFET Penn ESE 370 Fall 2010 -- De. Hon 58

Big Ideas • MOSFET Transistor as switch • Purpose-driven simplified modeling – Aid reasoning – Sanity check – Simplify design • New perspective on Rs and Cs Penn ESE 370 Fall 2010 -- De. Hon 59