ESE 370 CircuitLevel Modeling Design and Optimization for

- Slides: 20

ESE 370: Circuit-Level Modeling, Design, and Optimization for Digital Systems Day 16: October 17, 2011 Performance: Gates Penn ESE 370 Fall 2011 -- De. Hon 1

First Order Delay • R 0 = Resistance of minimum size NMOS device • C 0 = gate capacitance of minimum size NMOS device • Rdrive = R 0/Wn Cg = WC 0 • Technology independent relative delay t = R 0 C 0 Penn ESE 370 Fall 2011 -- De. Hon 2

Today • • • Delay in Gates Data Dependent Delay Large Fanin Capacitance in Gates Asymmetry of Inputs Penn ESE 370 Fall 2011 -- De. Hon 3

Gates Penn ESE 370 Fall 2011 -- De. Hon 4

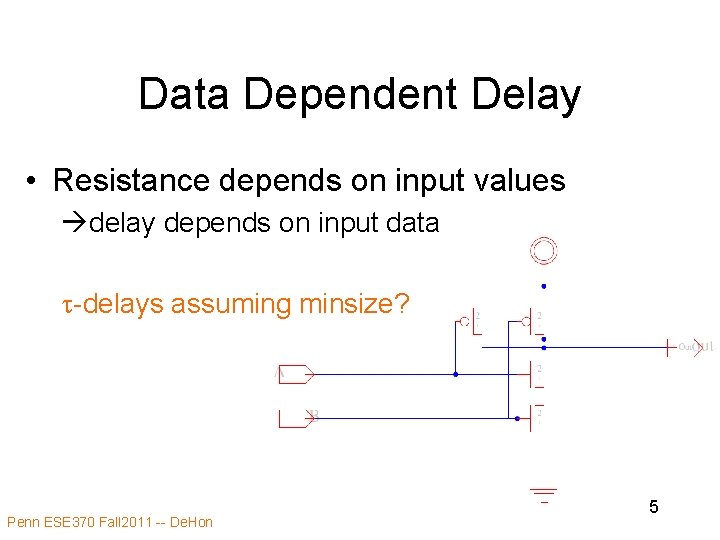

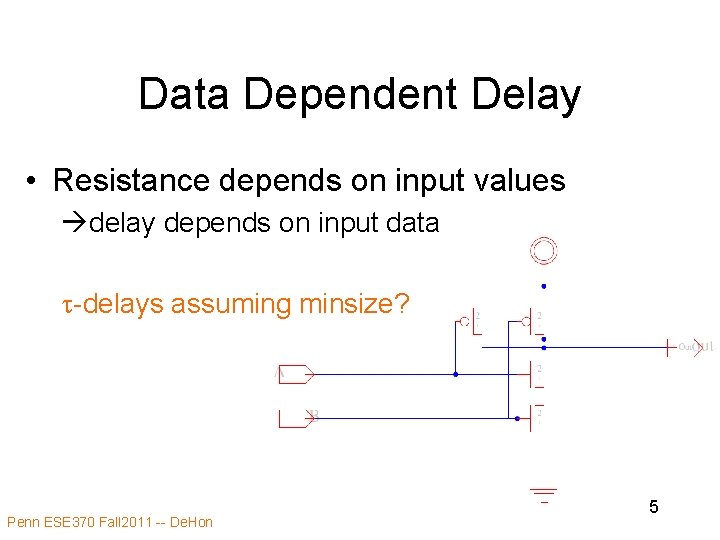

Data Dependent Delay • Resistance depends on input values àdelay depends on input data t-delays assuming minsize? Penn ESE 370 Fall 2011 -- De. Hon 5

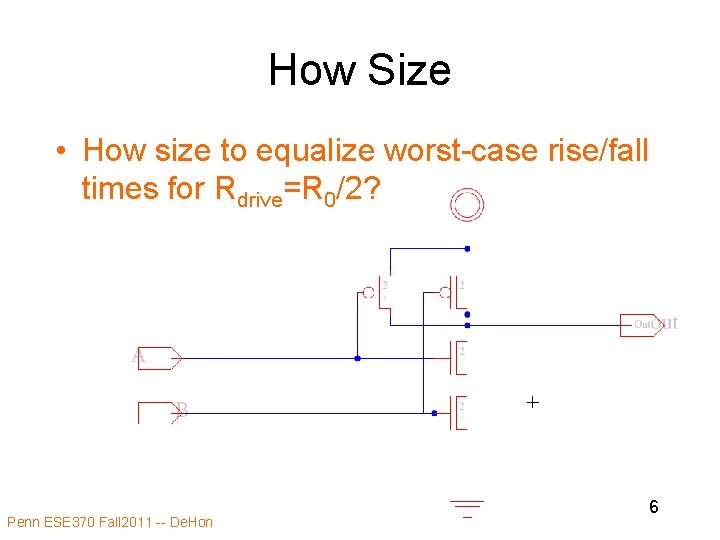

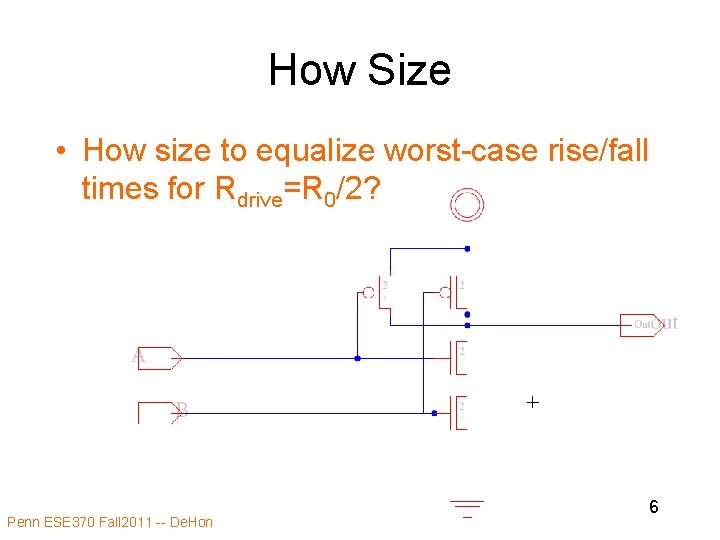

How Size • How size to equalize worst-case rise/fall times for Rdrive=R 0/2? Penn ESE 370 Fall 2011 -- De. Hon 6

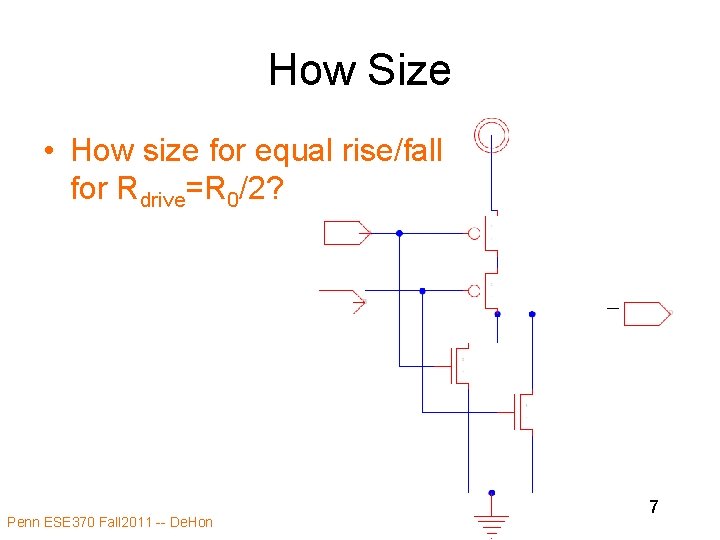

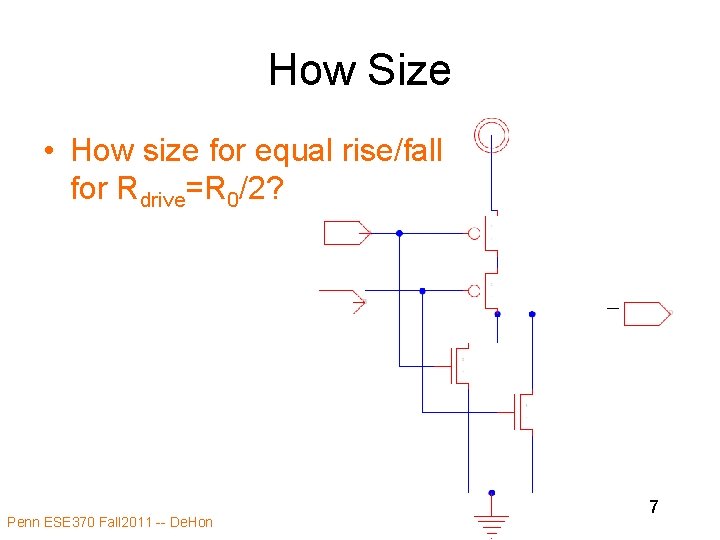

How Size • How size for equal rise/fall for Rdrive=R 0/2? Penn ESE 370 Fall 2011 -- De. Hon 7

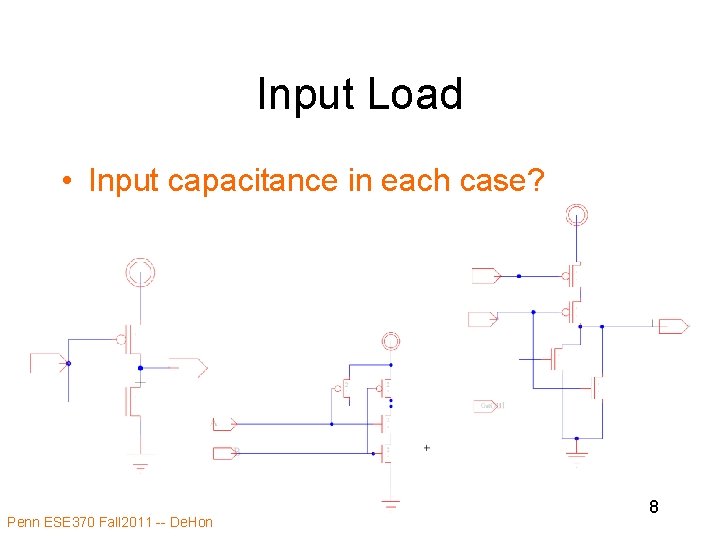

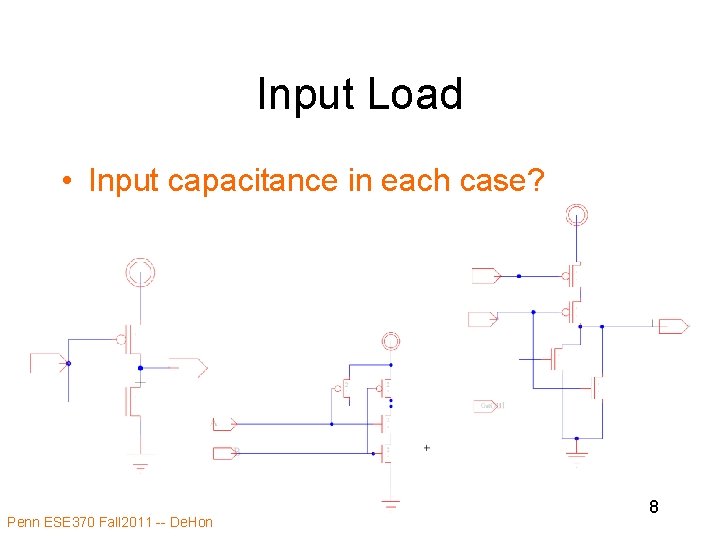

Input Load • Input capacitance in each case? Penn ESE 370 Fall 2011 -- De. Hon 8

Observe • Ratio of Input Load Capacitance to Output Drive Strength: CILoad/Ids – Differs with gate function • Some gates give more drive per capacitive load we pay Penn ESE 370 Fall 2011 -- De. Hon 9

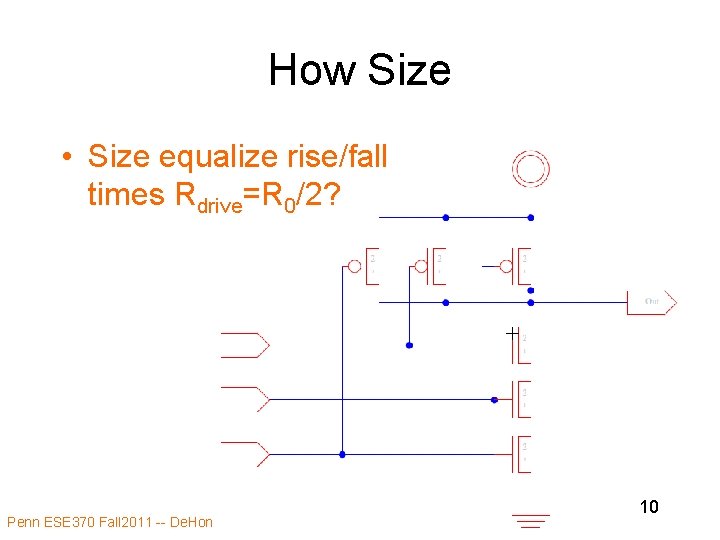

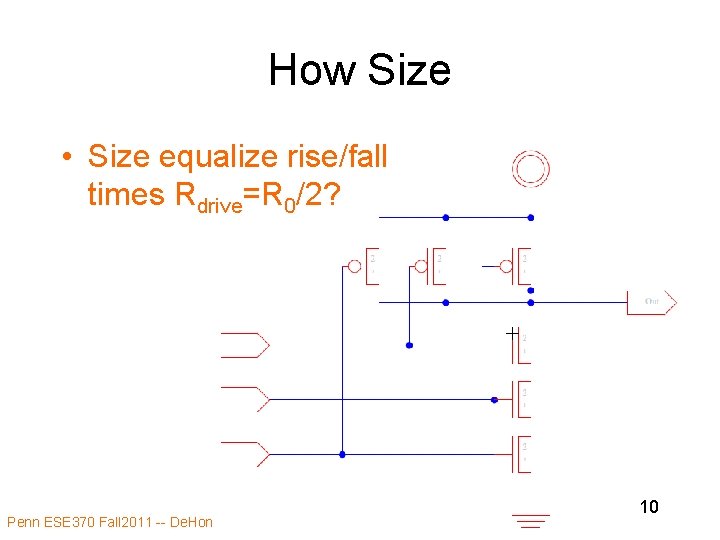

How Size • Size equalize rise/fall times Rdrive=R 0/2? Penn ESE 370 Fall 2011 -- De. Hon 10

Increasing Fanin • What happens to input capacitance as fanin (k) increases – Keeping output drive the same • E. g. Rdrive=R 0/2 • k-input nand gate has what input capacitance? Penn ESE 370 Fall 2011 -- De. Hon 11

Fanin • Conclude: gates slow down with fanin – Less drive per input capacitance Penn ESE 370 Fall 2011 -- De. Hon 12

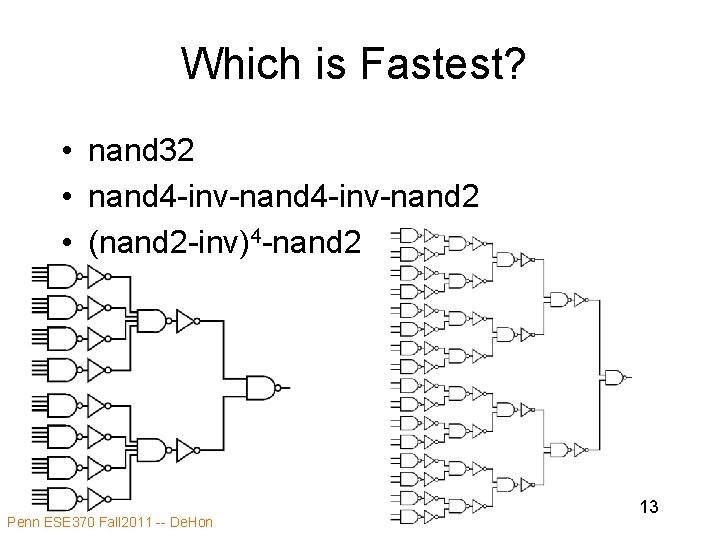

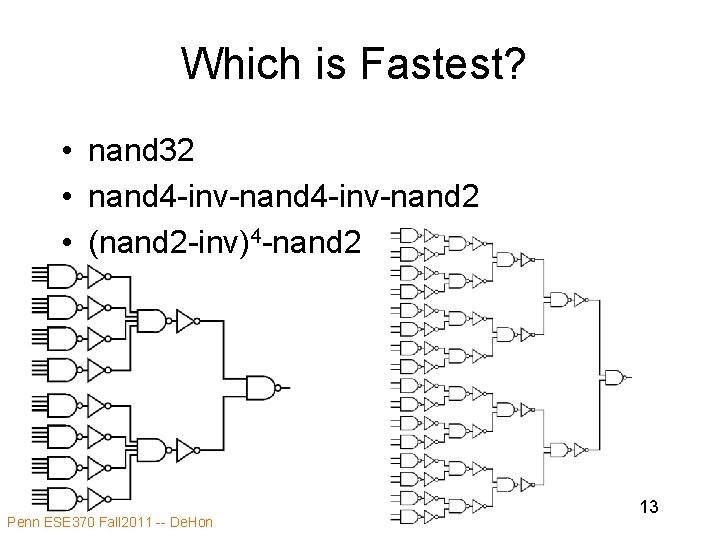

Which is Fastest? • nand 32 • nand 4 -inv-nand 2 • (nand 2 -inv)4 -nand 2 Penn ESE 370 Fall 2011 -- De. Hon 13

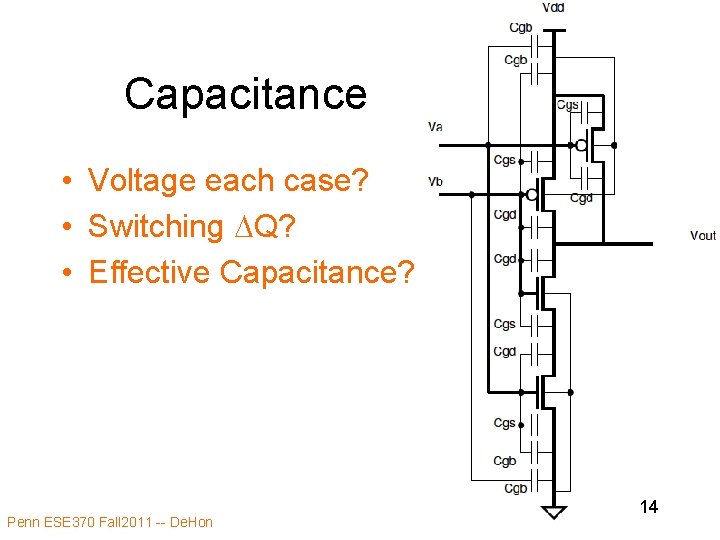

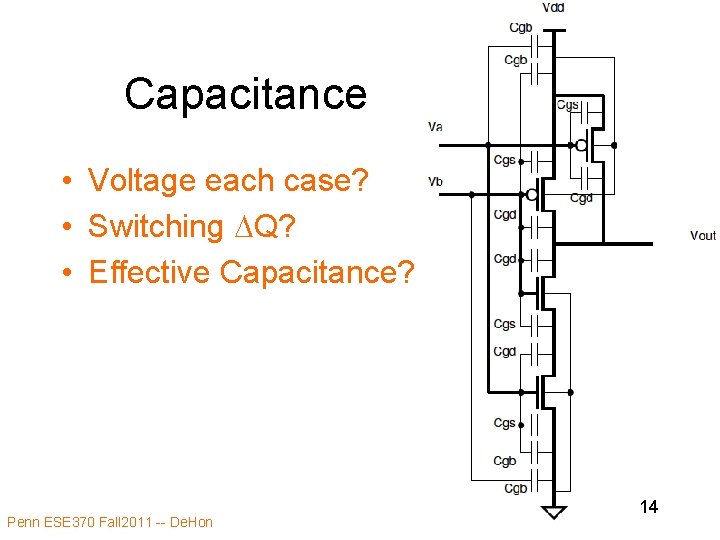

Capacitance • Voltage each case? • Switching DQ? • Effective Capacitance? Penn ESE 370 Fall 2011 -- De. Hon 14

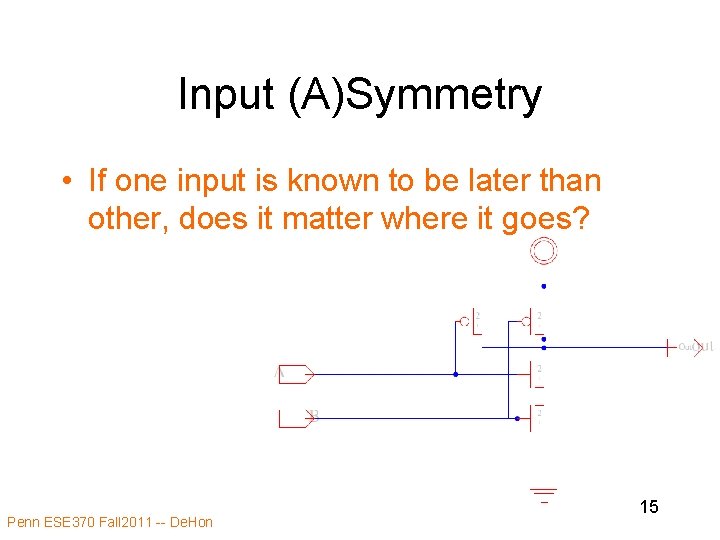

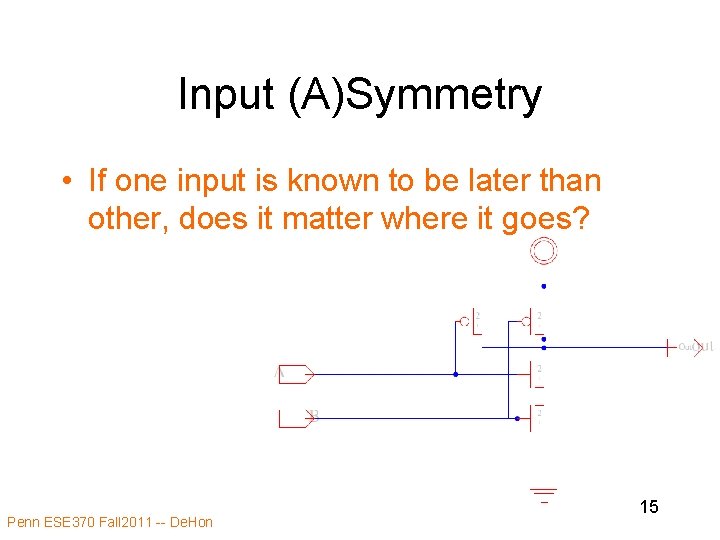

Input (A)Symmetry • If one input is known to be later than other, does it matter where it goes? Penn ESE 370 Fall 2011 -- De. Hon 15

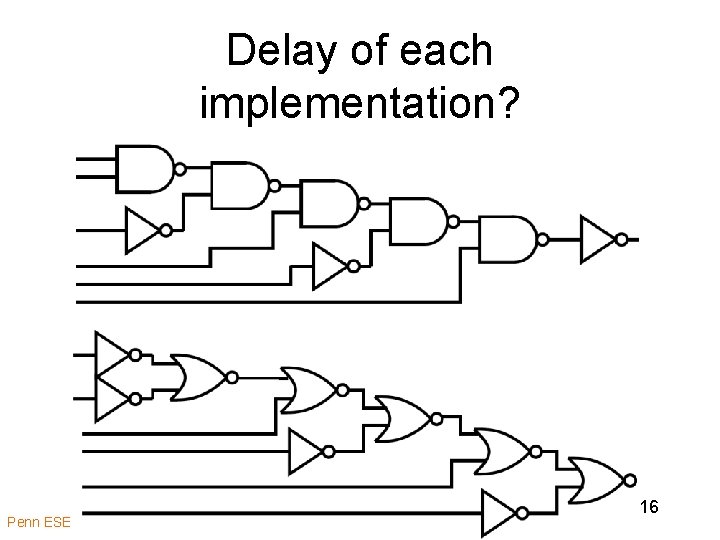

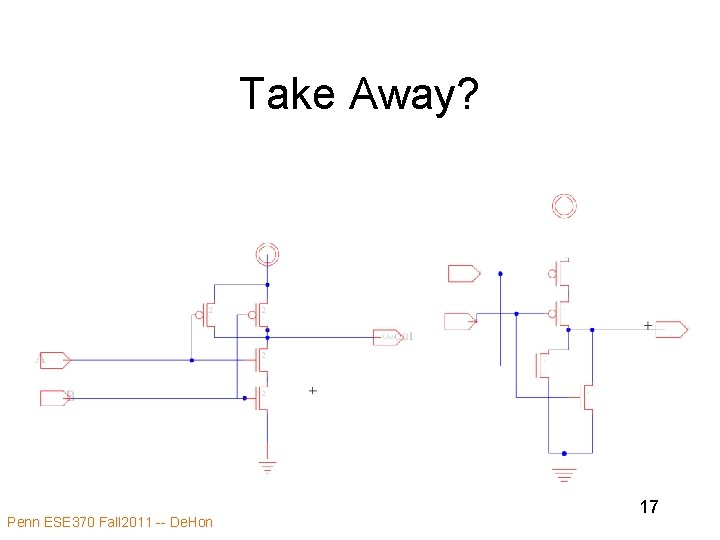

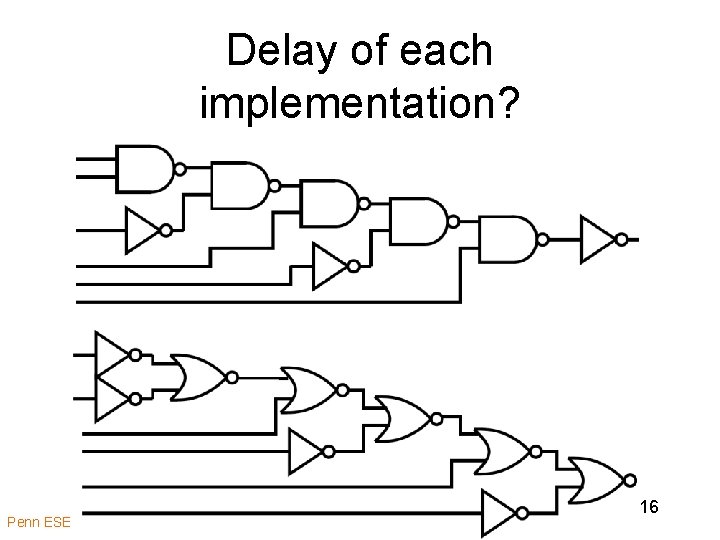

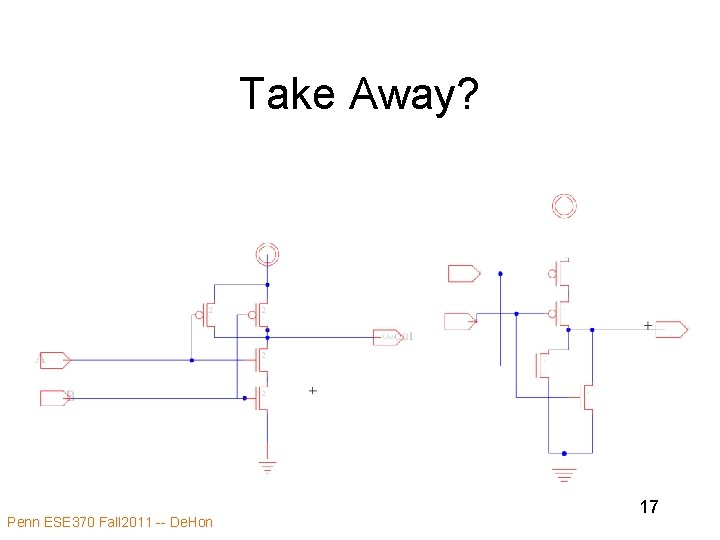

Delay of each implementation? Penn ESE 370 Fall 2011 -- De. Hon 16

Take Away? Penn ESE 370 Fall 2011 -- De. Hon 17

Lesson • Large gates are slow / inefficient – High capacitive load / drive strength • Small gates can be inefficient – Need many stages • Staging over moderate size gates minimizes delay • Exact size will be technology dependent Penn ESE 370 Fall 2011 -- De. Hon 18

Admin • Midterm solutions up • HW 5 – Should be able to compute delays, size gates – Energy next time Penn ESE 370 Fall 2011 -- De. Hon 19

Ideas • First order reason in t=R 0 C 0 units • Gates have different efficiencies – Drive strength per unit input capacitance • With velocity saturation (short term), – nands and nors are similar efficiency • Large fanin and fanout slow gates – Decompose into stages – …but not too much Penn ESE 370 Fall 2011 -- De. Hon 20