ESCI Base Serial Communication TX RX 8 bits

ESCI Base

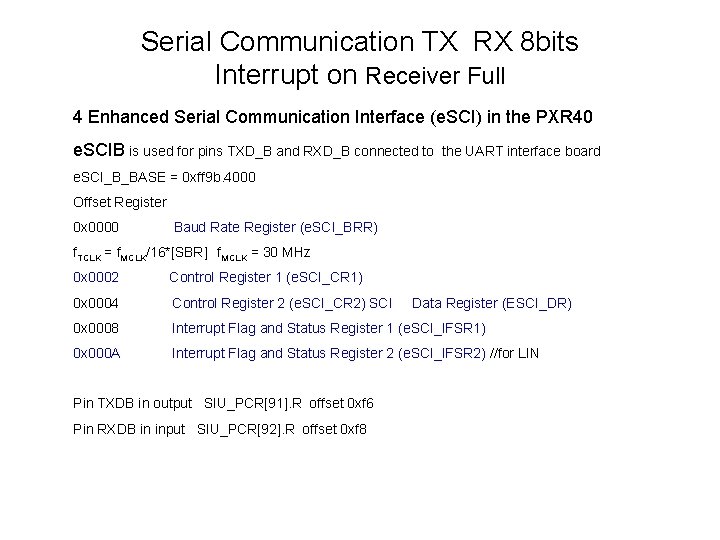

Serial Communication TX RX 8 bits Interrupt on Receiver Full 4 Enhanced Serial Communication Interface (e. SCI) in the PXR 40 e. SCIB is used for pins TXD_B and RXD_B connected to the UART interface board e. SCI_B_BASE = 0 xff 9 b. 4000 Offset Register 0 x 0000 Baud Rate Register (e. SCI_BRR) f. TCLK = f. MCLK/16*[SBR] f. MCLK = 30 MHz 0 x 0002 Control Register 1 (e. SCI_CR 1) 0 x 0004 Control Register 2 (e. SCI_CR 2) SCI 0 x 0008 Interrupt Flag and Status Register 1 (e. SCI_IFSR 1) 0 x 000 A Interrupt Flag and Status Register 2 (e. SCI_IFSR 2) //for LIN Pin TXDB in output SIU_PCR[91]. R offset 0 xf 6 Pin RXDB in input SIU_PCR[92]. R offset 0 xf 8 Data Register (ESCI_DR)

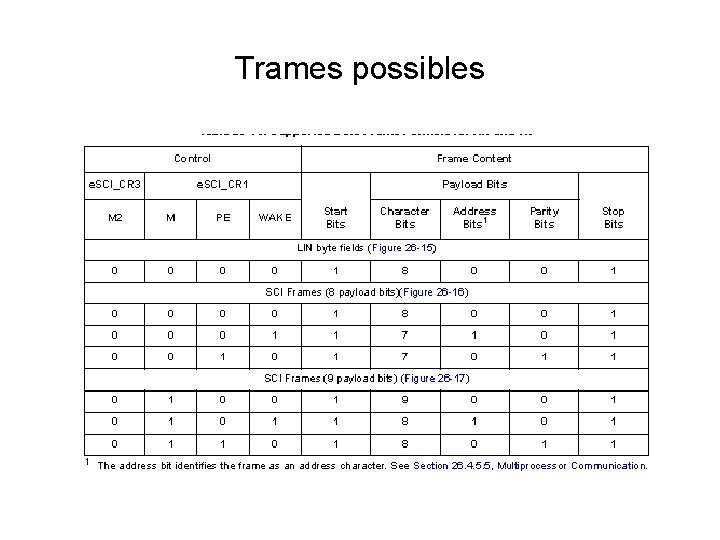

Trames possibles

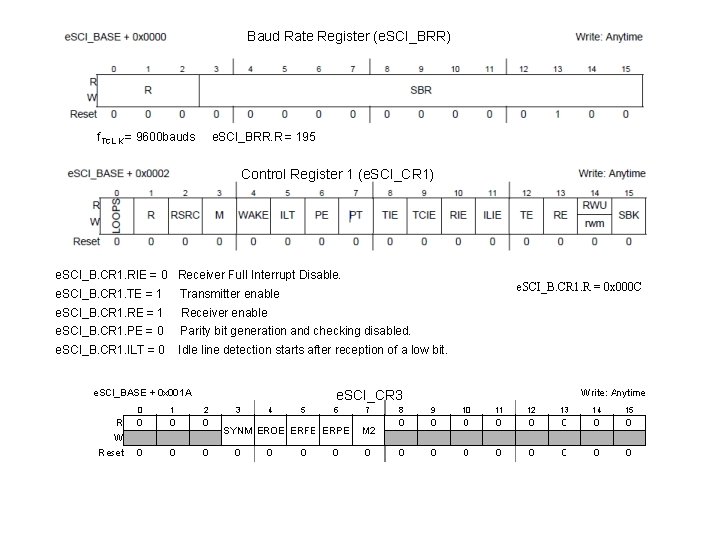

Baud Rate Register (e. SCI_BRR) f. TCL K = 9600 bauds e. SCI_BRR. R = 195 Control Register 1 (e. SCI_CR 1) e. SCI_B. CR 1. RIE = 0 Receiver Full Interrupt Disable. e. SCI_B. CR 1. TE = 1 Transmitter enable e. SCI_B. CR 1. RE = 1 Receiver enable e. SCI_B. CR 1. PE = 0 Parity bit generation and checking disabled. e. SCI_B. CR 1. ILT = 0 Idle line detection starts after reception of a low bit. e. SCI_CR 3 e. SCI_B. CR 1. R = 0 x 000 C

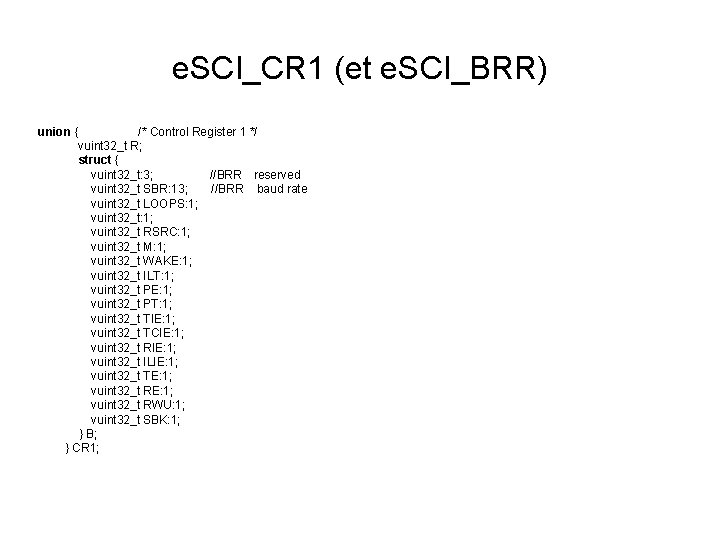

e. SCI_CR 1 (et e. SCI_BRR) union { /* Control Register 1 */ vuint 32_t R; struct { vuint 32_t: 3; //BRR reserved vuint 32_t SBR: 13; //BRR baud rate vuint 32_t LOOPS: 1; vuint 32_t RSRC: 1; vuint 32_t M: 1; vuint 32_t WAKE: 1; vuint 32_t ILT: 1; vuint 32_t PE: 1; vuint 32_t PT: 1; vuint 32_t TIE: 1; vuint 32_t TCIE: 1; vuint 32_t RIE: 1; vuint 32_t ILIE: 1; vuint 32_t TE: 1; vuint 32_t RWU: 1; vuint 32_t SBK: 1; } B; } CR 1;

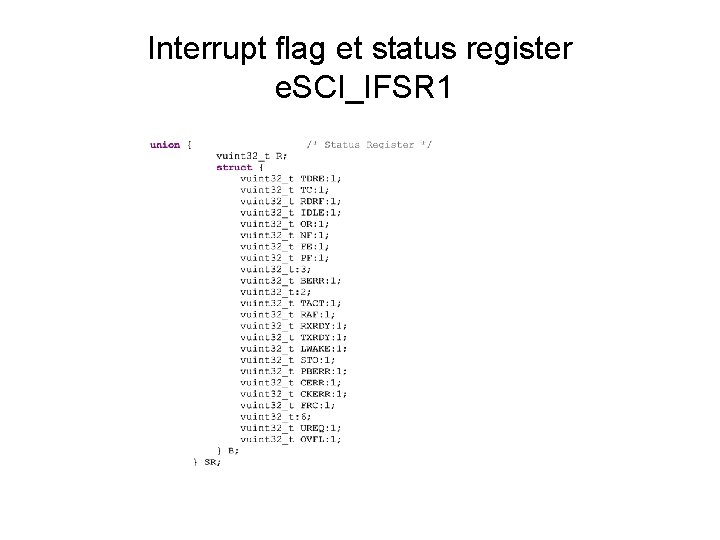

Interrupt flag et status register e. SCI_IFSR 1

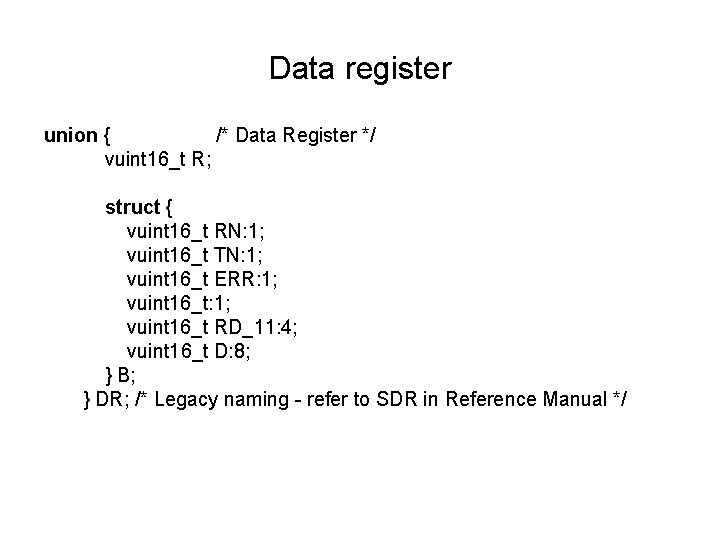

Data register union { /* Data Register */ vuint 16_t R; struct { vuint 16_t RN: 1; vuint 16_t TN: 1; vuint 16_t ERR: 1; vuint 16_t RD_11: 4; vuint 16_t D: 8; } B; } DR; /* Legacy naming - refer to SDR in Reference Manual */

- Slides: 7