Error Detection Correction Hamming code Error DetectionCorrection Errors

- Slides: 14

Error Detection / Correction Hamming code

Error Detection/Correction Errors: • Hard Failure — Permanent defect • Soft Error — Random, non-destructive — No permanent damage to memory Coding: • Coding can be used for - Error detection - Error correcting • Hamming code will be explored

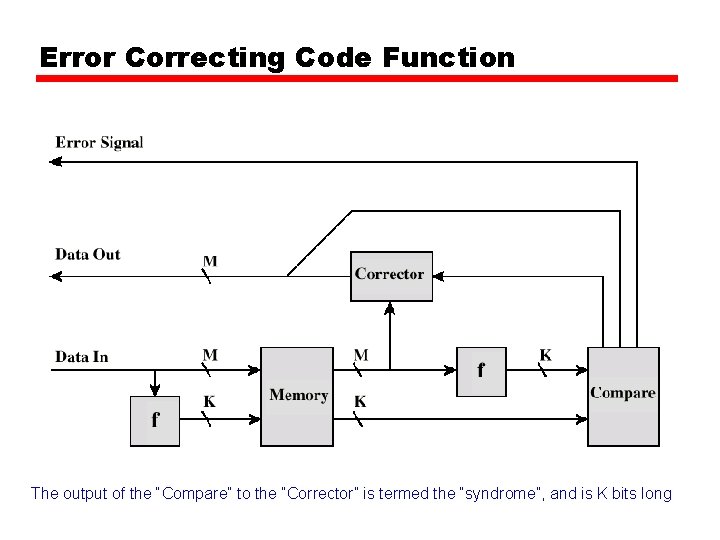

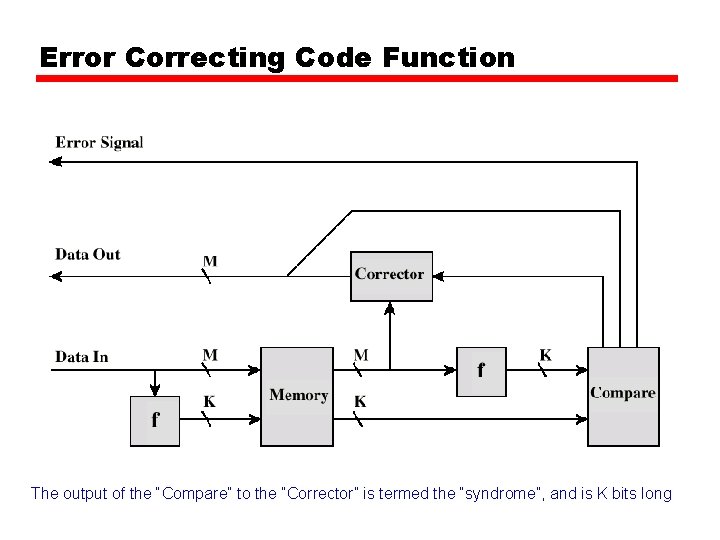

Error Correcting Code Function The output of the “Compare” to the “Corrector” is termed the “syndrome”, and is K bits long

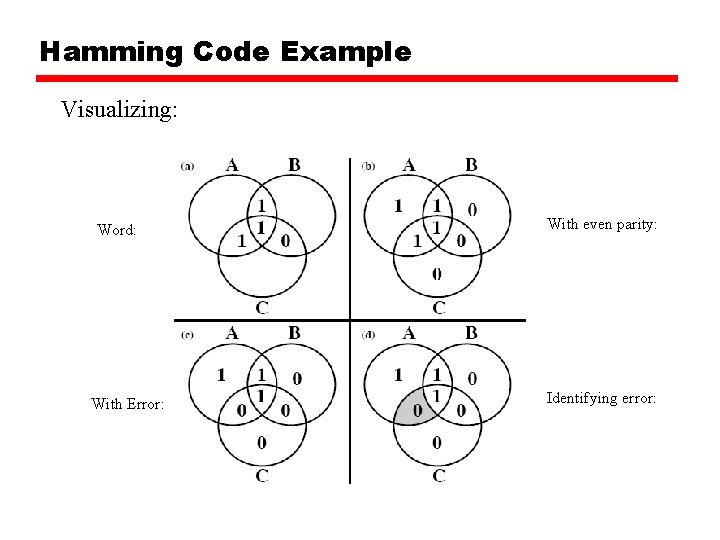

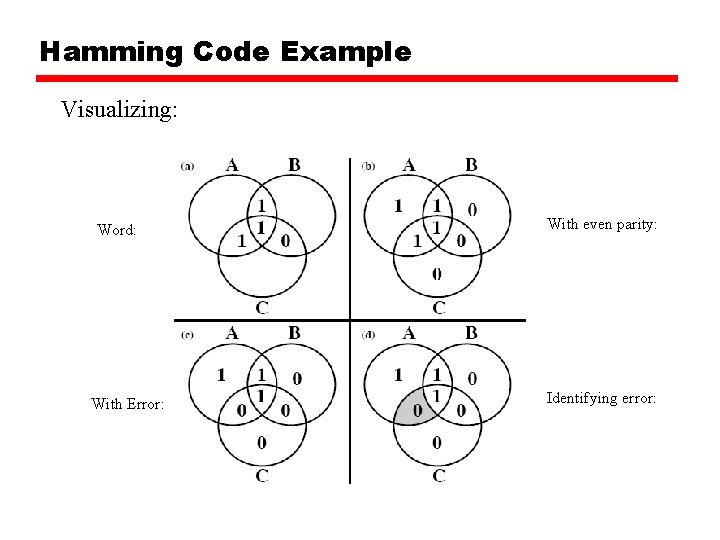

Hamming Code Example Visualizing: Word: With Error: With even parity: Identifying error:

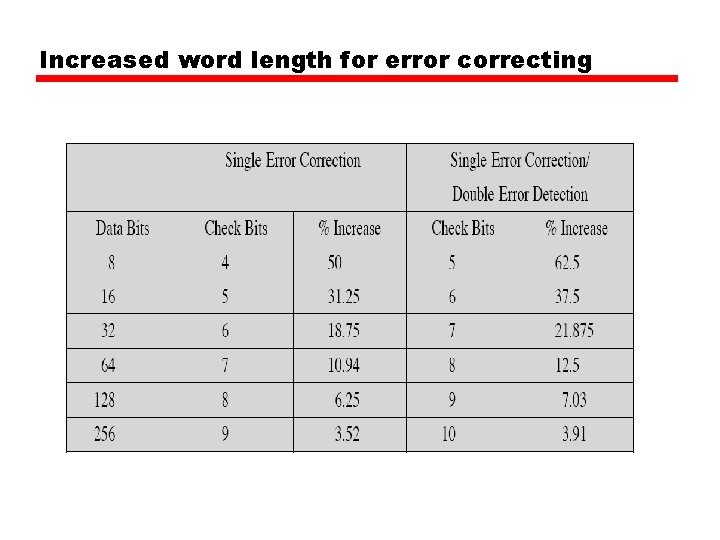

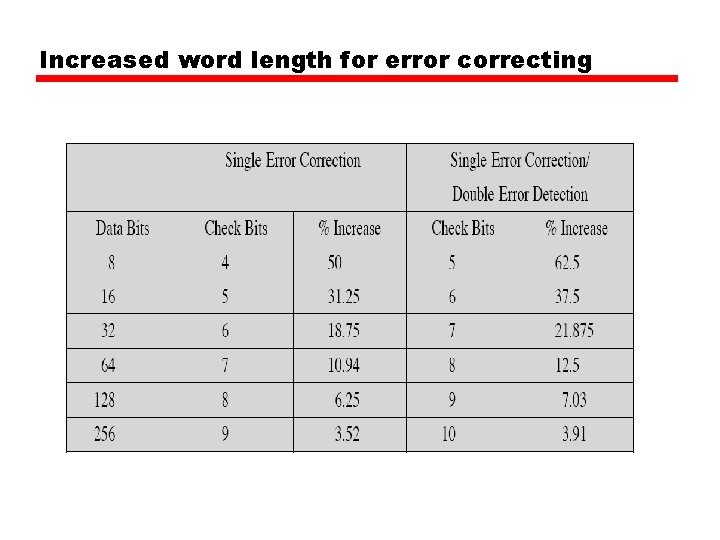

Increased word length for error correcting

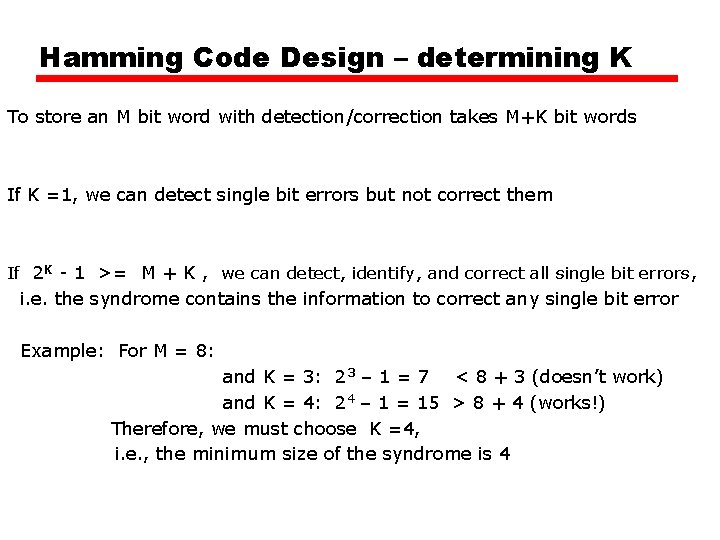

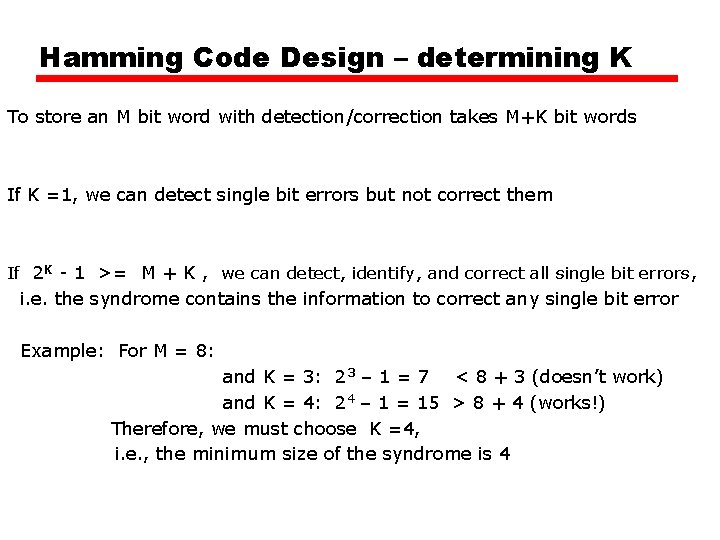

Hamming Code Design – determining K To store an M bit word with detection/correction takes M+K bit words If K =1, we can detect single bit errors but not correct them If 2 K - 1 >= M + K , we can detect, identify, and correct all single bit errors , i. e. the syndrome contains the information to correct any single bit error Example: For M = 8: and K = 3: 23 – 1 = 7 < 8 + 3 (doesn’t work) and K = 4: 24 – 1 = 15 > 8 + 4 (works!) Therefore, we must choose K =4, i. e. , the minimum size of the syndrome is 4

Hamming Code Syndrome If we compare the read K bits compared with the write K bits, using an exclusive or function, the result is called the “syndrome”. If the syndrome is all zeros, there were no errors. If there is a 1 bit somewhere, we know that represents an error.

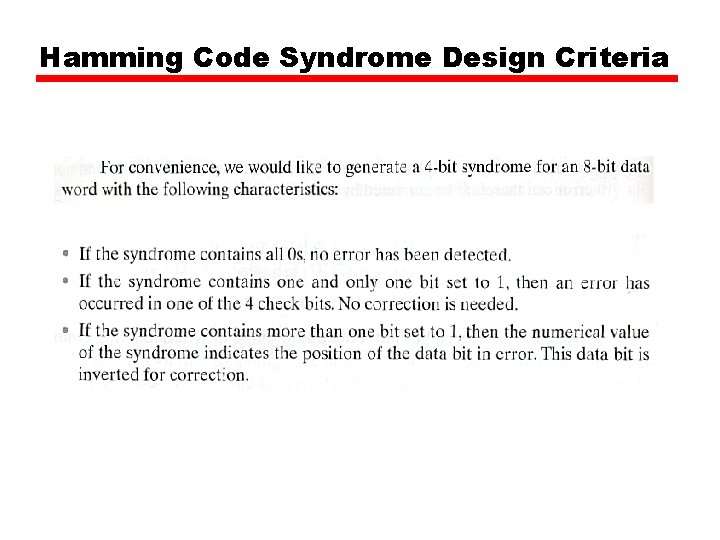

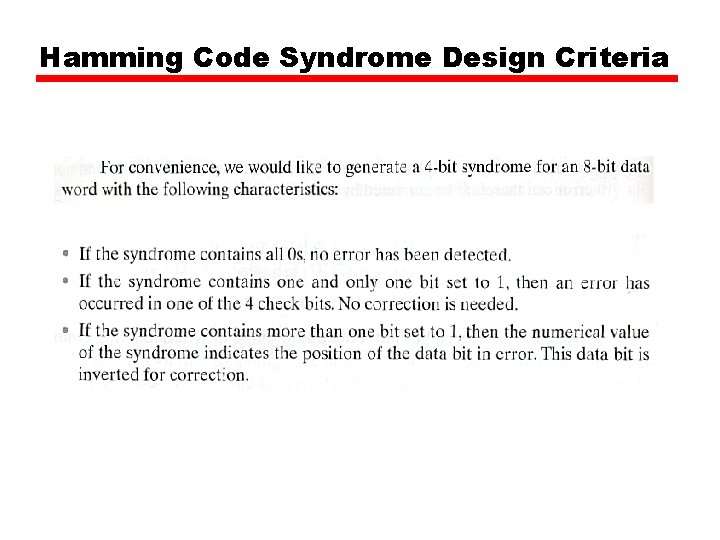

Hamming Code Syndrome Design Criteria

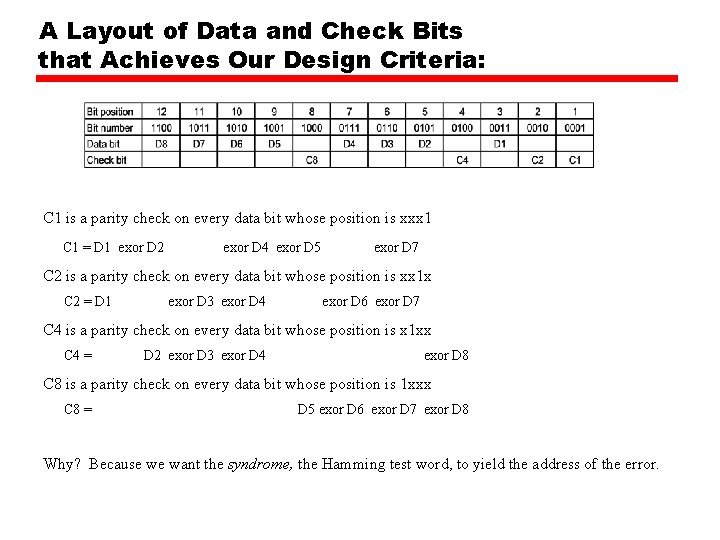

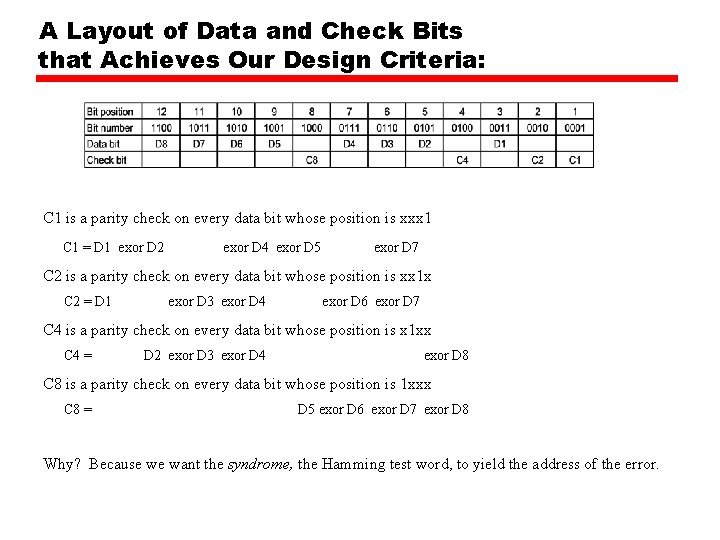

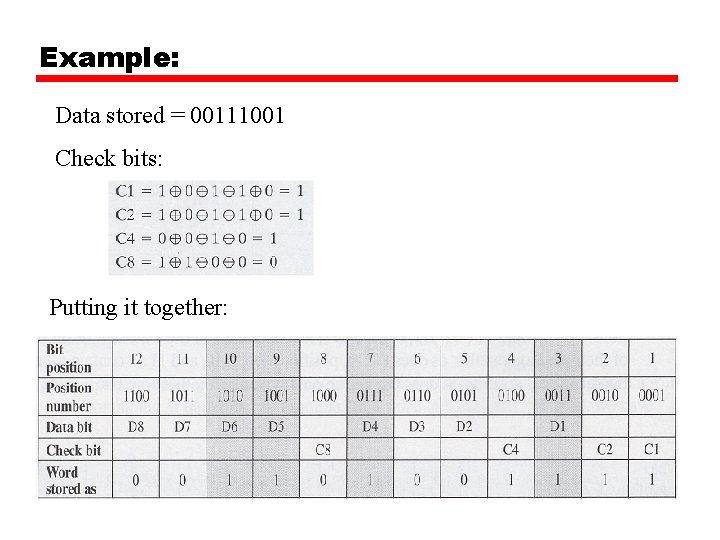

A Layout of Data and Check Bits that Achieves Our Design Criteria: C 1 is a parity check on every data bit whose position is xxx 1 C 1 = D 1 exor D 2 exor D 4 exor D 5 exor D 7 C 2 is a parity check on every data bit whose position is xx 1 x C 2 = D 1 exor D 3 exor D 4 exor D 6 exor D 7 C 4 is a parity check on every data bit whose position is x 1 xx C 4 = D 2 exor D 3 exor D 4 exor D 8 C 8 is a parity check on every data bit whose position is 1 xxx C 8 = D 5 exor D 6 exor D 7 exor D 8 Why? Because we want the syndrome, the Hamming test word, to yield the address of the error.

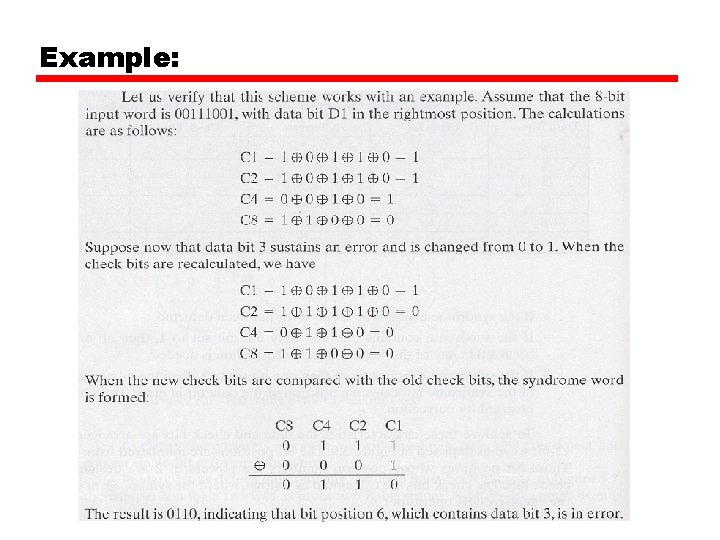

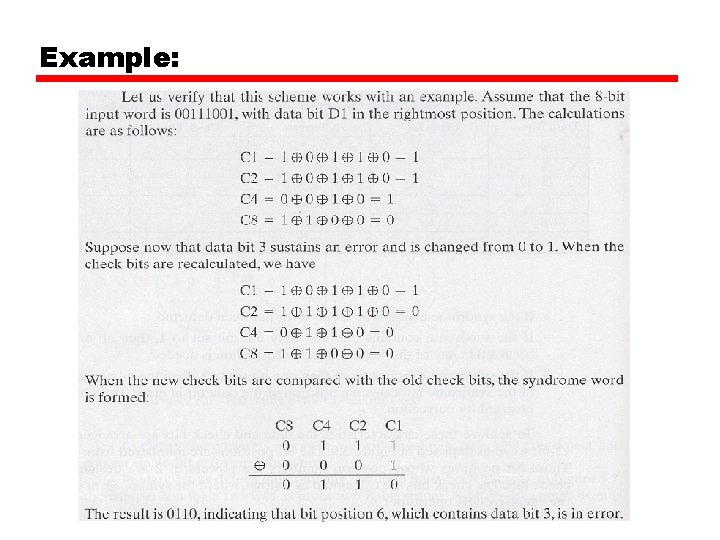

Example:

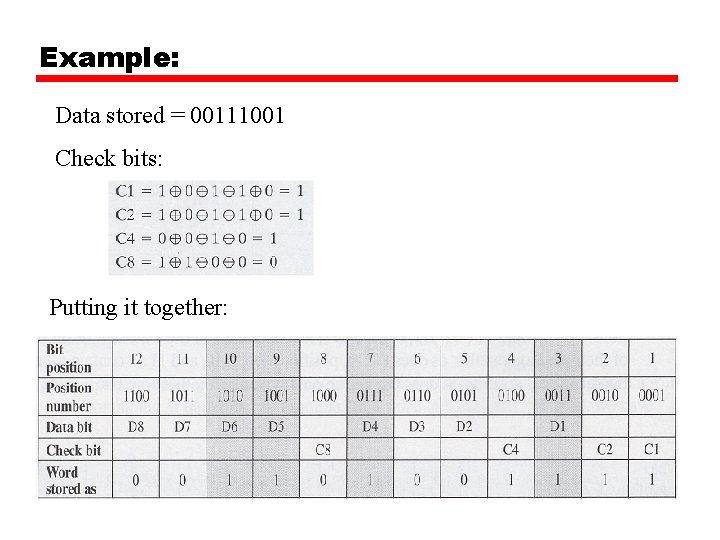

Example: Data stored = 00111001 Check bits: Putting it together:

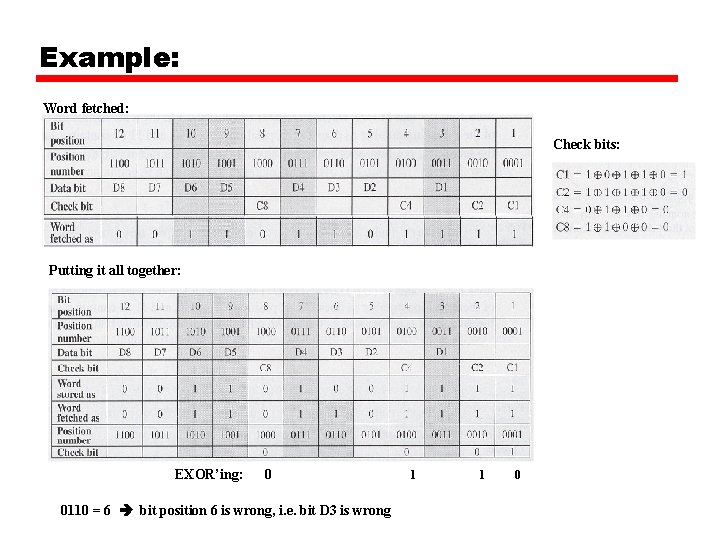

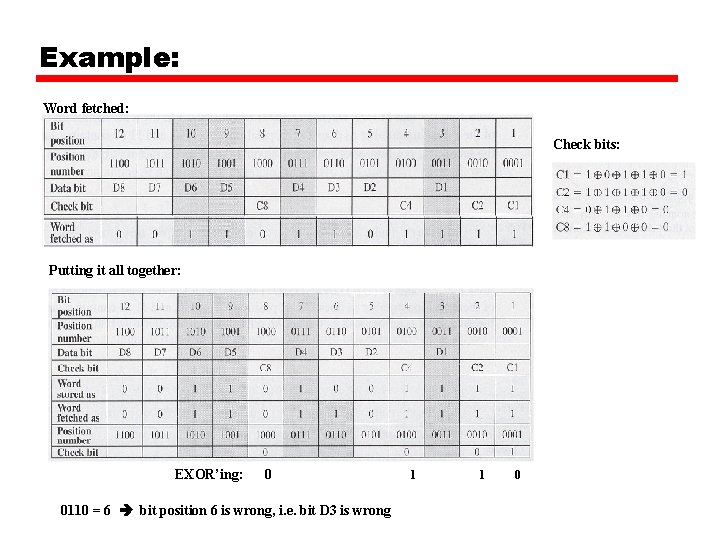

Example: Word fetched: Check bits: Putting it all together: EXOR’ing: 0 0110 = 6 bit position 6 is wrong, i. e. bit D 3 is wrong 1 1 0

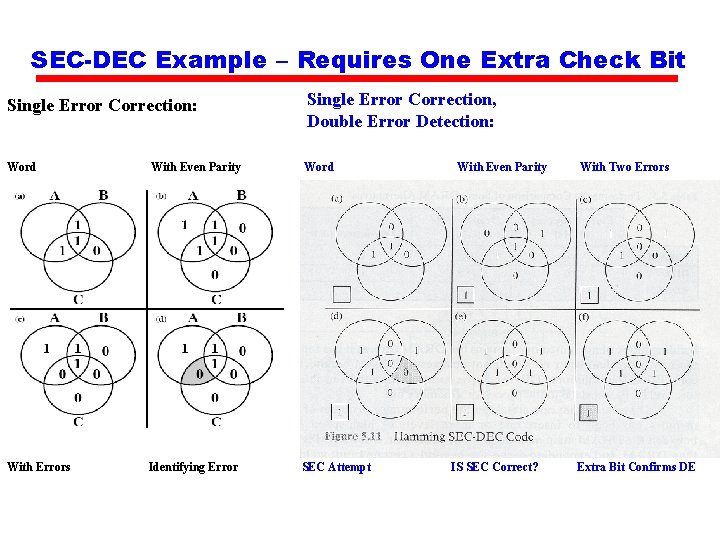

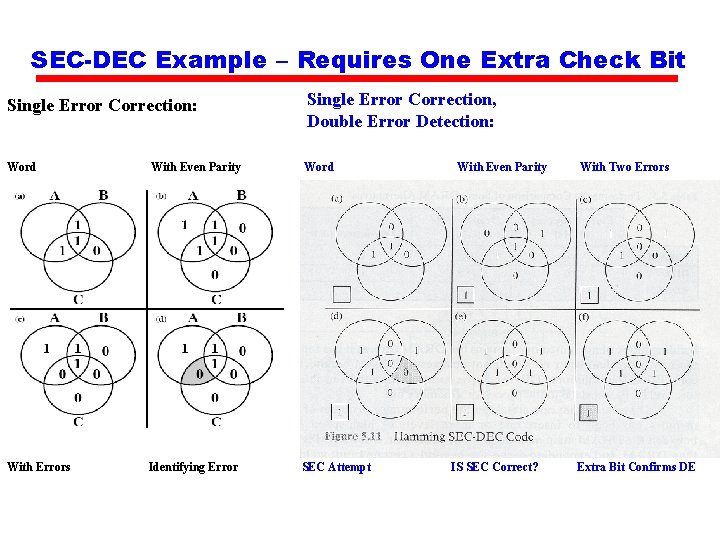

SEC-DEC Example – Requires One Extra Check Bit Single Error Correction: Single Error Correction, Double Error Detection: Word With Even Parity Word With Errors Identifying Error SEC Attempt With Even Parity IS SEC Correct? With Two Errors Extra Bit Confirms DE

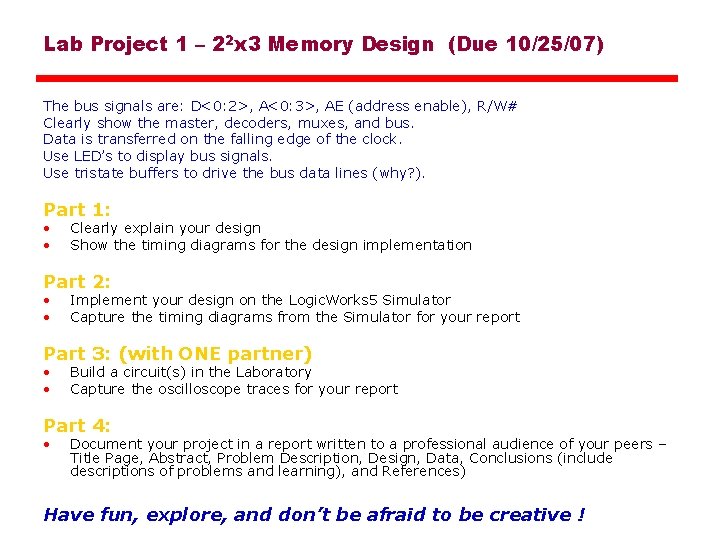

Lab Project 1 – 22 x 3 Memory Design (Due 10/25/07) The bus signals are: D<0: 2>, A<0: 3>, AE (address enable), R/W# Clearly show the master, decoders, muxes, and bus. Data is transferred on the falling edge of the clock. Use LED’s to display bus signals. Use tristate buffers to drive the bus data lines (why? ). Part 1: • • Clearly explain your design Show the timing diagrams for the design implementation Part 2: • • Implement your design on the Logic. Works 5 Simulator Capture the timing diagrams from the Simulator for your report Part 3: (with ONE partner) • • Build a circuit(s) in the Laboratory Capture the oscilloscope traces for your report Part 4: • Document your project in a report written to a professional audience of your peers – Title Page, Abstract, Problem Description, Design, Data, Conclusions (include descriptions of problems and learning), and References) Have fun, explore, and don’t be afraid to be creative !