Erik Jonsson School of Engineering Computer Science HighSpeed

- Slides: 36

Erik Jonsson School of Engineering & Computer Science High-Speed, High-Resolution, Radiation-Tolerant SAR ADC for Particle Physics Experiments Yuan Zhou 1, Hongda Xu 1, Yun Chiu 1 Datao Gong 2, Tiankuan Liu 2, Jingbo Ye 2 1 University of Texas at Dallas, Richardson, TX, USA 2 Southern Methodist University, Dallas, TX, USA

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 -2 - 2014 -09 -24

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 -3 - 2014 -09 -24

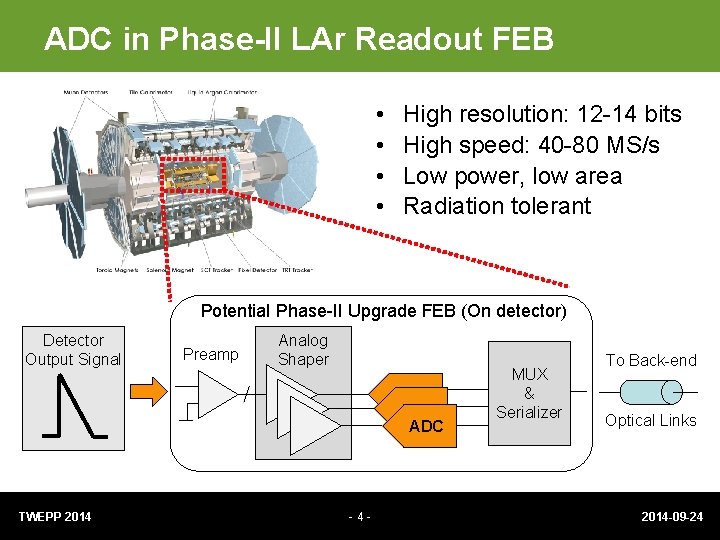

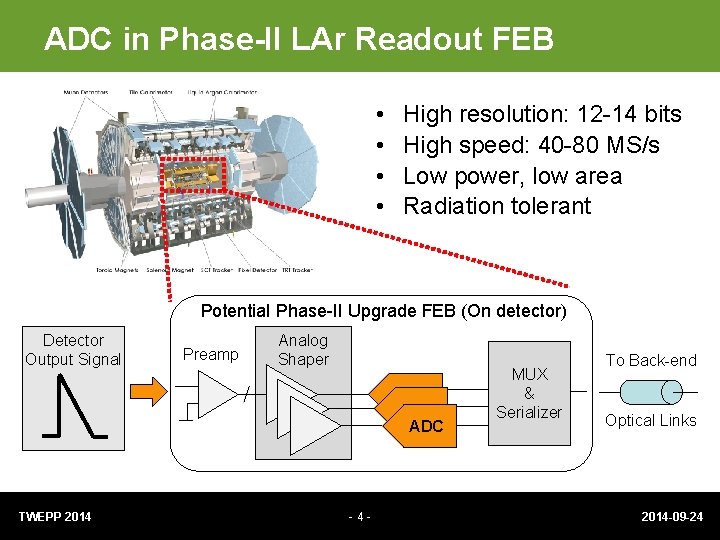

ADC in Phase-II LAr Readout FEB • • High resolution: 12 -14 bits High speed: 40 -80 MS/s Low power, low area Radiation tolerant Potential Phase-II Upgrade FEB (On detector) Detector Output Signal Preamp Analog Shaper ADC TWEPP 2014 -4 - MUX & Serializer To Back-end Optical Links 2014 -09 -24

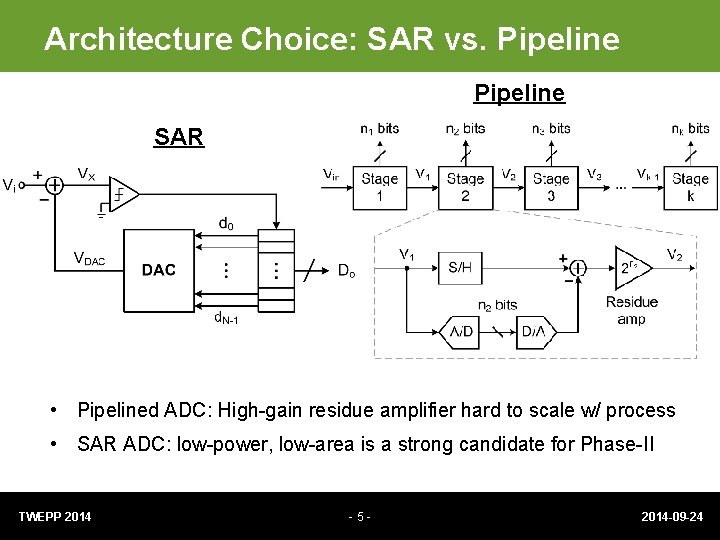

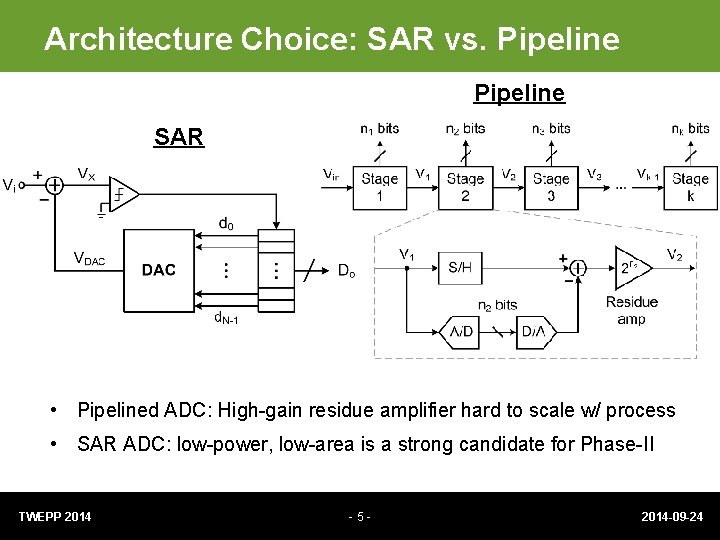

Architecture Choice: SAR vs. Pipeline SAR • Pipelined ADC: High-gain residue amplifier hard to scale w/ process • SAR ADC: low-power, low-area is a strong candidate for Phase-II TWEPP 2014 -5 - 2014 -09 -24

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 -6 - 2014 -09 -24

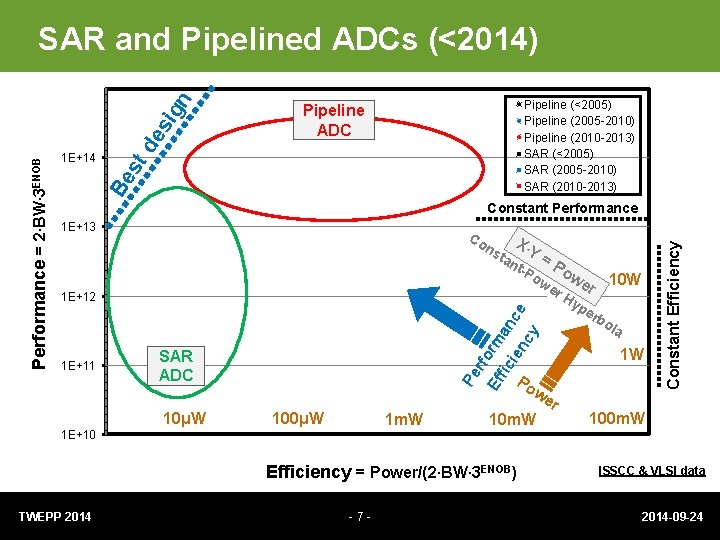

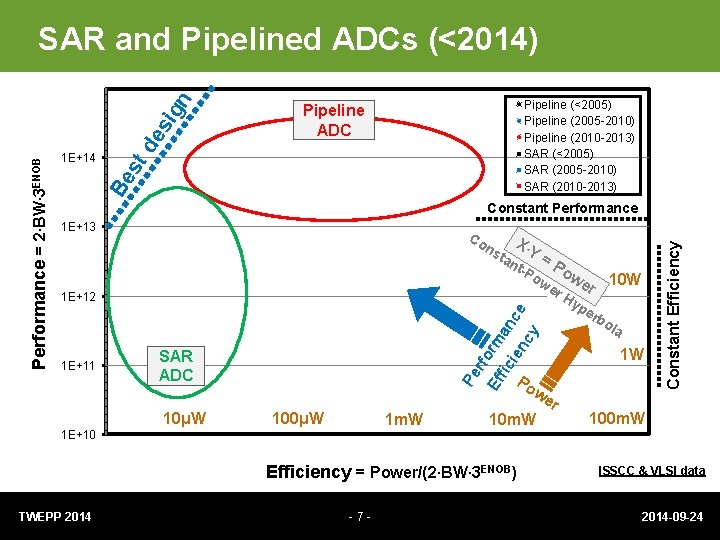

TWEPP 2014 -7 - 2014 -09 -24

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 -8 - 2014 -09 -24

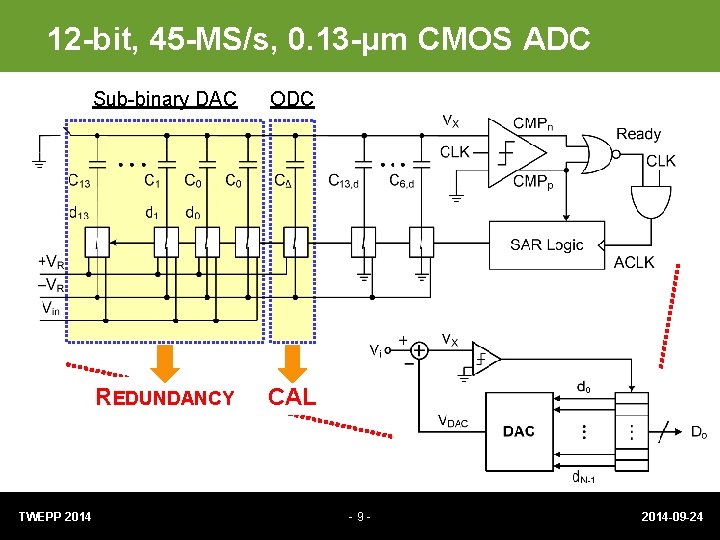

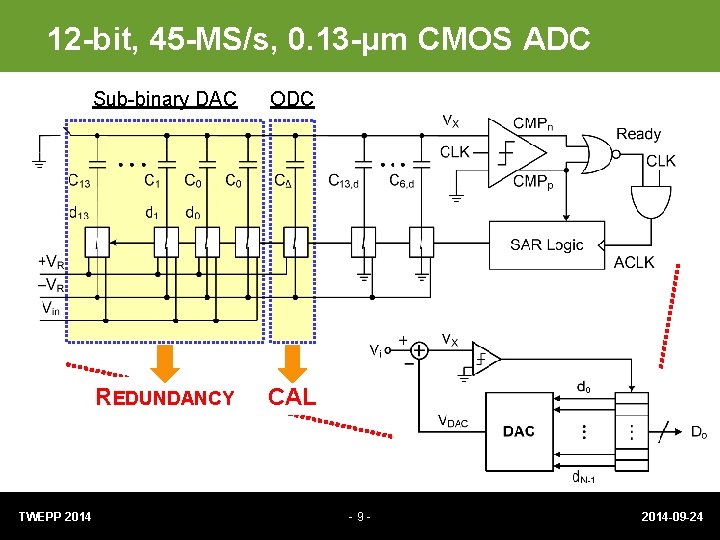

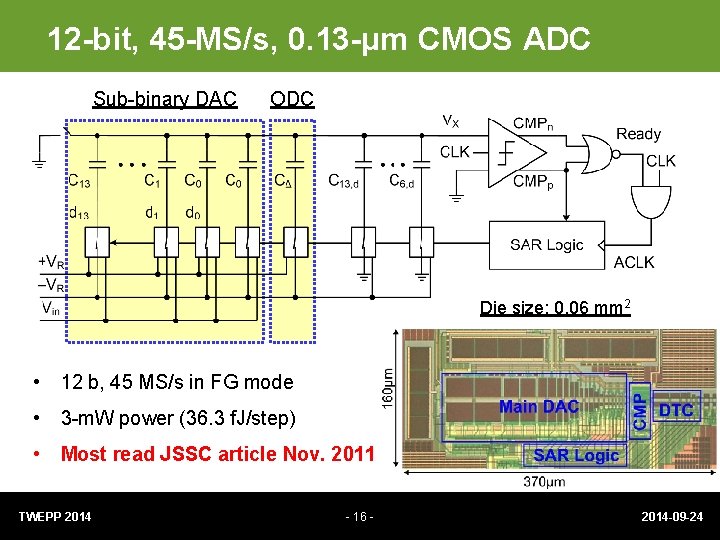

12 -bit, 45 -MS/s, 0. 13 -μm CMOS ADC TWEPP 2014 Sub-binary DAC ODC REDUNDANCY CAL -9 - 2014 -09 -24

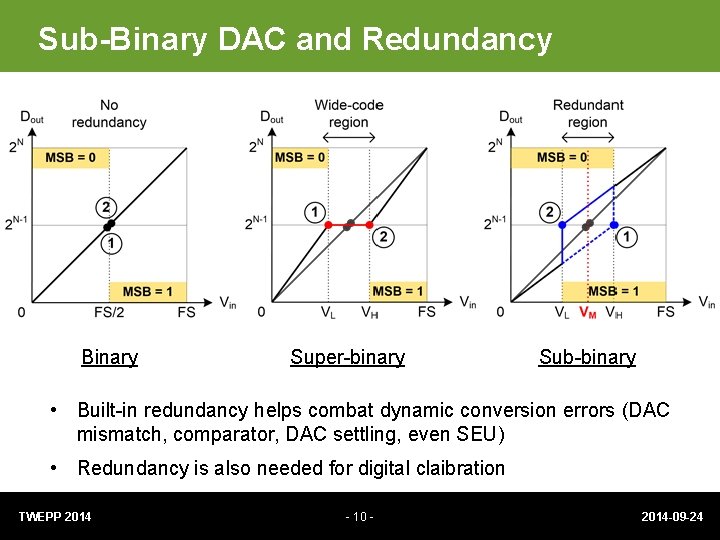

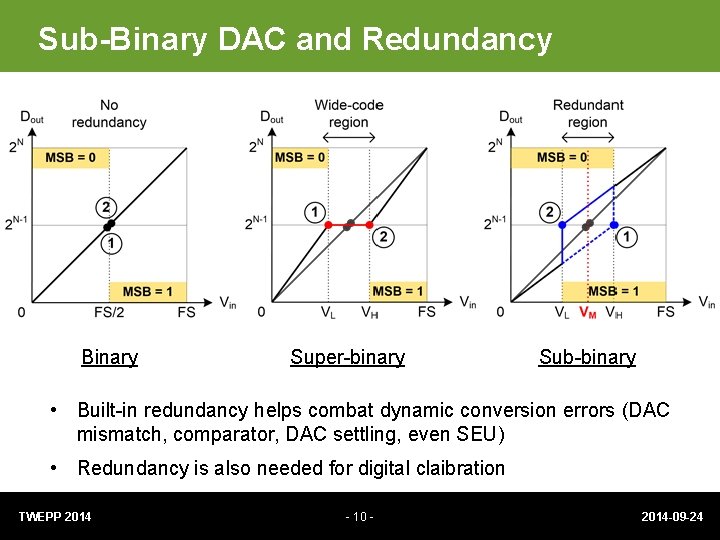

Sub-Binary DAC and Redundancy Binary Super-binary Sub-binary • Built-in redundancy helps combat dynamic conversion errors (DAC mismatch, comparator, DAC settling, even SEU) • Redundancy is also needed for digital claibration TWEPP 2014 - 10 - 2014 -09 -24

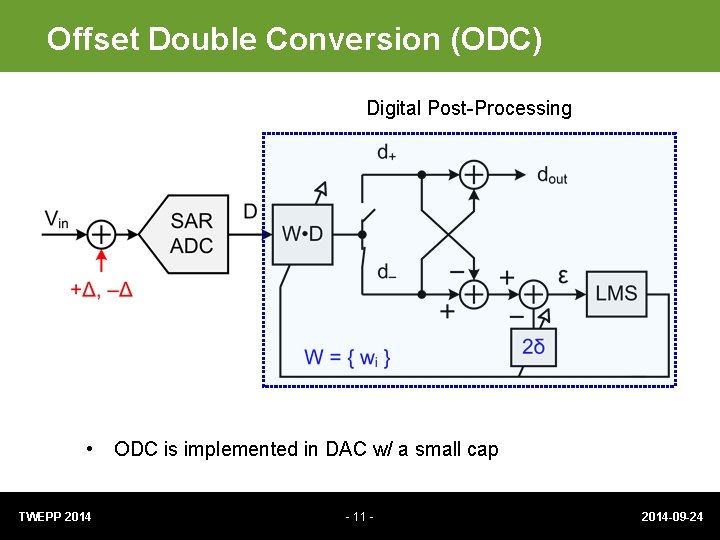

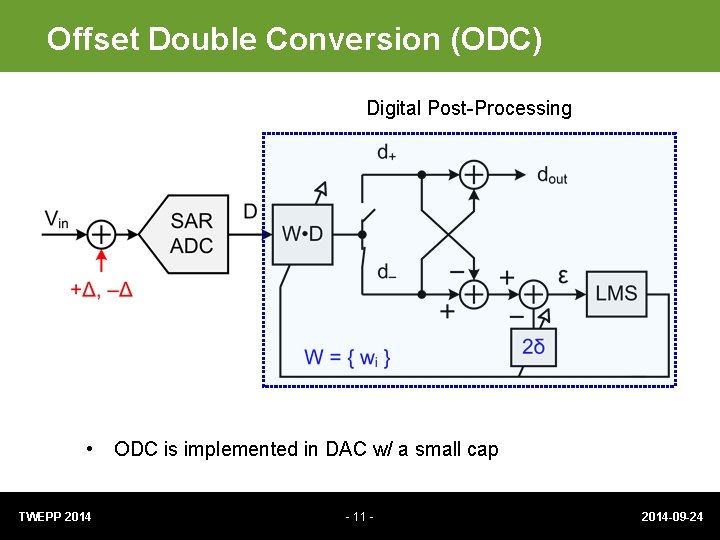

Offset Double Conversion (ODC) Digital Post-Processing • ODC is implemented in DAC w/ a small cap TWEPP 2014 - 11 - 2014 -09 -24

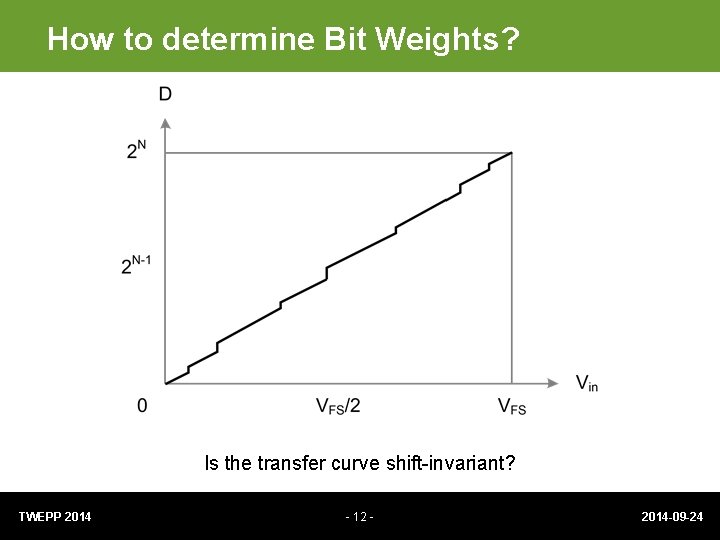

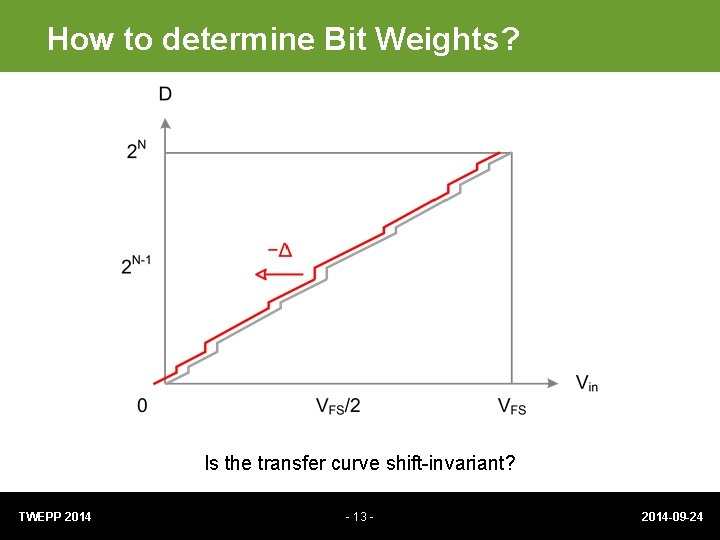

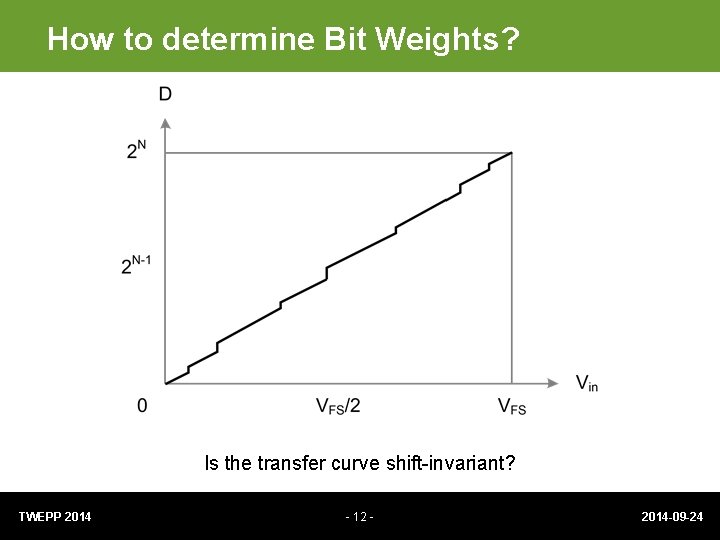

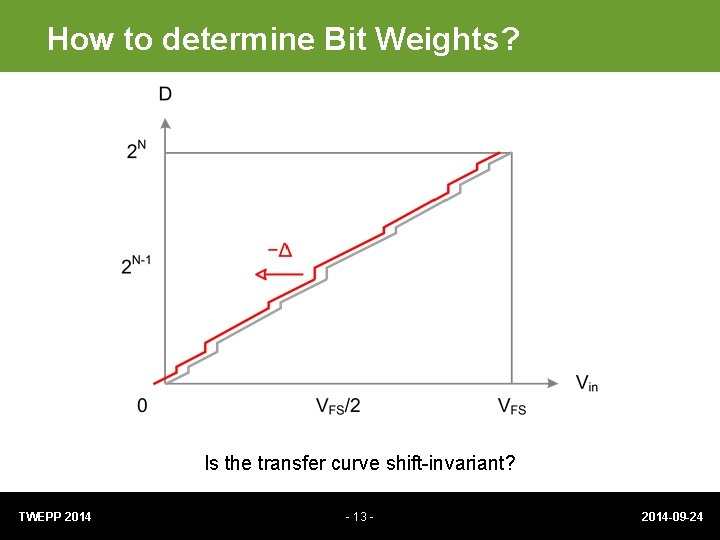

How to determine Bit Weights? Is the transfer curve shift-invariant? TWEPP 2014 - 12 - 2014 -09 -24

How to determine Bit Weights? Is the transfer curve shift-invariant? TWEPP 2014 - 13 - 2014 -09 -24

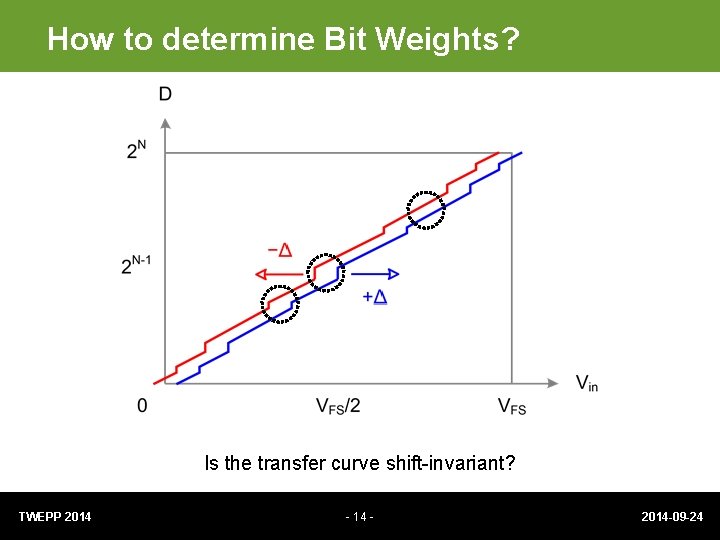

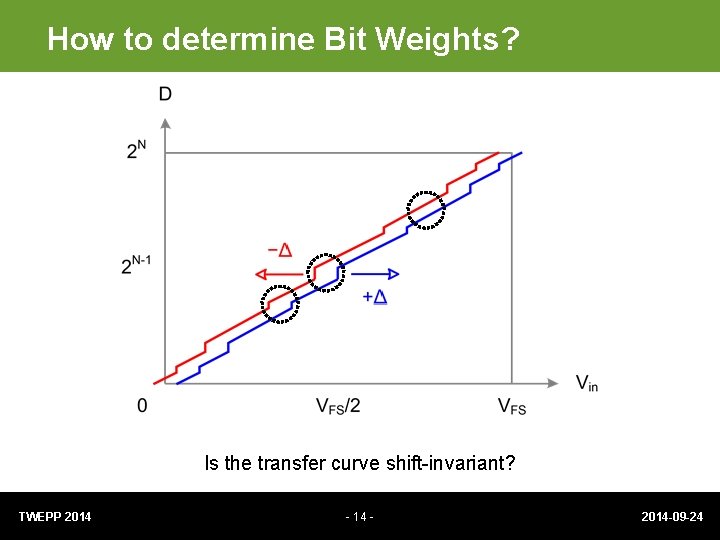

How to determine Bit Weights? Is the transfer curve shift-invariant? TWEPP 2014 - 2014 -09 -24

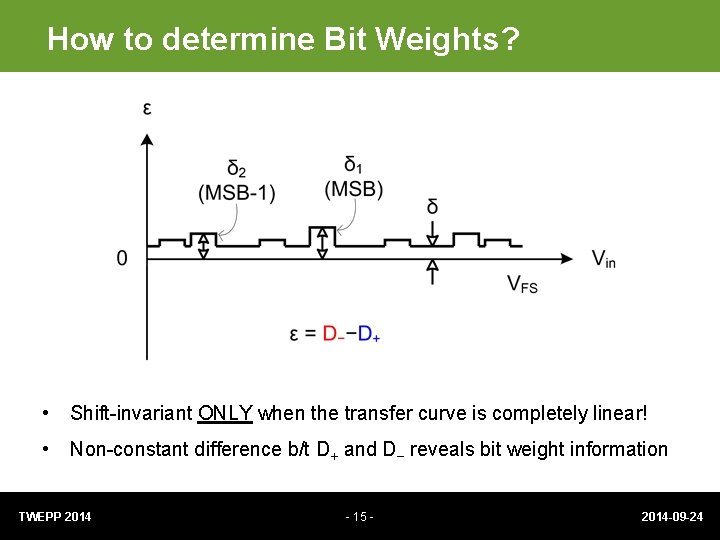

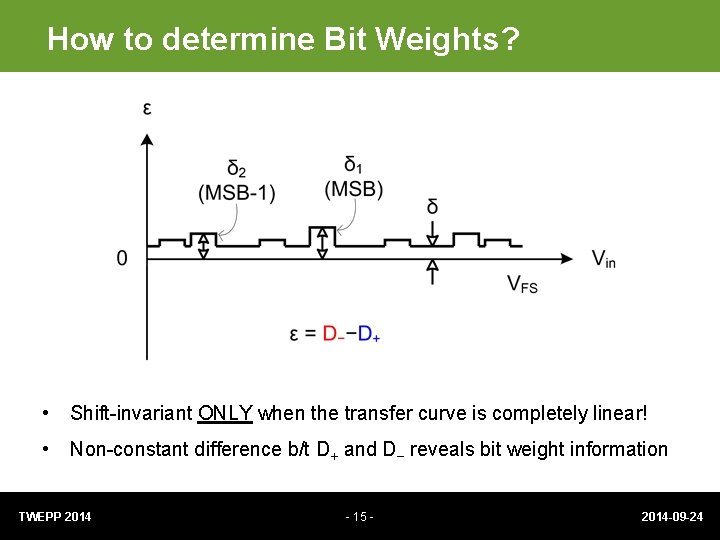

How to determine Bit Weights? • Shift-invariant ONLY when the transfer curve is completely linear! • Non-constant difference b/t D+ and D− reveals bit weight information TWEPP 2014 - 15 - 2014 -09 -24

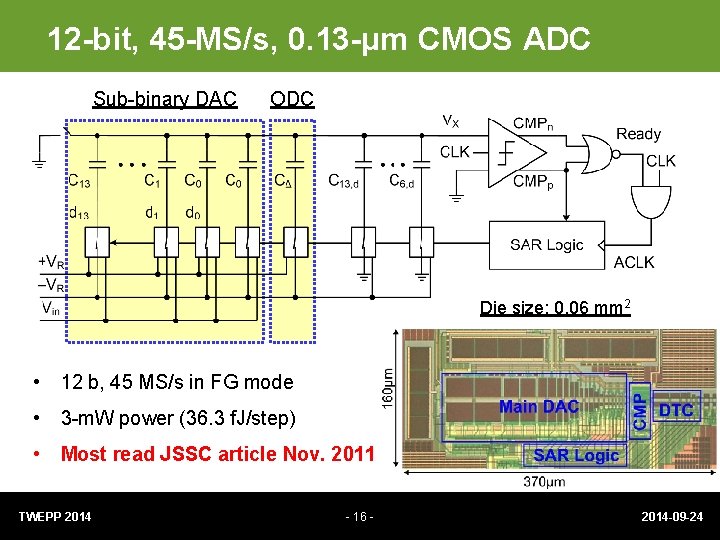

12 -bit, 45 -MS/s, 0. 13 -μm CMOS ADC Sub-binary DAC ODC Die size: 0. 06 mm 2 • 12 b, 45 MS/s in FG mode • 3 -m. W power (36. 3 f. J/step) • Most read JSSC article Nov. 2011 TWEPP 2014 - 16 - 2014 -09 -24

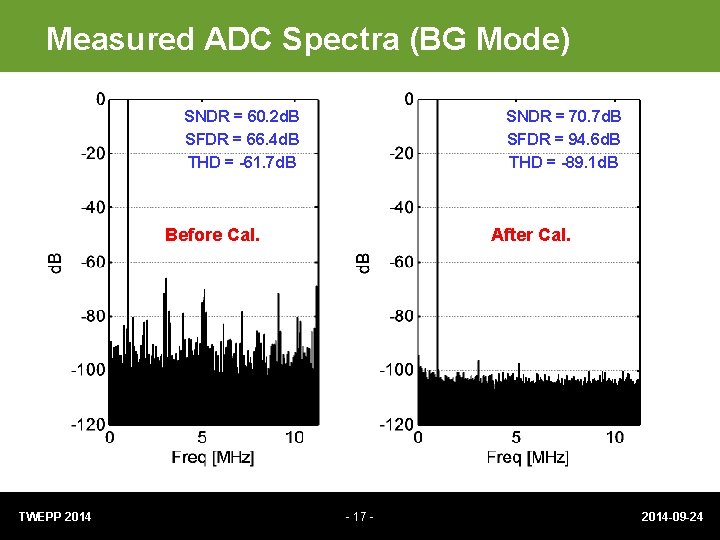

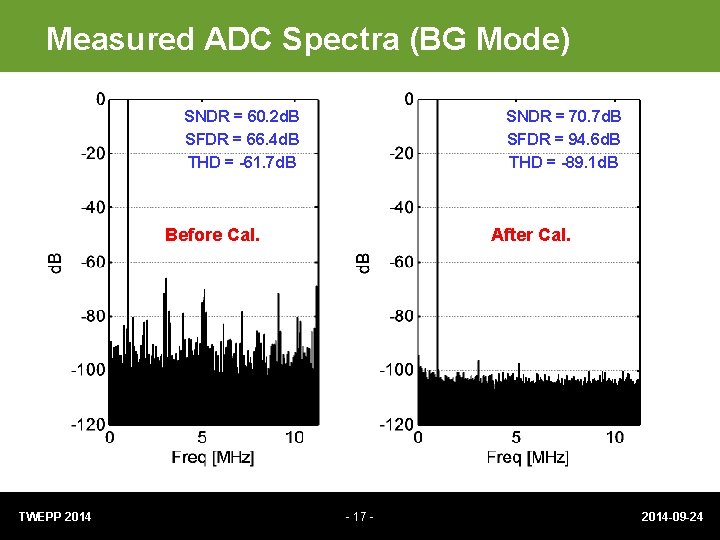

Measured ADC Spectra (BG Mode) SNDR = 60. 2 d. B SFDR = 66. 4 d. B THD = -61. 7 d. B SNDR = 70. 7 d. B SFDR = 94. 6 d. B THD = -89. 1 d. B After Cal. Before Cal. TWEPP 2014 - 17 - 2014 -09 -24

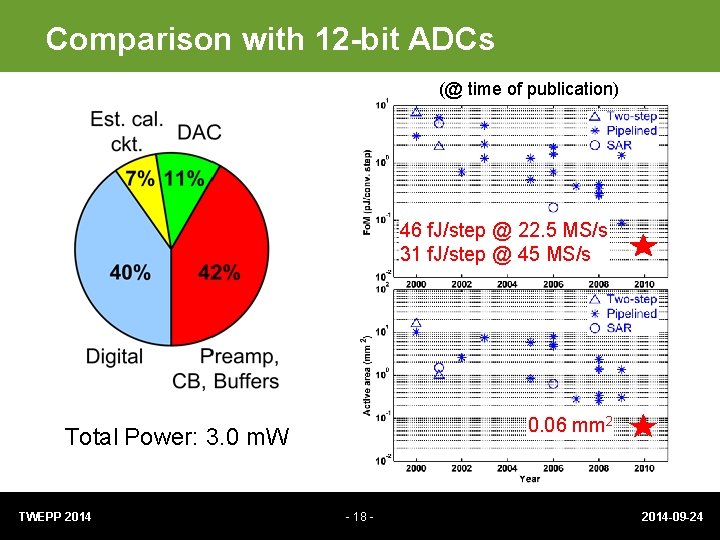

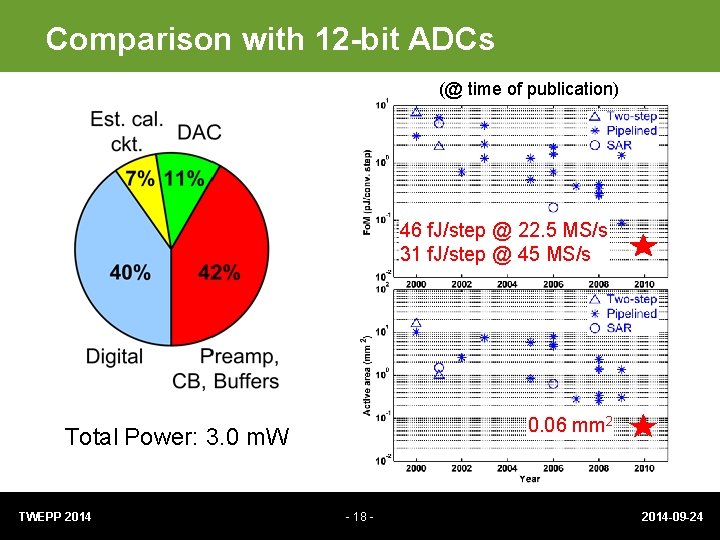

Comparison with 12 -bit ADCs (@ time of publication) 46 f. J/step @ 22. 5 MS/s 31 f. J/step @ 45 MS/s 0. 06 mm 2 Total Power: 3. 0 m. W TWEPP 2014 - 18 - 2014 -09 -24

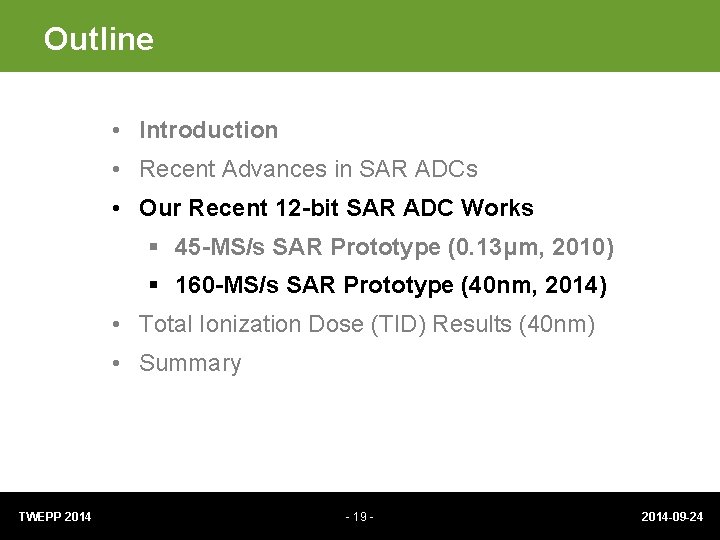

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 - 19 - 2014 -09 -24

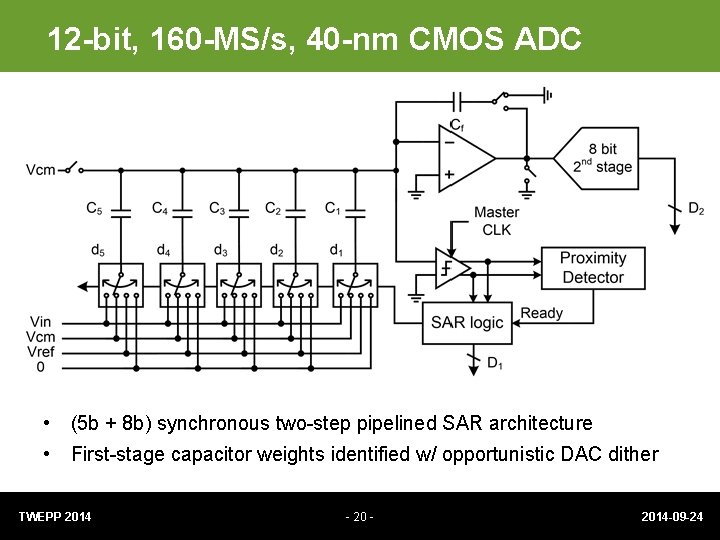

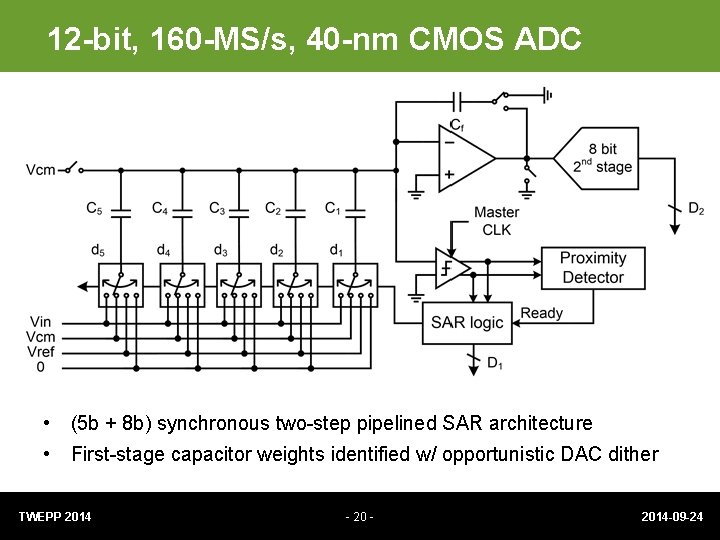

12 -bit, 160 -MS/s, 40 -nm CMOS ADC • (5 b + 8 b) synchronous two-step pipelined SAR architecture • First-stage capacitor weights identified w/ opportunistic DAC dither TWEPP 2014 - 2014 -09 -24

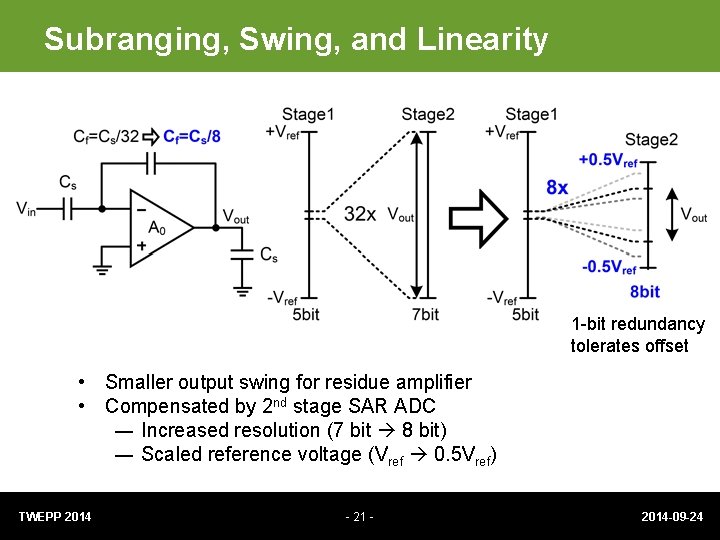

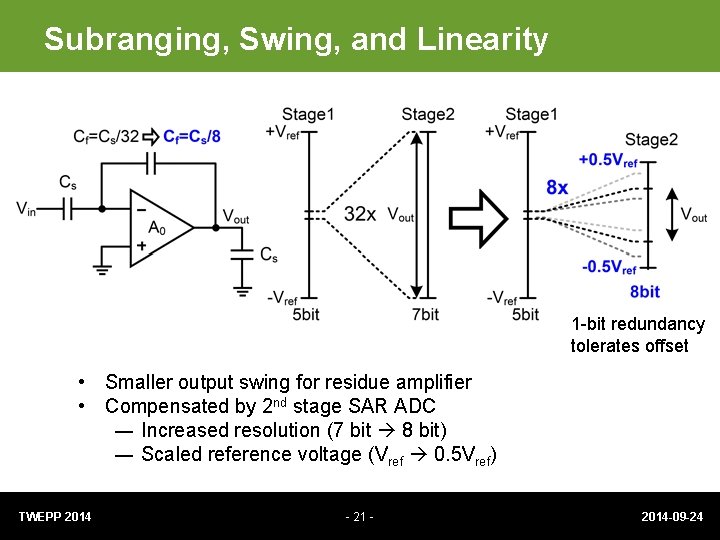

Subranging, Swing, and Linearity 1 -bit redundancy tolerates offset • Smaller output swing for residue amplifier • Compensated by 2 nd stage SAR ADC ― Increased resolution (7 bit 8 bit) ― Scaled reference voltage (Vref 0. 5 Vref) TWEPP 2014 - 21 - 2014 -09 -24

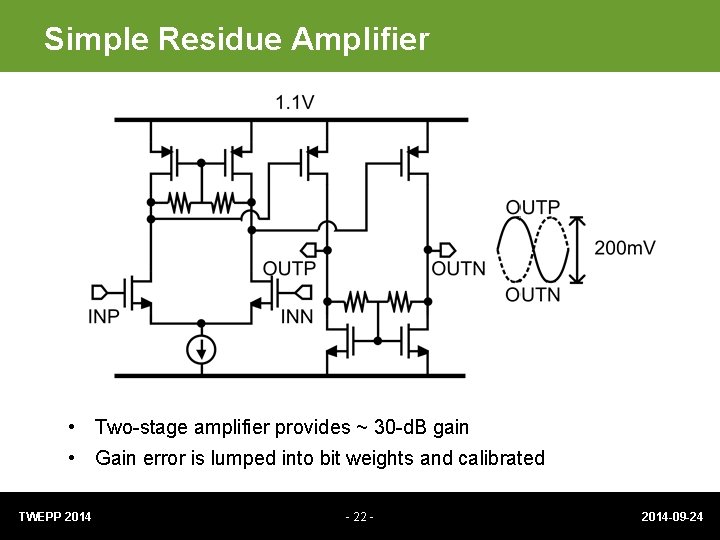

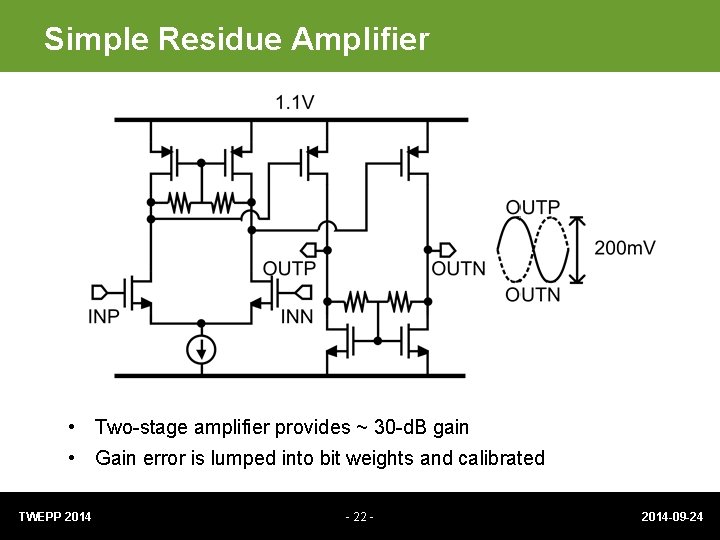

Simple Residue Amplifier • Two-stage amplifier provides ~ 30 -d. B gain • Gain error is lumped into bit weights and calibrated TWEPP 2014 - 22 - 2014 -09 -24

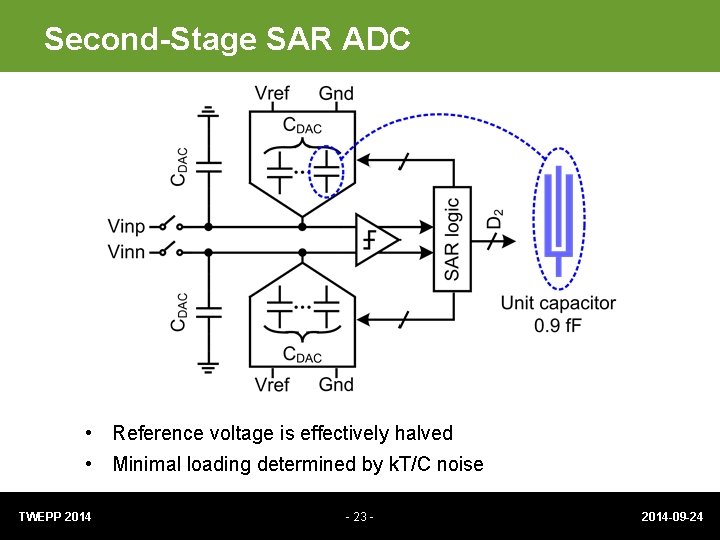

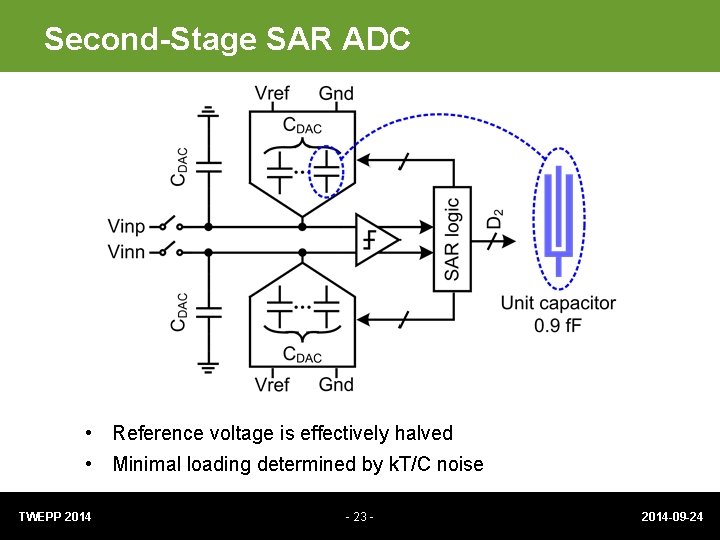

Second-Stage SAR ADC • Reference voltage is effectively halved • Minimal loading determined by k. T/C noise TWEPP 2014 - 23 - 2014 -09 -24

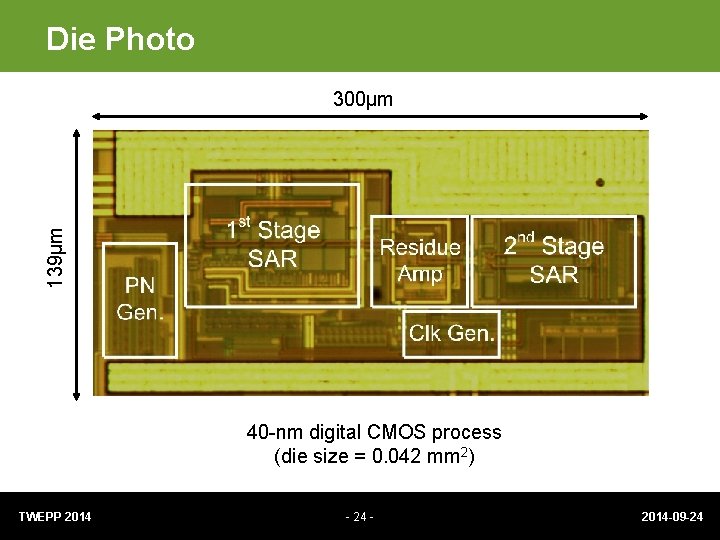

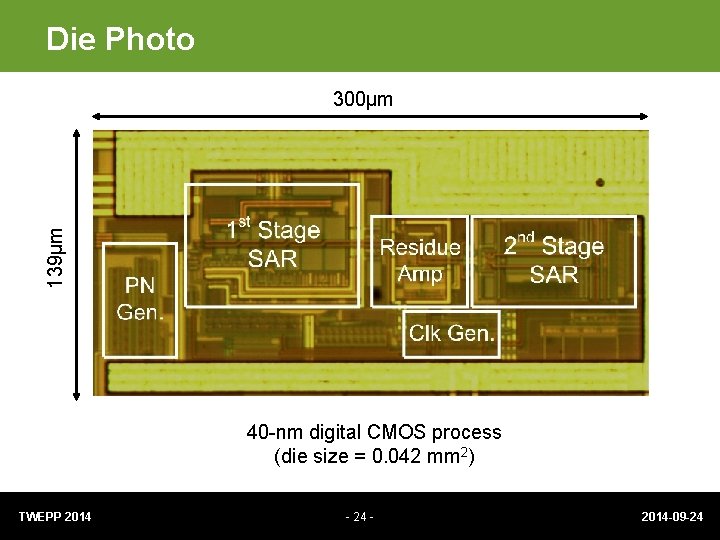

Die Photo 300μm 139μm Clock Sub& ADC 1 PN Gen. Integrator + DAC Sub. ADC 2 Sub. ADC 3 Sub. ADC 4 Sub. ADC 5 MDAC 1 MDAC 2 MDAC 3 MDAC 4 40 -nm digital CMOS process (die size = 0. 042 mm 2) TWEPP 2014 - 2014 -09 -24

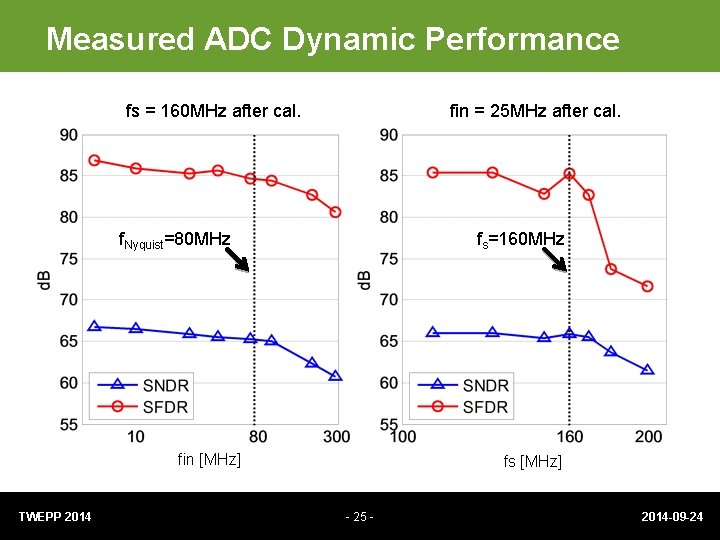

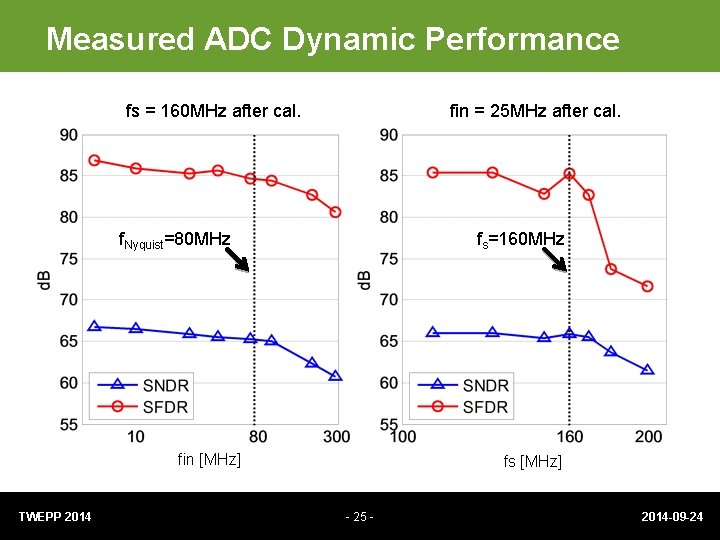

Measured ADC Dynamic Performance fs = 160 MHz after cal. fin = 25 MHz after cal. f. Nyquist=80 MHz fs=160 MHz fin [MHz] TWEPP 2014 fs [MHz] - 25 - 2014 -09 -24

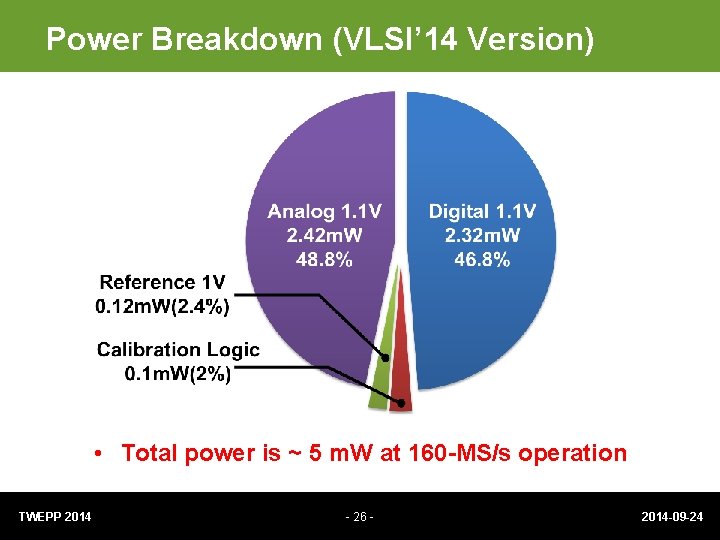

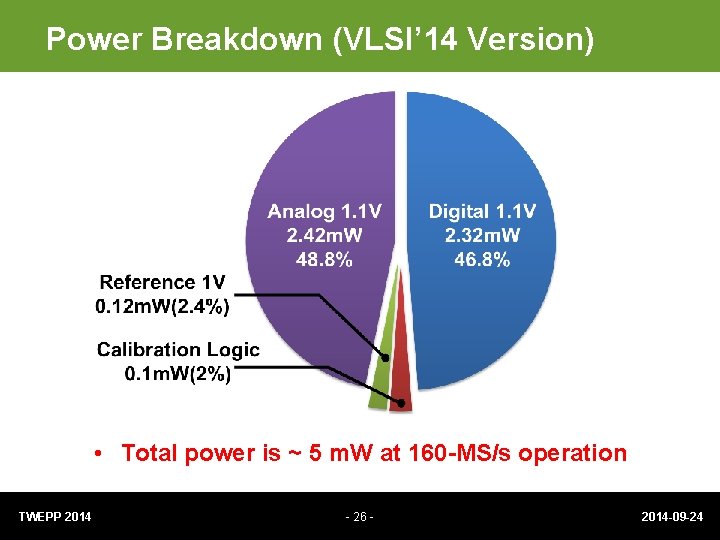

Power Breakdown (VLSI’ 14 Version) Analog 1. 1 V 2. 8 m. W (53. 6%) • Total power is ~ 5 m. W at 160 -MS/s operation TWEPP 2014 - 26 - 2014 -09 -24

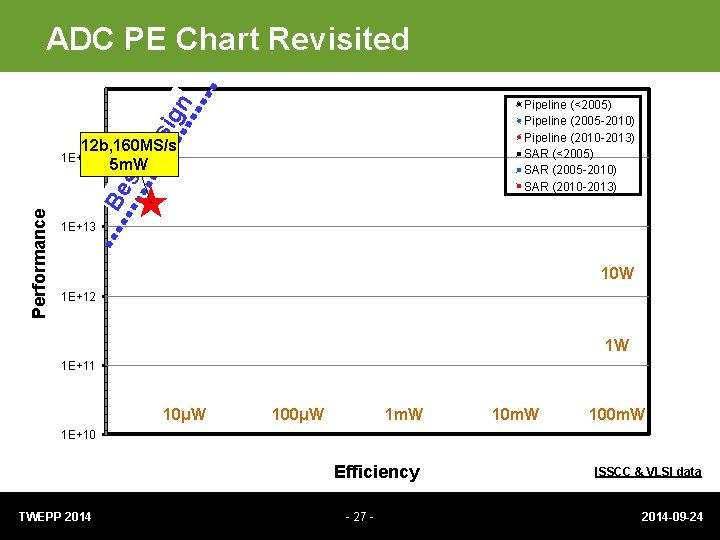

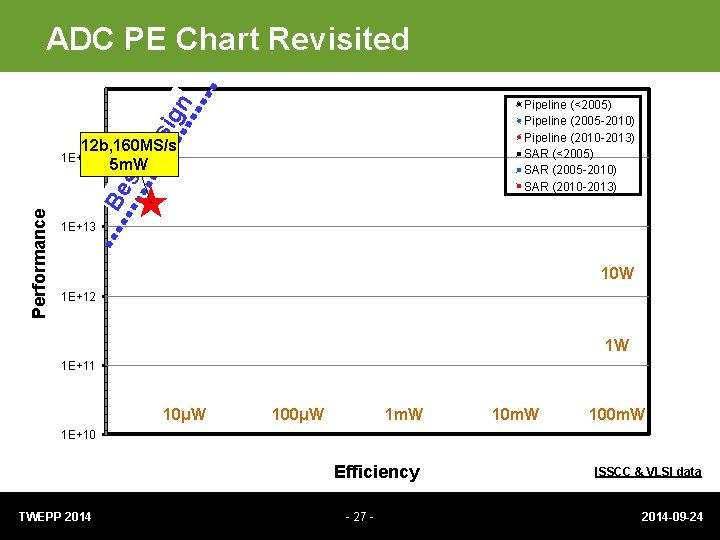

TWEPP 2014 - 27 - 2014 -09 -24

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 - 28 - 2014 -09 -24

TID Test of 40 -nm CMOS SAR ADC • DUT under X-ray radiation when powered up w/ clock input. • ADC performance (e. g. , SNDR, SFDR, power, etc. ) measured after irradiation is complete. TWEPP 2014 - 29 - 2014 -09 -24

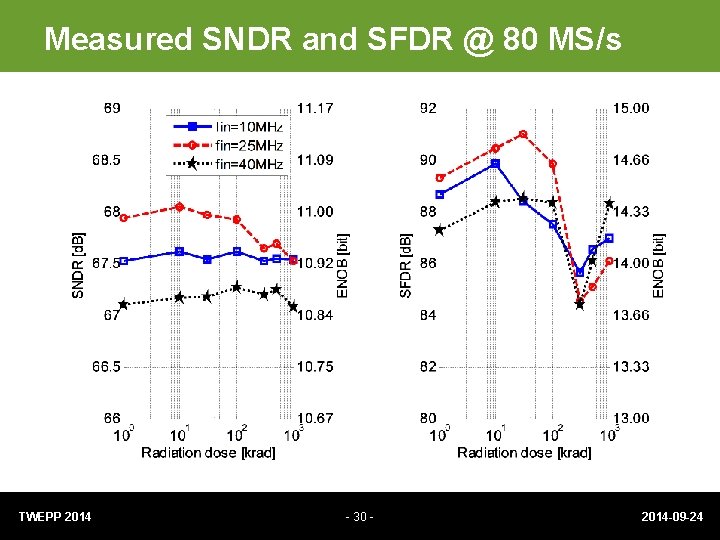

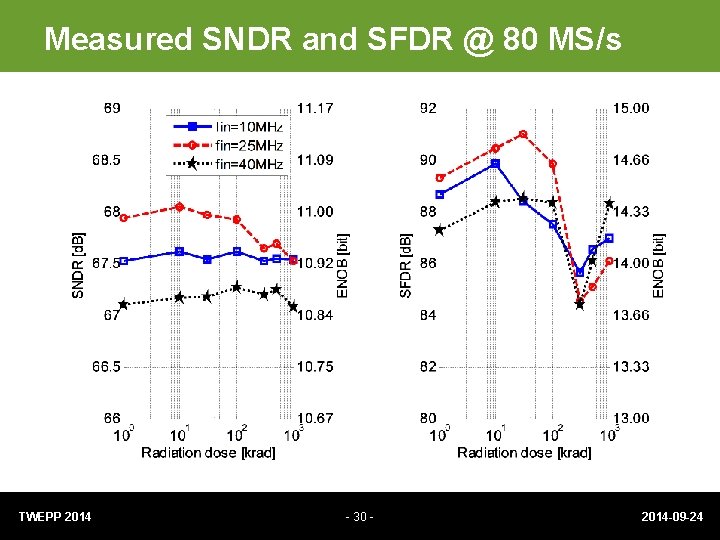

Measured SNDR and SFDR @ 80 MS/s TWEPP 2014 - 30 - 2014 -09 -24

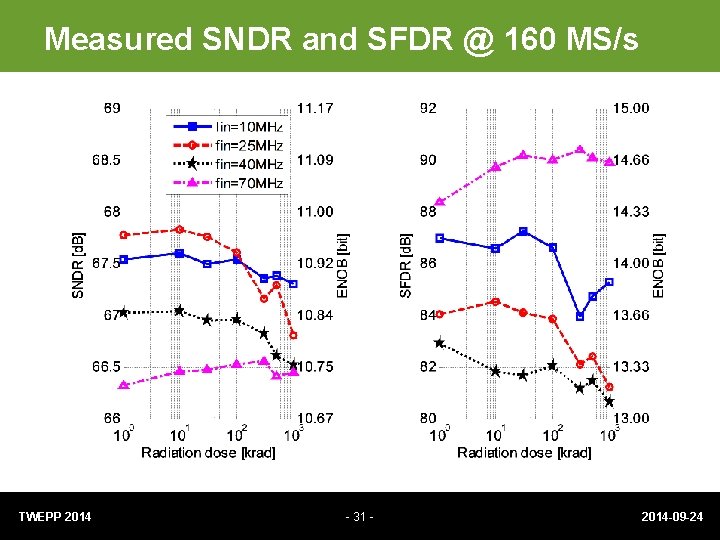

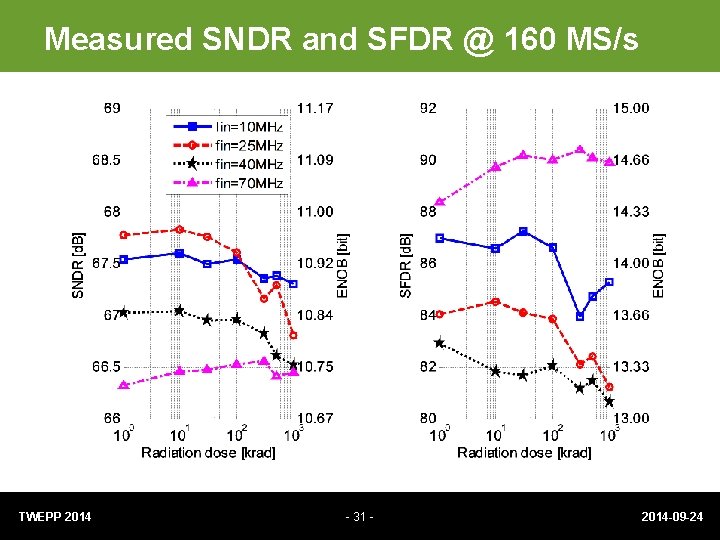

Measured SNDR and SFDR @ 160 MS/s TWEPP 2014 - 31 - 2014 -09 -24

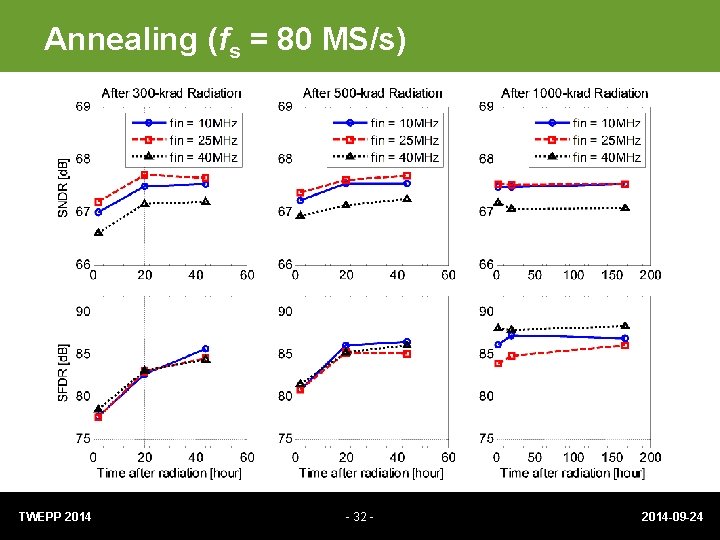

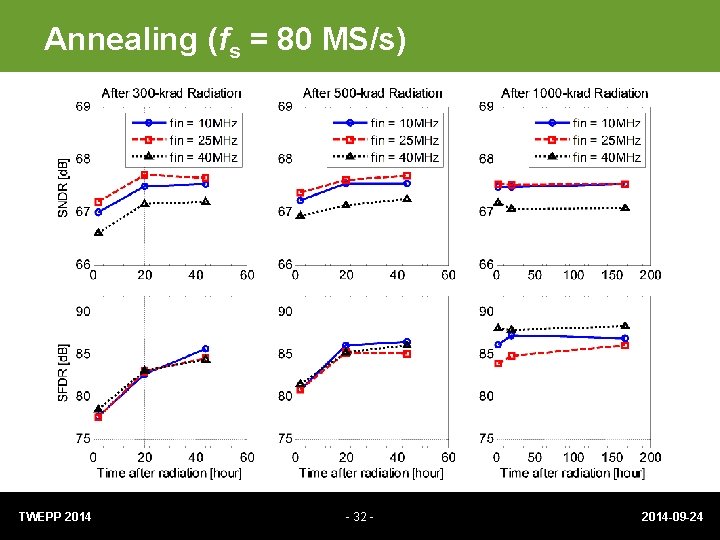

Annealing (fs = 80 MS/s) TWEPP 2014 - 32 - 2014 -09 -24

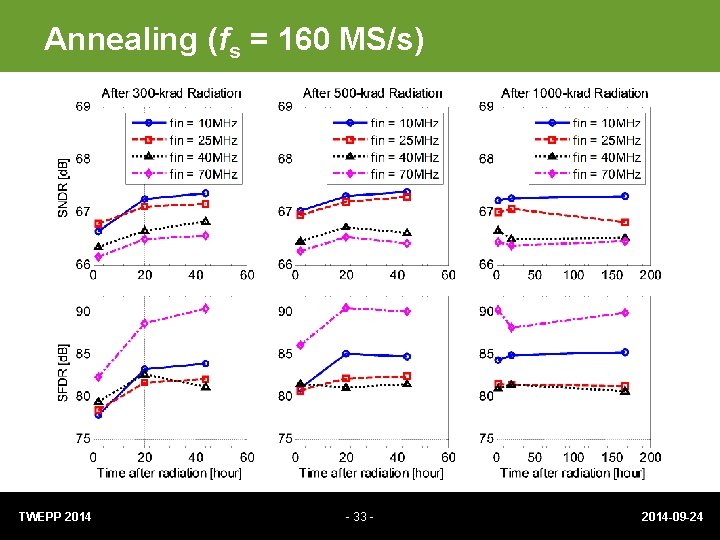

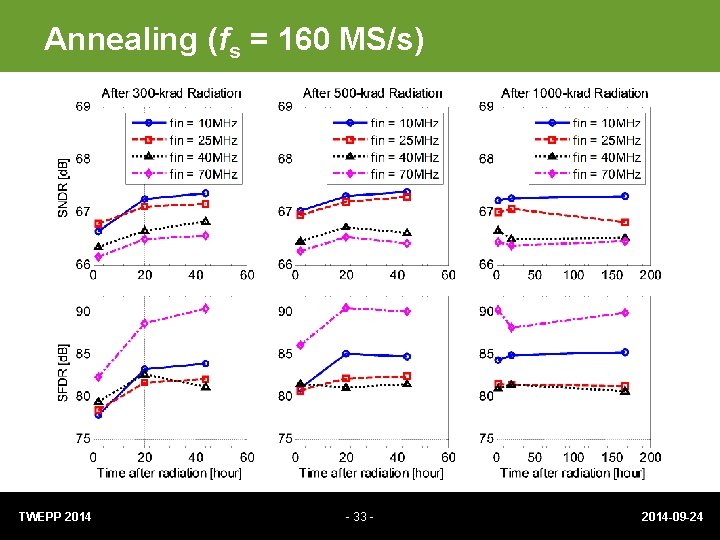

Annealing (fs = 160 MS/s) TWEPP 2014 - 33 - 2014 -09 -24

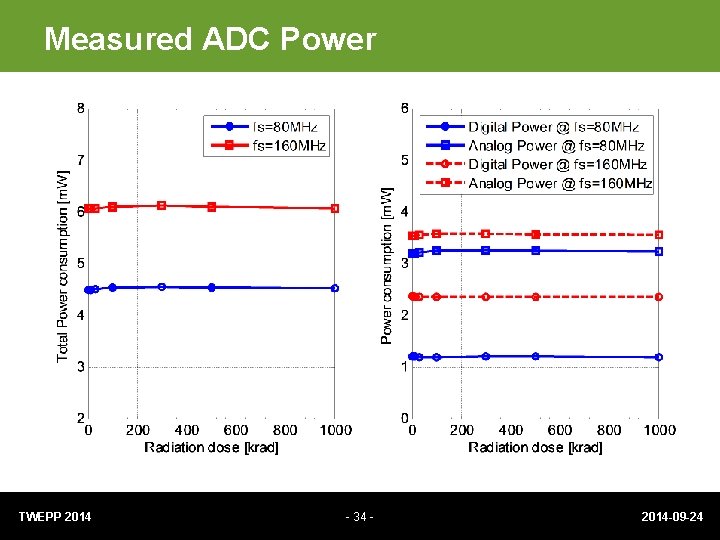

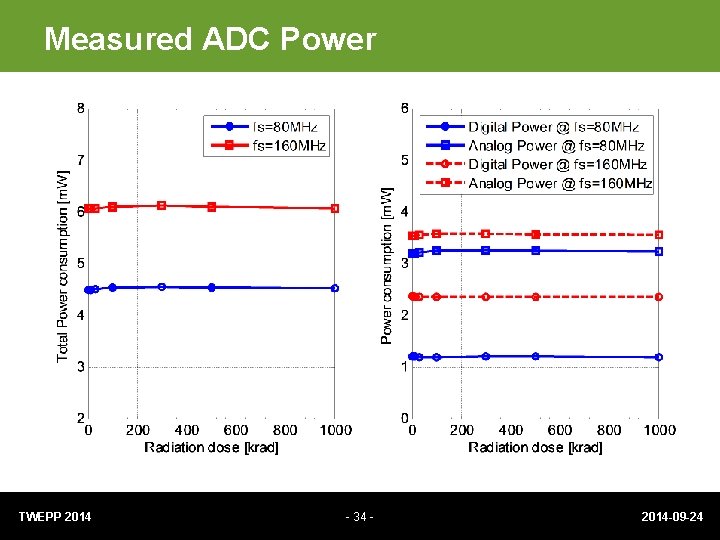

Measured ADC Power TWEPP 2014 - 34 - 2014 -09 -24

Outline • Introduction • Recent Advances in SAR ADCs • Our Recent 12 -bit SAR ADC Works § 45 -MS/s SAR Prototype (0. 13μm, 2010) § 160 -MS/s SAR Prototype (40 nm, 2014) • Total Ionization Dose (TID) Results (40 nm) • Summary TWEPP 2014 - 35 - 2014 -09 -24

Summary • High-resolution and high-speed SAR ADC is a strong candidate to meet the stringent requirements in HEP experiments • The preliminary irradiation test (TID) results further highlight the feasibility of SAR ADC in deeply scaled CMOS processes for HEP applications • Low power and small die size of SAR present great potentials for spatial redundancy technique to be employed in single-event upset (SEU) treatment Thank you for your attendance! TWEPP 2014 - 36 - 2014 -09 -24