Eri Prasetyo Wibowo Universitas Gunadarma http eri staffsite

Eri Prasetyo Wibowo Universitas Gunadarma http: //eri. staffsite. gunadarma. ac. id http: //pusatstudi. gunadarma. ac. id/pscitra

DIFINISI System-on-a-chip or system on chip (So. C or SOC) refers to integrating all components of a computer or other electronic system into a single integrated circuit (chip). It may contain digital, analog, mixed-signal, and often radio-frequency functions – all on one chip. A typical application is in the area of embedded systems. ( wikipedia) System-on-a-chip (So. C) technology is the packaging of all the necessary electronic circuits and parts for a "system" (such as a cell phone or digital camera) on a single integrated circuit ( IC ), generally known as a microchip. For example, a system-on-a-chip for a sound-detecting device might include an audio receiver, an analog-to-digital converter ( ADC ), a microprocessor , necessary memory , and the input/output logic control for a user - all on a single microchip.

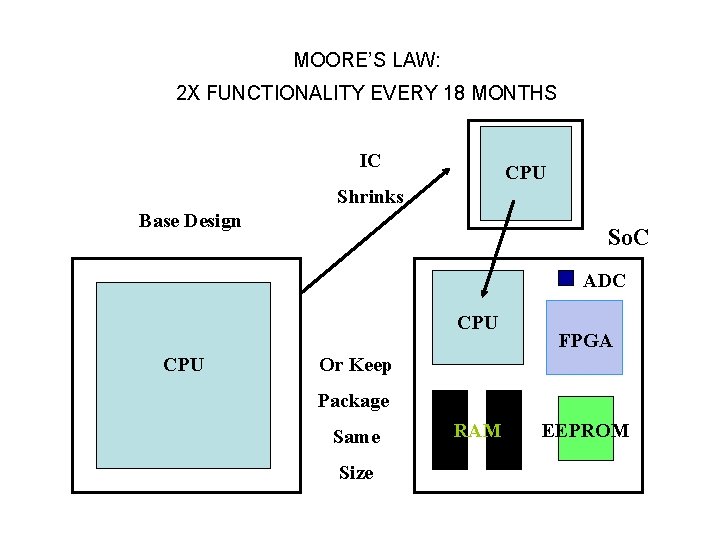

MOORE’S LAW: 2 X FUNCTIONALITY EVERY 18 MONTHS IC CPU Shrinks Base Design So. C ADC CPU FPGA Or Keep Package Same Size RAM EEPROM

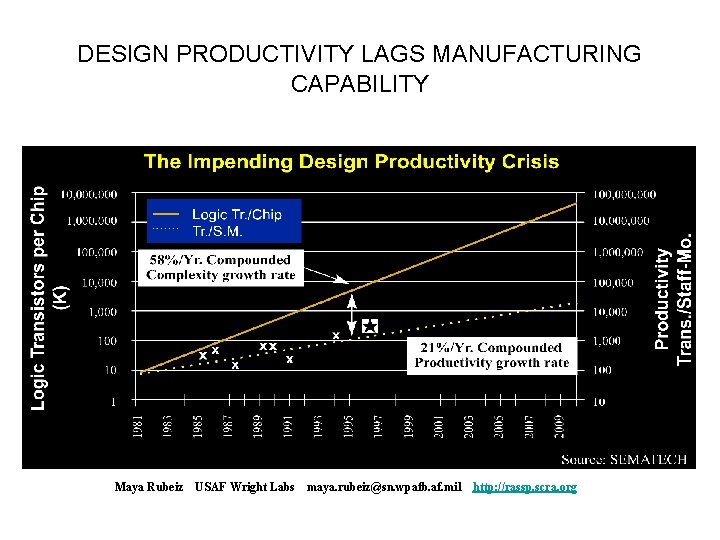

DESIGN PRODUCTIVITY LAGS MANUFACTURING CAPABILITY Maya Rubeiz USAF Wright Labs maya. rubeiz@sn. wpafb. af. mil http: //rassp. scra. org

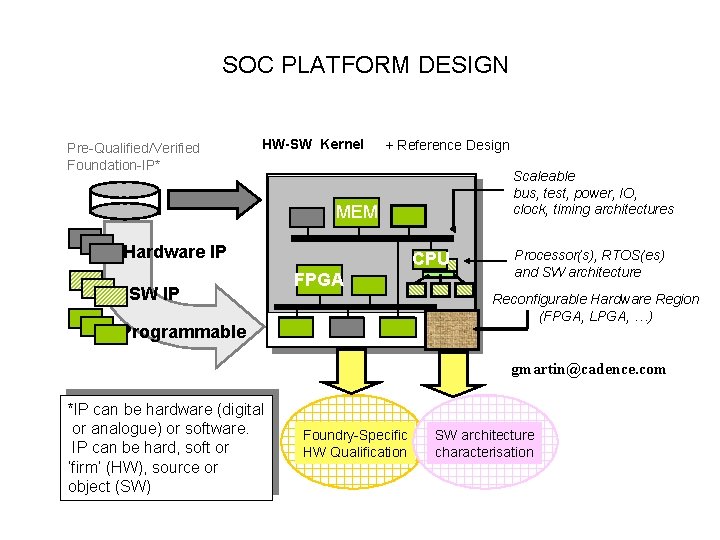

SOC PLATFORM DESIGN Pre-Qualified/Verified Foundation-IP* HW-SW Kernel + Reference Design Scaleable bus, test, power, IO, clock, timing architectures MEM Hardware IP SW IP Application Space CPU FPGA Processor(s), RTOS(es) and SW architecture Reconfigurable Hardware Region (FPGA, LPGA, …) Programmable gmartin@cadence. com *IP can be hardware (digital or analogue) or software. IP can be hard, soft or ‘firm’ (HW), source or object (SW) Foundry-Specific HW Qualification SW architecture characterisation

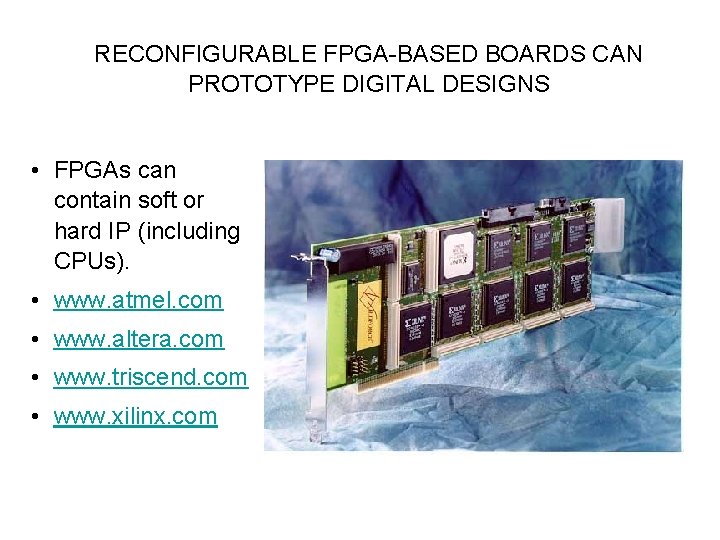

RECONFIGURABLE FPGA-BASED BOARDS CAN PROTOTYPE DIGITAL DESIGNS • FPGAs can contain soft or hard IP (including CPUs). • www. atmel. com • www. altera. com • www. triscend. com • www. xilinx. com

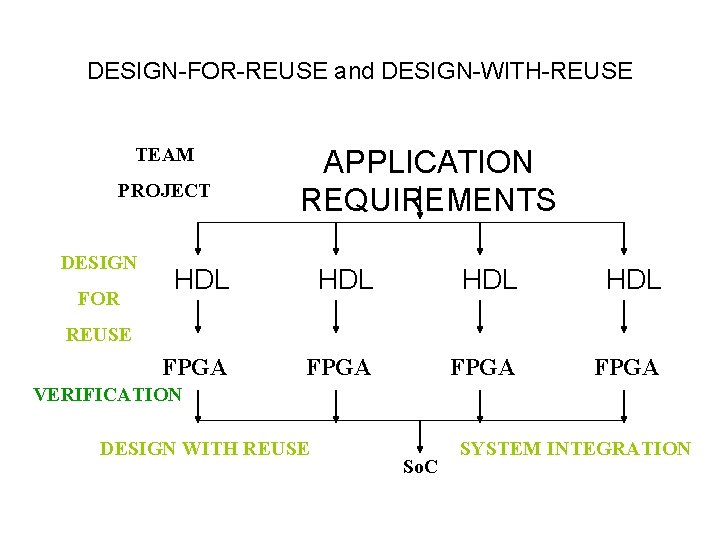

DESIGN-FOR-REUSE and DESIGN-WITH-REUSE TEAM PROJECT DESIGN FOR APPLICATION REQUIREMENTS HDL HDL FPGA REUSE VERIFICATION DESIGN WITH REUSE So. C SYSTEM INTEGRATION

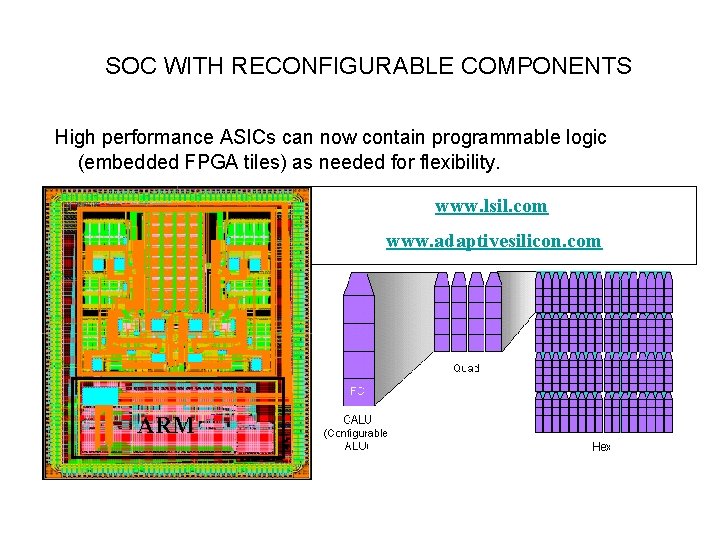

SOC WITH RECONFIGURABLE COMPONENTS High performance ASICs can now contain programmable logic (embedded FPGA tiles) as needed for flexibility. www. lsil. com www. adaptivesilicon. com ARM

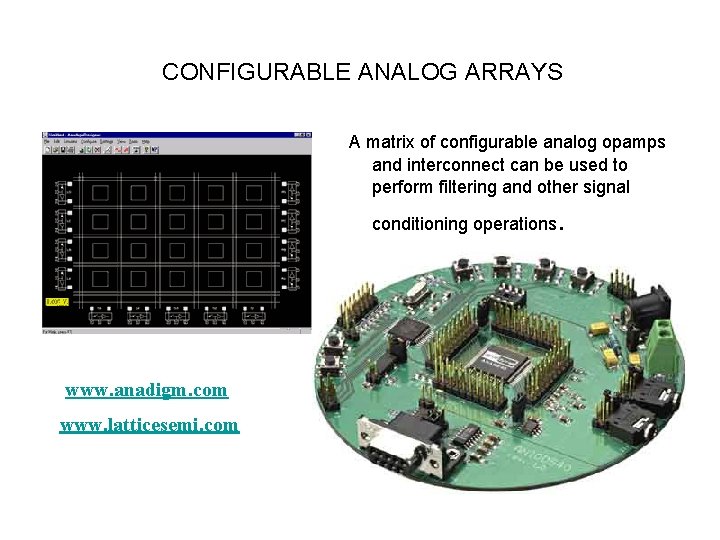

CONFIGURABLE ANALOG ARRAYS A matrix of configurable analog opamps and interconnect can be used to perform filtering and other signal conditioning operations www. anadigm. com www. latticesemi. com .

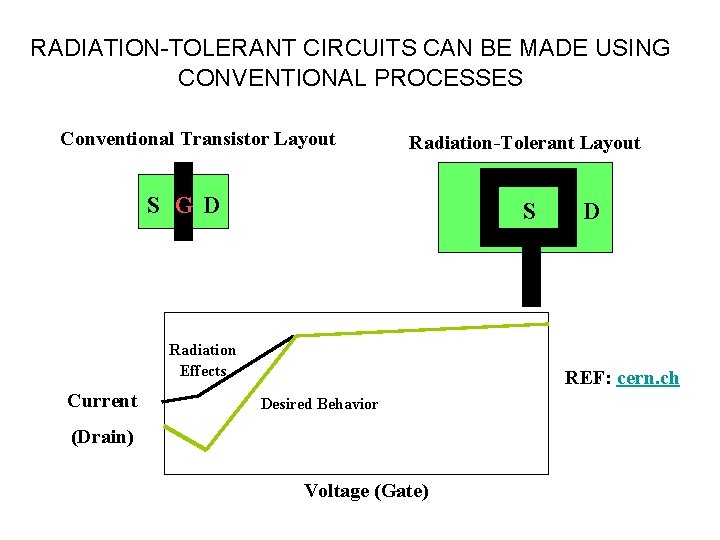

RADIATION-TOLERANT CIRCUITS CAN BE MADE USING CONVENTIONAL PROCESSES Conventional Transistor Layout Radiation-Tolerant Layout S G D S D G Radiation Effects Current REF: cern. ch Desired Behavior (Drain) Voltage (Gate)

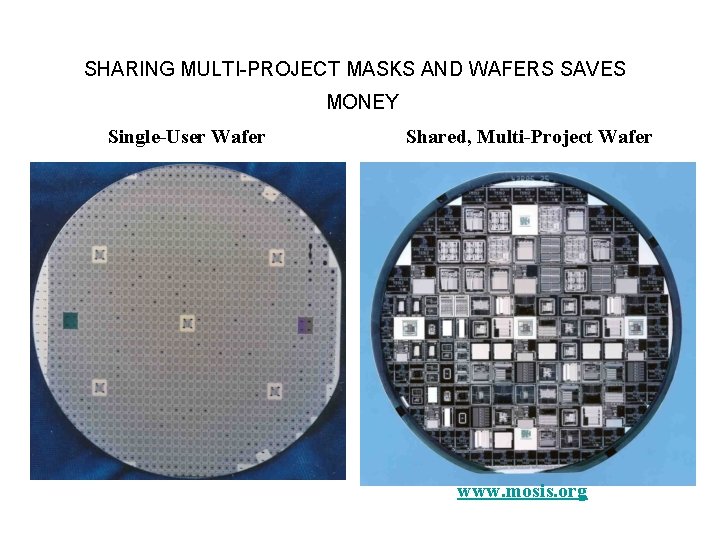

SHARING MULTI-PROJECT MASKS AND WAFERS SAVES MONEY Single-User Wafer Shared, Multi-Project Wafer www. mosis. org

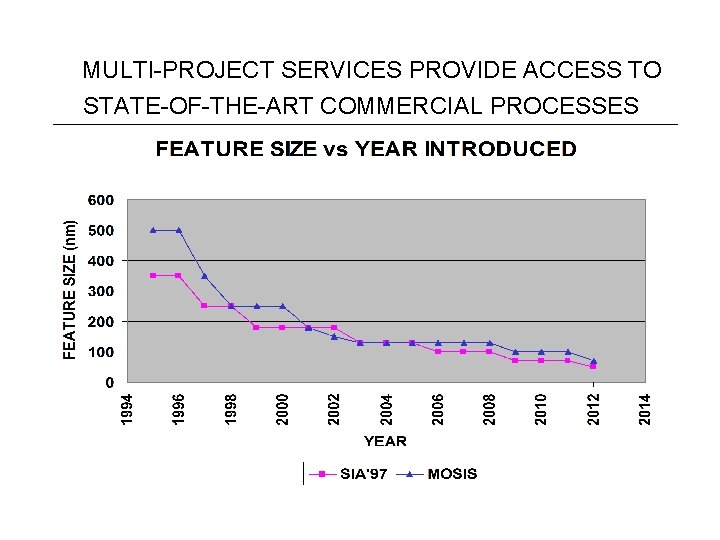

MULTI-PROJECT SERVICES PROVIDE ACCESS TO STATE-OF-THE-ART COMMERCIAL PROCESSES

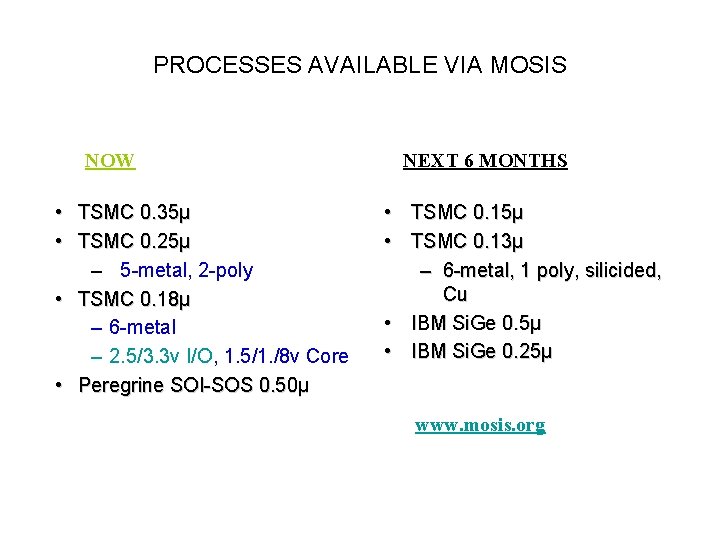

PROCESSES AVAILABLE VIA MOSIS NOW • TSMC 0. 35µ • TSMC 0. 25µ – 5 -metal, 2 -poly • TSMC 0. 18µ – 6 -metal – 2. 5/3. 3 v I/O, 1. 5/1. /8 v Core • Peregrine SOI-SOS 0. 50µ NEXT 6 MONTHS • • TSMC 0. 15µ TSMC 0. 13µ – 6 -metal, 1 poly, silicided, Cu • IBM Si. Ge 0. 5µ • IBM Si. Ge 0. 25µ www. mosis. org

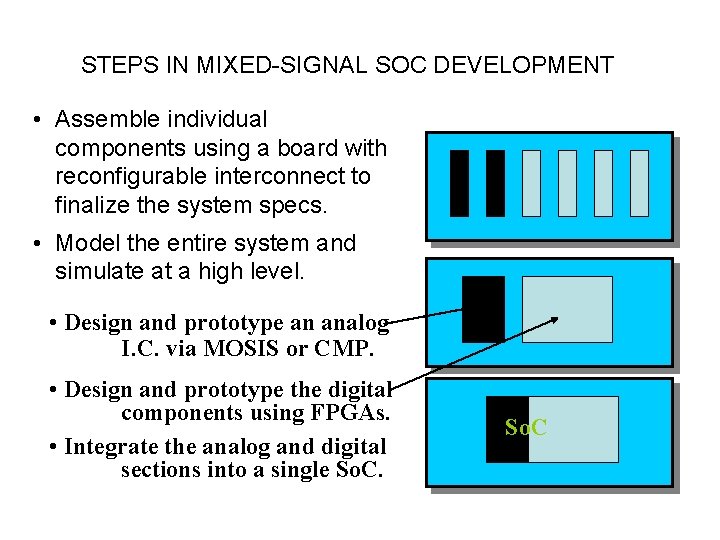

STEPS IN MIXED-SIGNAL SOC DEVELOPMENT • Assemble individual components using a board with reconfigurable interconnect to finalize the system specs. • Model the entire system and simulate at a high level. • Design and prototype an analog I. C. via MOSIS or CMP. • Design and prototype the digital components using FPGAs. • Integrate the analog and digital sections into a single So. C

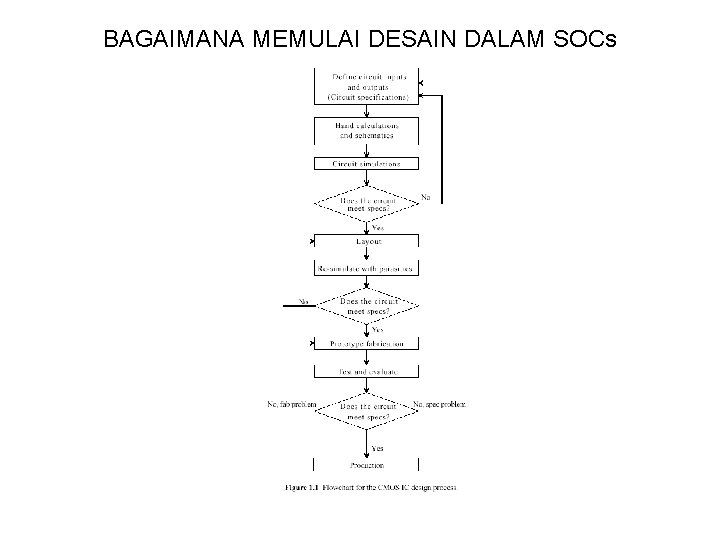

BAGAIMANA MEMULAI DESAIN DALAM SOCs

- Slides: 15