Eo C Status Report Giulio Dellacasa Giga Tracker

- Slides: 9

Eo. C Status Report Giulio Dellacasa Giga. Tracker Working Group CERN, December 9 th 2008

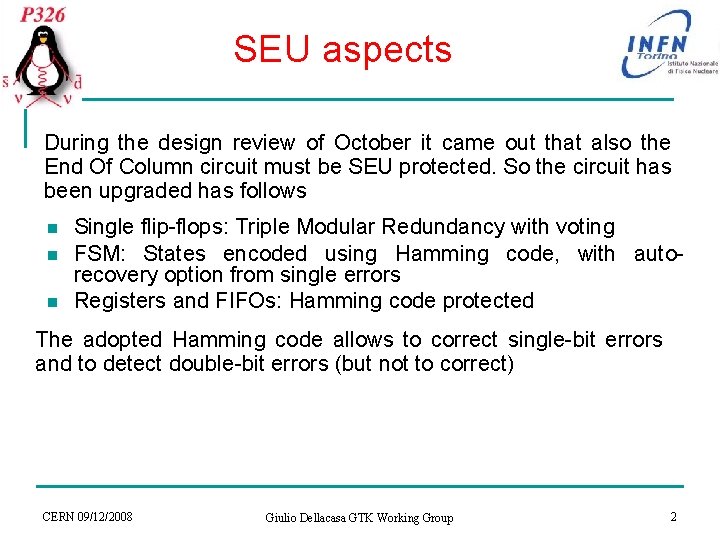

SEU aspects During the design review of October it came out that also the End Of Column circuit must be SEU protected. So the circuit has been upgraded has follows n n n Single flip-flops: Triple Modular Redundancy with voting FSM: States encoded using Hamming code, with autorecovery option from single errors Registers and FIFOs: Hamming code protected The adopted Hamming code allows to correct single-bit errors and to detect double-bit errors (but not to correct) CERN 09/12/2008 Giulio Dellacasa GTK Working Group 2

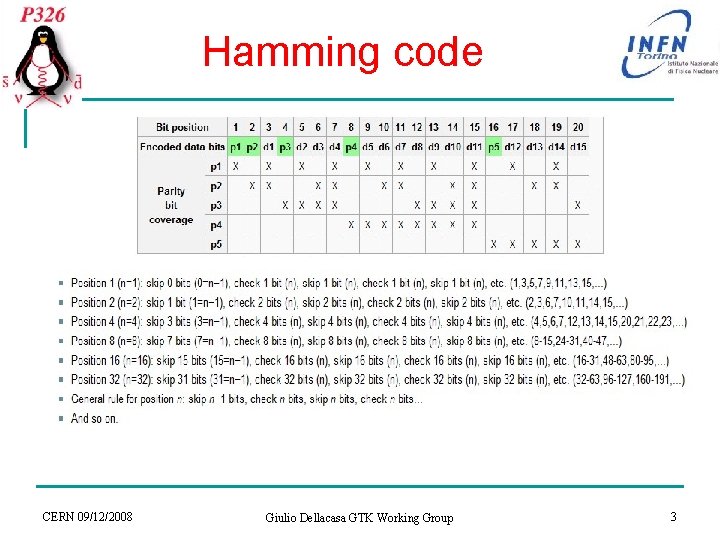

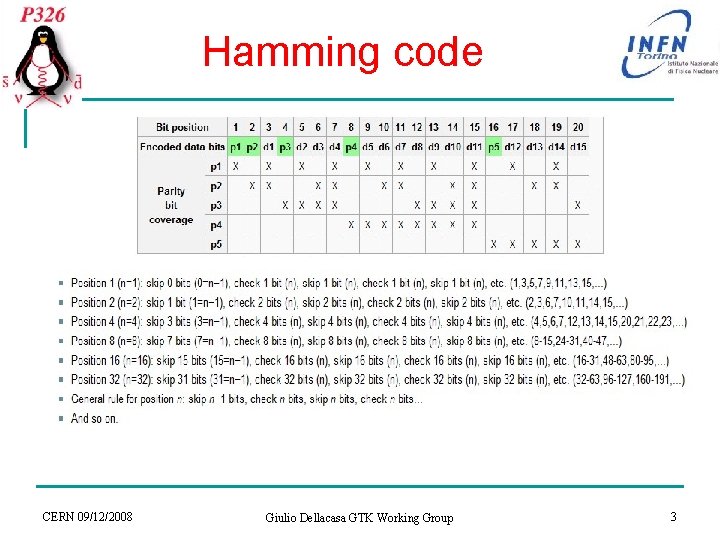

Hamming code CERN 09/12/2008 Giulio Dellacasa GTK Working Group 3

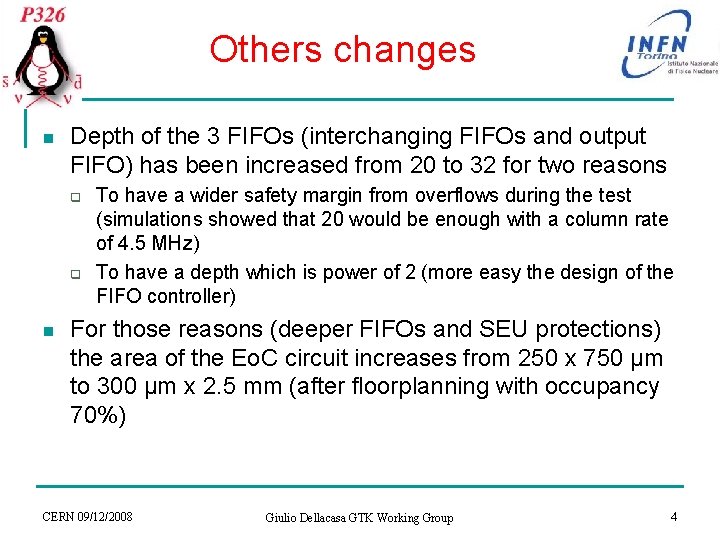

Others changes n Depth of the 3 FIFOs (interchanging FIFOs and output FIFO) has been increased from 20 to 32 for two reasons q q n To have a wider safety margin from overflows during the test (simulations showed that 20 would be enough with a column rate of 4. 5 MHz) To have a depth which is power of 2 (more easy the design of the FIFO controller) For those reasons (deeper FIFOs and SEU protections) the area of the Eo. C circuit increases from 250 x 750 µm to 300 µm x 2. 5 mm (after floorplanning with occupancy 70%) CERN 09/12/2008 Giulio Dellacasa GTK Working Group 4

Synthesis n Synthesis has been performed with the following operating environment: q q q n n n clock frequency at 200 MHz (5 ns) VDD 1. 08 Temperature 100 C No timing violations observed in reports Post-Synthesis simulations has been performed at lower frequency due the built-in delay there is the Synopsys library (3 ns each gate! Not realistic) Only post-layout simulations will have realistic signals delays CERN 09/12/2008 Giulio Dellacasa GTK Working Group 5

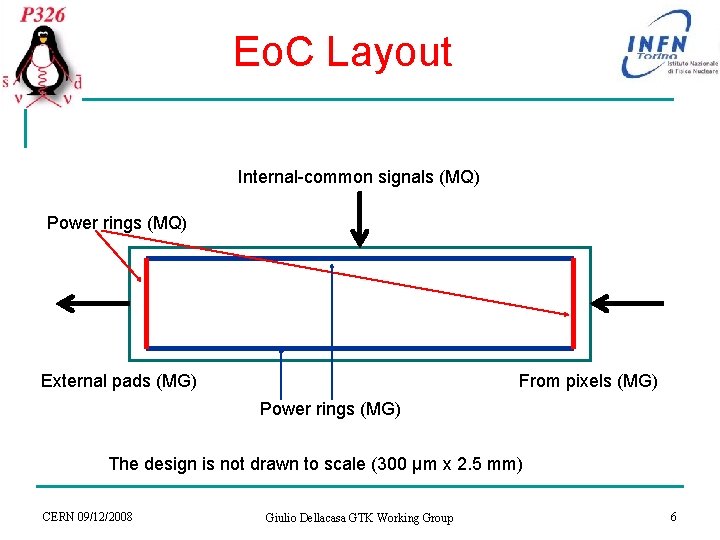

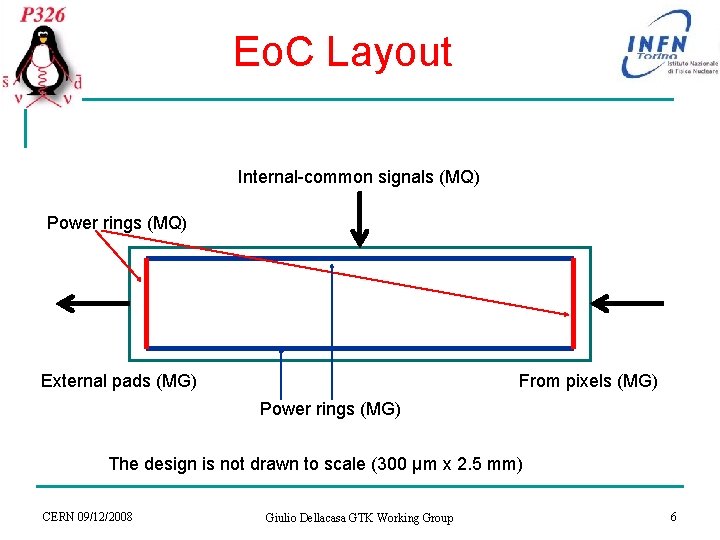

Eo. C Layout Internal-common signals (MQ) Power rings (MQ) External pads (MG) From pixels (MG) Power rings (MG) The design is not drawn to scale (300 µm x 2. 5 mm) CERN 09/12/2008 Giulio Dellacasa GTK Working Group 6

Other things to change… n n After a first floorplanning we discovered that we won’t have enough space for all the pads we need (29 differential signals + 9 debug/status signals) One possible solution (maybe the only one) is to have serial data output from the Eo. C circuit (instead of the 16 bit parallel bus) 3 different serial data ports (+ 3 Dval ports) will provide the 3 columns read-out Number of estimated signals with serial read-out: 15 (+ 9 debug/status) CERN 09/12/2008 Giulio Dellacasa GTK Working Group 7

Serial output n n Each Eo. C circuit will be equipped with a 32 bit shift register working at 160 MHz by default, with the possibility to slow down at 80 or 40 MHz (work in progress) One more differential signal will provide the write-enable signal for the DAQ (Data Valid Flag, Dval) CERN 09/12/2008 Giulio Dellacasa GTK Working Group 8

Conclusion n n All the possible effort will be put in order to have a preliminary layout before Christmas, with the latest changes (serial output) Post-Layout simulations and verifications will be performed in the beginning of January CERN 09/12/2008 Giulio Dellacasa GTK Working Group 9