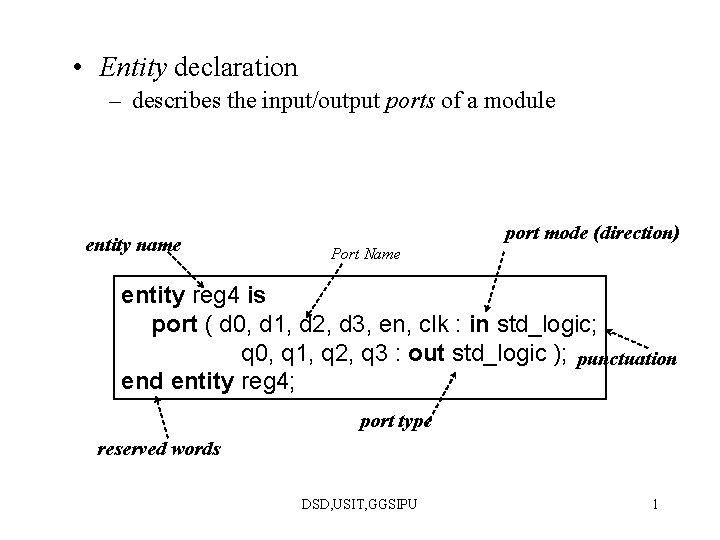

Entity declaration describes the inputoutput ports of a

• Entity declaration – describes the input/output ports of a module entity name port mode (direction) Port Name entity reg 4 is port ( d 0, d 1, d 2, d 3, en, clk : in std_logic; q 0, q 1, q 2, q 3 : out std_logic ); punctuation end entity reg 4; port type reserved words DSD, USIT, GGSIPU 1

Modeling Behavior • Architecture body – describes an implementation of an entity – may be several per entity • Behavioral architecture – describes the algorithm performed by the module – contains • • process statements, Function Statement 1 Port interface DSD, USIT, GGSIPU 2

Modeling Structure • Structural architecture – implements the module as a composition of subsystems – contains • signal declarations, for internal interconnections – the entity ports are also treated as signals • component declarations – instances of previously declared entity/architecture pairs • port maps in component instances – connect signals to component ports DSD, USIT, GGSIPU 3

![Component Declaration Component-name [is] [port (list-of-interface-port); ] End component [component-name]; Component-name: may or may Component Declaration Component-name [is] [port (list-of-interface-port); ] End component [component-name]; Component-name: may or may](http://slidetodoc.com/presentation_image_h2/14d3a8f8bcba8cf26091ffcaee4adfa1/image-4.jpg)

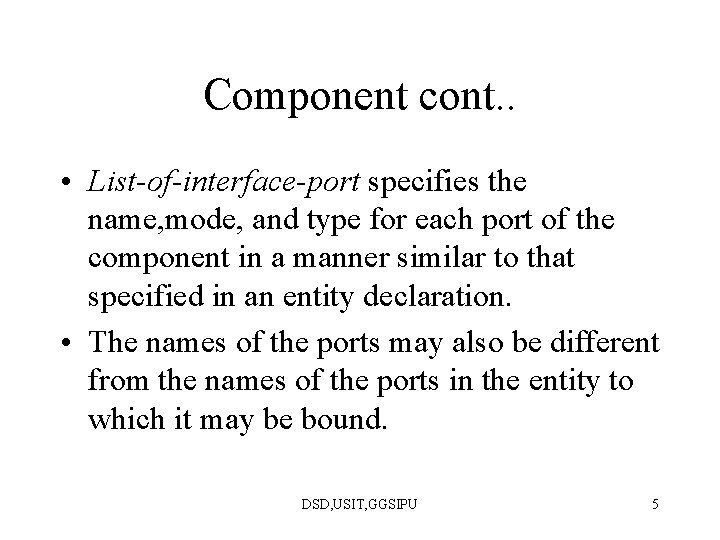

Component Declaration Component-name [is] [port (list-of-interface-port); ] End component [component-name]; Component-name: may or may not refer to the name of an entity already existing in a library. DSD, USIT, GGSIPU 4

Component cont. . • List-of-interface-port specifies the name, mode, and type for each port of the component in a manner similar to that specified in an entity declaration. • The names of the ports may also be different from the names of the ports in the entity to which it may be bound. DSD, USIT, GGSIPU 5

Component declaration • Component declaration appear in the declaration part of an architecture body. • They may also appear in a package declaration DSD, USIT, GGSIPU 6

Signal declaration • Are required to connect different types of ports. (mode of ports) • Class of the object identifier • Signal object should be same data type as it is in component and entity. • Signal object can be also be declared as an array DSD, USIT, GGSIPU 7

Component Instantiation • A Component instantiation statement defines a subcomponent of the entity in which it appears. • It associates the signals in the entity with the ports of that subcomponent. DSD, USIT, GGSIPU 8

![Format of a component Instantiation statement Component-label : component-name [port map (association-list)]; * Component-label: Format of a component Instantiation statement Component-label : component-name [port map (association-list)]; * Component-label:](http://slidetodoc.com/presentation_image_h2/14d3a8f8bcba8cf26091ffcaee4adfa1/image-9.jpg)

Format of a component Instantiation statement Component-label : component-name [port map (association-list)]; * Component-label: It can be any legal identifier and can be considered as the name of the instance. DSD, USIT, GGSIPU 9

Component instantiation • The component-name must be the name of a component declared earlier using a component declaration. • The association-list associates signals in the entity, called actuals, with the ports of a component, called formals. DSD, USIT, GGSIPU 10

Association technique • There are two ways to perform the association of formals with actuals: 1. Positional association 2. Named association DSD, USIT, GGSIPU 11

Positional association • An association-list is of the form: Actual 1, actual 2, actual 3……………actualn The first port in the component declaration corresponds to the first actual in the component instantiation, the second with second, and so on. DSD, USIT, GGSIPU 12

Named association • An association-list is of the form: Formal 1=>actual 1, formal 2=>actual 2……. . formaln=>actualn In named association, the ordering of the association is not important since the mapping between the actuals and formals is explicitly specified. The scope of the formals is restricted to be within the port map part of the instantiation for that component. DSD, USIT, GGSIPU 13

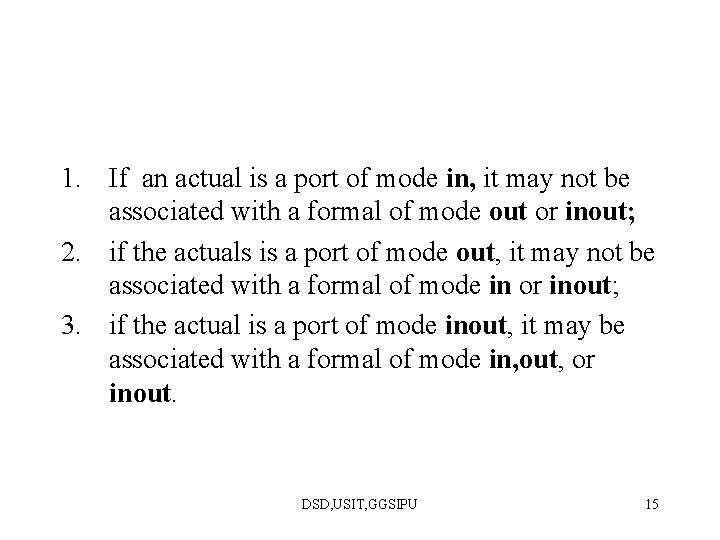

Rules of the port map 1. The types of the formal and actual being associated must be the same. 2. The modes of the ports must conform to the rule that if the formal s readable, so must the actual be; and if the formal is considered to be both readable and writeable, such a signal may be associated with a formal of any mode. DSD, USIT, GGSIPU 14

1. If an actual is a port of mode in, it may not be associated with a formal of mode out or inout; 2. if the actuals is a port of mode out, it may not be associated with a formal of mode in or inout; 3. if the actual is a port of mode inout, it may be associated with a formal of mode in, out, or inout. DSD, USIT, GGSIPU 15

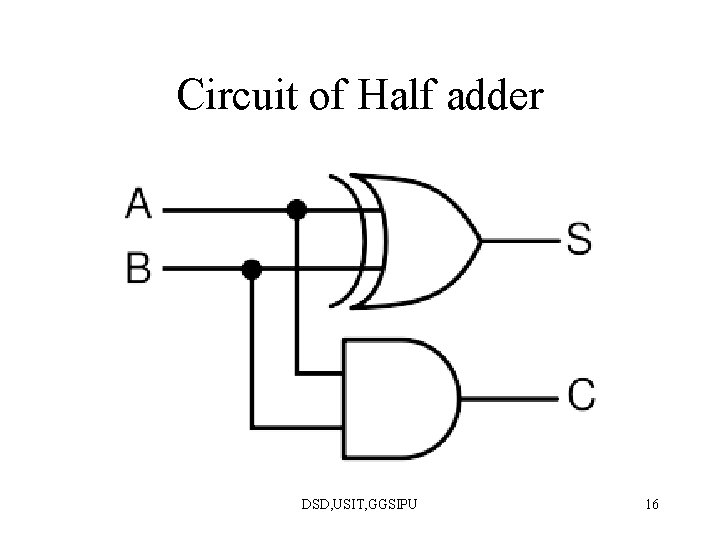

Circuit of Half adder DSD, USIT, GGSIPU 16

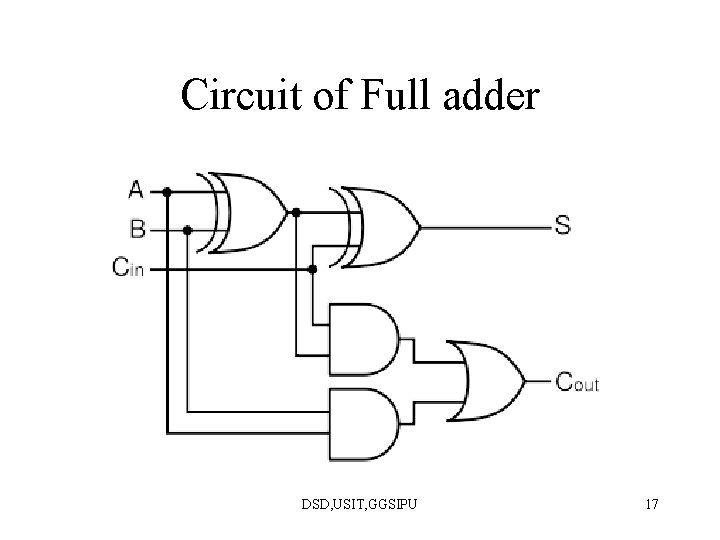

Circuit of Full adder DSD, USIT, GGSIPU 17

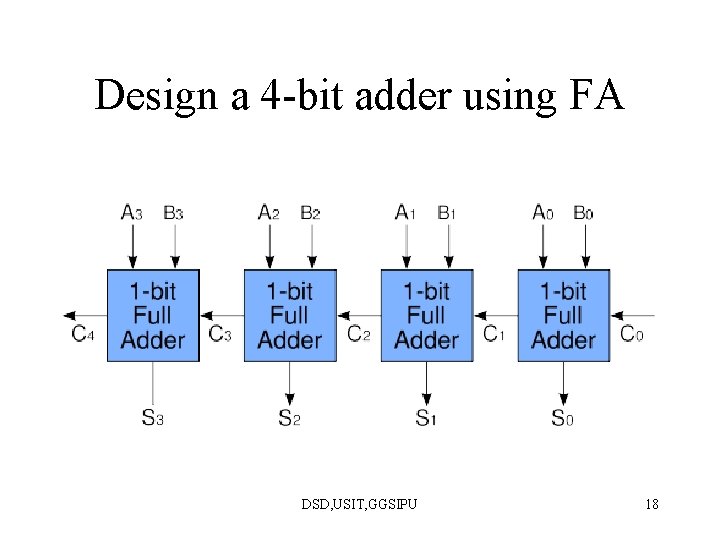

Design a 4 -bit adder using FA DSD, USIT, GGSIPU 18

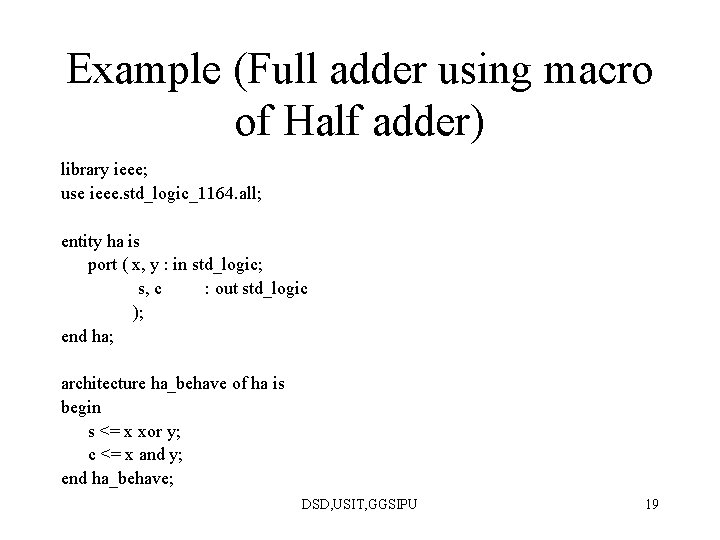

Example (Full adder using macro of Half adder) library ieee; use ieee. std_logic_1164. all; entity ha is port ( x, y : in std_logic; s, c : out std_logic ); end ha; architecture ha_behave of ha is begin s <= x xor y; c <= x and y; end ha_behave; DSD, USIT, GGSIPU 19

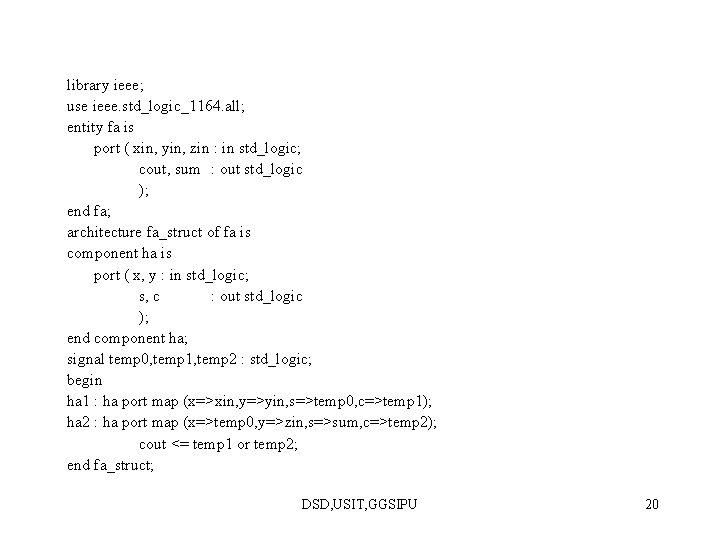

library ieee; use ieee. std_logic_1164. all; entity fa is port ( xin, yin, zin : in std_logic; cout, sum : out std_logic ); end fa; architecture fa_struct of fa is component ha is port ( x, y : in std_logic; s, c : out std_logic ); end component ha; signal temp 0, temp 1, temp 2 : std_logic; begin ha 1 : ha port map (x=>xin, y=>yin, s=>temp 0, c=>temp 1); ha 2 : ha port map (x=>temp 0, y=>zin, s=>sum, c=>temp 2); cout <= temp 1 or temp 2; end fa_struct; DSD, USIT, GGSIPU 20

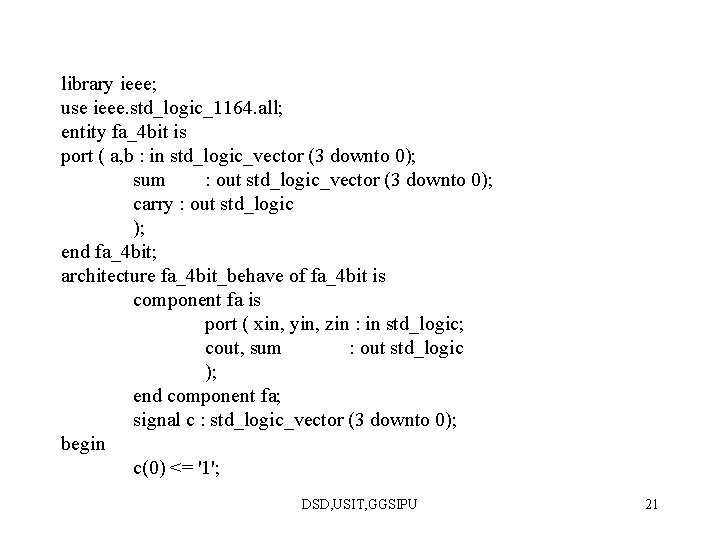

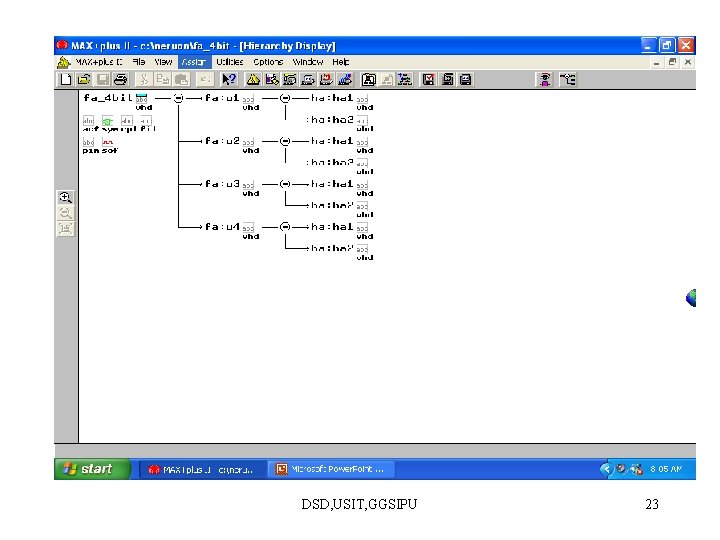

library ieee; use ieee. std_logic_1164. all; entity fa_4 bit is port ( a, b : in std_logic_vector (3 downto 0); sum : out std_logic_vector (3 downto 0); carry : out std_logic ); end fa_4 bit; architecture fa_4 bit_behave of fa_4 bit is component fa is port ( xin, yin, zin : in std_logic; cout, sum : out std_logic ); end component fa; signal c : std_logic_vector (3 downto 0); begin c(0) <= '1'; DSD, USIT, GGSIPU 21

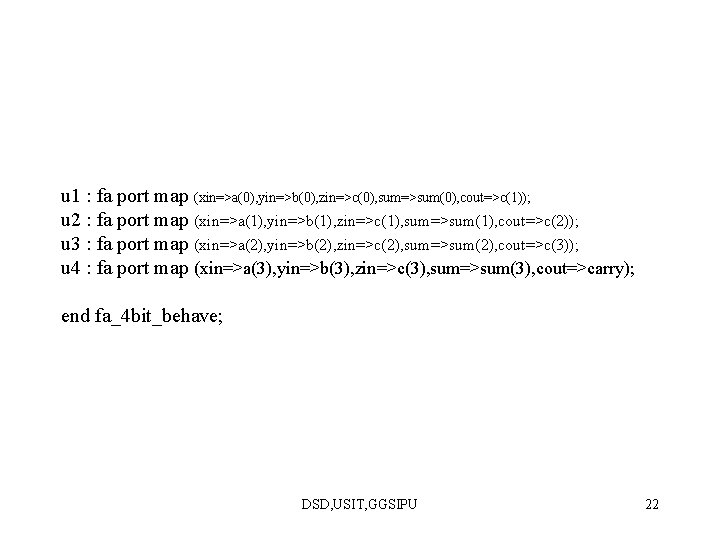

u 1 : fa port map (xin=>a(0), yin=>b(0), zin=>c(0), sum=>sum(0), cout=>c(1)); u 2 : fa port map (xin=>a(1), yin=>b(1), zin=>c(1), sum=>sum(1), cout=>c(2)); u 3 : fa port map (xin=>a(2), yin=>b(2), zin=>c(2), sum=>sum(2), cout=>c(3)); u 4 : fa port map (xin=>a(3), yin=>b(3), zin=>c(3), sum=>sum(3), cout=>carry); end fa_4 bit_behave; DSD, USIT, GGSIPU 22

DSD, USIT, GGSIPU 23

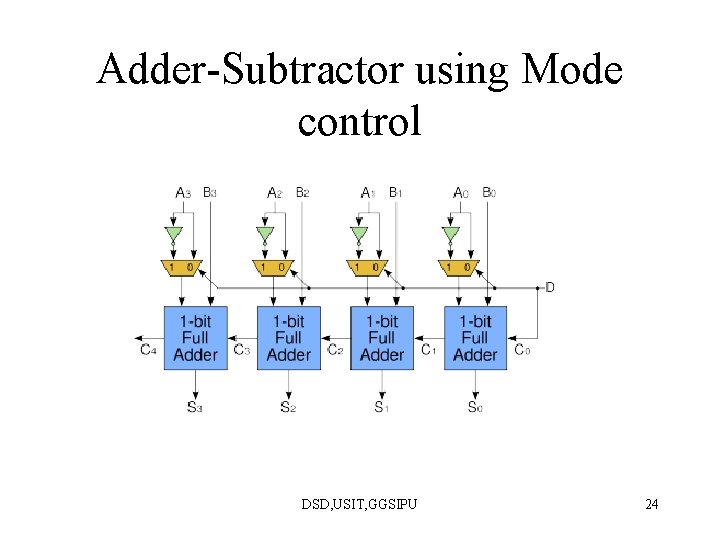

Adder-Subtractor using Mode control DSD, USIT, GGSIPU 24

- Slides: 24