Enhanced Scan Based Flip Flop for Delay Testing

Enhanced Scan Based Flip -Flop for Delay Testing By Sudheer Vemula 4/28/05 Vemula: ELEC 7250 1

Problem to be solved: o To perform delay test, two vectors, V 1 and V 2, have to be applied in sequence n n o o The problem is, if we want to apply two independent vectors to the scan chain of flip-flops, we will loose the initialization of the circuit. This problem can be solved by inserting hold latches, with an additional HOLD signal, to each scan flip-flop. n o 4/28/05 V 1 – For initializing the output of a particular path under test V 2 – To observe the transition at the output Area over head and delay in the signal path are increased. Problem to be solved: - We need hold latches which have less area overhead and time delay. Vemula: ELEC 7250 2

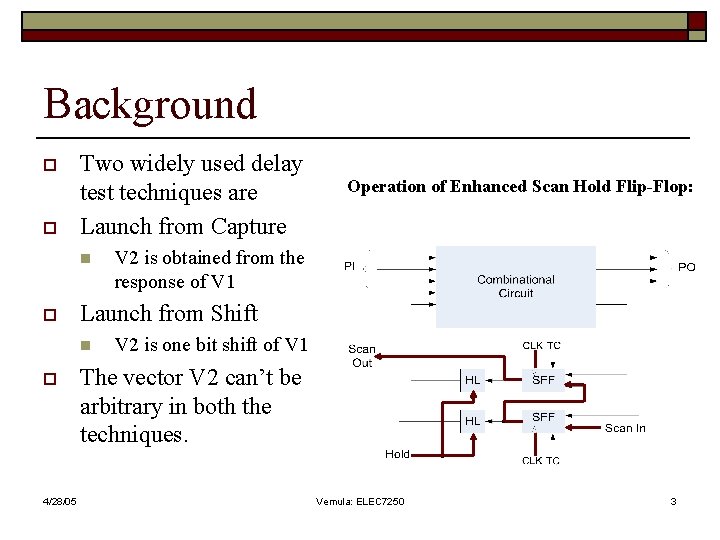

Background o o Two widely used delay test techniques are Launch from Capture n o 4/28/05 V 2 is obtained from the response of V 1 Launch from Shift n o Operation of Enhanced Scan Hold Flip-Flop: V 2 is one bit shift of V 1 The vector V 2 can’t be arbitrary in both the techniques. Vemula: ELEC 7250 3

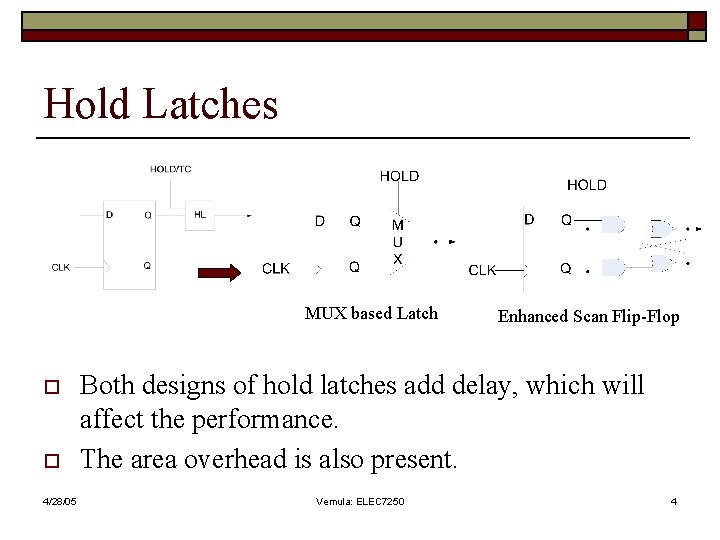

Hold Latches MUX based Latch o o 4/28/05 Enhanced Scan Flip-Flop Both designs of hold latches add delay, which will affect the performance. The area overhead is also present. Vemula: ELEC 7250 4

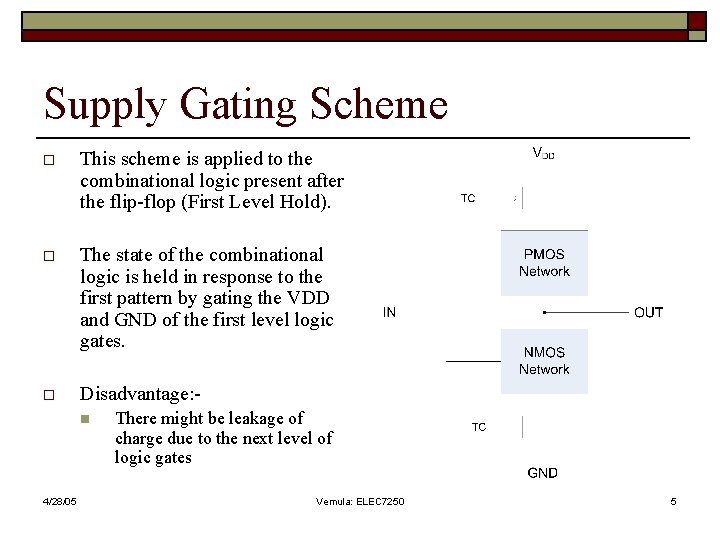

Supply Gating Scheme o This scheme is applied to the combinational logic present after the flip-flop (First Level Hold). o The state of the combinational logic is held in response to the first pattern by gating the VDD and GND of the first level logic gates. o Disadvantage: n 4/28/05 There might be leakage of charge due to the next level of logic gates Vemula: ELEC 7250 5

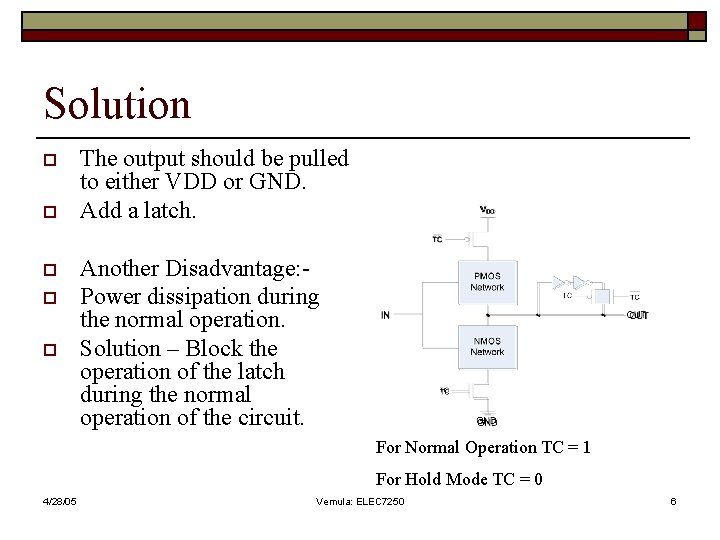

Solution o o o The output should be pulled to either VDD or GND. Add a latch. Another Disadvantage: Power dissipation during the normal operation. Solution – Block the operation of the latch during the normal operation of the circuit. For Normal Operation TC = 1 For Hold Mode TC = 0 4/28/05 Vemula: ELEC 7250 6

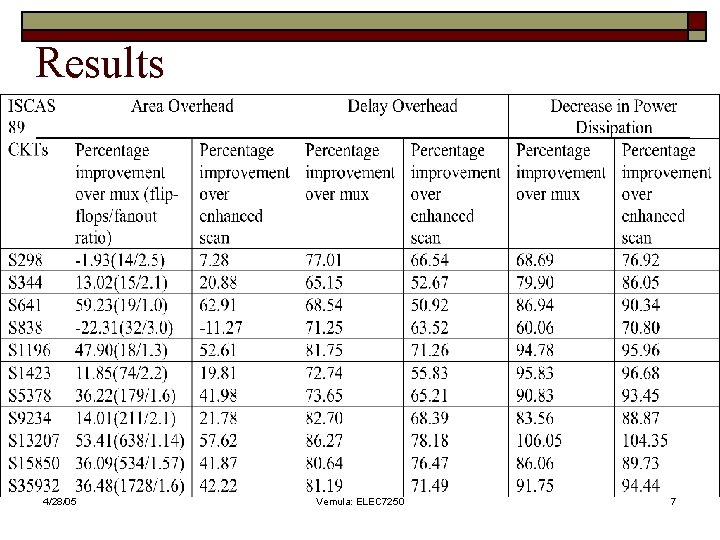

Results 4/28/05 Vemula: ELEC 7250 7

Conclusions o o The additional transistors in both PMOS and NMOS networks will increase the load at the output of the flip-flop, which will cause some additional delay compared to normal operation of the circuit without hold latch. If fan outs are present at the output of the flip-flops, this will cause an increase the area and delay overhead. n o 4/28/05 For smaller circuits with more fan outs, MUX based latch may give better results for some cases. There is an average reduction of 33% in area overhead with an average improvement of 71% in delay overhead and 90% in power overhead during normal mode of operation compared to enhanced scan implementation. Vemula: ELEC 7250 8

![Reference [1] S. Bhunia, H. Mahmoodi, A. Raychowdhury, and K. Roy, ‘‘A Novel Low-overhead Reference [1] S. Bhunia, H. Mahmoodi, A. Raychowdhury, and K. Roy, ‘‘A Novel Low-overhead](http://slidetodoc.com/presentation_image_h/cf928dd2ce57b7d56f848e3e156bf24b/image-9.jpg)

Reference [1] S. Bhunia, H. Mahmoodi, A. Raychowdhury, and K. Roy, ‘‘A Novel Low-overhead Delay Testing Technique for Arbitrary Two-Pattern Test Application, ’’ Proc. Design, Automation and Test in Europe, pp. 1136 -1141, 2005 4/28/05 Vemula: ELEC 7250 9

- Slides: 9