Enhanced SAR ADC Energy Efficiency from the Early

![References [1] V. Hariprasath, J. Guerber, S. -H. Lee, U. Moon, “Merged capacitor switching References [1] V. Hariprasath, J. Guerber, S. -H. Lee, U. Moon, “Merged capacitor switching](https://slidetodoc.com/presentation_image_h/e2d483e1195837bbb4f9e9cfd8e97dba/image-16.jpg)

- Slides: 16

Enhanced SAR ADC Energy Efficiency from the Early Reset Merged Capacitor Switching Algorithm Jon Guerber, Hariprasath Venkatram, Taehwan Oh, Un-Ku Moon Oregon State University, Corvallis OR, USA

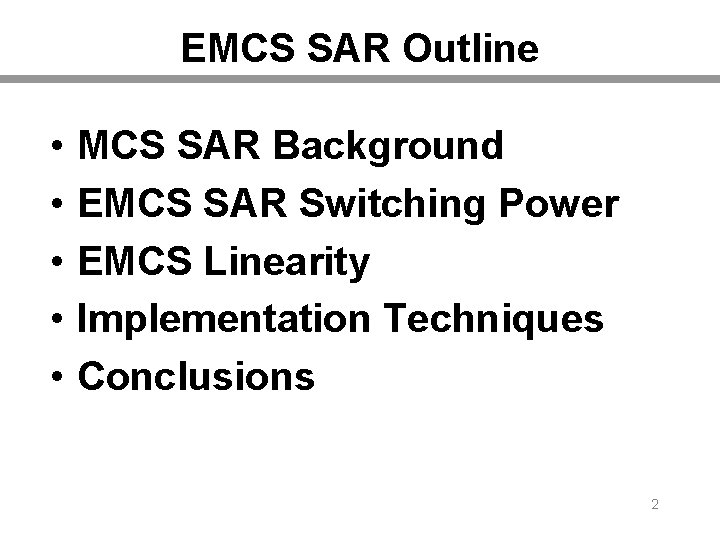

EMCS SAR Outline • • • MCS SAR Background EMCS SAR Switching Power EMCS Linearity Implementation Techniques Conclusions 2

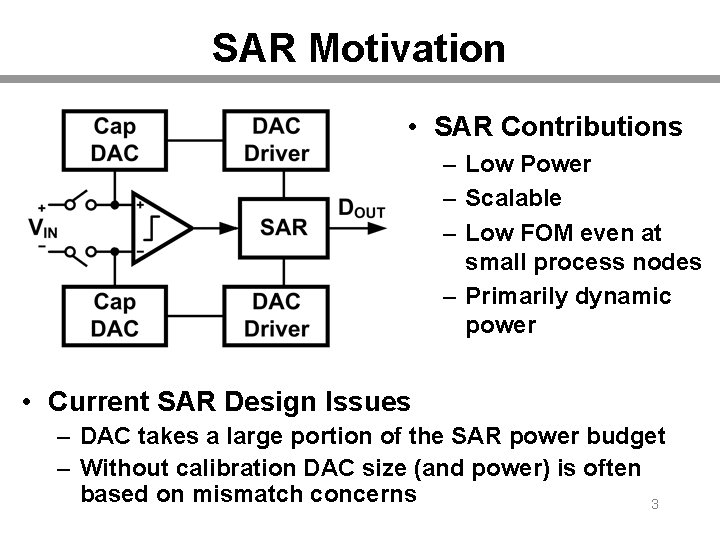

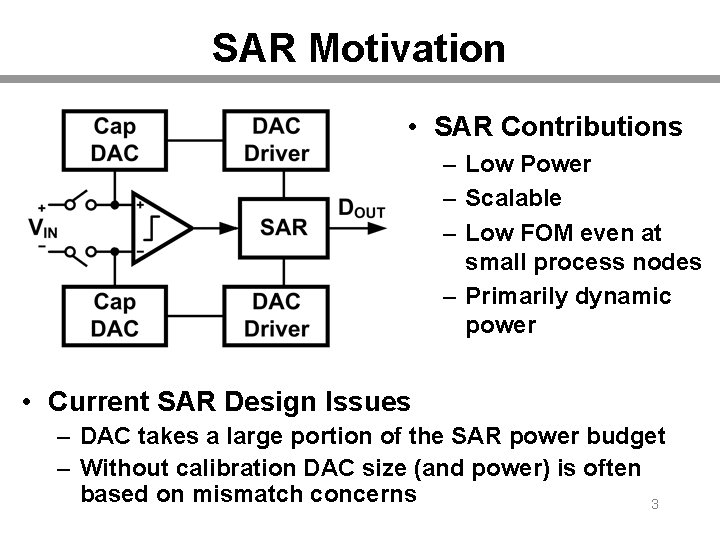

SAR Motivation • SAR Contributions – Low Power – Scalable – Low FOM even at small process nodes – Primarily dynamic power • Current SAR Design Issues – DAC takes a large portion of the SAR power budget – Without calibration DAC size (and power) is often based on mismatch concerns 3

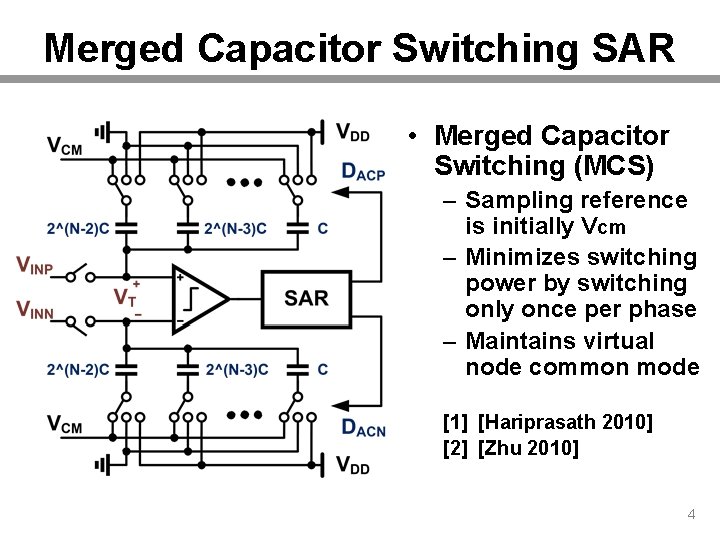

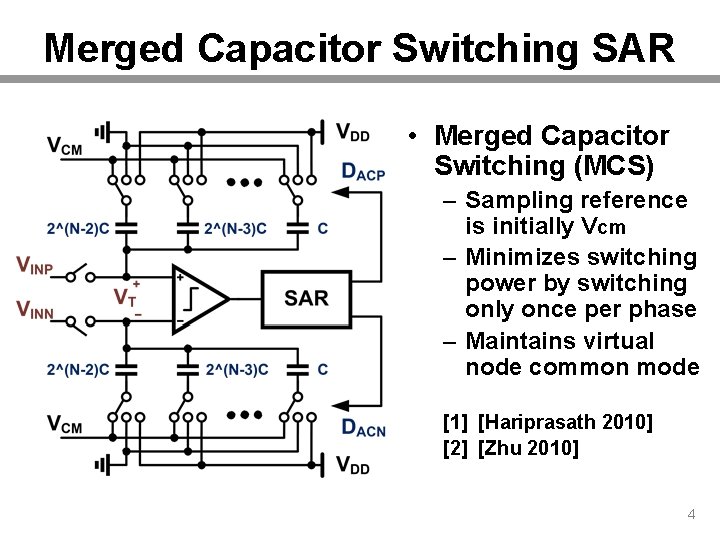

Merged Capacitor Switching SAR • Merged Capacitor Switching (MCS) – Sampling reference is initially Vcm – Minimizes switching power by switching only once per phase – Maintains virtual node common mode [1] [Hariprasath 2010] [2] [Zhu 2010] 4

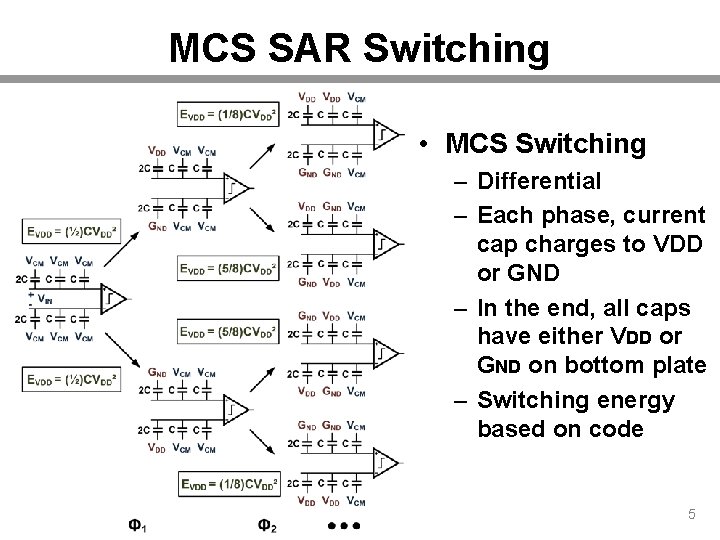

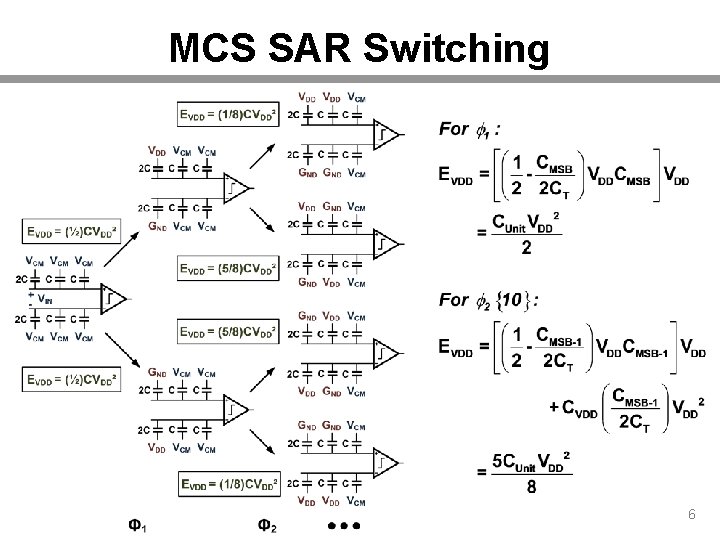

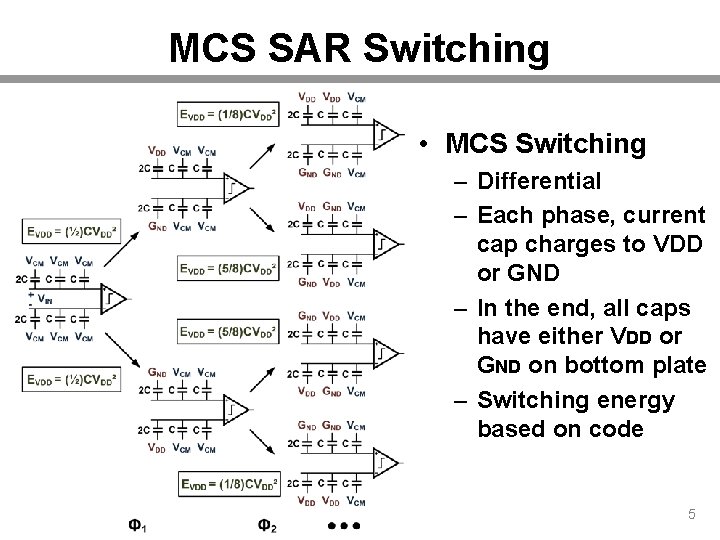

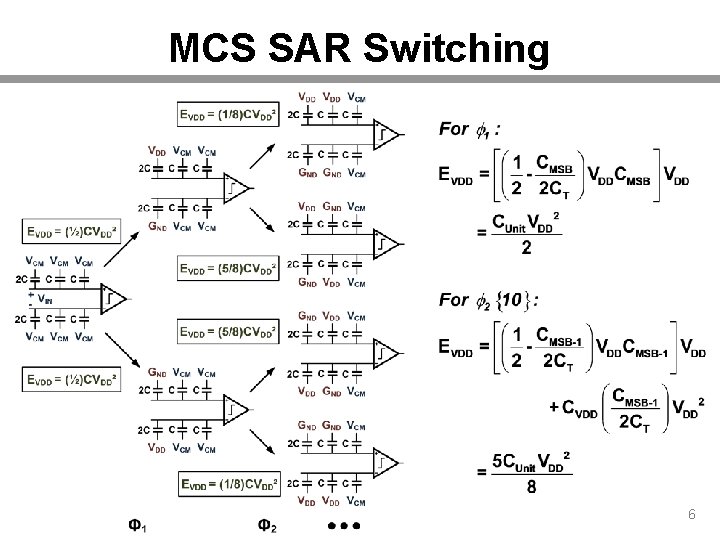

MCS SAR Switching • MCS Switching – Differential – Each phase, current cap charges to VDD or GND – In the end, all caps have either VDD or GND on bottom plate – Switching energy based on code 5

MCS SAR Switching 6

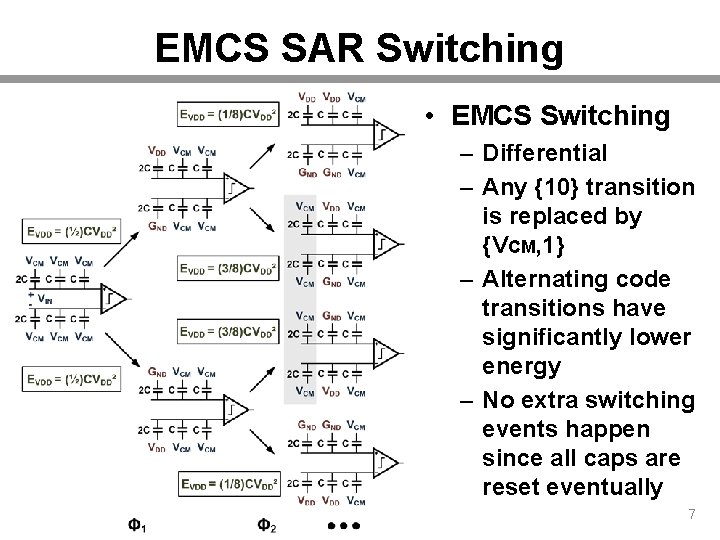

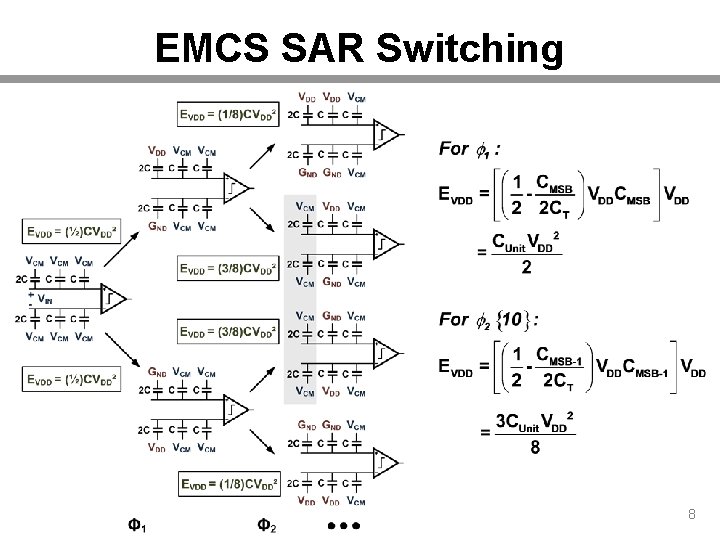

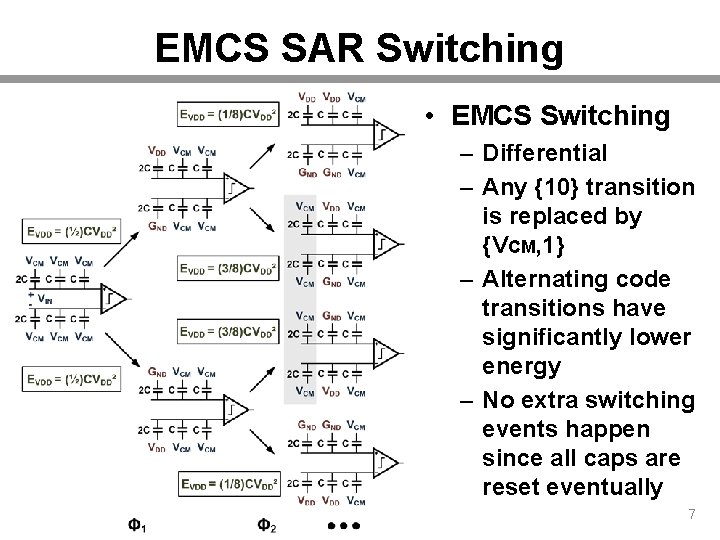

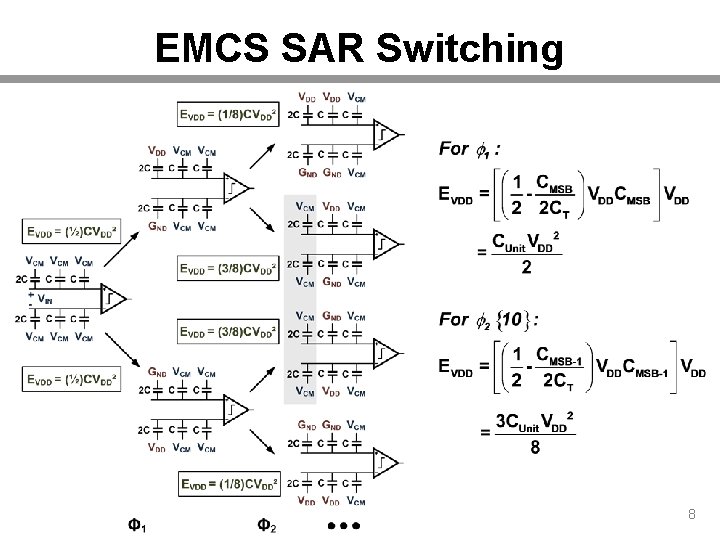

EMCS SAR Switching • EMCS Switching – Differential – Any {10} transition is replaced by {VCM, 1} – Alternating code transitions have significantly lower energy – No extra switching events happen since all caps are reset eventually 7

EMCS SAR Switching 8

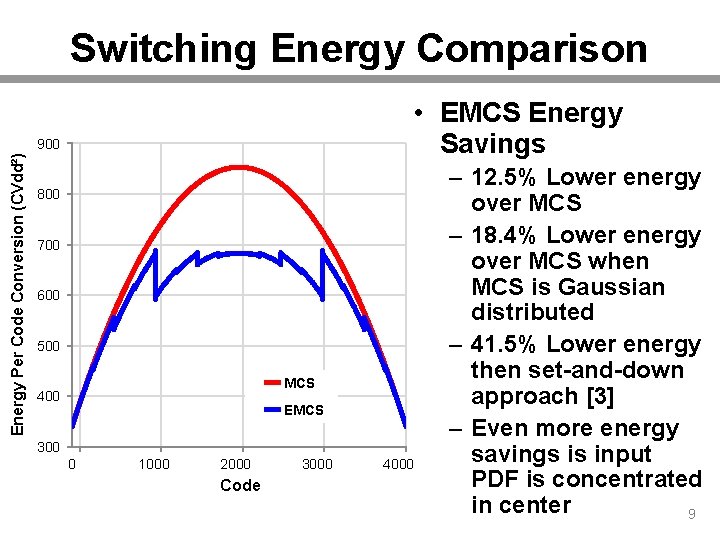

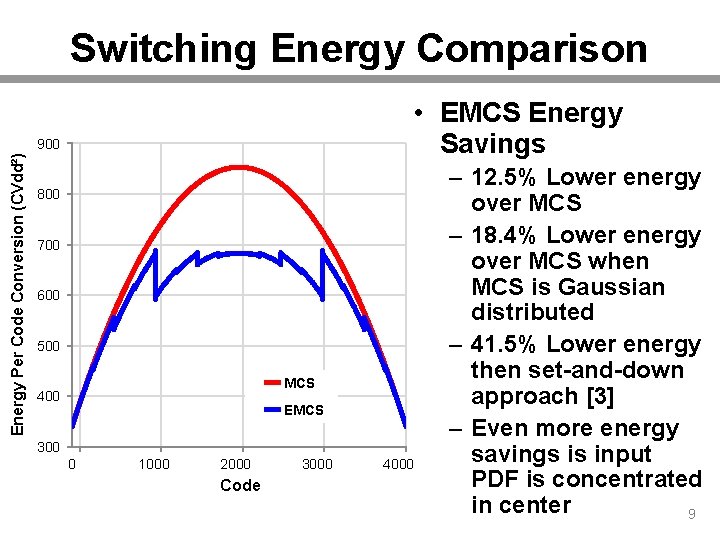

Switching Energy Comparison • EMCS Energy Savings Energy Per Code Conversion (CVdd²) 900 800 700 600 500 MCS 400 EMCS 300 0 1000 2000 Code 3000 4000 – 12. 5% Lower energy over MCS – 18. 4% Lower energy over MCS when MCS is Gaussian distributed – 41. 5% Lower energy then set-and-down approach [3] – Even more energy savings is input PDF is concentrated in center 9

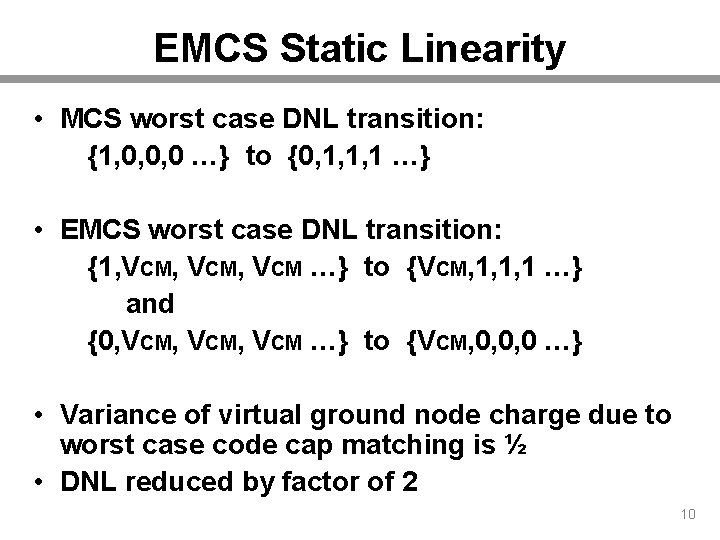

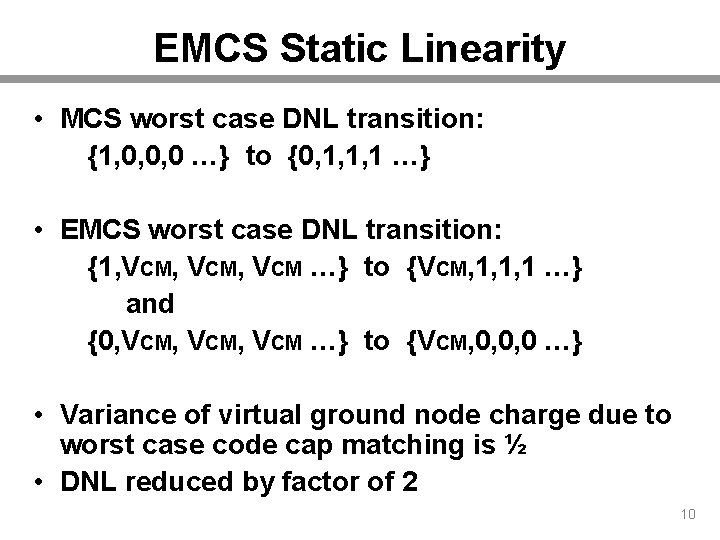

EMCS Static Linearity • MCS worst case DNL transition: {1, 0, 0, 0 …} to {0, 1, 1, 1 …} • EMCS worst case DNL transition: {1, VCM, VCM …} to {VCM, 1, 1, 1 …} and {0, VCM, VCM …} to {VCM, 0, 0, 0 …} • Variance of virtual ground node charge due to worst case code cap matching is ½ • DNL reduced by factor of 2 10

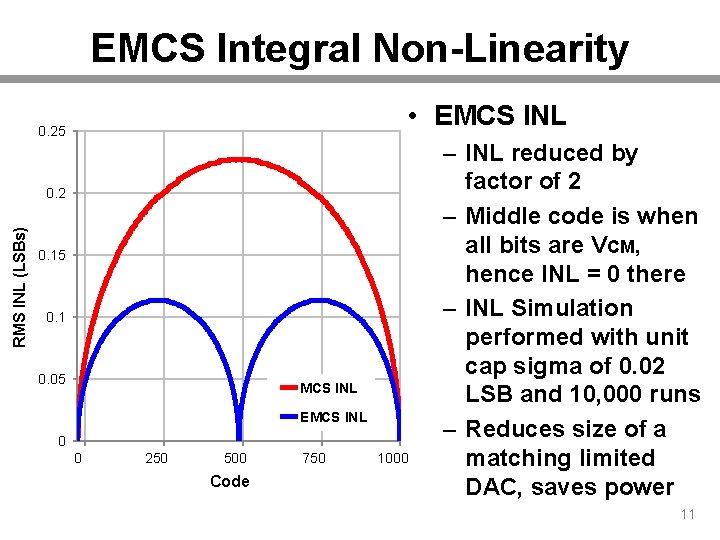

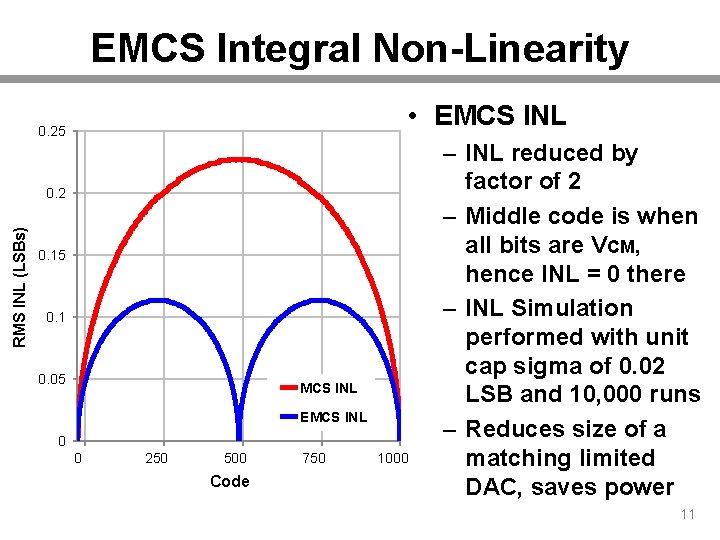

EMCS Integral Non-Linearity • EMCS INL 0. 25 RMS INL (LSBs) 0. 2 0. 15 0. 1 0. 05 MCS INL EMCS INL 0 0 250 500 Code 750 1000 – INL reduced by factor of 2 – Middle code is when all bits are VCM, hence INL = 0 there – INL Simulation performed with unit cap sigma of 0. 02 LSB and 10, 000 runs – Reduces size of a matching limited DAC, saves power 11

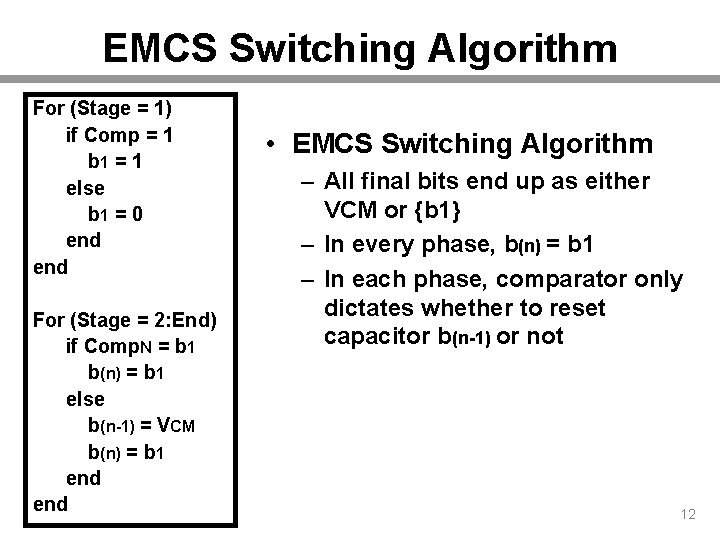

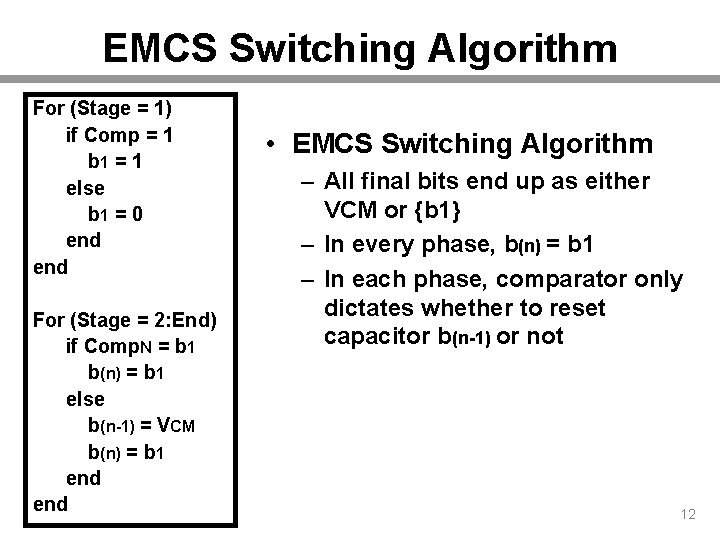

EMCS Switching Algorithm For (Stage = 1) if Comp = 1 b 1 = 1 else b 1 = 0 end For (Stage = 2: End) if Comp. N = b 1 b(n) = b 1 else b(n-1) = VCM b(n) = b 1 end • EMCS Switching Algorithm – All final bits end up as either VCM or {b 1} – In every phase, b(n) = b 1 – In each phase, comparator only dictates whether to reset capacitor b(n-1) or not 12

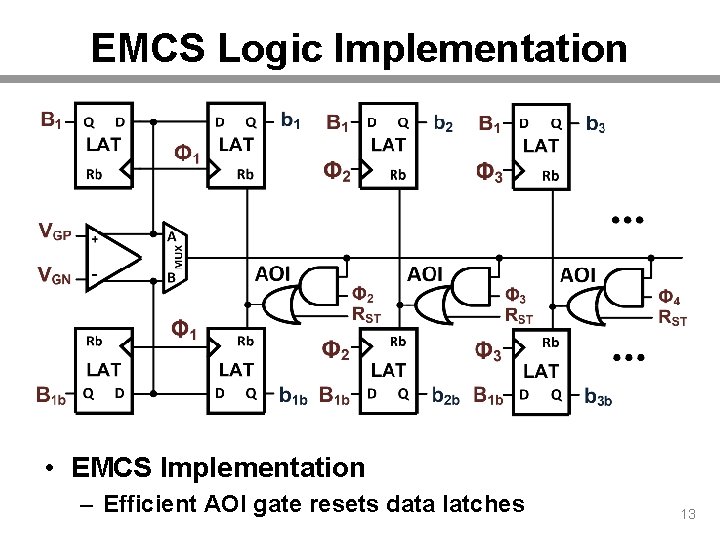

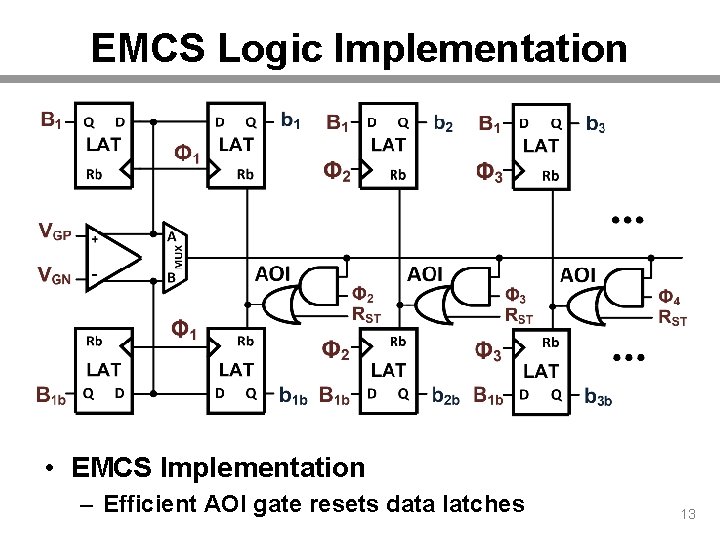

EMCS Logic Implementation • EMCS Implementation – Efficient AOI gate resets data latches 13

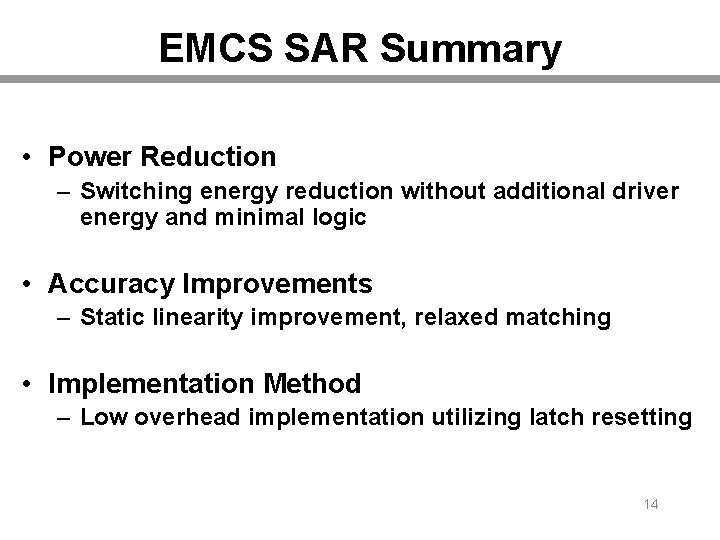

EMCS SAR Summary • Power Reduction – Switching energy reduction without additional driver energy and minimal logic • Accuracy Improvements – Static linearity improvement, relaxed matching • Implementation Method – Low overhead implementation utilizing latch resetting 14

Questions 15

![References 1 V Hariprasath J Guerber S H Lee U Moon Merged capacitor switching References [1] V. Hariprasath, J. Guerber, S. -H. Lee, U. Moon, “Merged capacitor switching](https://slidetodoc.com/presentation_image_h/e2d483e1195837bbb4f9e9cfd8e97dba/image-16.jpg)

References [1] V. Hariprasath, J. Guerber, S. -H. Lee, U. Moon, “Merged capacitor switching based SAR ADC with highest switching energyefficiency, ” Electron. Lett. , vol. 46, pp. 620 -621, Apr. 2010. [2] Y. Zhu, C. -H. Chan, U. Cho, S. -W. Sin, S. -P. U, R. Martins, F. Maloberti, “A 10 -bit 100 -MS/s reference-free SAR ADC in 90 nm CMOS, ” IEEE J. Solid-State Circuits, vol. 45, no. 6, pp. 1111 -1120, Jun. 2010. [3] B. Ginsburg and A. Chandrakasen, “An energy efficient charge recycling approach for a SAR converter with capacitive DAC, ” Proc. of IEEE Int. Sym. On Circuits and Systems, ISCAS, pp. 184 -187, 2005. 16