Engineering Technology State Machines in VHDL Dr H

- Slides: 27

Engineering Technology State Machines in VHDL Dr. H. v. d. Biggelaar 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / March 22, 2000 1

State Machines Moore Mealy 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 2

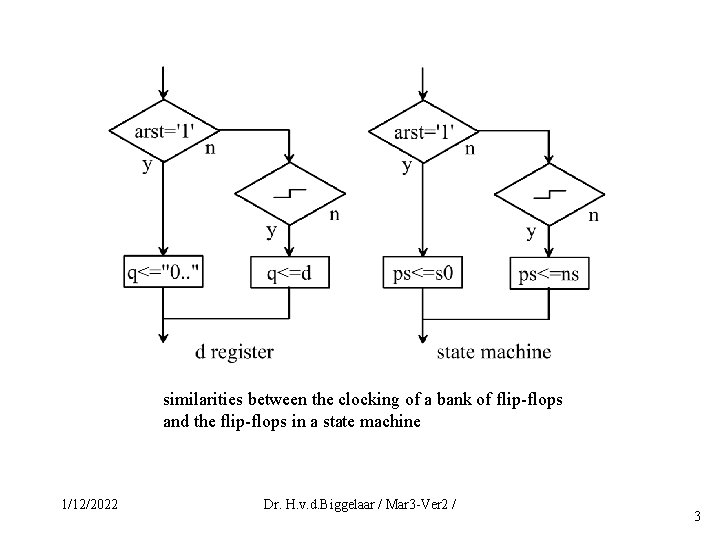

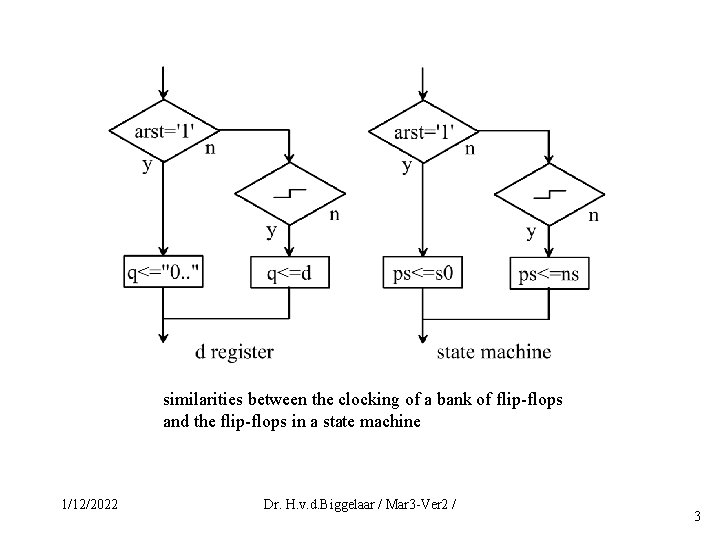

similarities between the clocking of a bank of flip-flops and the flip-flops in a state machine 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 3

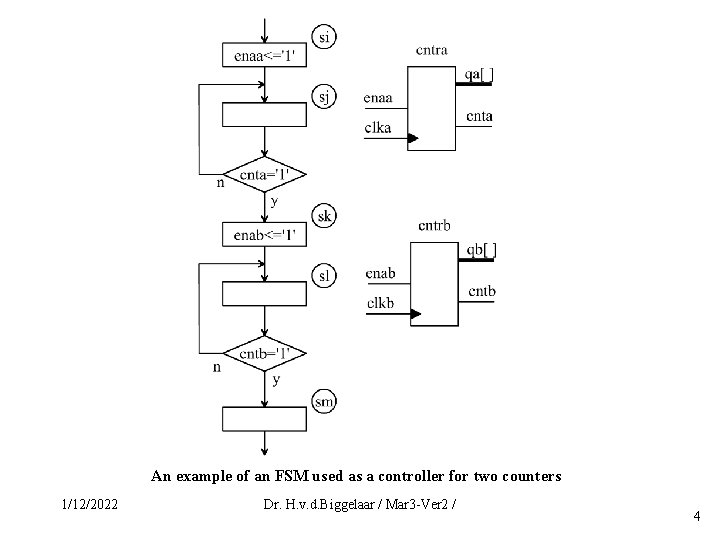

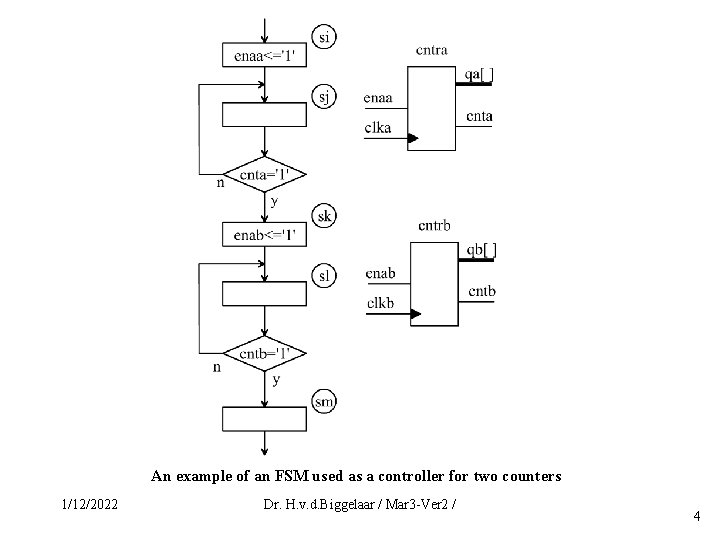

An example of an FSM used as a controller for two counters 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 4

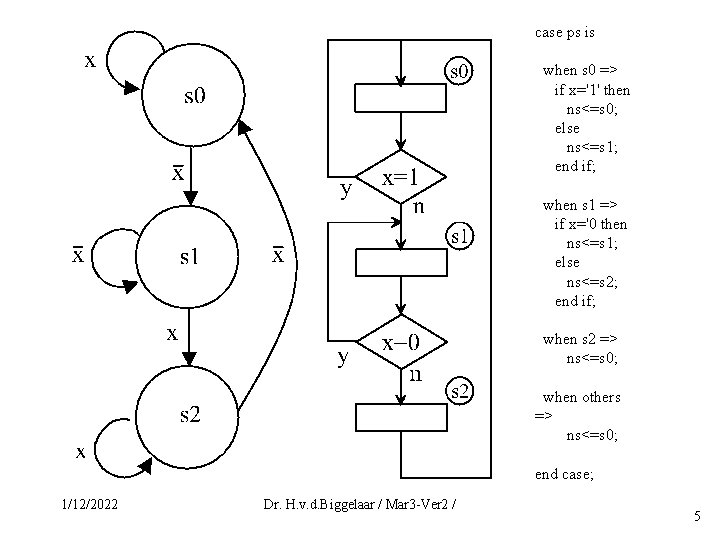

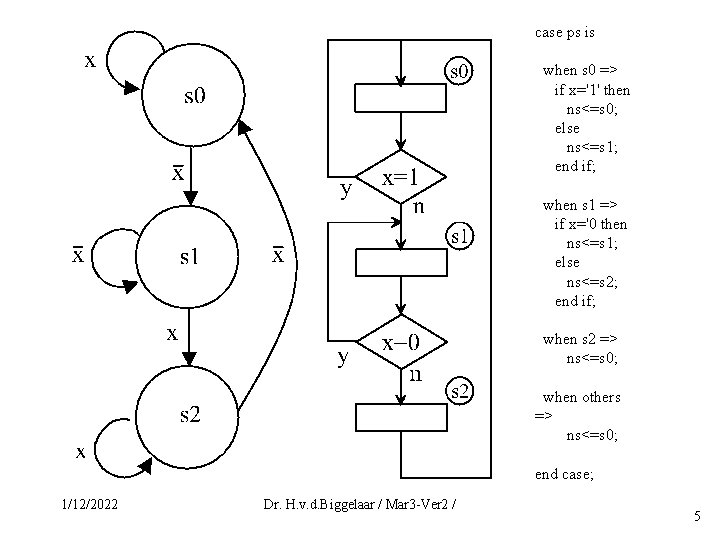

case ps is when s 0 => if x='1' then ns<=s 0; else ns<=s 1; end if; when s 1 => if x='0 then ns<=s 1; else ns<=s 2; end if; when s 2 => ns<=s 0; when others => ns<=s 0; end case; 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 5

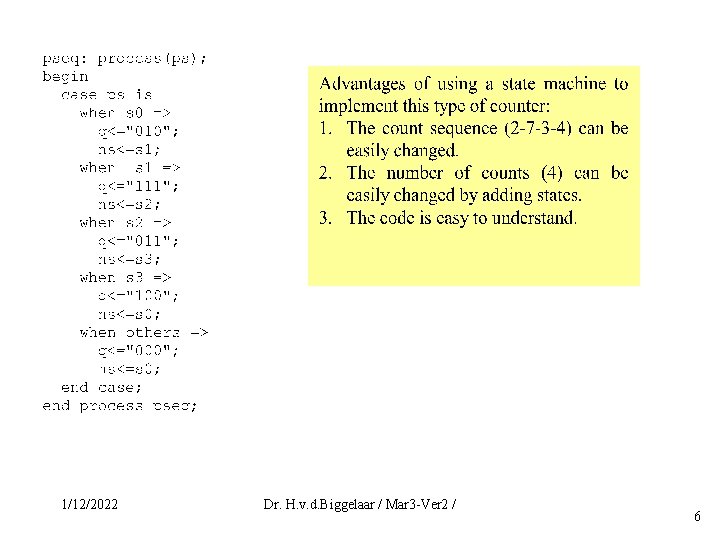

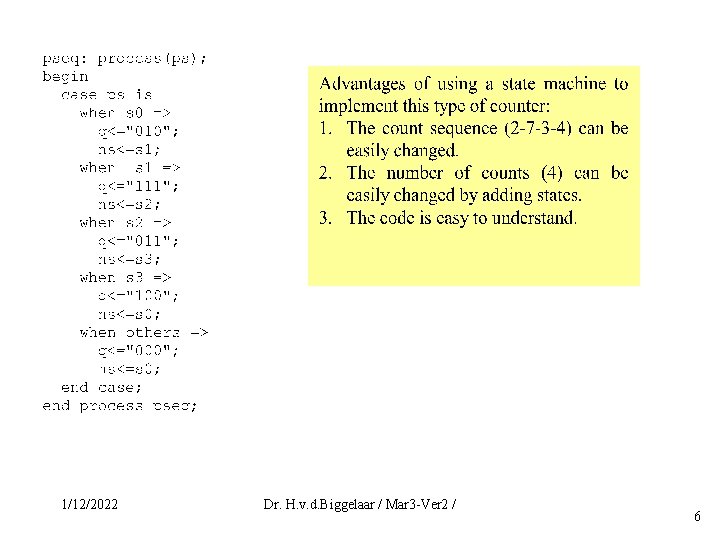

1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 6

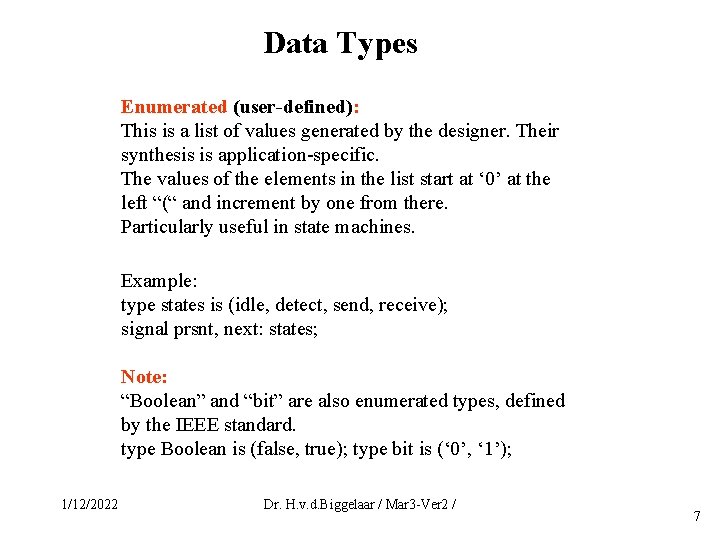

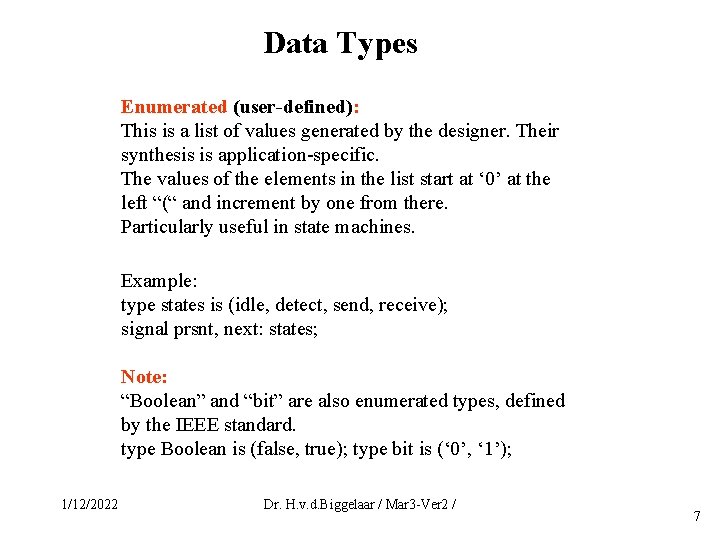

Data Types Enumerated (user-defined): This is a list of values generated by the designer. Their synthesis is application-specific. The values of the elements in the list start at ‘ 0’ at the left “(“ and increment by one from there. Particularly useful in state machines. Example: type states is (idle, detect, send, receive); signal prsnt, next: states; Note: “Boolean” and “bit” are also enumerated types, defined by the IEEE standard. type Boolean is (false, true); type bit is (‘ 0’, ‘ 1’); 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 7

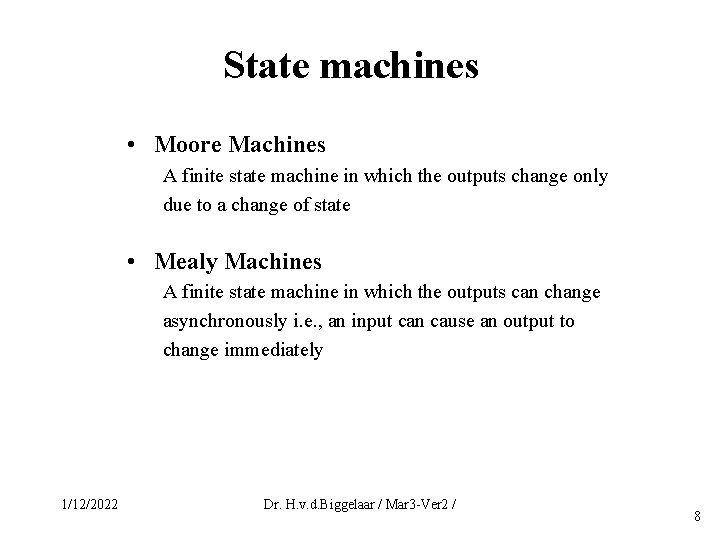

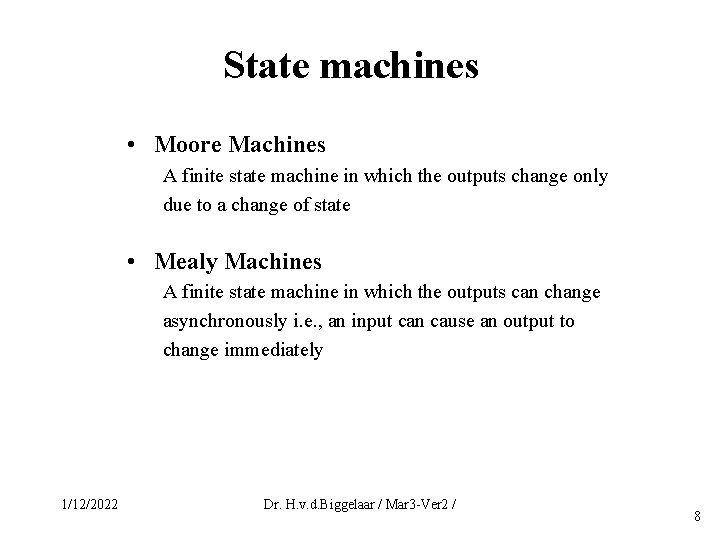

State machines • Moore Machines A finite state machine in which the outputs change only due to a change of state • Mealy Machines A finite state machine in which the outputs can change asynchronously i. e. , an input can cause an output to change immediately 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 8

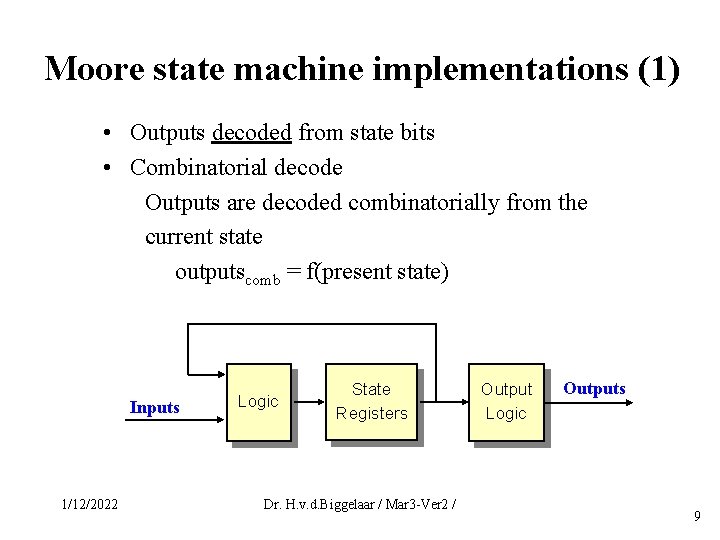

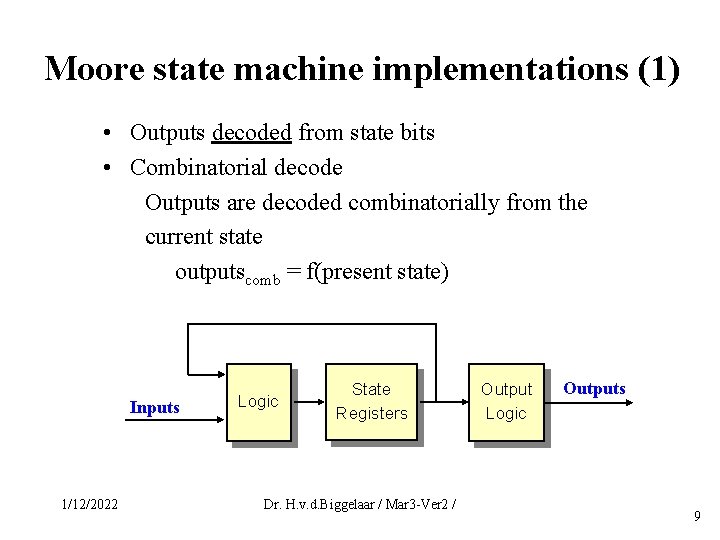

Moore state machine implementations (1) • Outputs decoded from state bits • Combinatorial decode Outputs are decoded combinatorially from the current state outputscomb = f(present state) Inputs 1/12/2022 Logic State Registers Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / Output Logic Outputs 9

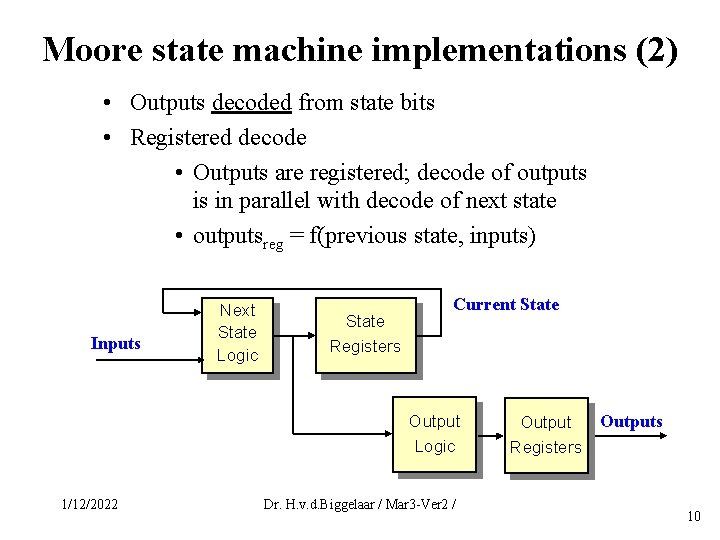

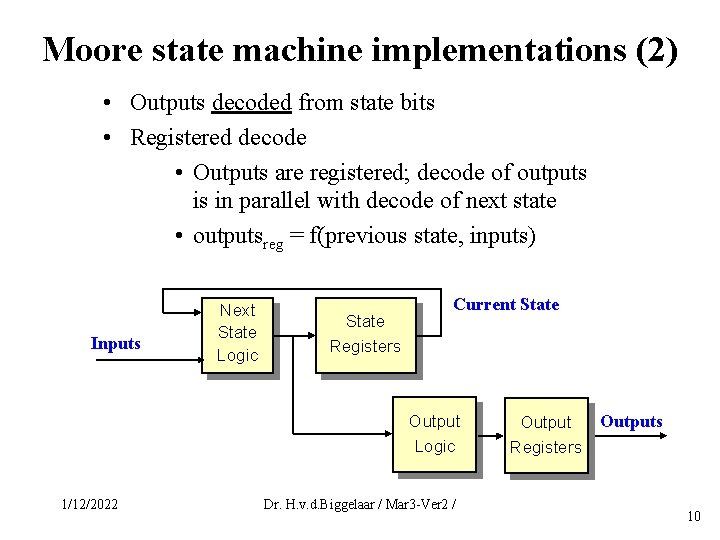

Moore state machine implementations (2) • Outputs decoded from state bits • Registered decode • Outputs are registered; decode of outputs is in parallel with decode of next state • outputsreg = f(previous state, inputs) Inputs Next State Logic State Registers Current State Output Logic 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / Output Registers Outputs 10

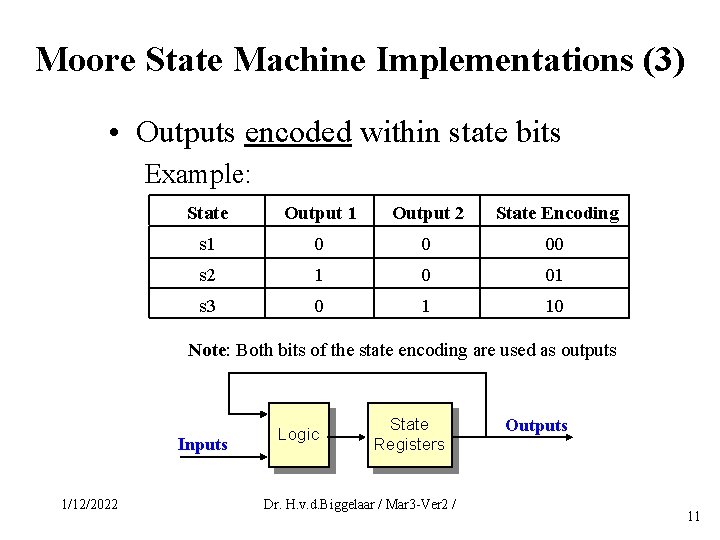

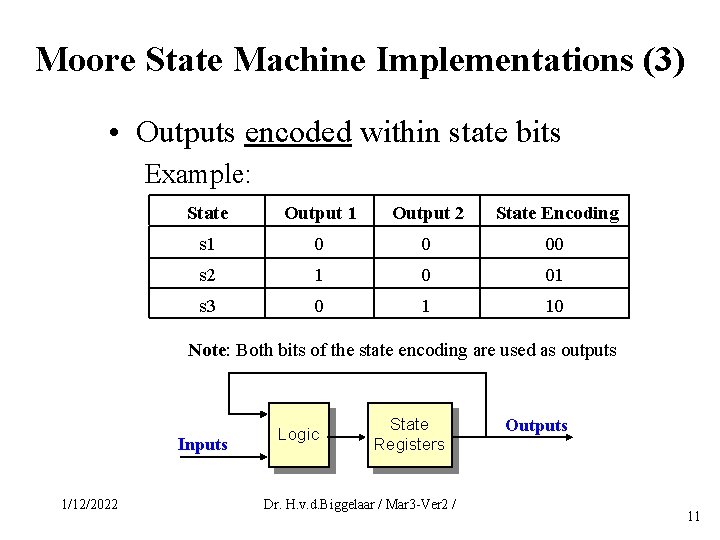

Moore State Machine Implementations (3) • Outputs encoded within state bits Example: State Output 1 Output 2 State Encoding s 1 0 0 00 s 2 1 0 01 s 3 0 1 10 Note: Both bits of the state encoding are used as outputs Inputs 1/12/2022 Logic State Registers Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / Outputs 11

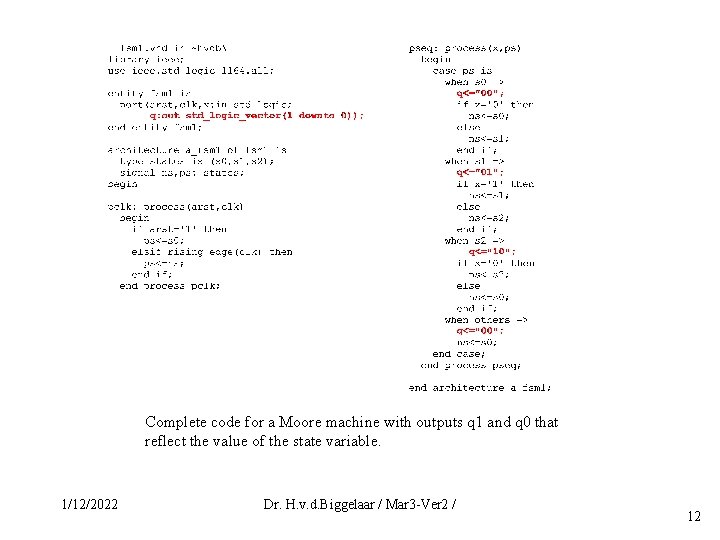

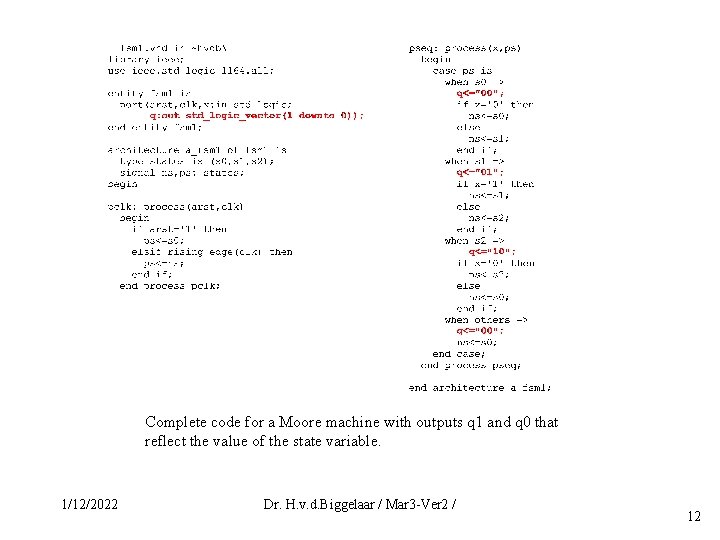

Complete code for a Moore machine with outputs q 1 and q 0 that reflect the value of the state variable. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 12

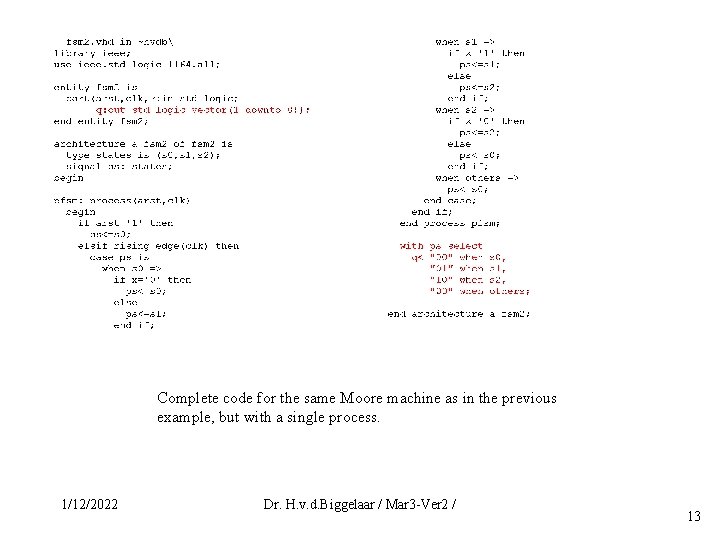

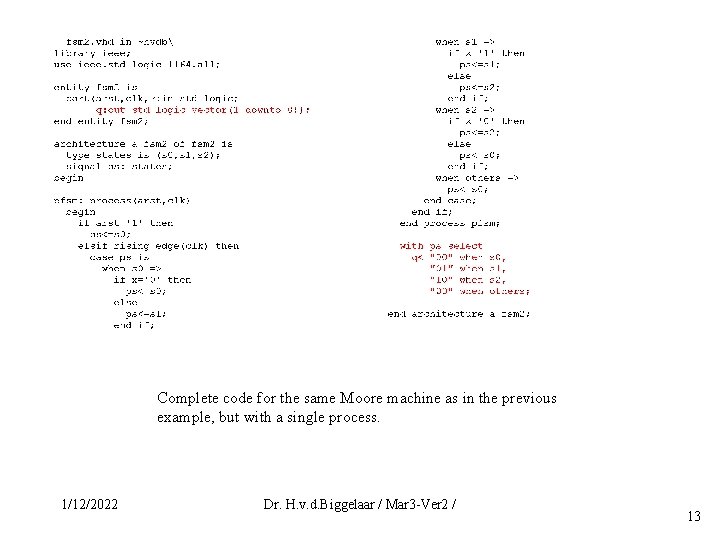

Complete code for the same Moore machine as in the previous example, but with a single process. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 13

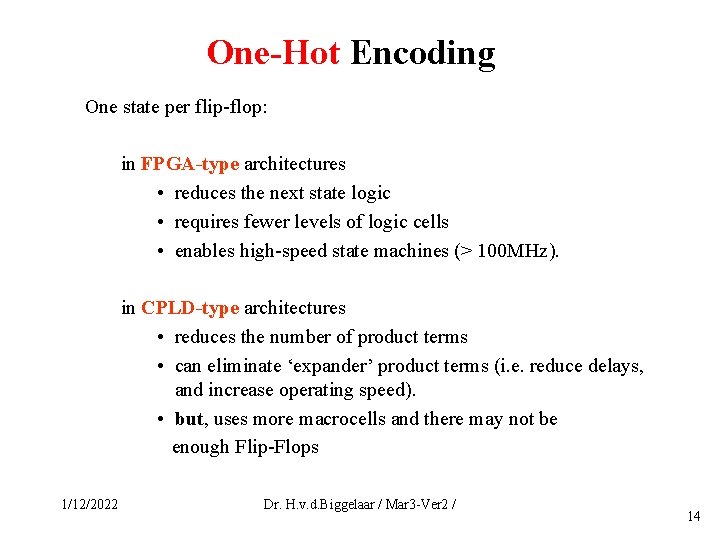

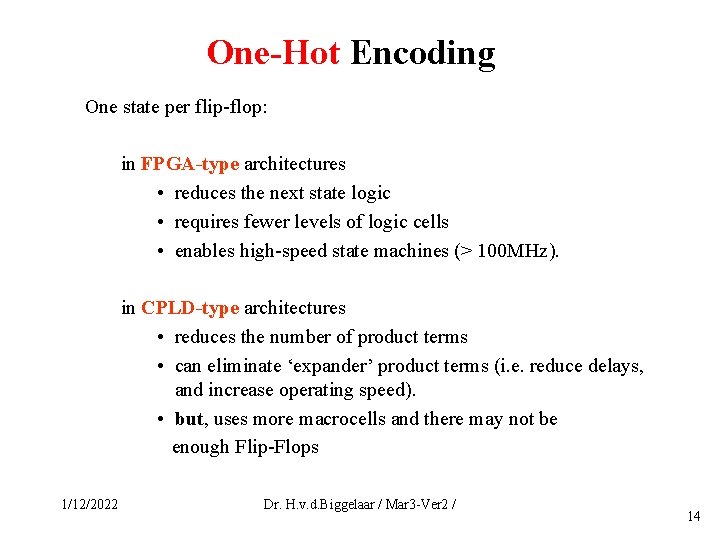

One-Hot Encoding One state per flip-flop: in FPGA-type architectures • reduces the next state logic • requires fewer levels of logic cells • enables high-speed state machines (> 100 MHz). in CPLD-type architectures • reduces the number of product terms • can eliminate ‘expander’ product terms (i. e. reduce delays, and increase operating speed). • but, uses more macrocells and there may not be enough Flip-Flops 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 14

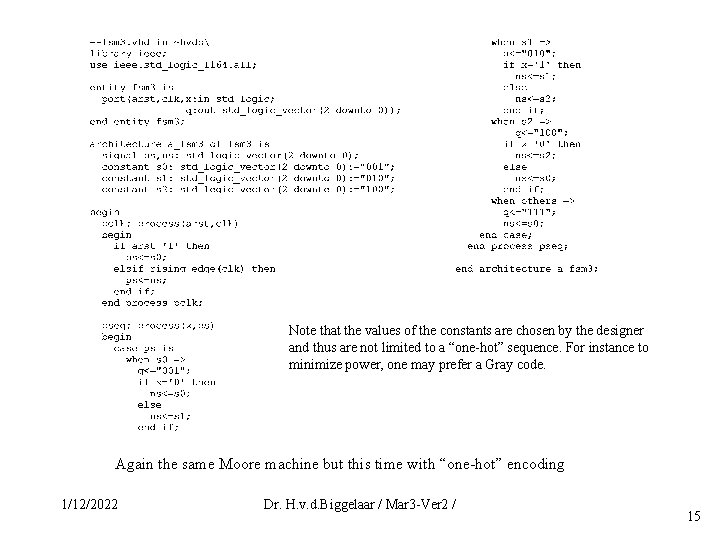

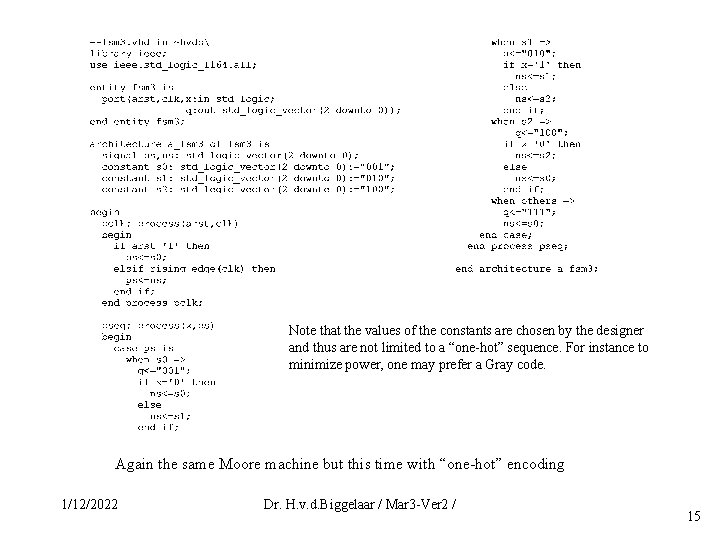

Note that the values of the constants are chosen by the designer and thus are not limited to a “one-hot” sequence. For instance to minimize power, one may prefer a Gray code. Again the same Moore machine but this time with “one-hot” encoding 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 15

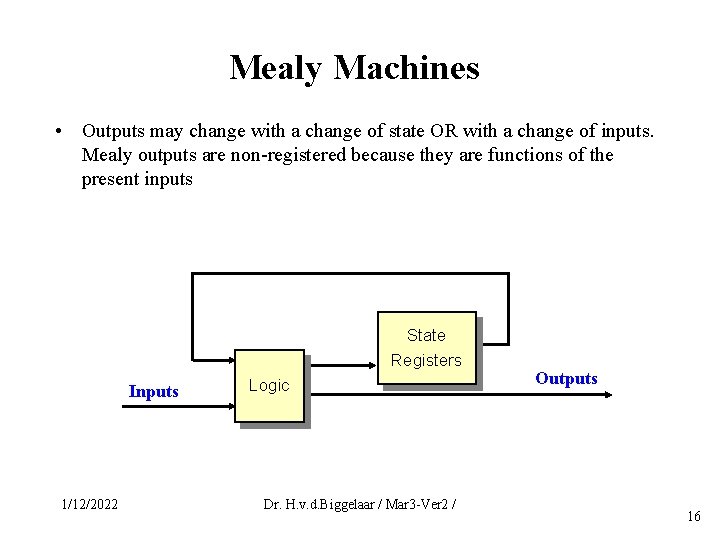

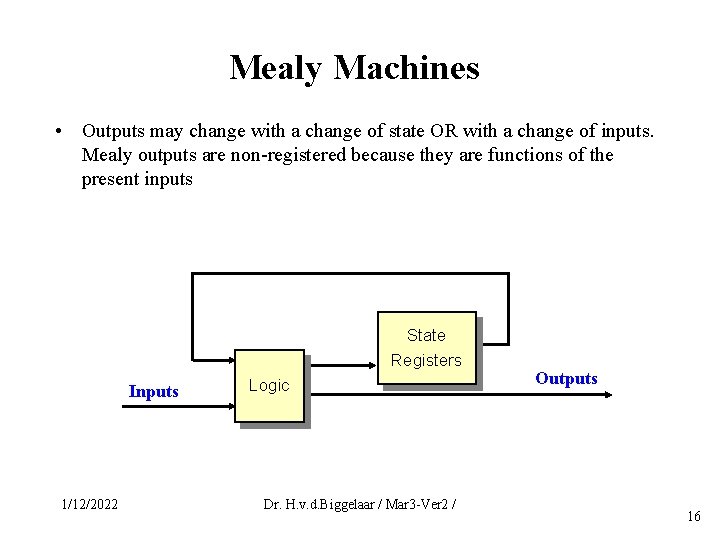

Mealy Machines • Outputs may change with a change of state OR with a change of inputs. Mealy outputs are non-registered because they are functions of the present inputs State Registers Inputs 1/12/2022 Logic Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / Outputs 16

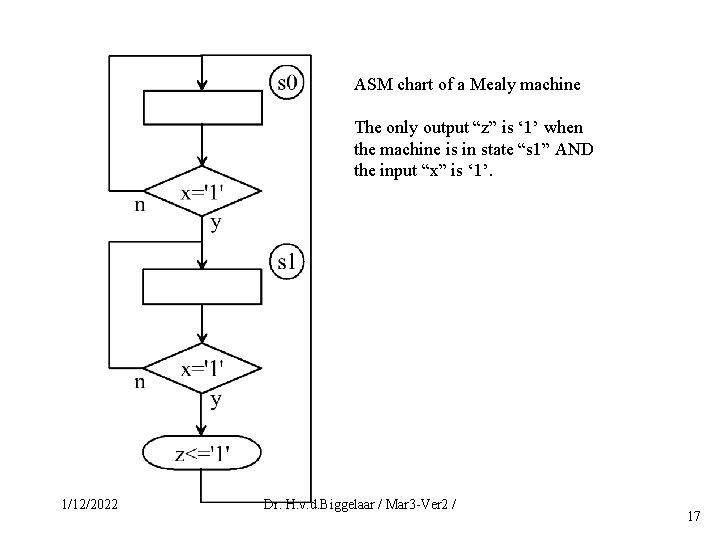

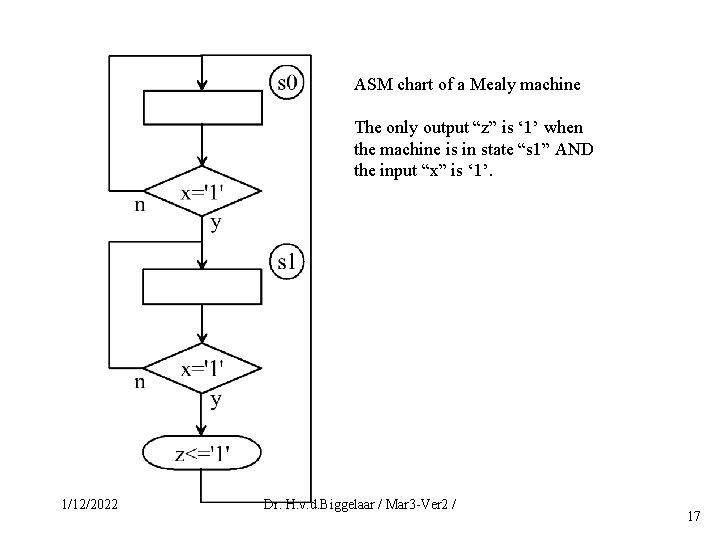

ASM chart of a Mealy machine The only output “z” is ‘ 1’ when the machine is in state “s 1” AND the input “x” is ‘ 1’. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 17

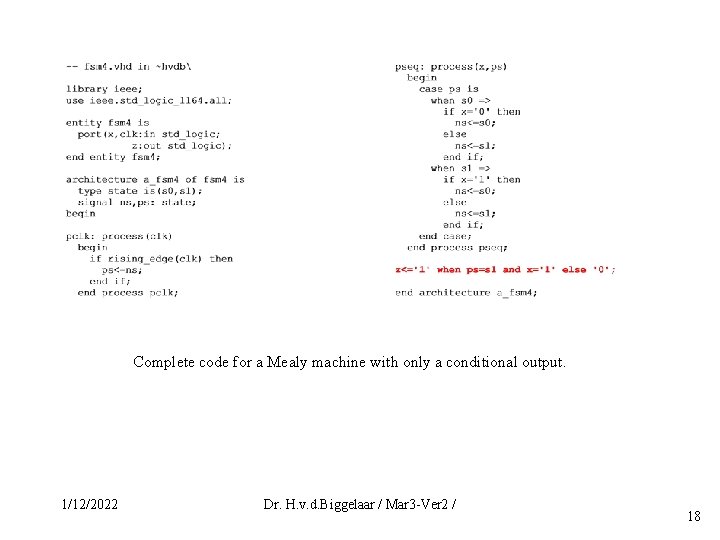

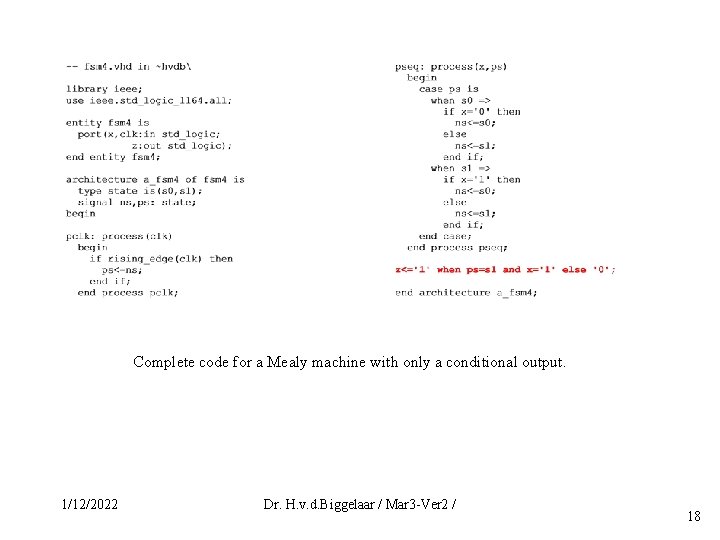

Complete code for a Mealy machine with only a conditional output. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 18

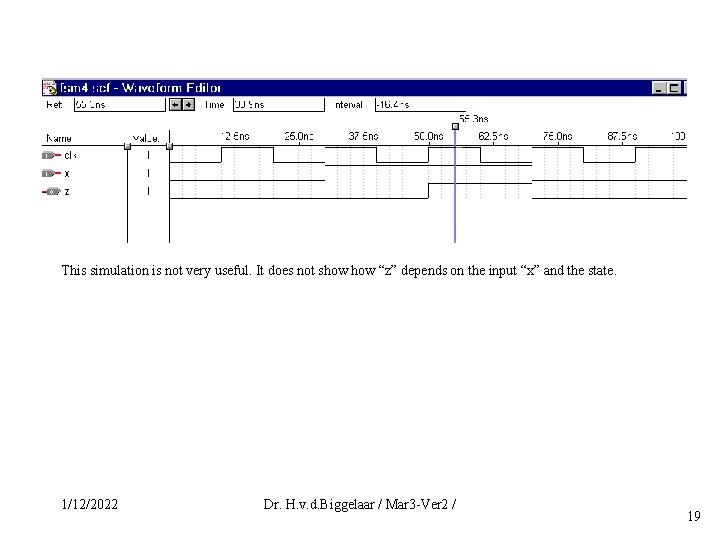

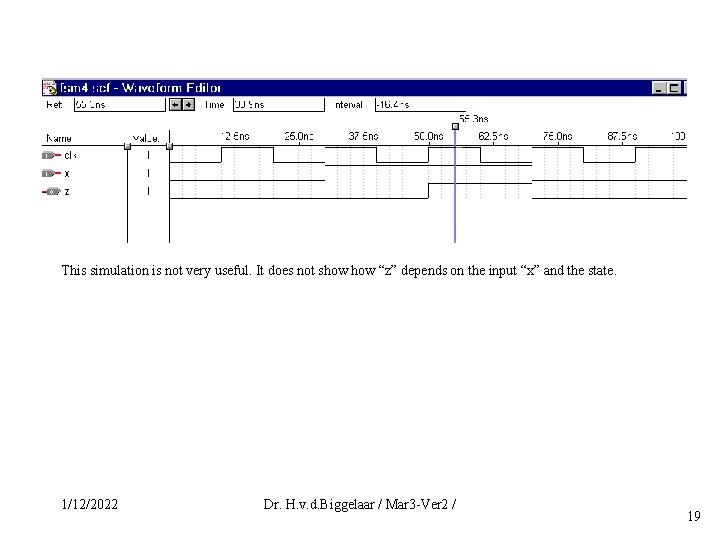

This simulation is not very useful. It does not show “z” depends on the input “x” and the state. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 19

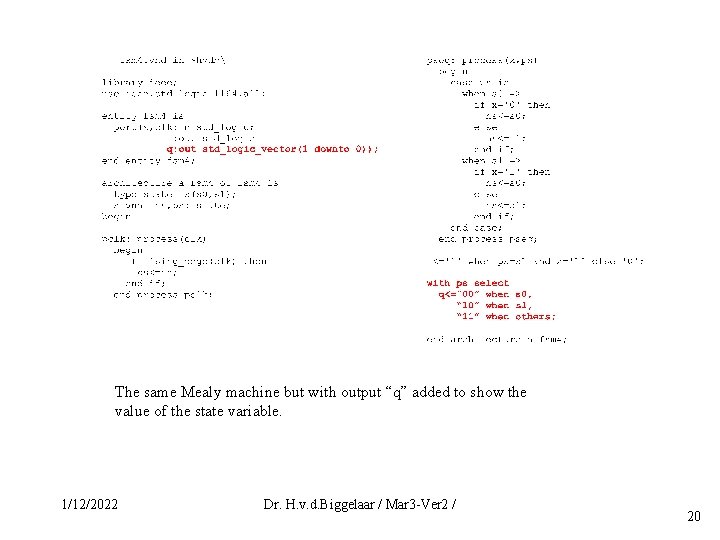

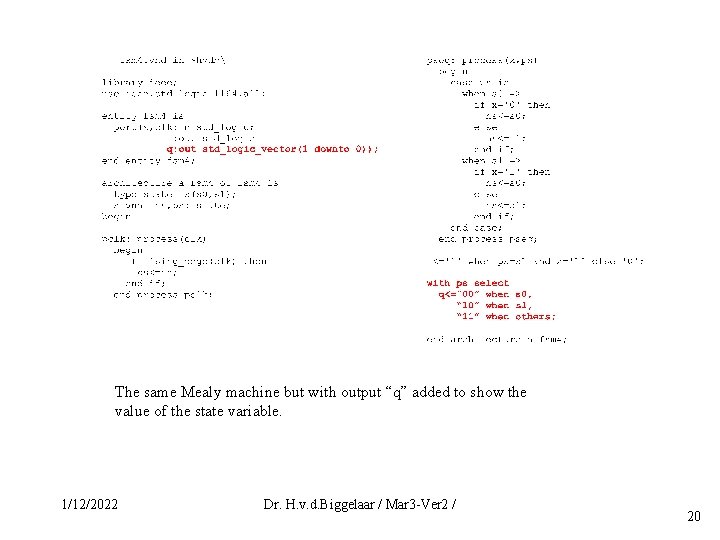

The same Mealy machine but with output “q” added to show the value of the state variable. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 20

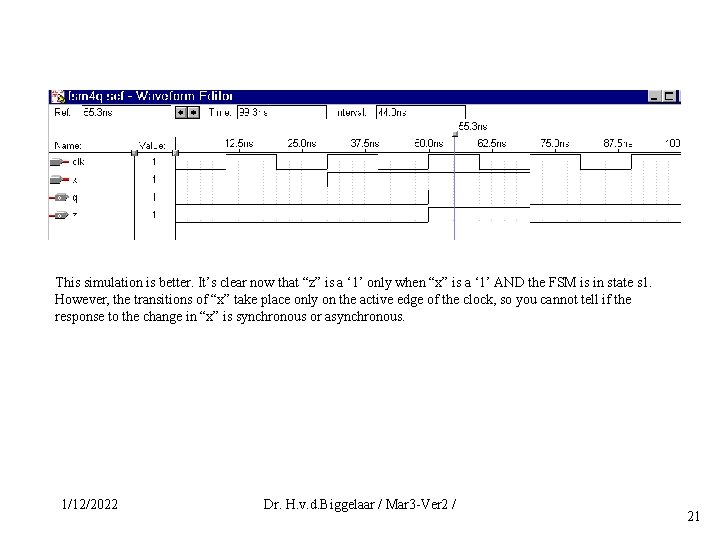

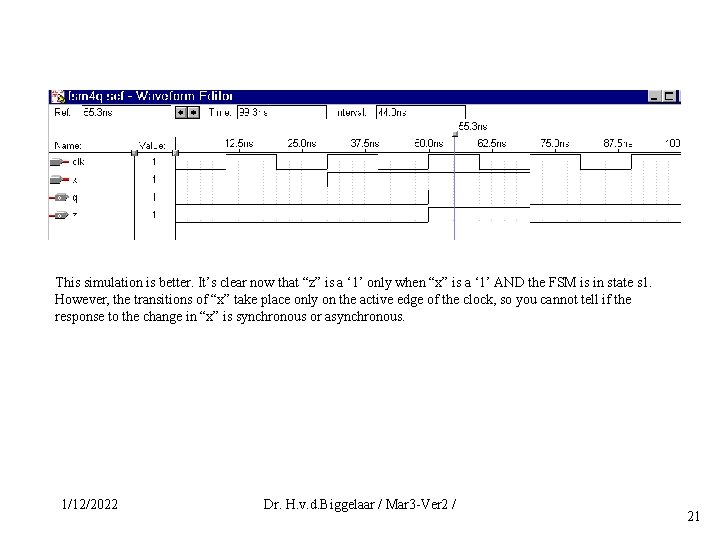

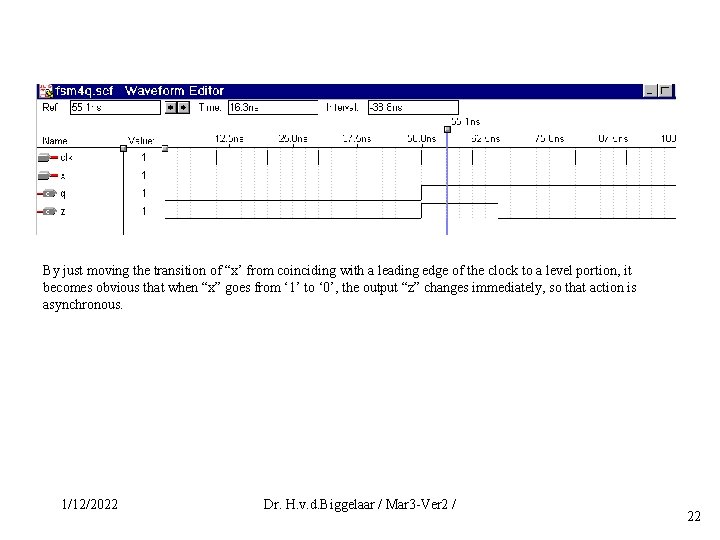

This simulation is better. It’s clear now that “z” is a ‘ 1’ only when “x” is a ‘ 1’ AND the FSM is in state s 1. However, the transitions of “x” take place only on the active edge of the clock, so you cannot tell if the response to the change in “x” is synchronous or asynchronous. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 21

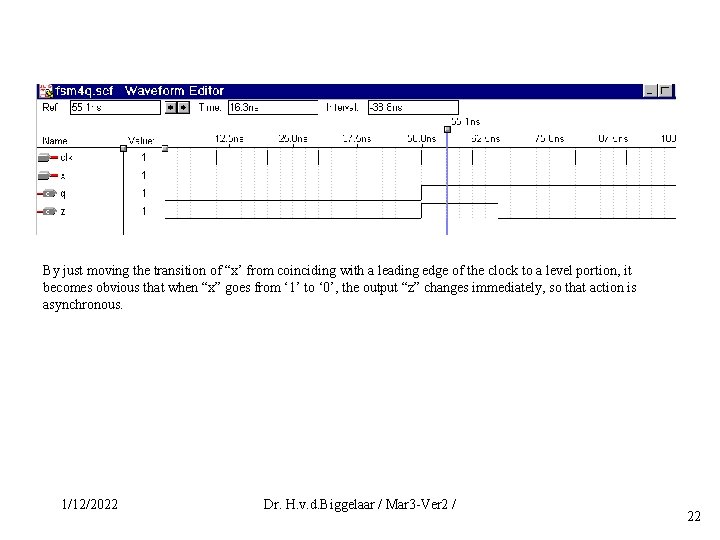

By just moving the transition of “x’ from coinciding with a leading edge of the clock to a level portion, it becomes obvious that when “x” goes from ‘ 1’ to ‘ 0’, the output “z” changes immediately, so that action is asynchronous. 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 22

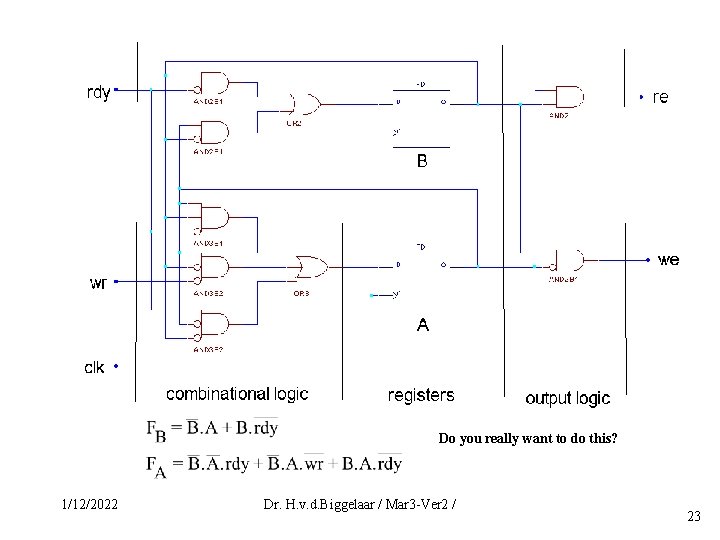

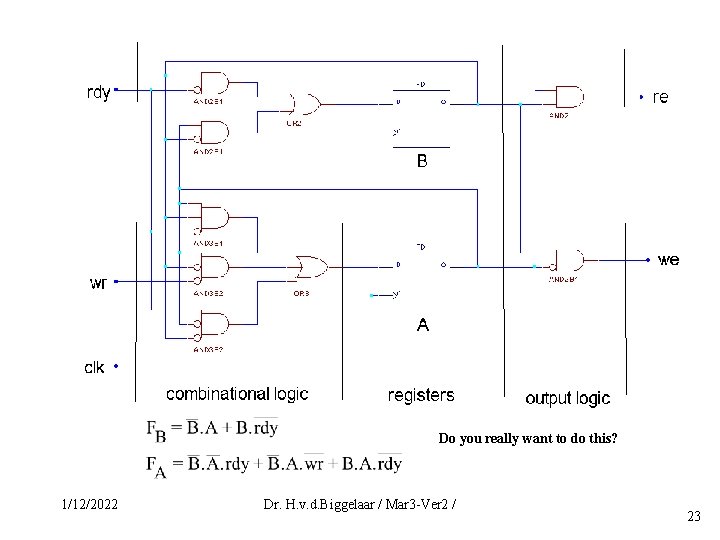

Do you really want to do this? 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 23

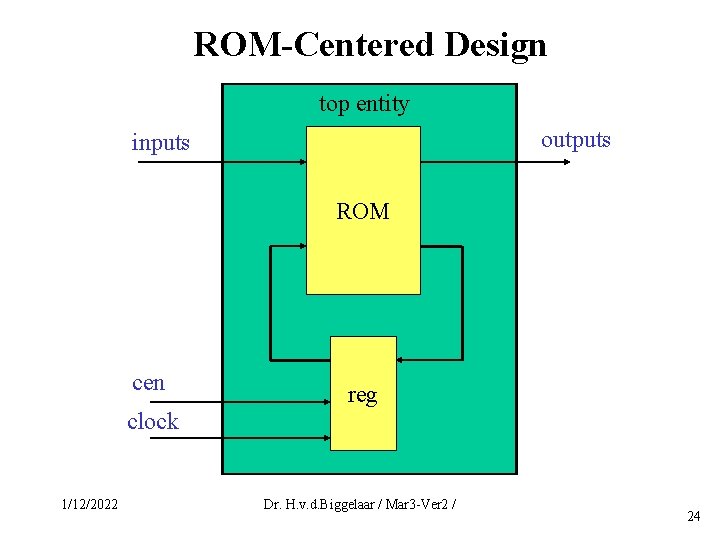

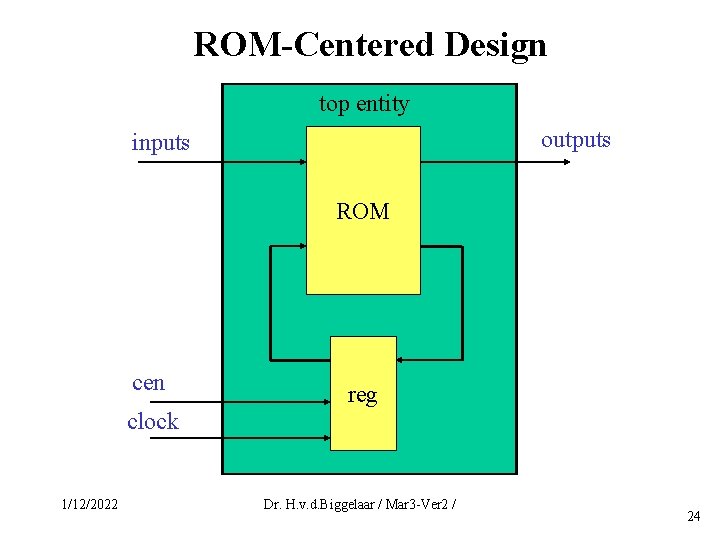

ROM-Centered Design top entity outputs inputs ROM cen reg clock 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 24

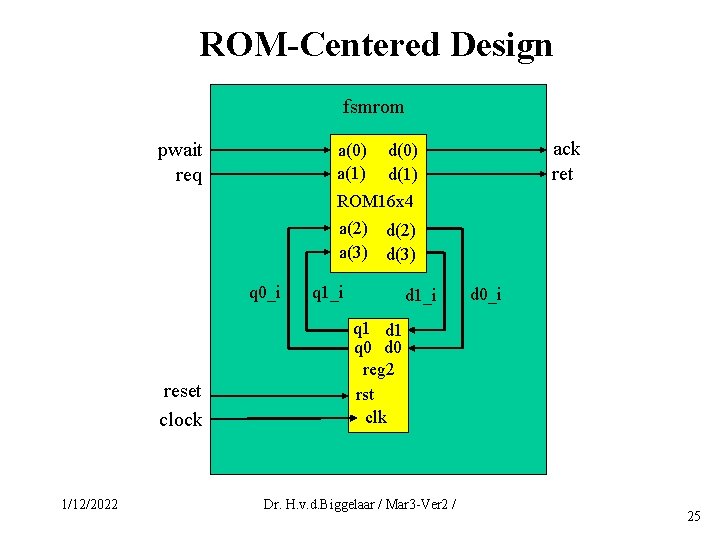

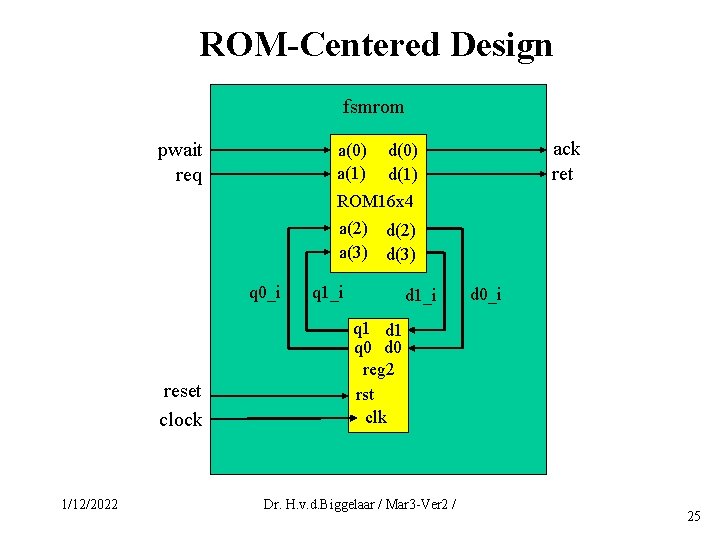

ROM-Centered Design fsmrom pwait req d(0) d(1) ROM 16 x 4 a(2) d(2) a(3) d(3) q 0_i reset clock 1/12/2022 ack ret a(0) a(1) q 1_i d 0_i q 1 d 1 q 0 d 0 reg 2 rst clk Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 25

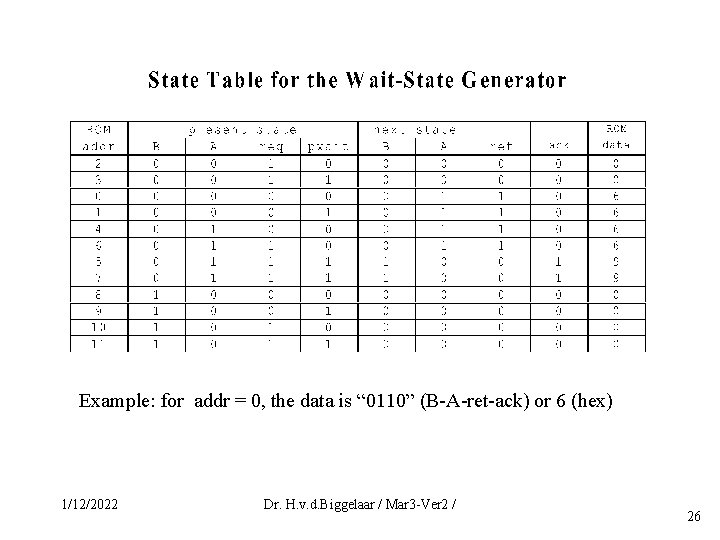

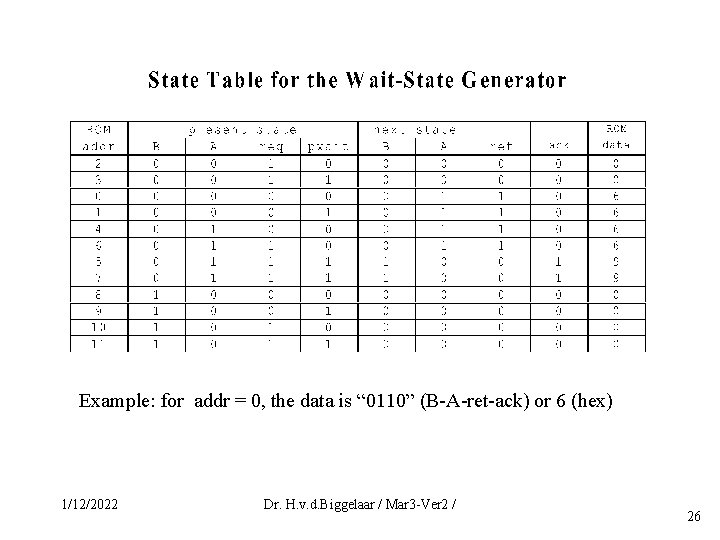

Example: for addr = 0, the data is “ 0110” (B-A-ret-ack) or 6 (hex) 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 26

And that’s IT for State Machines 1/12/2022 Dr. H. v. d. Biggelaar / Mar 3 -Ver 2 / 27