Engineering Models and Circuit Realization of Quantum State

- Slides: 30

Engineering Models and Circuit Realization of Quantum State Machines

5. Complete Automated System for Design of QSM

5. 1. Complete Automated System for Design of QSM 1. Use state minimization/state assignment techniques available in the Berkeley tools to obtain various encoded ( and/or minimized ) flavors of the machine 2. Use DCARL/MMD to find the reversible logic solutions for all flavors of the encoded machine 3. Analyze the results and come up with the best state minimization / encoding strategy that works for reversible logic implementation of the FSM 4. Use the Benchmark circuits for the input FSM’s

Problem Definition • State assignment problem – Involves assigning binary coded values to the states of an FSM – The target is to minimize the area of the combinational circuit required to realize the FSM – The complexity of the combinational component of the FSM depends heavily on the state assignment and selection of memory elements • Creating completely specified functions – Done by assigning values to the “don’t care” outputs to produce reversible logic

Tools and Flow

Tools and Flow • Available Berkeley tools – MVSIS, VIS • SIS – System for Sequential circuit synthesis • MVSIS – for multiple valued logic synthesis, does not implement sequential logic yet • VIS – Verification tool for sequential logic, calls SIS to do the optimization for any given state machine • SIS available 1. 2 for Windows and 1. 3 for Linux • Can be downloaded from http: //embedded. eecs. berkeley. edu/pubs/downloads/sis/ind ex. htm

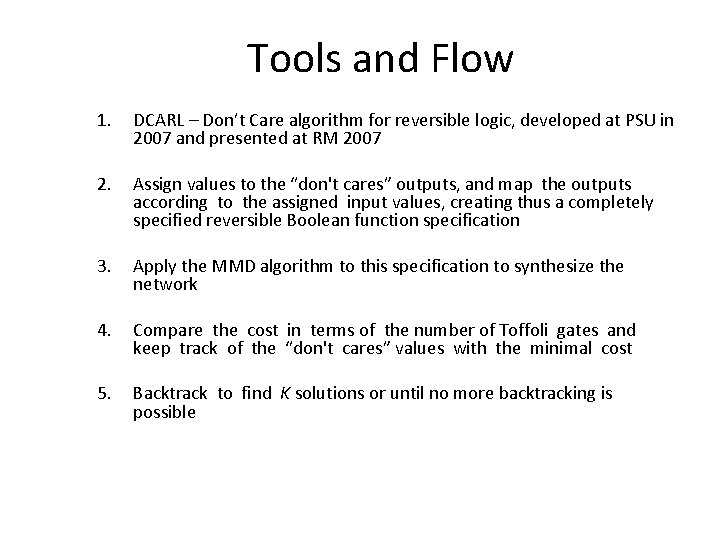

Tools and Flow 1. DCARL – Don’t Care algorithm for reversible logic, developed at PSU in 2007 and presented at RM 2007 2. Assign values to the “don't cares” outputs, and map the outputs according to the assigned input values, creating thus a completely specified reversible Boolean function specification 3. Apply the MMD algorithm to this specification to synthesize the network 4. Compare the cost in terms of the number of Toffoli gates and keep track of the “don't cares” values with the minimal cost 5. Backtrack to find K solutions or until no more backtracking is possible

SIS Usage • Inputs can be in KISS, BLIF format • KISS – uses State Transition Graph format, can be synchronous as well as asynchronous • BLIF – Netlist of Combinational gates and latches • BLIF – internally represented as care network, don’t care network, can be verified by stg_cover command which simulates both symbolically • Performs State minimization, State assignment, Retiming

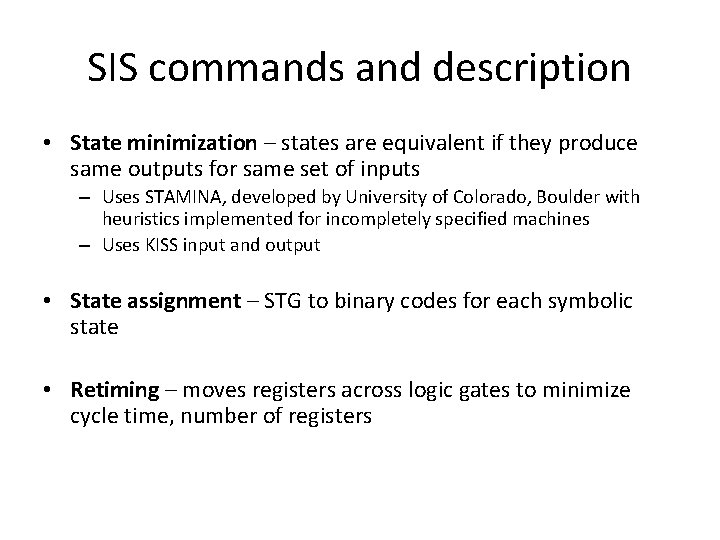

SIS commands and description • State minimization – states are equivalent if they produce same outputs for same set of inputs – Uses STAMINA, developed by University of Colorado, Boulder with heuristics implemented for incompletely specified machines – Uses KISS input and output • State assignment – STG to binary codes for each symbolic state • Retiming – moves registers across logic gates to minimize cycle time, number of registers

Nova

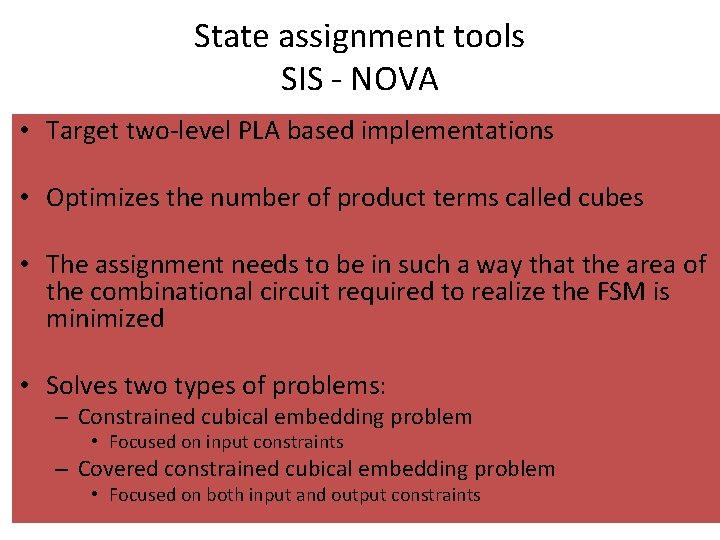

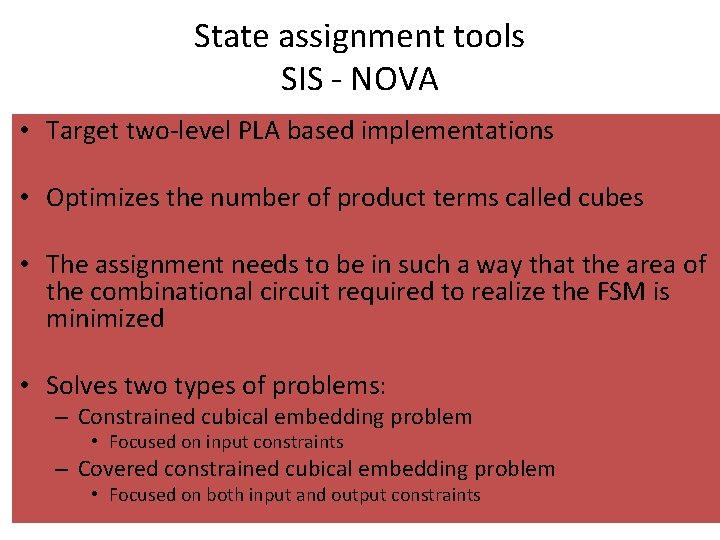

State assignment tools SIS - NOVA • Target two-level PLA based implementations • Optimizes the number of product terms called cubes • The assignment needs to be in such a way that the area of the combinational circuit required to realize the FSM is minimized • Solves two types of problems: – Constrained cubical embedding problem • Focused on input constraints – Covered constrained cubical embedding problem • Focused on both input and output constraints

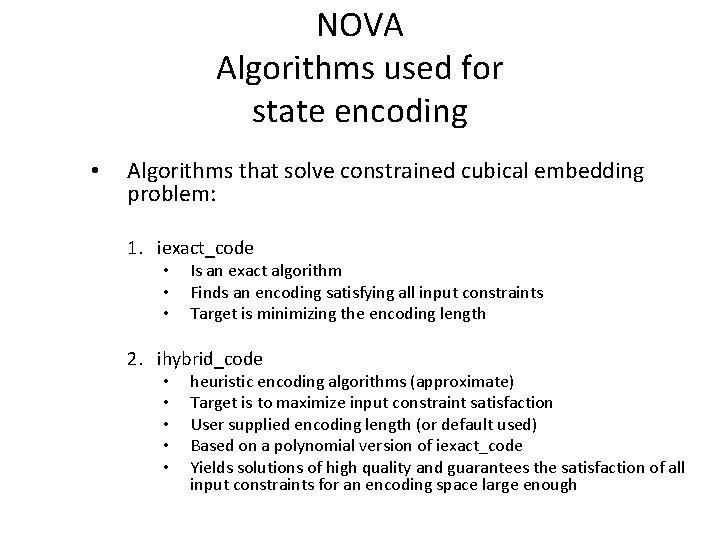

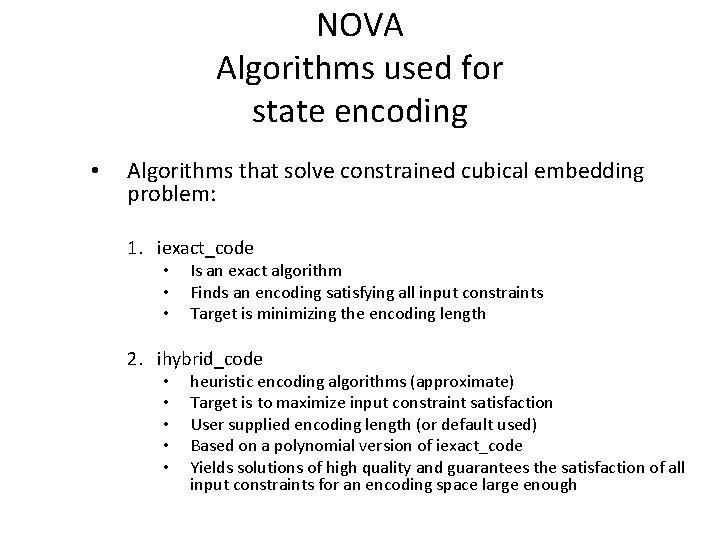

NOVA Algorithms used for state encoding • Algorithms that solve constrained cubical embedding problem: 1. iexact_code • • • Is an exact algorithm Finds an encoding satisfying all input constraints Target is minimizing the encoding length 2. ihybrid_code • • • heuristic encoding algorithms (approximate) Target is to maximize input constraint satisfaction User supplied encoding length (or default used) Based on a polynomial version of iexact_code Yields solutions of high quality and guarantees the satisfaction of all input constraints for an encoding space large enough

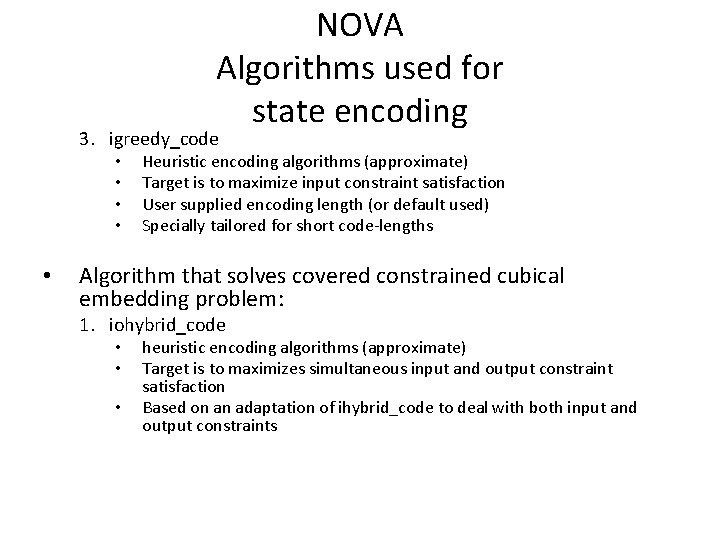

NOVA Algorithms used for state encoding 3. igreedy_code • • • Heuristic encoding algorithms (approximate) Target is to maximize input constraint satisfaction User supplied encoding length (or default used) Specially tailored for short code-lengths Algorithm that solves covered constrained cubical embedding problem: 1. iohybrid_code • • • heuristic encoding algorithms (approximate) Target is to maximizes simultaneous input and output constraint satisfaction Based on an adaptation of ihybrid_code to deal with both input and output constraints

Jedi

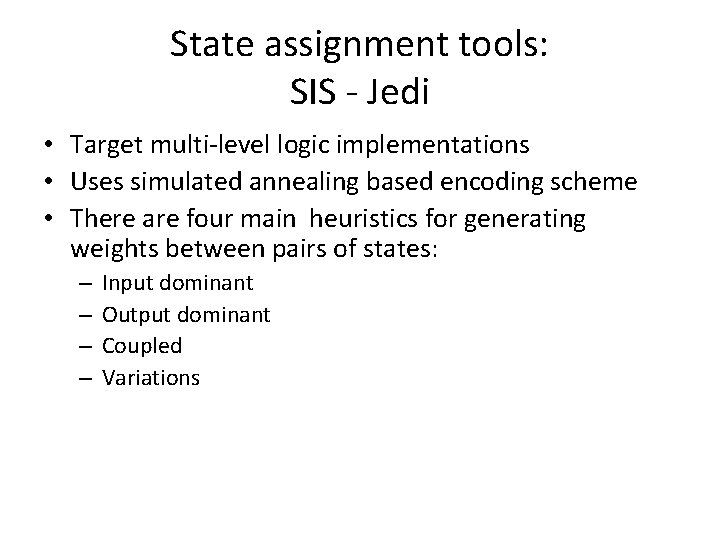

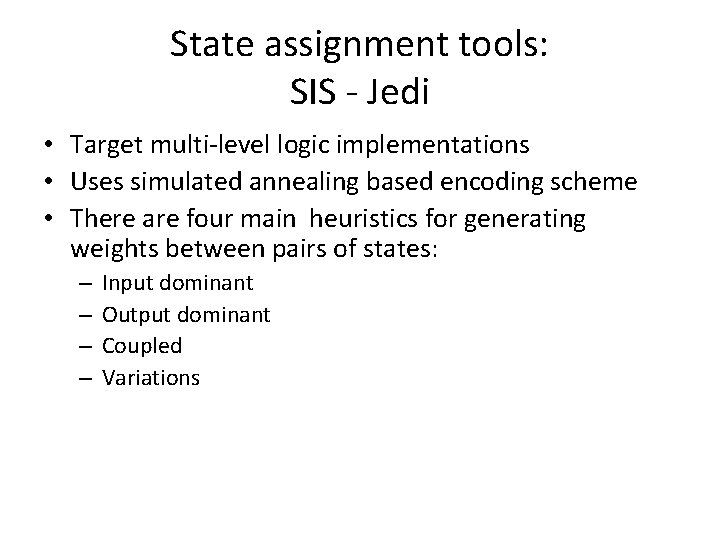

State assignment tools: SIS - Jedi • Target multi-level logic implementations • Uses simulated annealing based encoding scheme • There are four main heuristics for generating weights between pairs of states: – – Input dominant Output dominant Coupled Variations

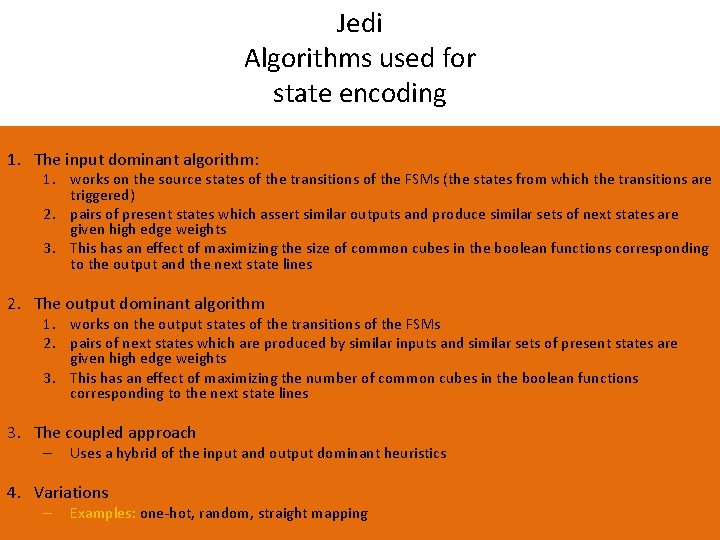

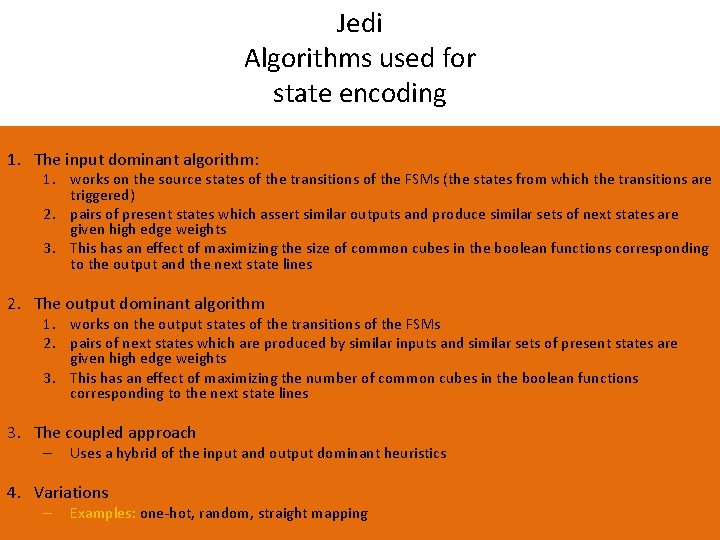

Jedi Algorithms used for state encoding 1. The input dominant algorithm: 1. works on the source states of the transitions of the FSMs (the states from which the transitions are triggered) 2. pairs of present states which assert similar outputs and produce similar sets of next states are given high edge weights 3. This has an effect of maximizing the size of common cubes in the boolean functions corresponding to the output and the next state lines 2. The output dominant algorithm 1. works on the output states of the transitions of the FSMs 2. pairs of next states which are produced by similar inputs and similar sets of present states are given high edge weights 3. This has an effect of maximizing the number of common cubes in the boolean functions corresponding to the next state lines 3. The coupled approach – Uses a hybrid of the input and output dominant heuristics 4. Variations – Examples: one-hot, random, straight mapping

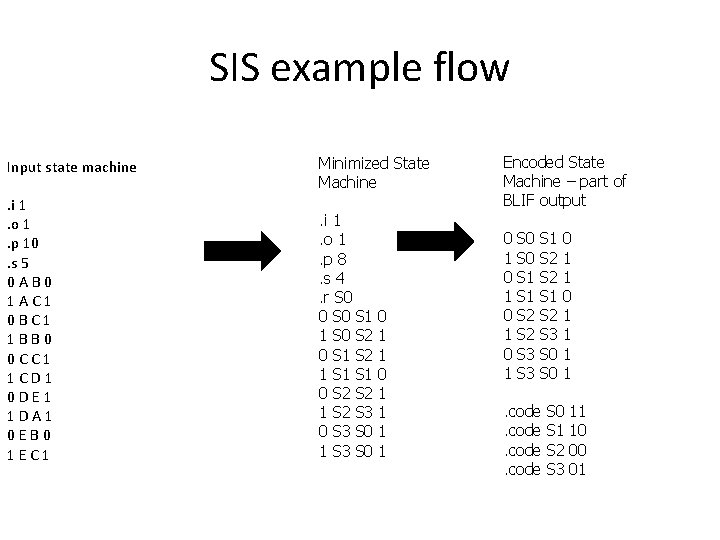

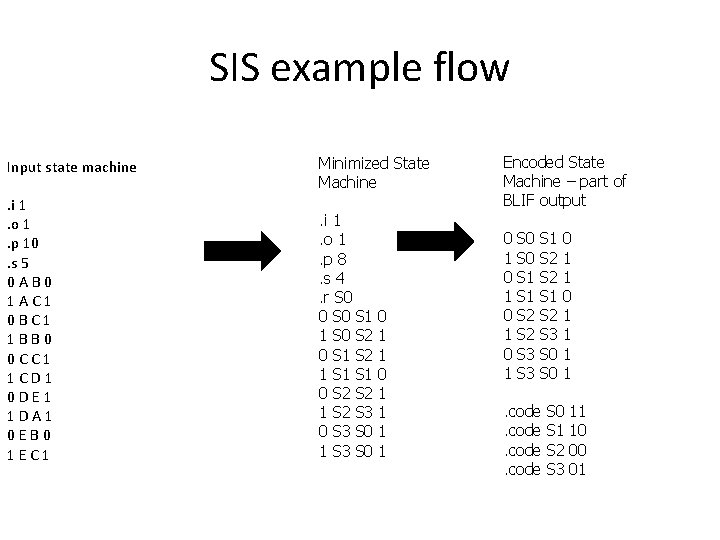

SIS example flow Input state machine Minimized State Machine . i 1. o 1. p 10. s 5 0 AB 0 1 AC 1 0 BC 1 1 BB 0 0 CC 1 1 CD 1 0 DE 1 1 DA 1 0 EB 0 1 EC 1 . i 1. o 1. p 8. s 4. r S 0 0 S 1 1 S 0 S 2 0 S 1 S 2 1 S 1 0 S 2 1 S 2 S 3 0 S 3 S 0 1 S 3 S 0 0 1 1 1 1 Encoded State Machine – part of BLIF output 0 1 0 1 S 0 S 1 S 2 S 3 S 1 S 2 S 3 S 0 . code 0 1 1 1 1 S 0 S 1 S 2 S 3 11 10 00 01

DCARL

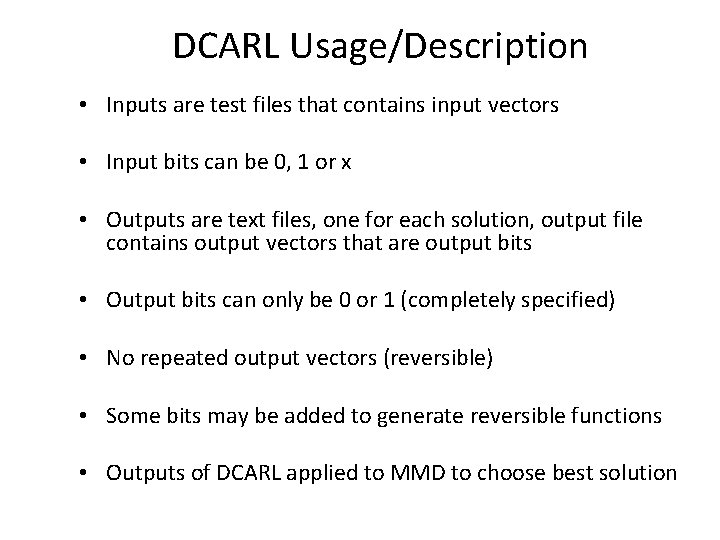

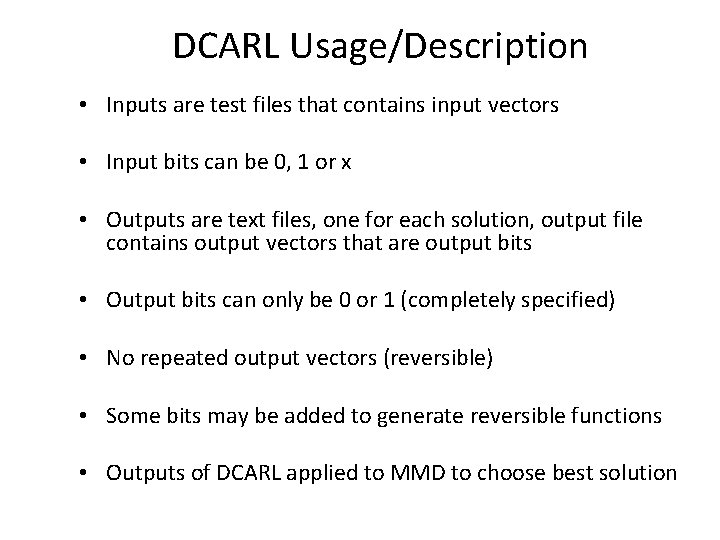

DCARL Usage/Description • Inputs are test files that contains input vectors • Input bits can be 0, 1 or x • Outputs are text files, one for each solution, output file contains output vectors that are output bits • Output bits can only be 0 or 1 (completely specified) • No repeated output vectors (reversible) • Some bits may be added to generate reversible functions • Outputs of DCARL applied to MMD to choose best solution

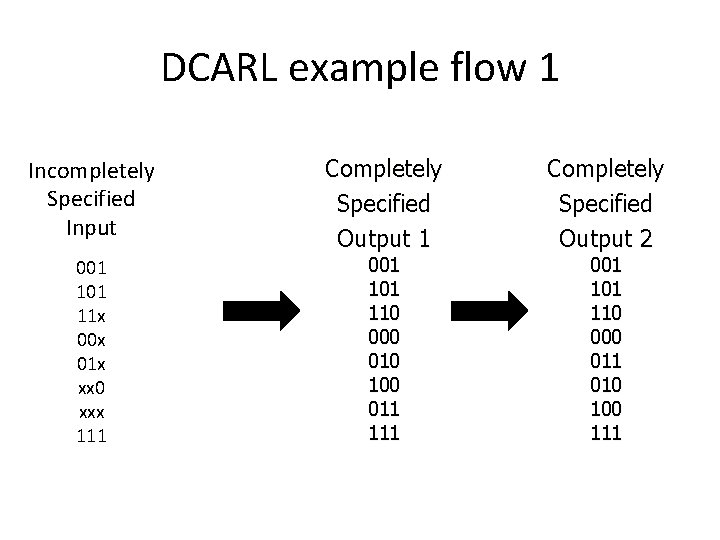

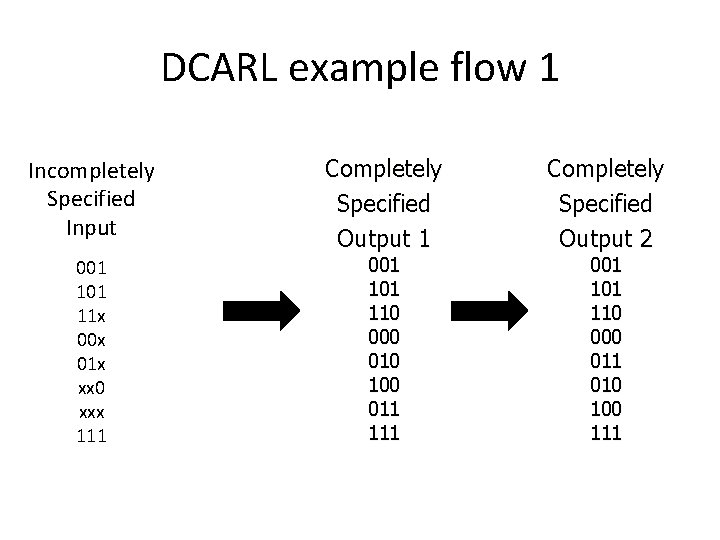

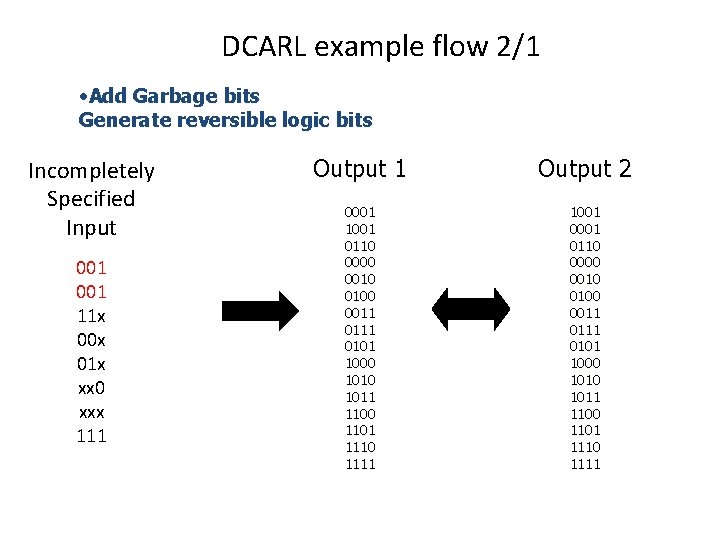

DCARL example flow 1 Incompletely Specified Input 001 11 x 00 x 01 x xx 0 xxx 111 Completely Specified Output 1 001 110 000 010 100 011 111 Completely Specified Output 2 001 110 000 011 010 100 111

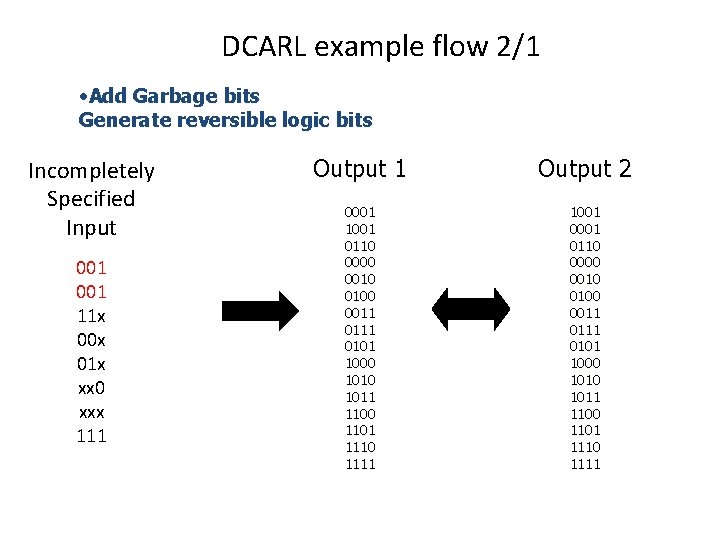

DCARL example flow 2/1 • Add Garbage bits Generate reversible logic bits Incompletely Specified Input 001 11 x 00 x 01 x xx 0 xxx 111 Output 2 0001 1001 0110 0000 0010 0100 0011 0101 1000 1011 1100 1101 1110 1111

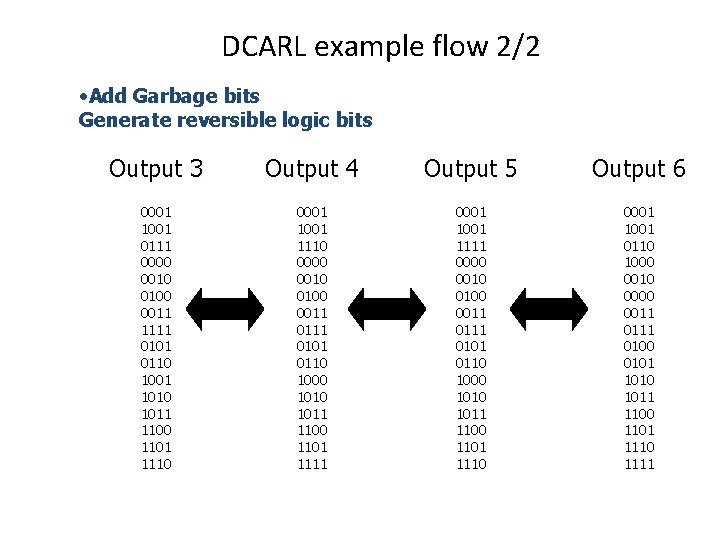

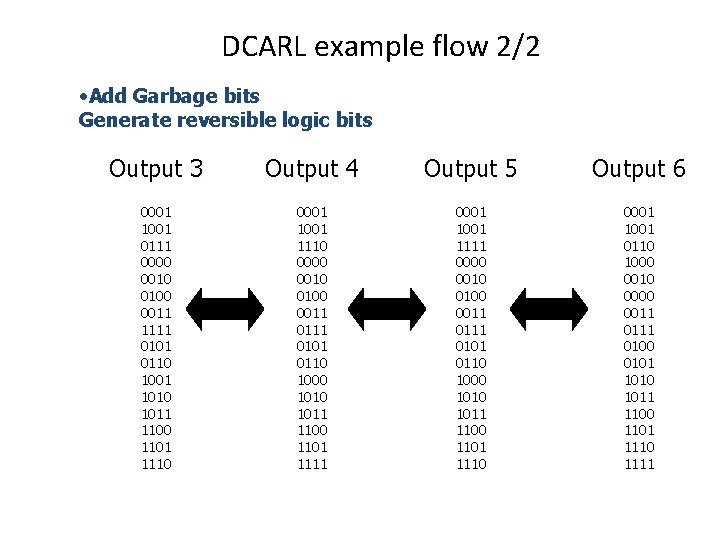

DCARL example flow 2/2 • Add Garbage bits Generate reversible logic bits Output 3 Output 4 Output 5 Output 6 0001 1001 0111 0000 0010 0100 0011 1111 0101 0110 1001 1010 1011 1100 1101 1110 0001 1110 0000 0010 0100 0011 0101 0110 1000 1011 1100 1101 1111 0001 1111 0000 0010 0100 0011 0101 0110 1000 1011 1100 1101 1110 0001 1001 0110 1000 0010 0000 0011 0100 0101 1010 1011 1100 1101 1110 1111

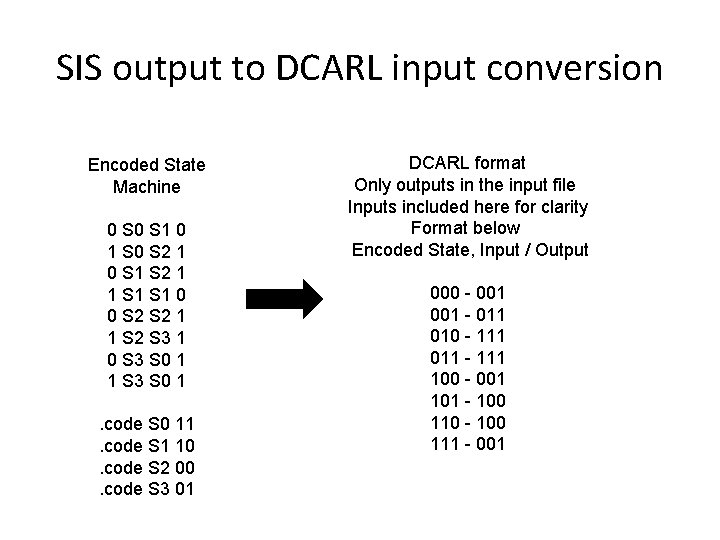

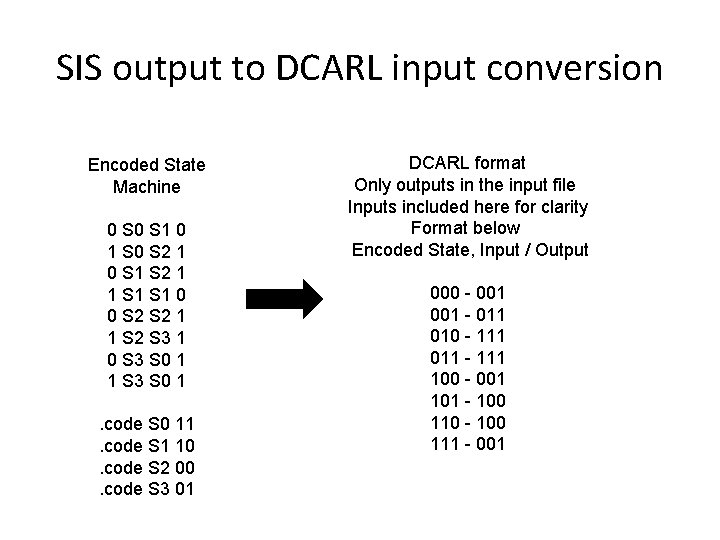

SIS output to DCARL input conversion Encoded State Machine 0 S 1 0 1 S 0 S 2 1 0 S 1 S 2 1 1 S 1 0 0 S 2 1 1 S 2 S 3 1 0 S 3 S 0 1 1 S 3 S 0 1. code S 0 11. code S 1 10. code S 2 00. code S 3 01 DCARL format Only outputs in the input file Inputs included here for clarity Format below Encoded State, Input / Output 000 - 001 - 011 010 - 111 011 - 111 100 - 001 101 - 100 110 - 100 111 - 001

6. Results

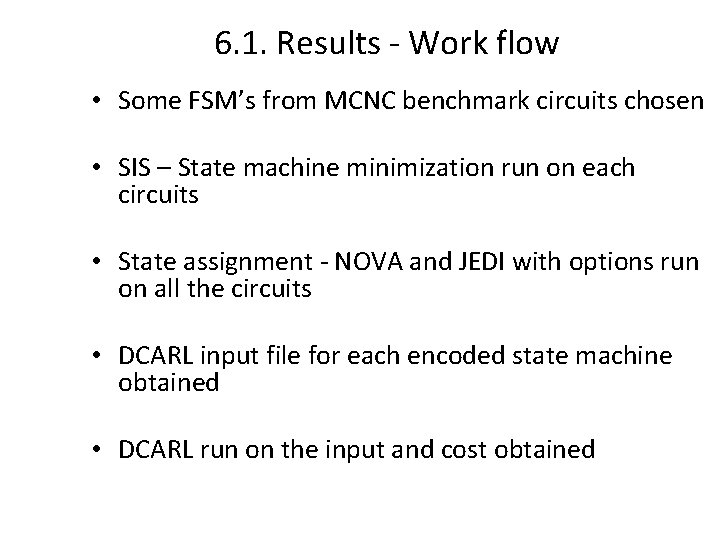

6. 1. Results - Work flow • Some FSM’s from MCNC benchmark circuits chosen • SIS – State machine minimization run on each circuits • State assignment - NOVA and JEDI with options run on all the circuits • DCARL input file for each encoded state machine obtained • DCARL run on the input and cost obtained

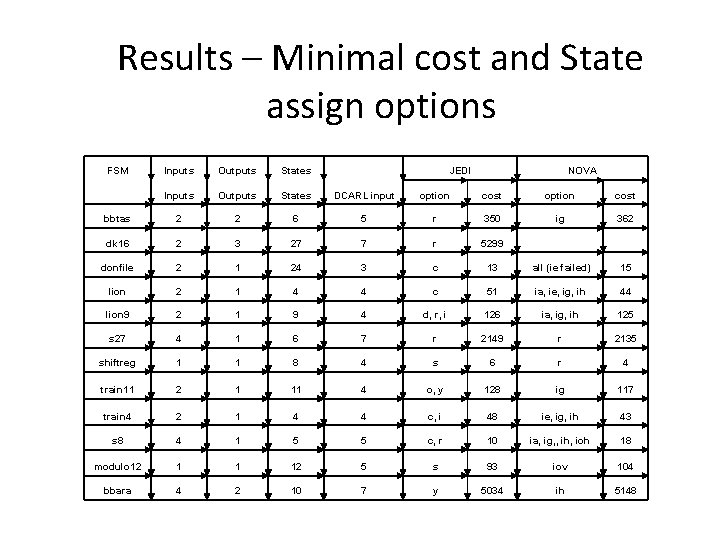

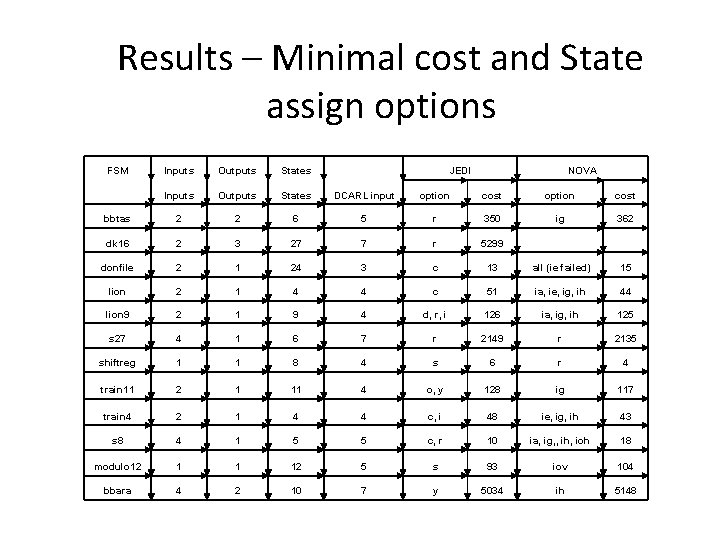

Results – Minimal cost and State assign options FSM Inputs Outputs States JEDI NOVA Inputs Outputs States DCARL input option cost bbtas 2 2 6 5 r 350 ig 362 dk 16 2 3 27 7 r 5299 donfile 2 1 24 3 c 13 all (ie failed) 15 lion 2 1 4 4 c 51 ia, ie, ig, ih 44 lion 9 2 1 9 4 d, r, i 126 ia, ig, ih 125 s 27 4 1 6 7 r 2149 r 2135 shiftreg 1 1 8 4 s 6 r 4 train 11 2 1 11 4 o, y 128 ig 117 train 4 2 1 4 4 c, i 48 ie, ig, ih 43 s 8 4 1 5 5 c, r 10 ia, ig, , ih, ioh 18 modulo 12 1 1 12 5 s 93 iov 104 bbara 4 2 10 7 y 5034 ih 5148

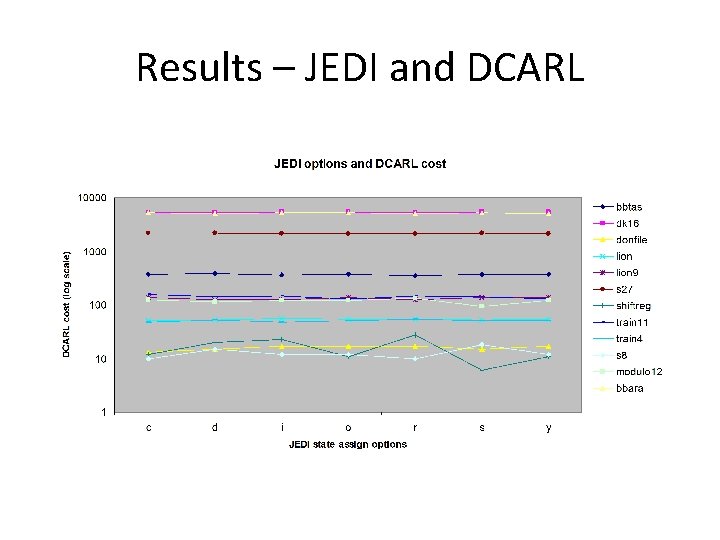

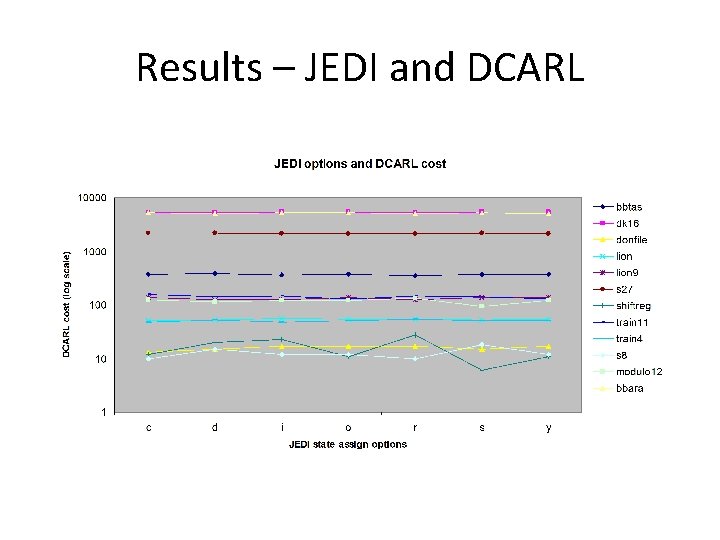

Results – JEDI and DCARL

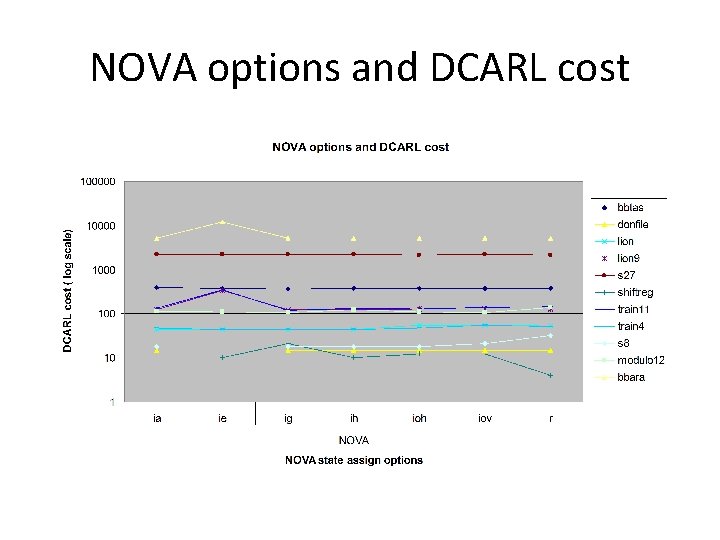

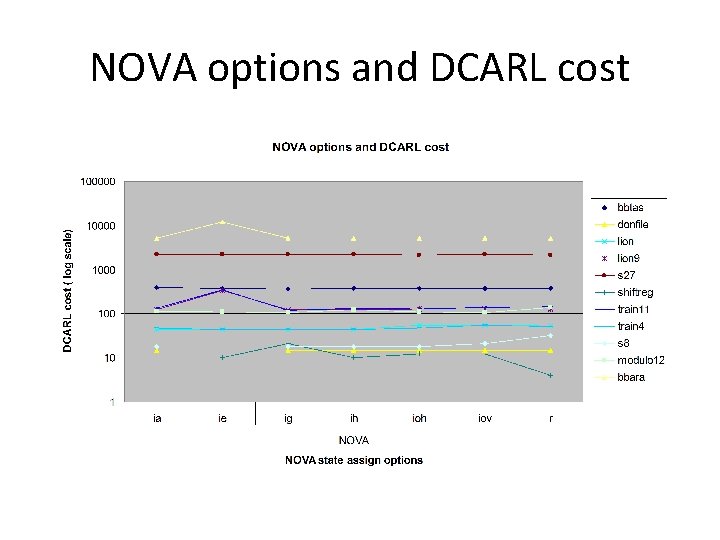

NOVA options and DCARL cost

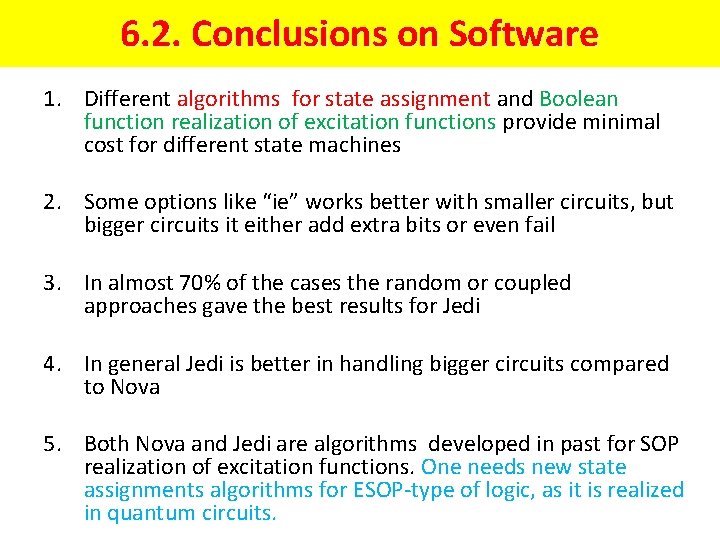

6. 2. Conclusions on Software 1. Different algorithms for state assignment and Boolean function realization of excitation functions provide minimal cost for different state machines 2. Some options like “ie” works better with smaller circuits, but bigger circuits it either add extra bits or even fail 3. In almost 70% of the cases the random or coupled approaches gave the best results for Jedi 4. In general Jedi is better in handling bigger circuits compared to Nova 5. Both Nova and Jedi are algorithms developed in past for SOP realization of excitation functions. One needs new state assignments algorithms for ESOP-type of logic, as it is realized in quantum circuits.

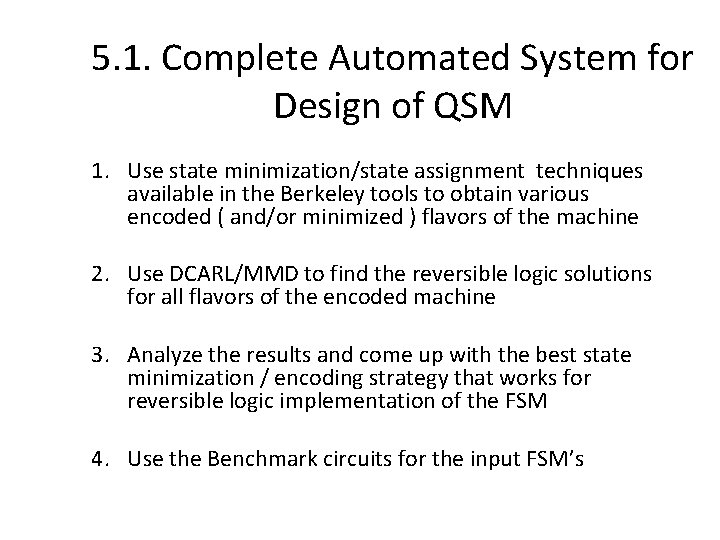

7. General Conclusions on QSM Synthesis 1. Practical models for QSMs and their classical controllers have been developed. Our approaches all involve state minimization and state assignment of machines. Other methods of realization that are used in classical machines, such as decomposition or one-hot encoding, should be also investigated. 2. A synthesis flow which allows us to design QSMs from abstract specifications has been developed. The CAD tool can be improved by improving backtracking method to convert incomplete to complete functions and by better quantum circuit minimizer that will replace MMD. 3. Synchronous as well as asynchronous techniques for high level synthesis of QSMs have been demonstrated by us. More details can be found in MS thesis of Manjith Kumar. 4. State assignment tools from U. C. Berkeley were used but new algorithms specific to reversible logic should be developed