EMT 362 Microelectronic Fabrication CMOS ISOLATION TECHNOLOGY Part

EMT 362: Microelectronic Fabrication CMOS ISOLATION TECHNOLOGY Part 2 Ramzan Mat Ayub School of Microelectronic Engineering

Lecture Objectives • Understand the basic operation of MOS Capacitor • Able to calculate the Threshold Voltage for MOS Capacitor and Transistor • Understand why isolation is needed in CMOS process • Understand the isolation requirements and related design rules • Able to describe in terms of wafer cross section, the process steps for Semirecessed LOCOS, Fully Recessed LOCOS, STI and several advanced isolation structures formation. School of Microelectronic Engineering

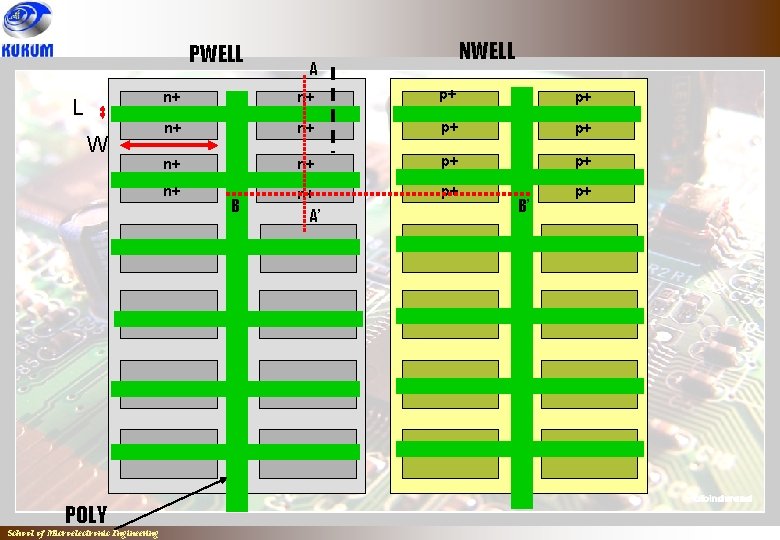

PWELL L W POLY School of Microelectronic Engineering NWELL A n+ n+ p+ p+ B A’ B’

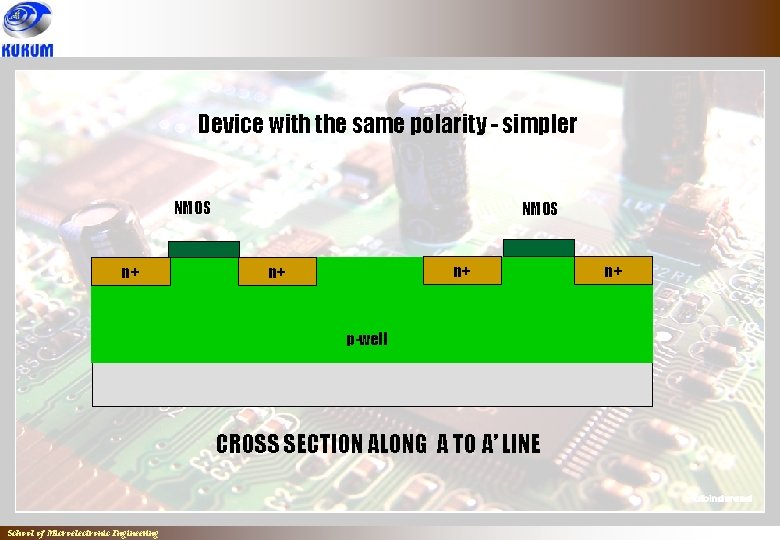

Device with the same polarity - simpler NMOS n+ n+ p-well CROSS SECTION ALONG A TO A’ LINE School of Microelectronic Engineering n+

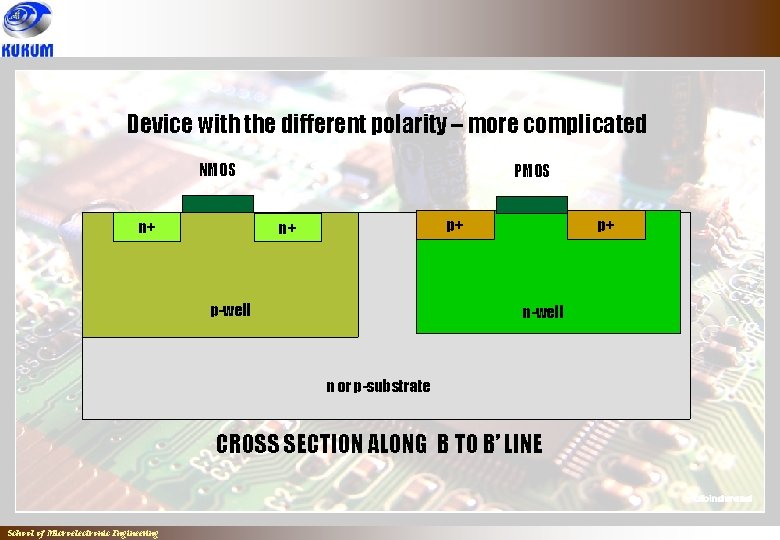

Device with the different polarity – more complicated NMOS n+ PMOS p+ p+ n+ p-well n or p-substrate CROSS SECTION ALONG B TO B’ LINE School of Microelectronic Engineering

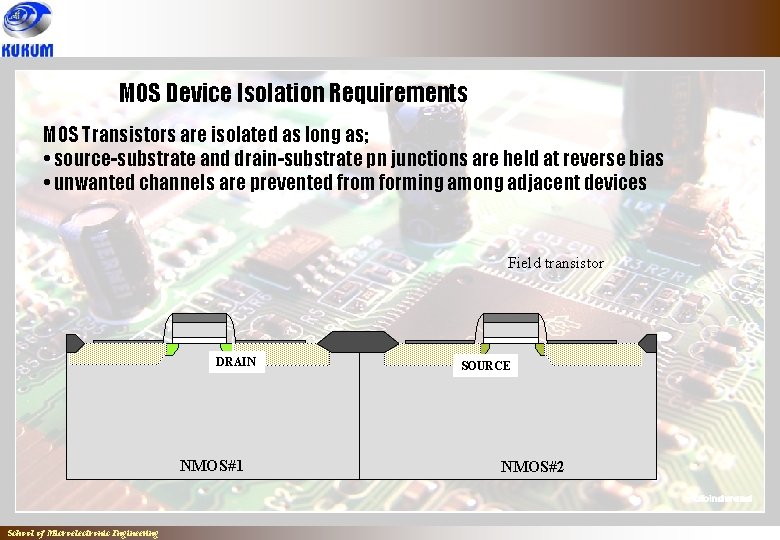

MOS Device Isolation Requirements MOS Transistors are isolated as long as; • source-substrate and drain-substrate pn junctions are held at reverse bias • unwanted channels are prevented from forming among adjacent devices Field transistor DRAIN NMOS#1 School of Microelectronic Engineering SOURCE NMOS#2

• Electric circuit in VLSI technology is implemented by connecting isolated devices through specific conducting path. • To fabricate monolithic ICs, electrically isolated devices must be created in the silicon substrate. • Only later they are connected. • Improper isolated device will result; • total circuit failure • high leakage (large dc power dissipation) • noise margin degradation • voltage shift, cross talk between transistors and etc. • The challenge is VLSI device only allows single transistor leakage < 10 p. A/um). On the other hand, process integration imposed a stringent requirement on the isolation technology; • spacing between actives should be as small as possible • to produce the surface topography as planar as possible • isolation process module must be simple to implement and easy to control School of Microelectronic Engineering

School of Microelectronic Engineering

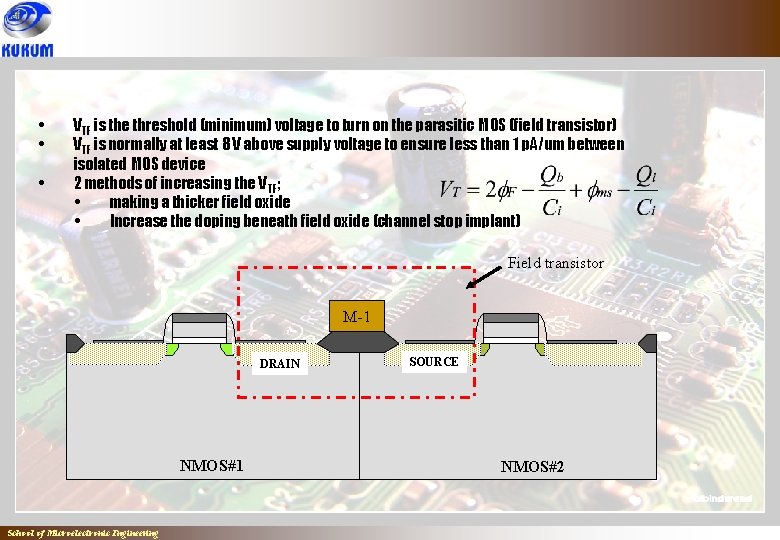

• • • VTF is the threshold (minimum) voltage to turn on the parasitic MOS (field transistor) VTF is normally at least 8 V above supply voltage to ensure less than 1 p. A/um between isolated MOS device 2 methods of increasing the VTF; • making a thicker field oxide • Increase the doping beneath field oxide (channel stop implant) Field transistor M-1 DRAIN NMOS#1 School of Microelectronic Engineering SOURCE NMOS#2

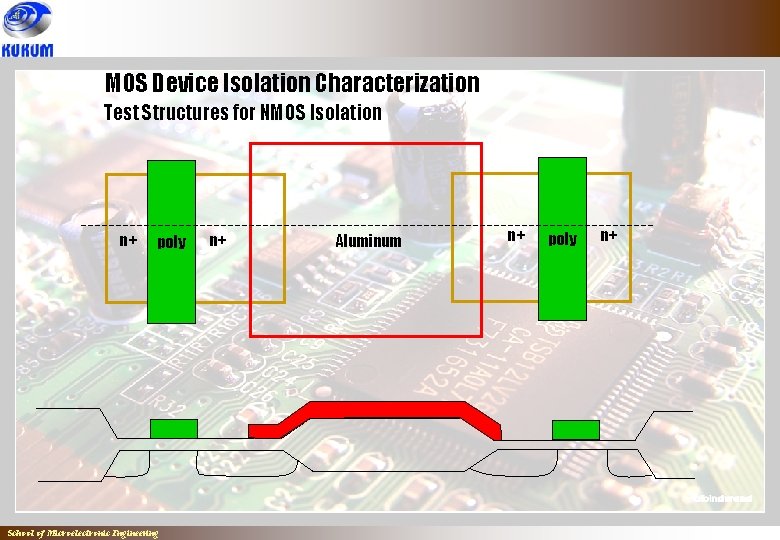

MOS Device Isolation Characterization Test Structures for NMOS Isolation n+ poly School of Microelectronic Engineering n+ Aluminum n+ poly n+

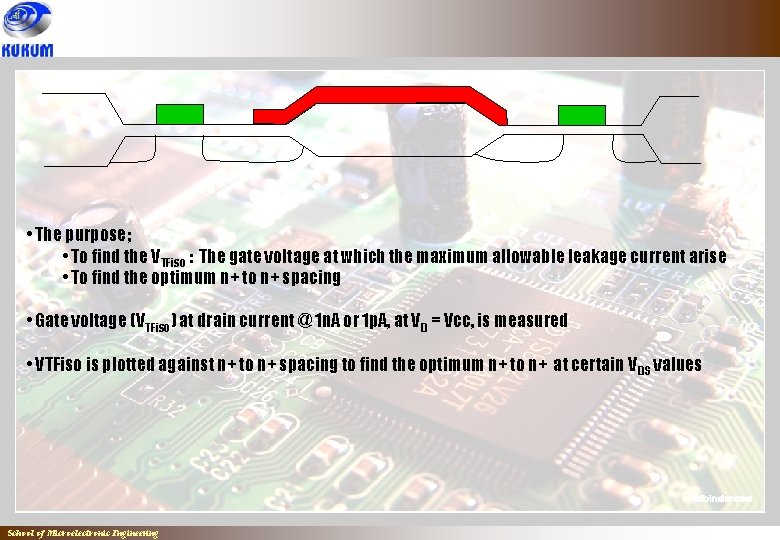

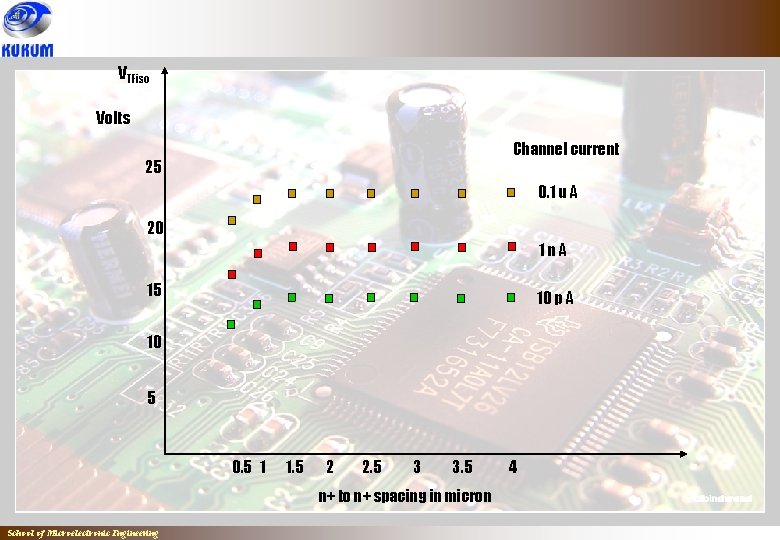

• The purpose; • To find the VTFiso : The gate voltage at which the maximum allowable leakage current arise • To find the optimum n+ to n+ spacing • Gate voltage (VTFiso) at drain current @ 1 n. A or 1 p. A, at VD = Vcc, is measured • VTFiso is plotted against n+ to n+ spacing to find the optimum n+ to n+ at certain V DS values School of Microelectronic Engineering

VTFiso Volts Channel current 25 0. 1 u A 20 1 n. A 15 10 p A 10 5 0. 5 1 1. 5 2 2. 5 3 3. 5 n+ to n+ spacing in micron School of Microelectronic Engineering 4

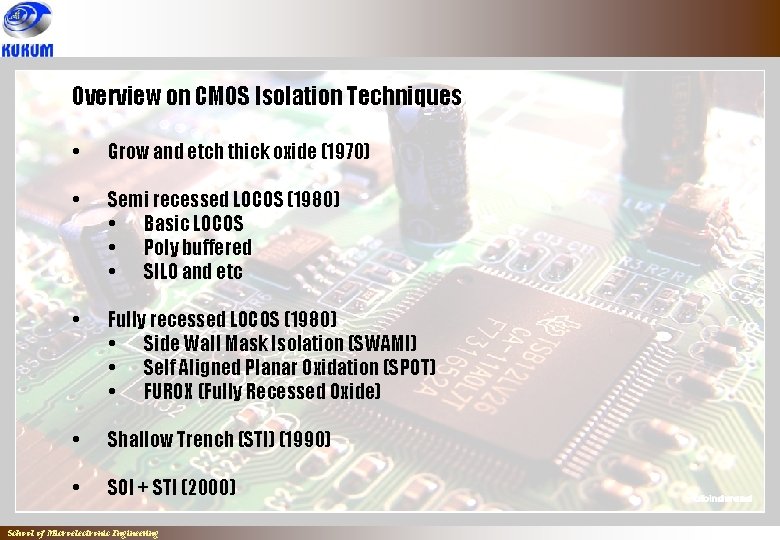

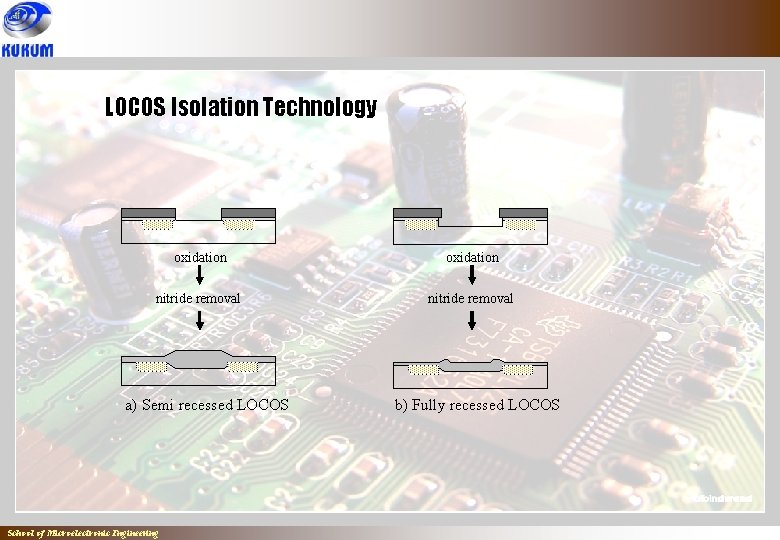

Overview on CMOS Isolation Techniques • Grow and etch thick oxide (1970) • Semi recessed LOCOS (1980) • Basic LOCOS • Poly buffered • SILO and etc • Fully recessed LOCOS (1980) • Side Wall Mask Isolation (SWAMI) • Self Aligned Planar Oxidation (SPOT) • FUROX (Fully Recessed Oxide) • Shallow Trench (STI) (1990) • SOI + STI (2000) School of Microelectronic Engineering

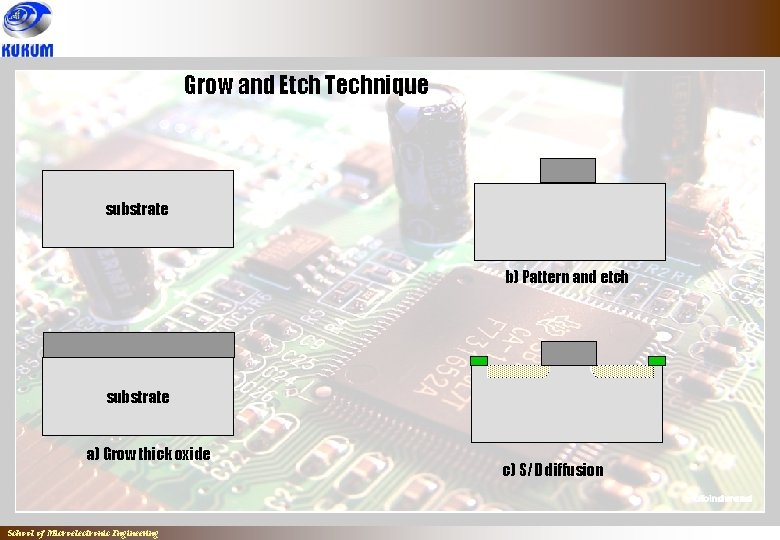

Grow and Etch Technique substrate b) Pattern and etch substrate a) Grow thick oxide School of Microelectronic Engineering c) S/D diffusion

A) Grow and etch (used until late 70 s) • • Thick oxide is grown thermally in the furnace Wafer is patterned and etch Disadvantages • • Sharp corners, difficult to cover in the latter process steps Channel stop must be implanted before oxide is grown (active to be aligned with channel stop region – low packing density) School of Microelectronic Engineering

LOCOS Isolation Technology oxidation nitride removal a) Semi recessed LOCOS School of Microelectronic Engineering b) Fully recessed LOCOS

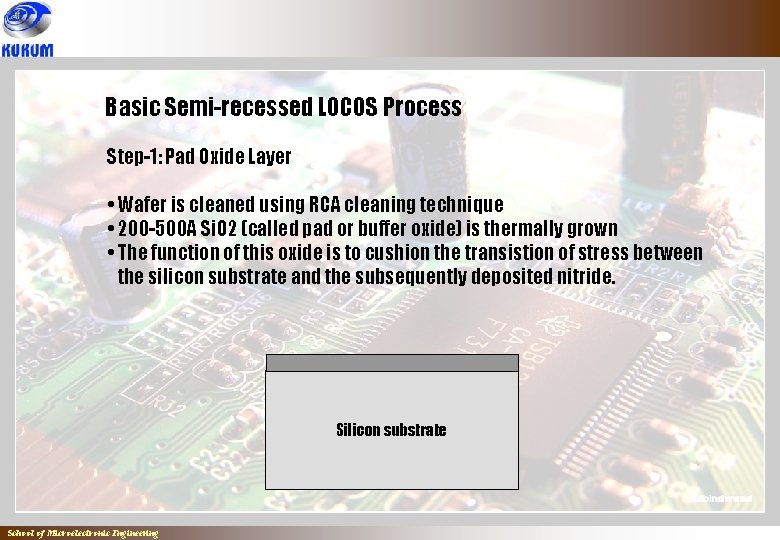

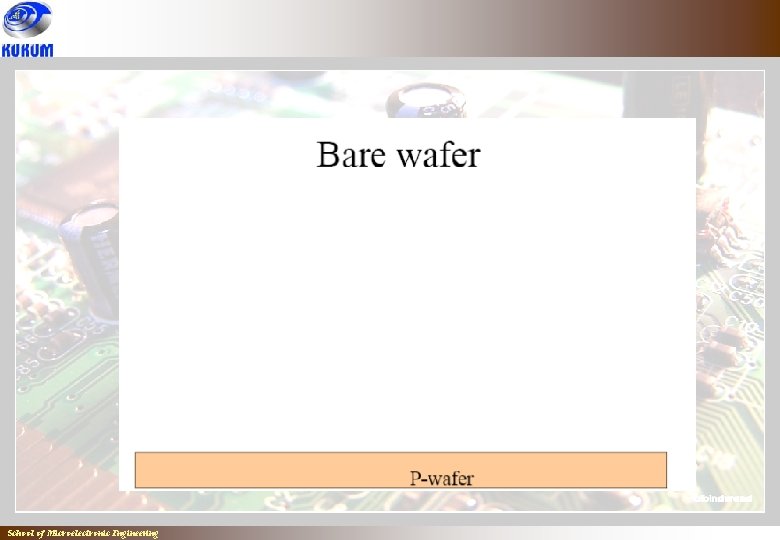

Basic Semi-recessed LOCOS Process Step-1: Pad Oxide Layer • Wafer is cleaned using RCA cleaning technique • 200 -500 A Si. O 2 (called pad or buffer oxide) is thermally grown • The function of this oxide is to cushion the transistion of stress between the silicon substrate and the subsequently deposited nitride. Silicon substrate School of Microelectronic Engineering

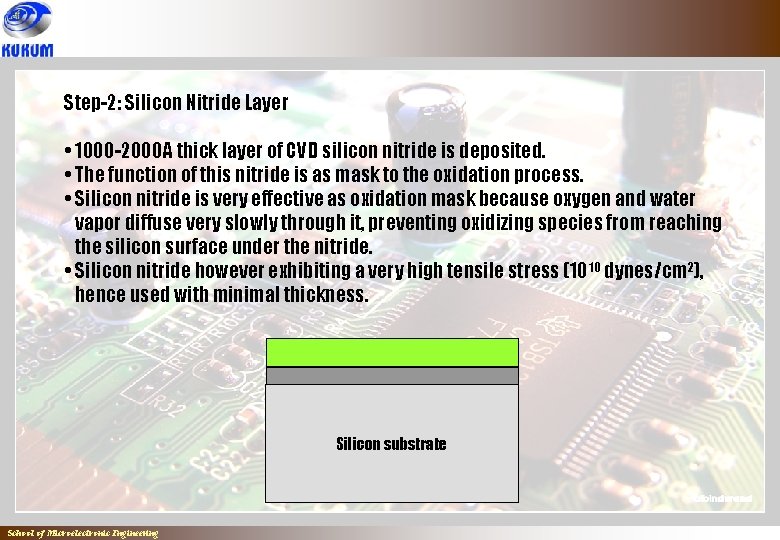

Step-2: Silicon Nitride Layer • 1000 -2000 A thick layer of CVD silicon nitride is deposited. • The function of this nitride is as mask to the oxidation process. • Silicon nitride is very effective as oxidation mask because oxygen and water vapor diffuse very slowly through it, preventing oxidizing species from reaching the silicon surface under the nitride. • Silicon nitride however exhibiting a very high tensile stress (10 10 dynes/cm 2), hence used with minimal thickness. Silicon substrate School of Microelectronic Engineering

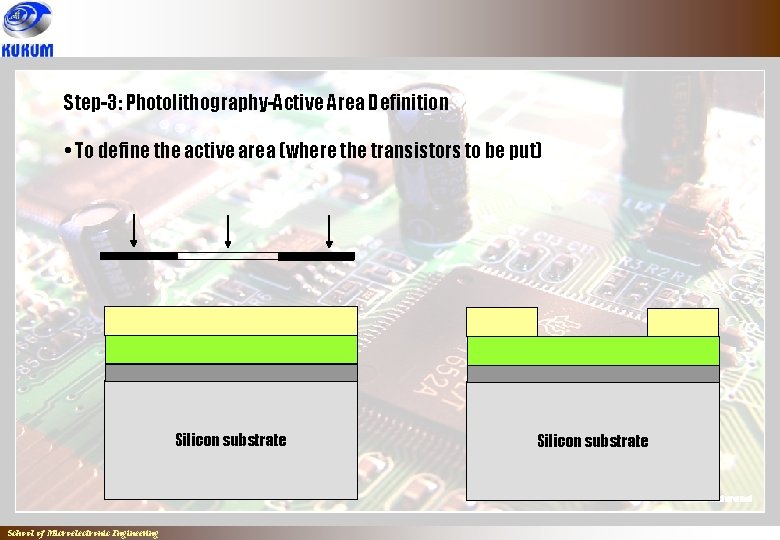

Step-3: Photolithography-Active Area Definition • To define the active area (where the transistors to be put) Silicon substrate School of Microelectronic Engineering Silicon substrate

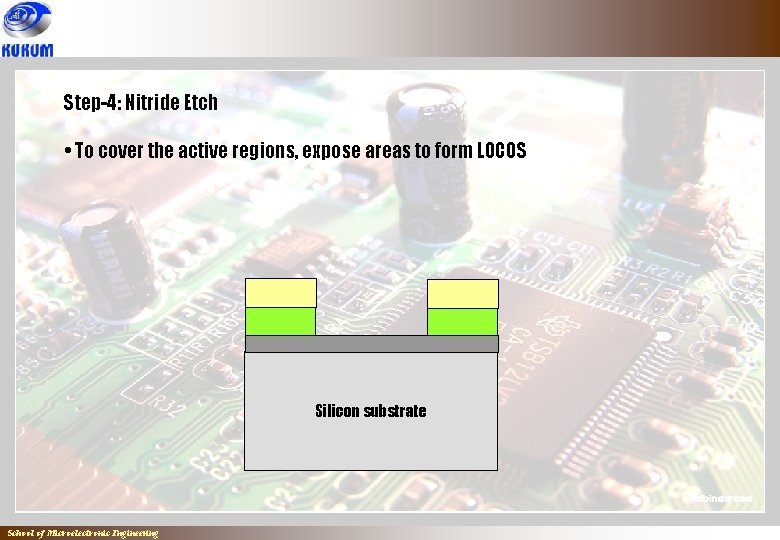

Step-4: Nitride Etch • To cover the active regions, expose areas to form LOCOS Silicon substrate School of Microelectronic Engineering

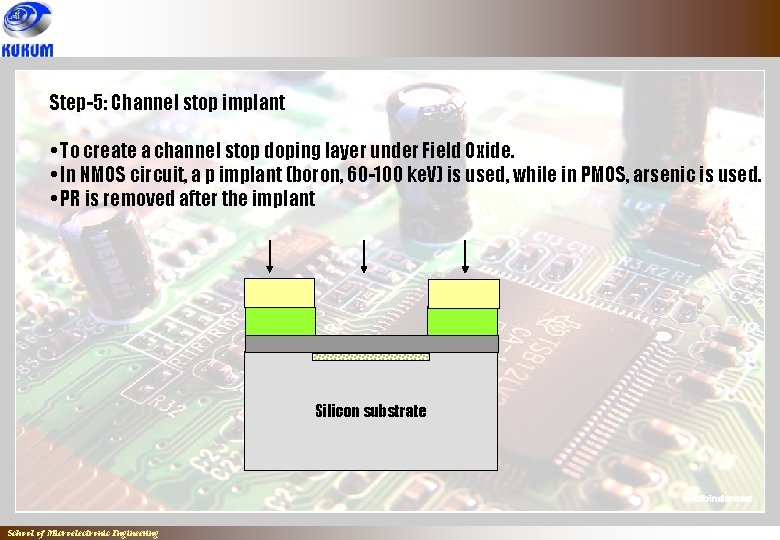

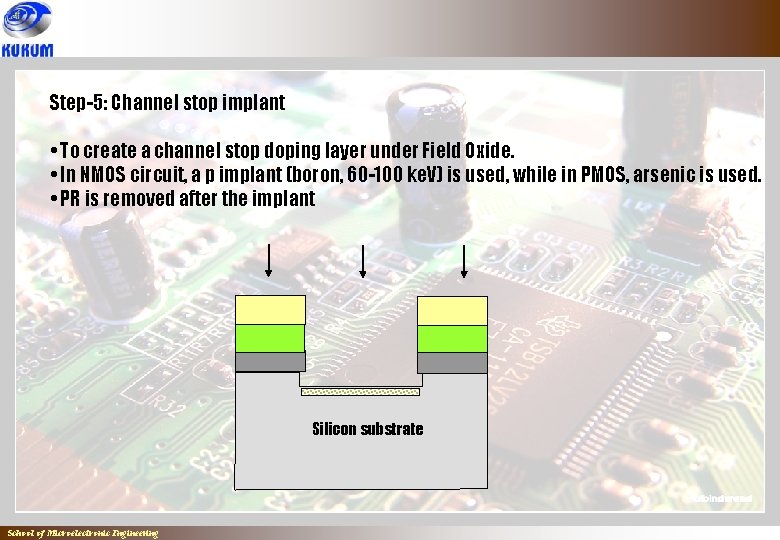

Step-5: Channel stop implant • To create a channel stop doping layer under Field Oxide. • In NMOS circuit, a p implant (boron, 60 -100 ke. V) is used, while in PMOS, arsenic is used. • PR is removed after the implant Silicon substrate School of Microelectronic Engineering

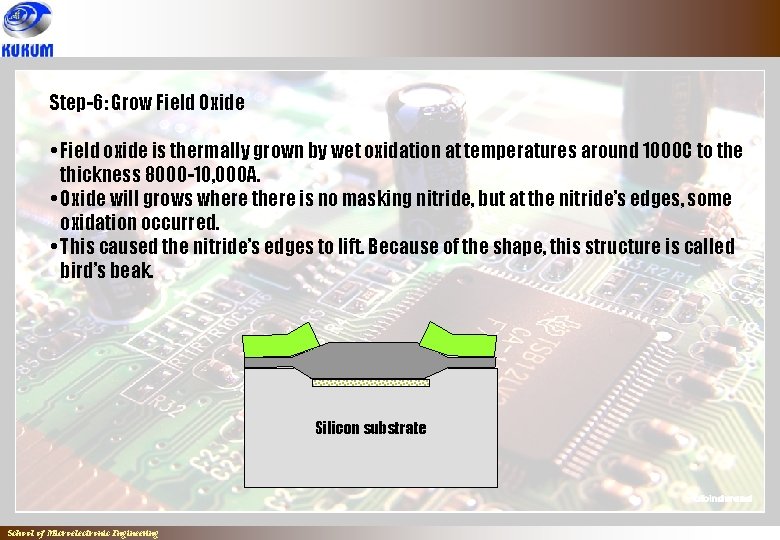

Step-6: Grow Field Oxide • Field oxide is thermally grown by wet oxidation at temperatures around 1000 C to the thickness 8000 -10, 000 A. • Oxide will grows where there is no masking nitride, but at the nitride’s edges, some oxidation occurred. • This caused the nitride’s edges to lift. Because of the shape, this structure is called bird’s beak. Silicon substrate School of Microelectronic Engineering

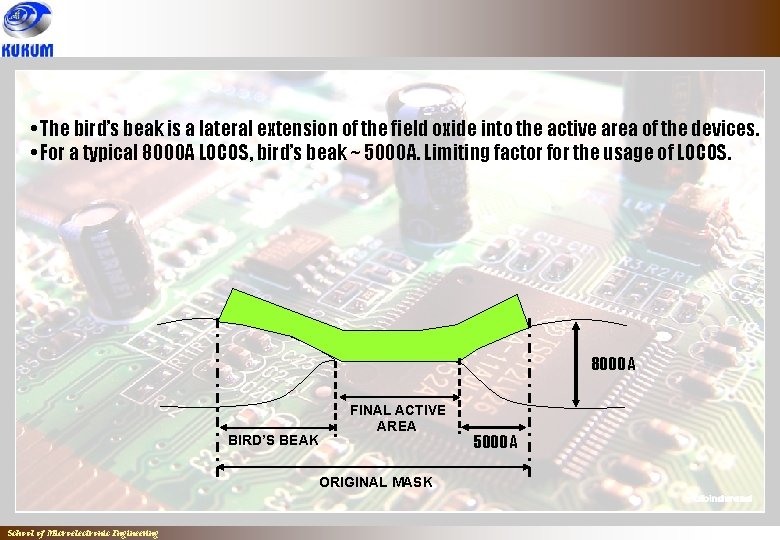

• The bird’s beak is a lateral extension of the field oxide into the active area of the devices. • For a typical 8000 A LOCOS, bird’s beak ~ 5000 A. Limiting factor for the usage of LOCOS. 8000 A BIRD’S BEAK FINAL ACTIVE AREA ORIGINAL MASK School of Microelectronic Engineering 5000 A

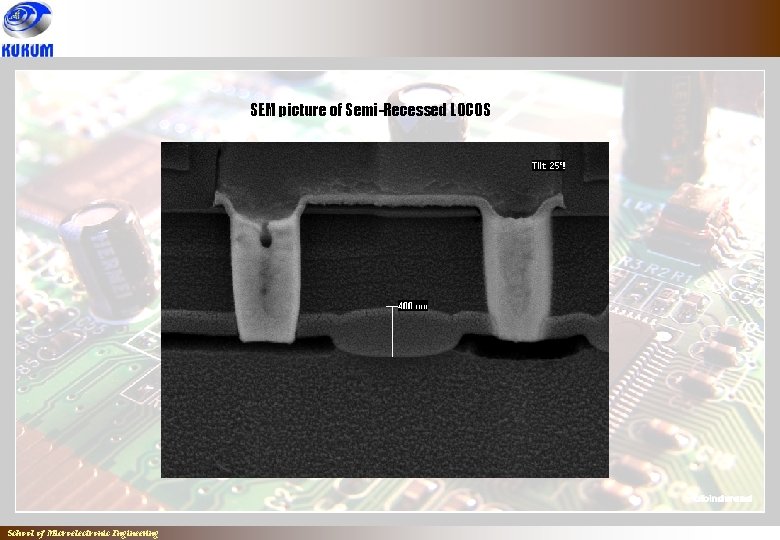

SEM picture of Semi-Recessed LOCOS School of Microelectronic Engineering

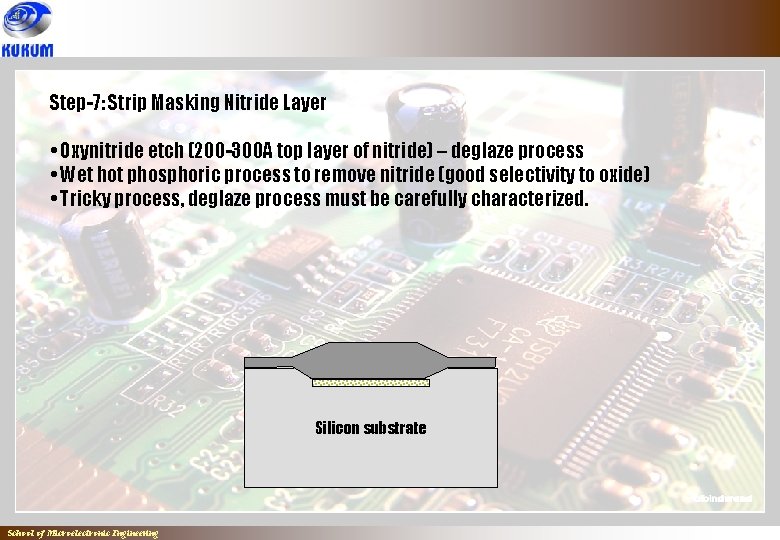

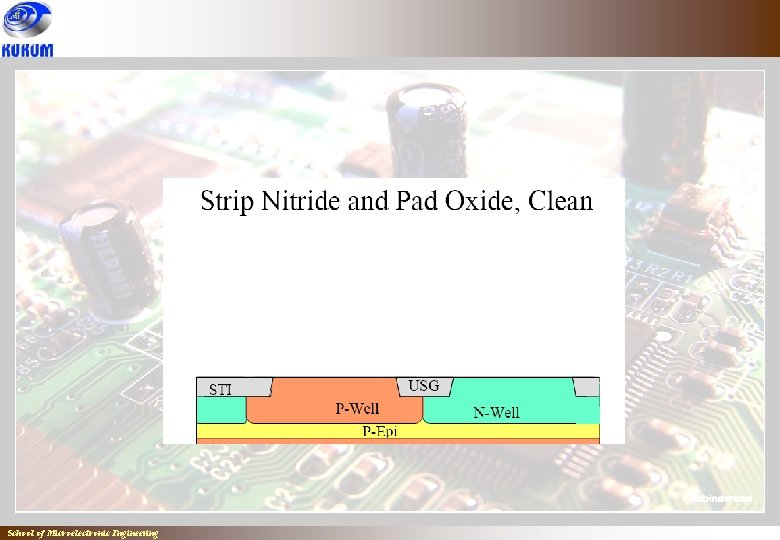

Step-7: Strip Masking Nitride Layer • Oxynitride etch (200 -300 A top layer of nitride) – deglaze process • Wet hot phosphoric process to remove nitride (good selectivity to oxide) • Tricky process, deglaze process must be carefully characterized. Silicon substrate School of Microelectronic Engineering

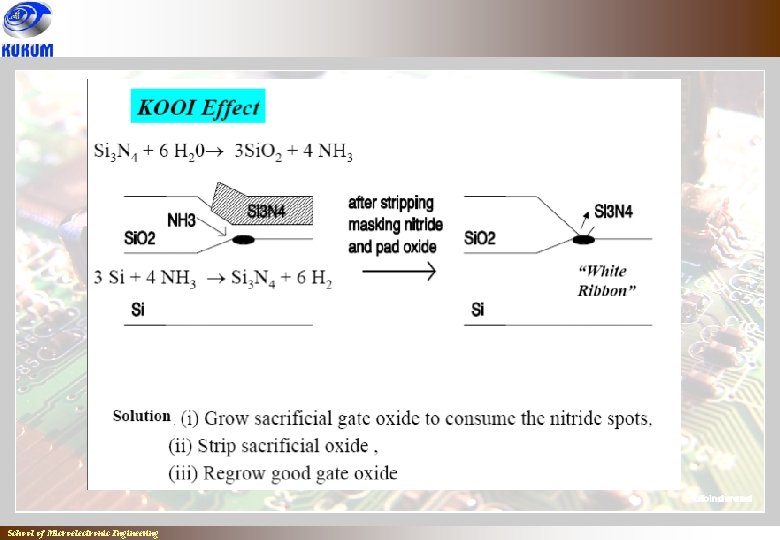

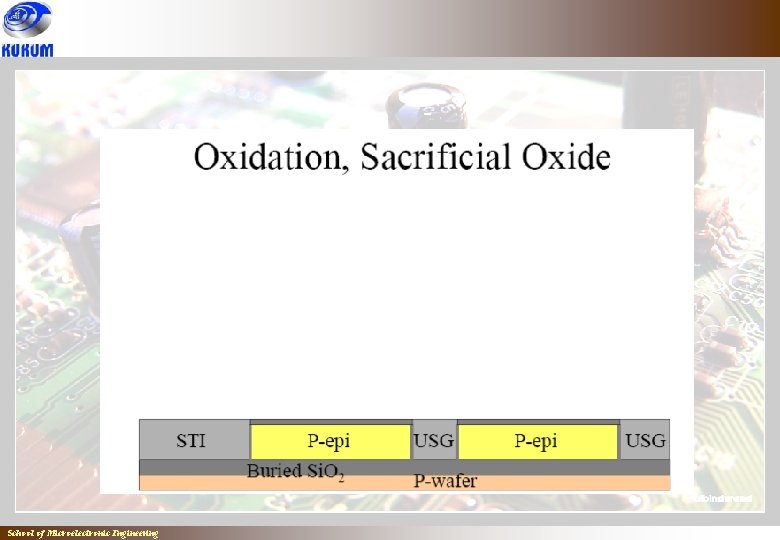

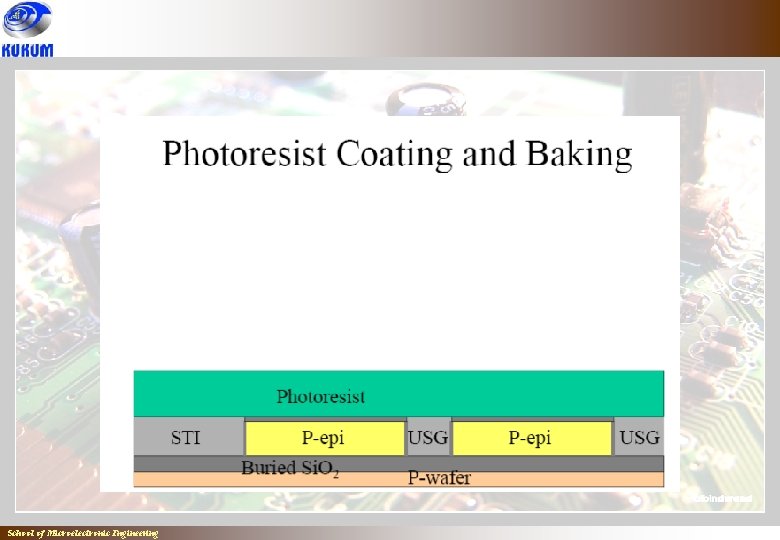

Step-8: Regrow and strip sacrificial oxide • Kooi et al discovered that a thin layer of silicon nitride can form on the silicon surface (pad oxide – silicon interface). • This nitride spot is called white ribbon or Kooi Effect and must be removed to prevent defect from occuring when growing gate oxide. • This can be done by regrowing a pad oxide and subsequently removed. School of Microelectronic Engineering

School of Microelectronic Engineering

Factors Affecting Bird’s Beak Length and Shape 1) Pad oxide thickness 2) Lateral oxidation can be reduced by using a thinner pad oxide, leading to a shorter 3) bird’s beak. 2) Pad layer composition – CVD oxynitride 3) Silicon crystal orientation – shorter bird’s beak in <111> compared to <100> 4) Field oxide process temperature – Shorter with higher oxidation temperature. 5) Thickness and mechanical properties of nitride layer – the thicker the nitride, 6) the shorter the bird’s beak 6) Mask stack geometry – depends on the shape and size of the structures School of Microelectronic Engineering

Advanced Semi-Recessed LOCOS Process A) Poly Buffered LOCOS • Based on the fact that a thinner pad oxide will produce a shorter bird’s beak. • Usual pad oxide is replaced with a polybuffered layer; poly 500 A: oxide 100 A • Thicker nitride is used to suppress the bird’s beak more, 1000 – 2500 A B) Sealed Interface LOCOS Q 7, Tutorial 1 • Reduce the bird’s beak by depositing nitride layer directly onto the silicon. • Lateral diffusion of oxidants is suppressed better, resulting a shorter bird’s beak. Q 8, Tutorial 1 School of Microelectronic Engineering

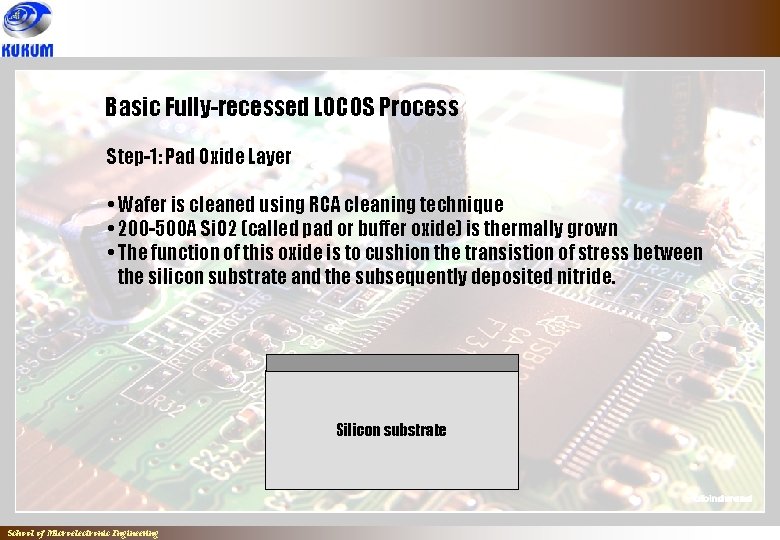

Basic Fully-recessed LOCOS Process Step-1: Pad Oxide Layer • Wafer is cleaned using RCA cleaning technique • 200 -500 A Si. O 2 (called pad or buffer oxide) is thermally grown • The function of this oxide is to cushion the transistion of stress between the silicon substrate and the subsequently deposited nitride. Silicon substrate School of Microelectronic Engineering

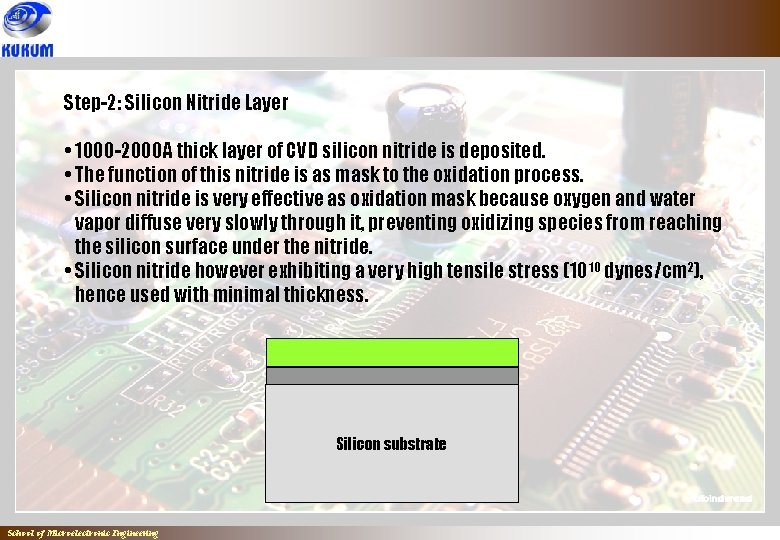

Step-2: Silicon Nitride Layer • 1000 -2000 A thick layer of CVD silicon nitride is deposited. • The function of this nitride is as mask to the oxidation process. • Silicon nitride is very effective as oxidation mask because oxygen and water vapor diffuse very slowly through it, preventing oxidizing species from reaching the silicon surface under the nitride. • Silicon nitride however exhibiting a very high tensile stress (10 10 dynes/cm 2), hence used with minimal thickness. Silicon substrate School of Microelectronic Engineering

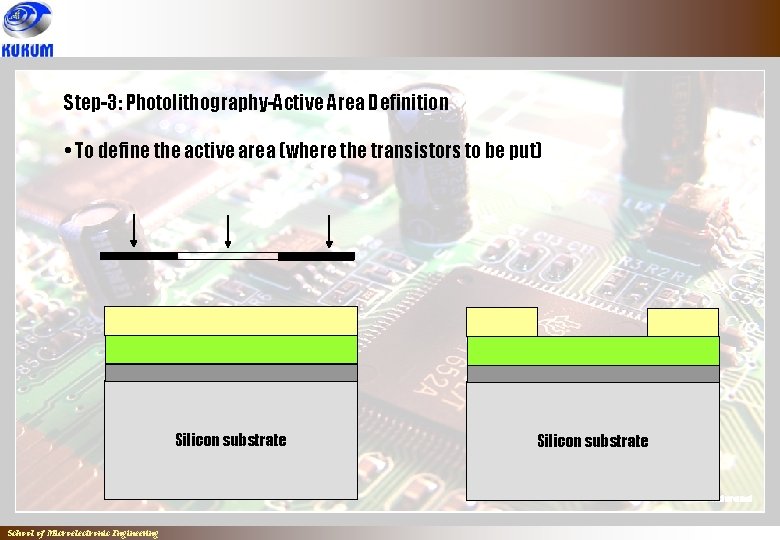

Step-3: Photolithography-Active Area Definition • To define the active area (where the transistors to be put) Silicon substrate School of Microelectronic Engineering Silicon substrate

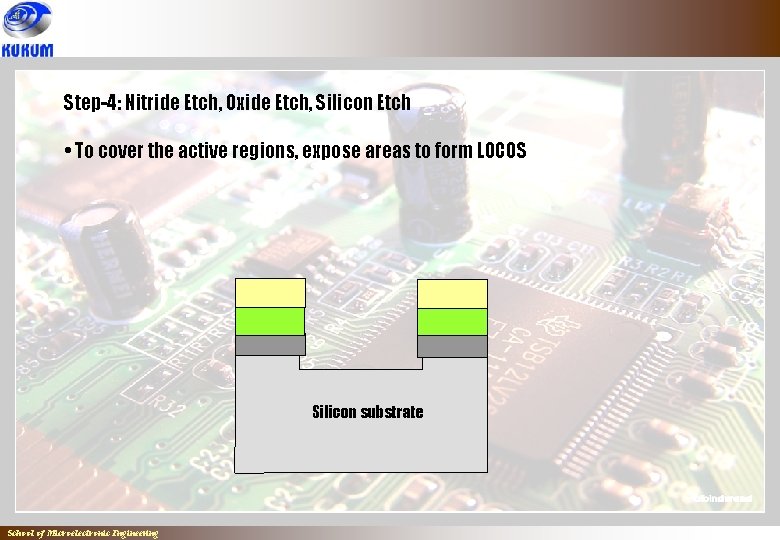

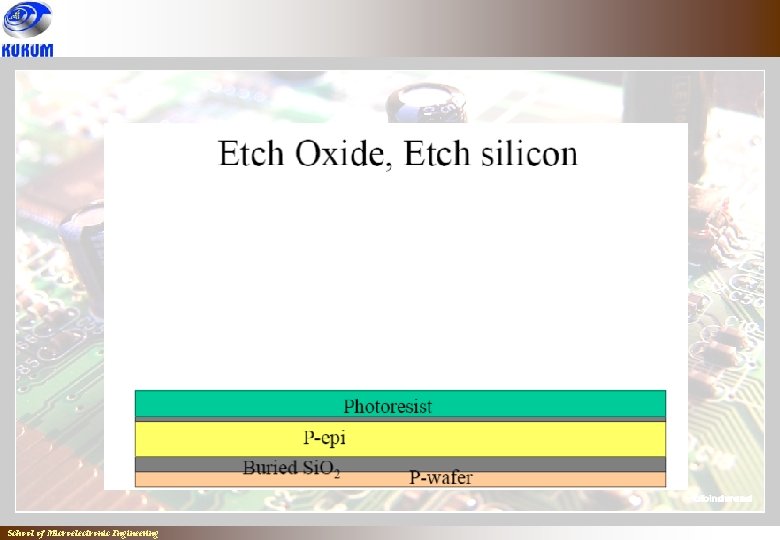

Step-4: Nitride Etch, Oxide Etch, Silicon Etch • To cover the active regions, expose areas to form LOCOS Silicon substrate School of Microelectronic Engineering

Step-5: Channel stop implant • To create a channel stop doping layer under Field Oxide. • In NMOS circuit, a p implant (boron, 60 -100 ke. V) is used, while in PMOS, arsenic is used. • PR is removed after the implant Silicon substrate School of Microelectronic Engineering

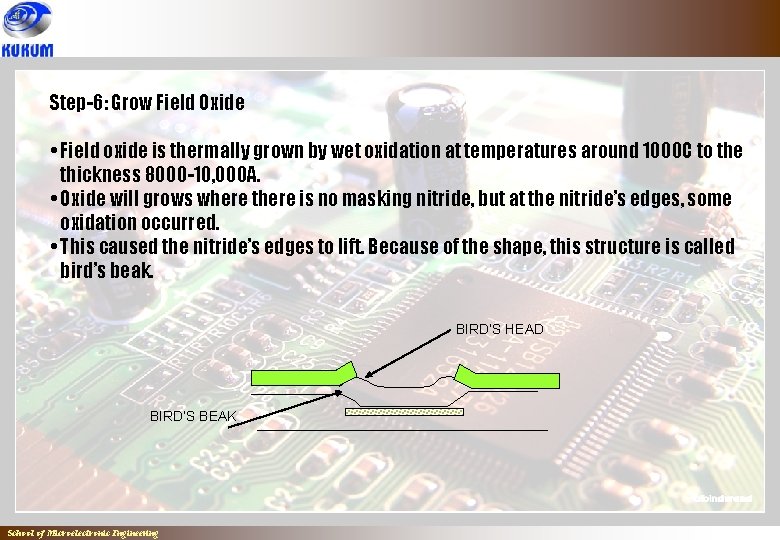

Step-6: Grow Field Oxide • Field oxide is thermally grown by wet oxidation at temperatures around 1000 C to the thickness 8000 -10, 000 A. • Oxide will grows where there is no masking nitride, but at the nitride’s edges, some oxidation occurred. • This caused the nitride’s edges to lift. Because of the shape, this structure is called bird’s beak. BIRD’S HEAD BIRD’S BEAK School of Microelectronic Engineering

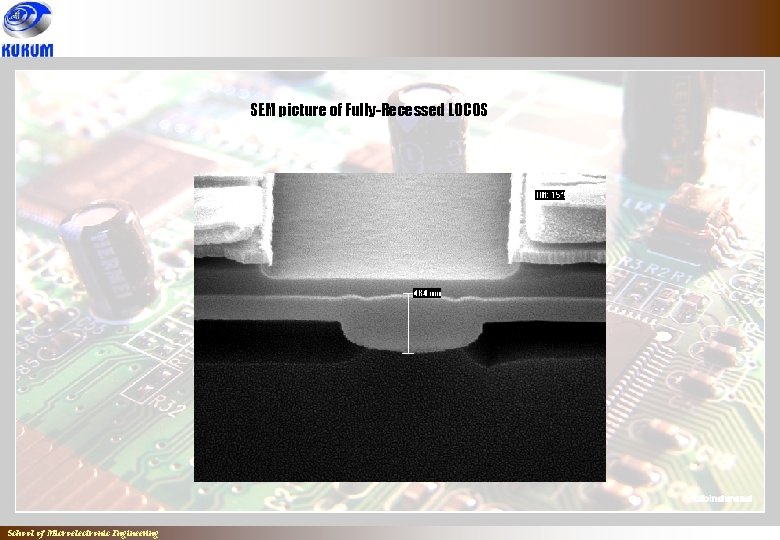

SEM picture of Fully-Recessed LOCOS School of Microelectronic Engineering

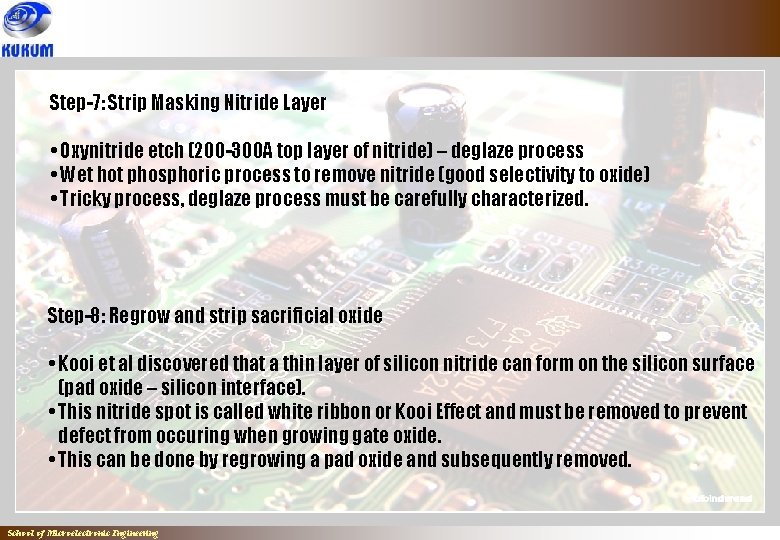

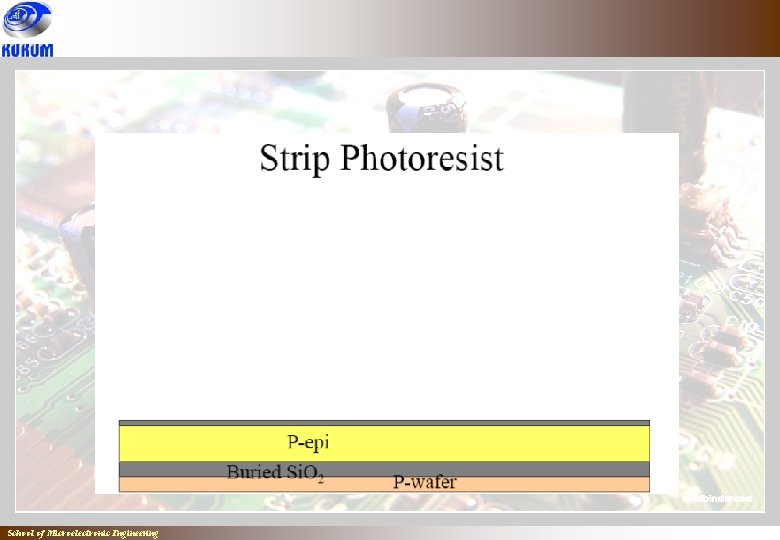

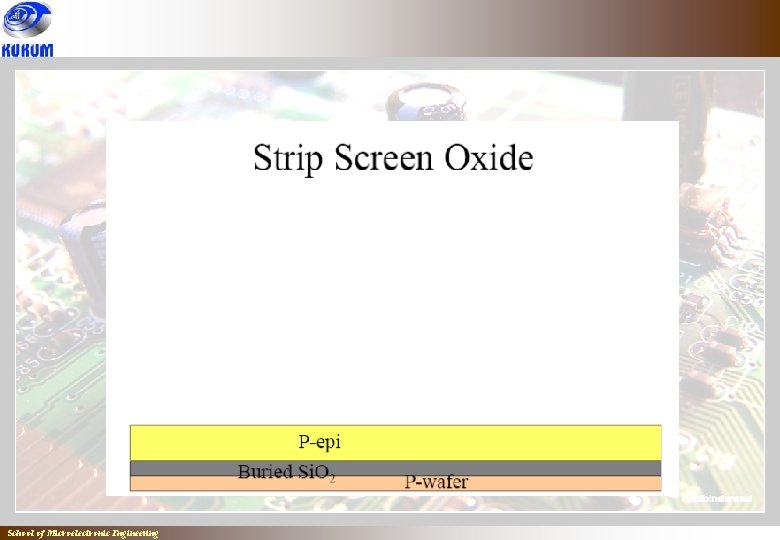

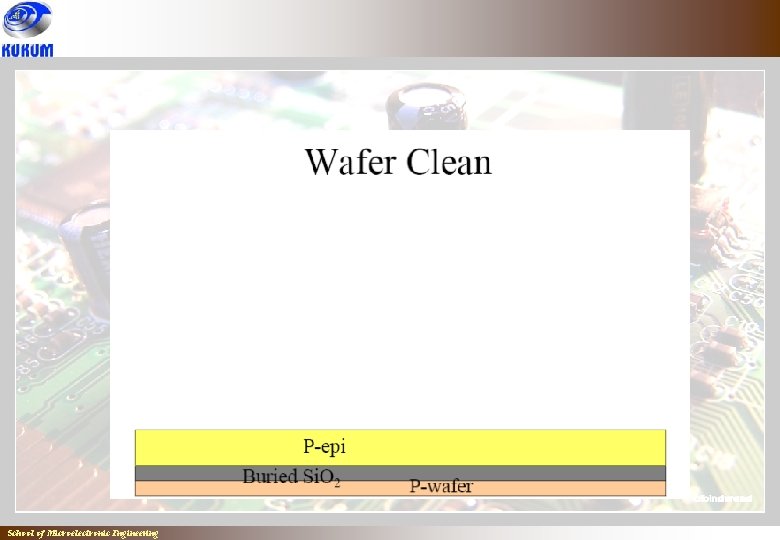

Step-7: Strip Masking Nitride Layer • Oxynitride etch (200 -300 A top layer of nitride) – deglaze process • Wet hot phosphoric process to remove nitride (good selectivity to oxide) • Tricky process, deglaze process must be carefully characterized. Step-8: Regrow and strip sacrificial oxide • Kooi et al discovered that a thin layer of silicon nitride can form on the silicon surface (pad oxide – silicon interface). • This nitride spot is called white ribbon or Kooi Effect and must be removed to prevent defect from occuring when growing gate oxide. • This can be done by regrowing a pad oxide and subsequently removed. School of Microelectronic Engineering

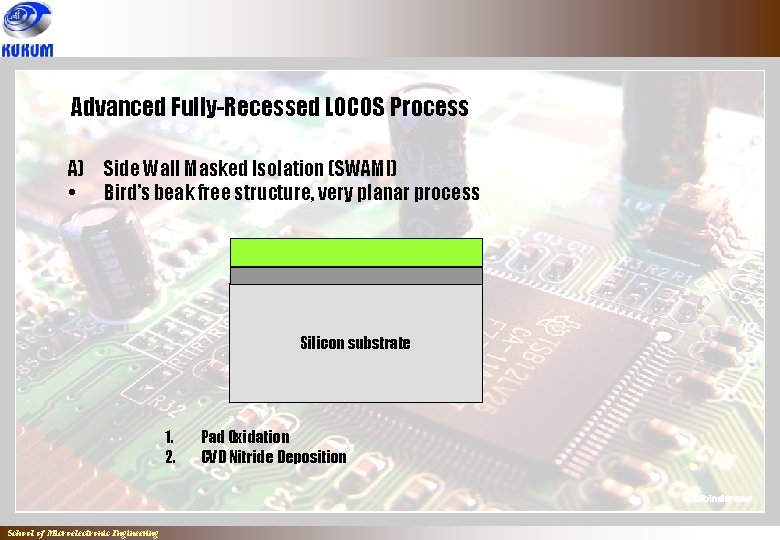

Advanced Fully-Recessed LOCOS Process A) Side Wall Masked Isolation (SWAMI) • Bird’s beak free structure, very planar process Silicon substrate 1. 2. School of Microelectronic Engineering Pad Oxidation CVD Nitride Deposition

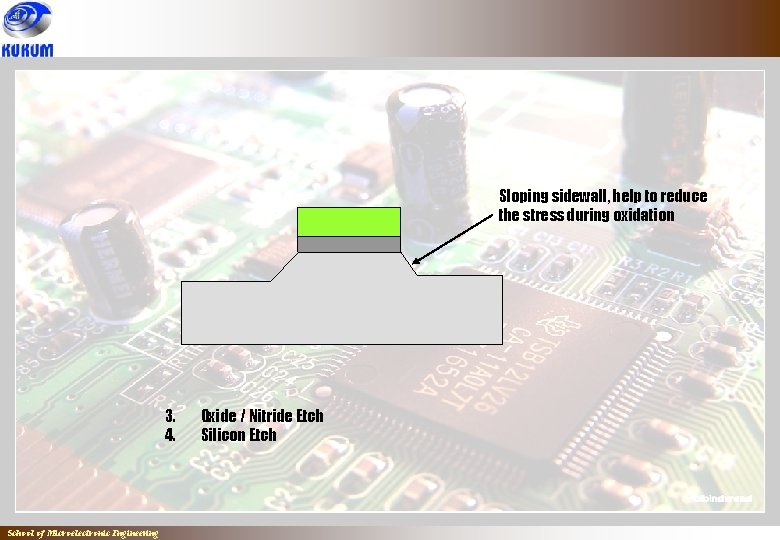

Sloping sidewall, help to reduce the stress during oxidation 3. 4. School of Microelectronic Engineering Oxide / Nitride Etch Silicon Etch

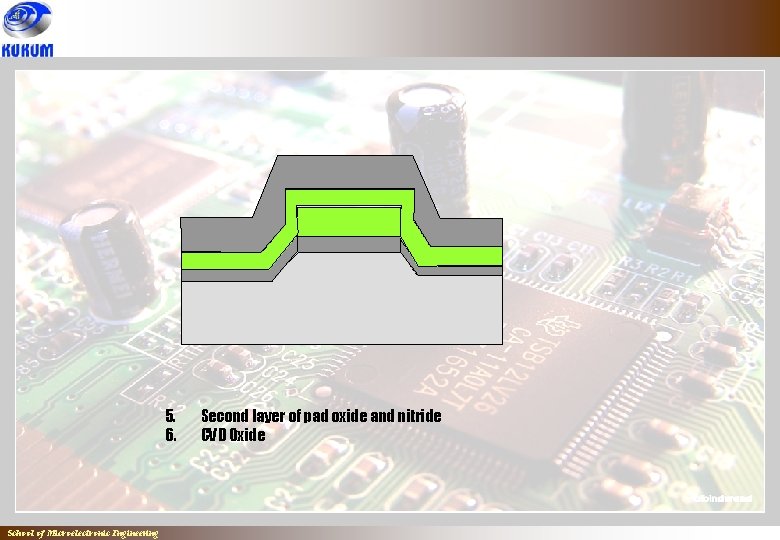

5. 6. School of Microelectronic Engineering Second layer of pad oxide and nitride CVD Oxide

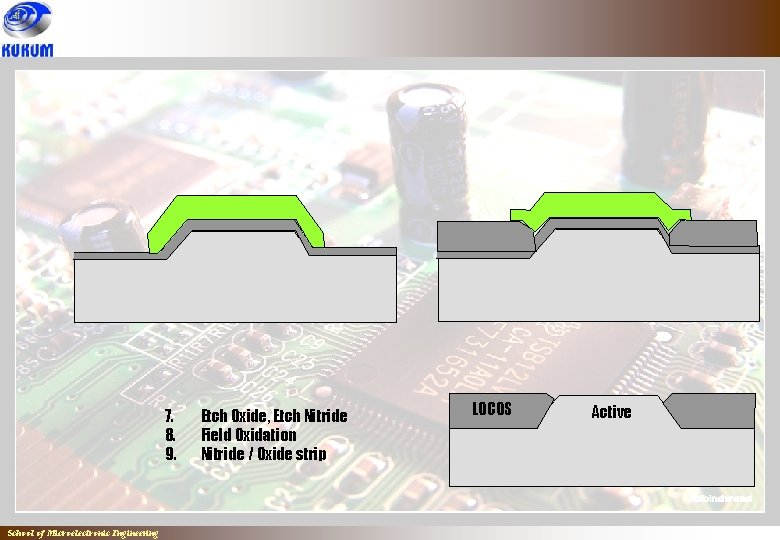

7. 8. 9. School of Microelectronic Engineering Etch Oxide, Etch Nitride Field Oxidation Nitride / Oxide strip LOCOS Active

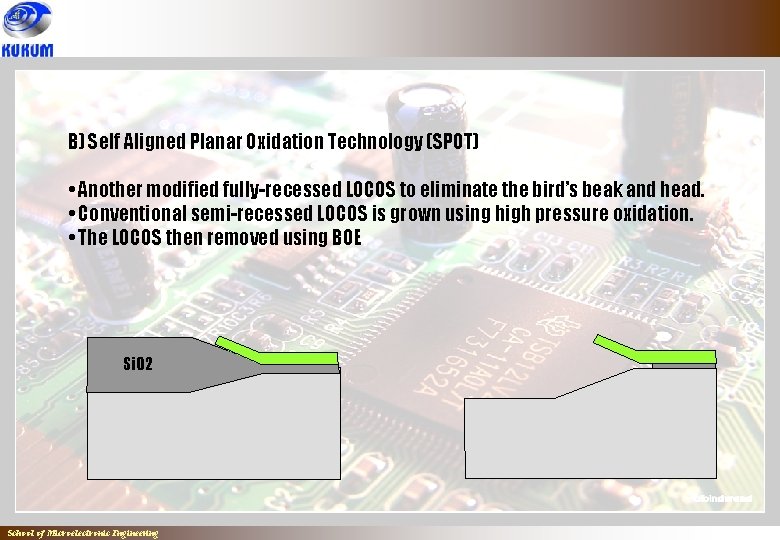

B) Self Aligned Planar Oxidation Technology (SPOT) • Another modified fully-recessed LOCOS to eliminate the bird’s beak and head. • Conventional semi-recessed LOCOS is grown using high pressure oxidation. • The LOCOS then removed using BOE Si. O 2 School of Microelectronic Engineering

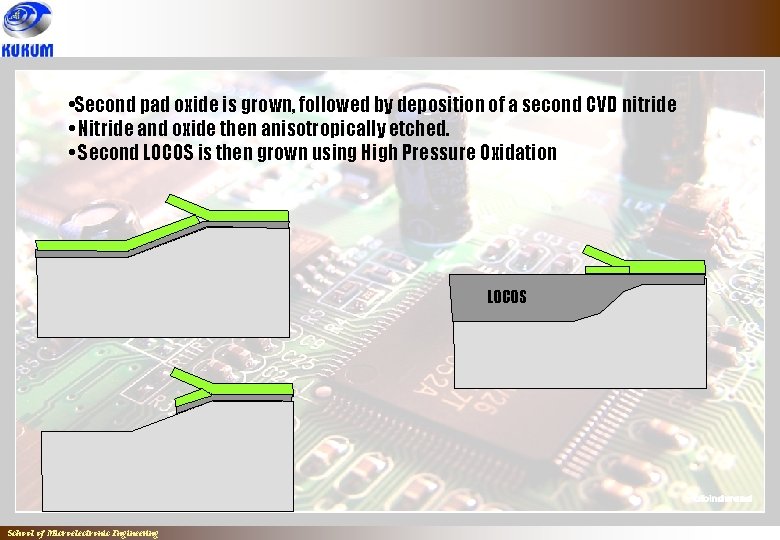

• Second pad oxide is grown, followed by deposition of a second CVD nitride • Nitride and oxide then anisotropically etched. • Second LOCOS is then grown using High Pressure Oxidation LOCOS School of Microelectronic Engineering

C) Fully Recessed Oxide (FUROX) D) OSELO E) ETC School of Microelectronic Engineering

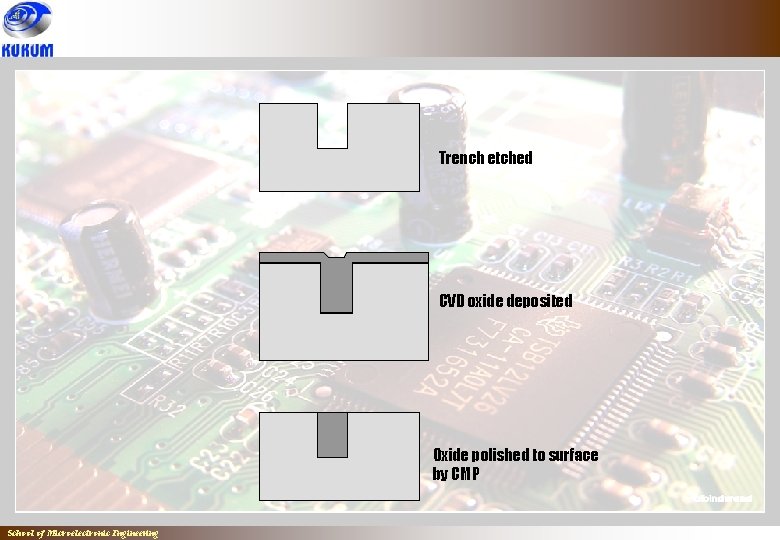

Trench Isolation Technology 4 major applications • Locos replacement for isolation within the well (STI) • Isolation in bipolar (Moderate Trench) • Latch prevention in CMOS (Moderate Trench) • Trench capacitor in DRAM (Deep Trench) 3 categories • Shallow trench <1 um • Moderate 1 -3 um • Deep >3 um deep Advantages Increase the packing density tremendously Disadvantages Complex to fabricate, very expensive machines Poor uniformity, Low throughput School of Microelectronic Engineering

Trench etched CVD oxide deposited Oxide polished to surface by CMP School of Microelectronic Engineering

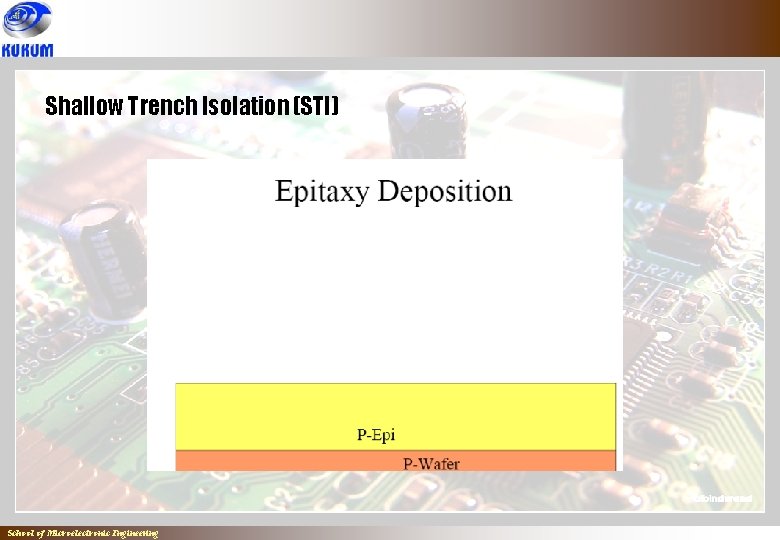

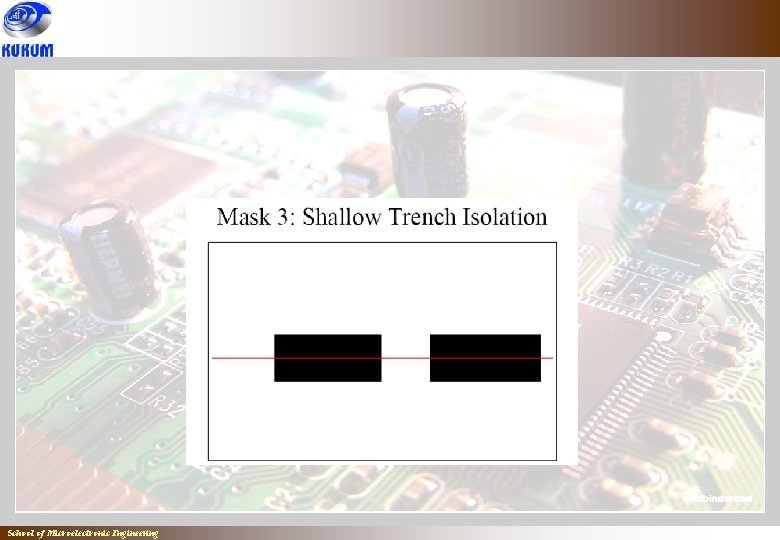

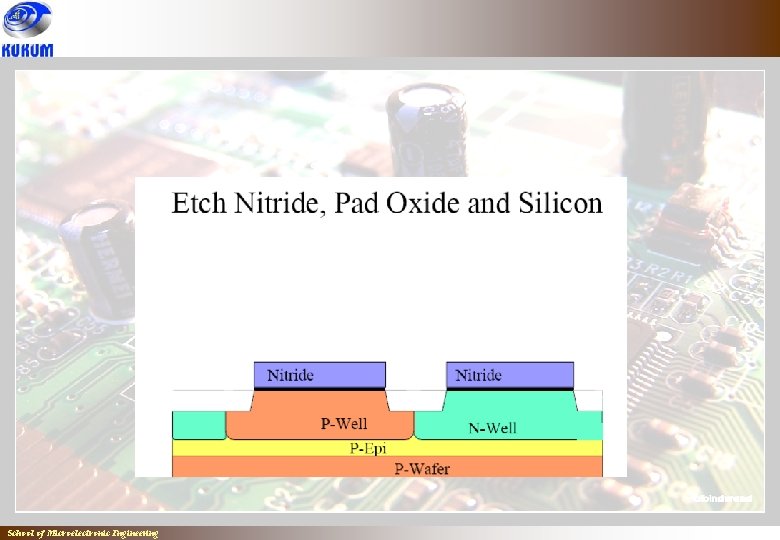

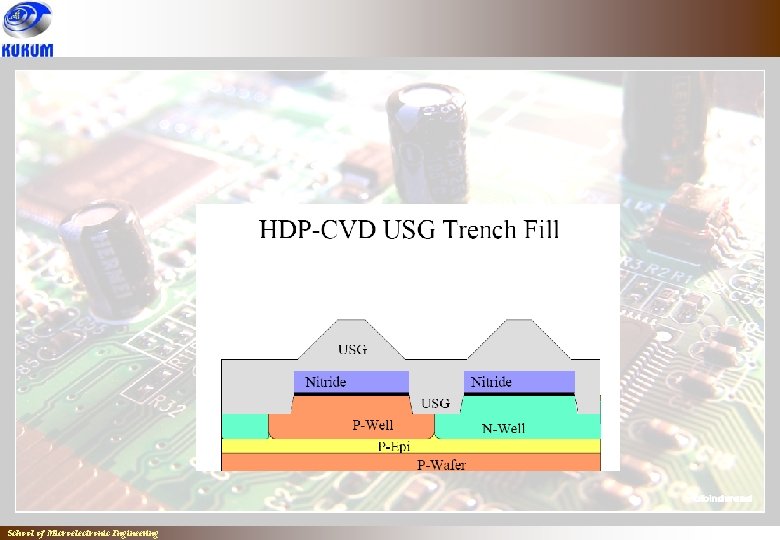

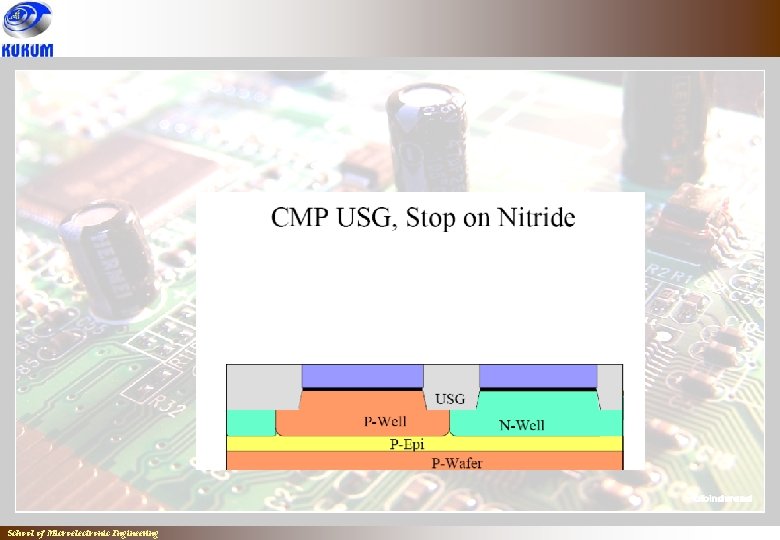

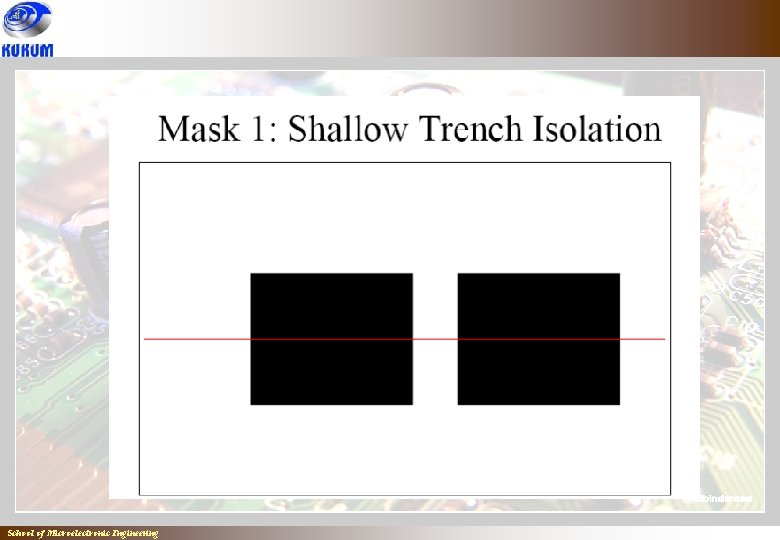

Shallow Trench Isolation (STI) School of Microelectronic Engineering

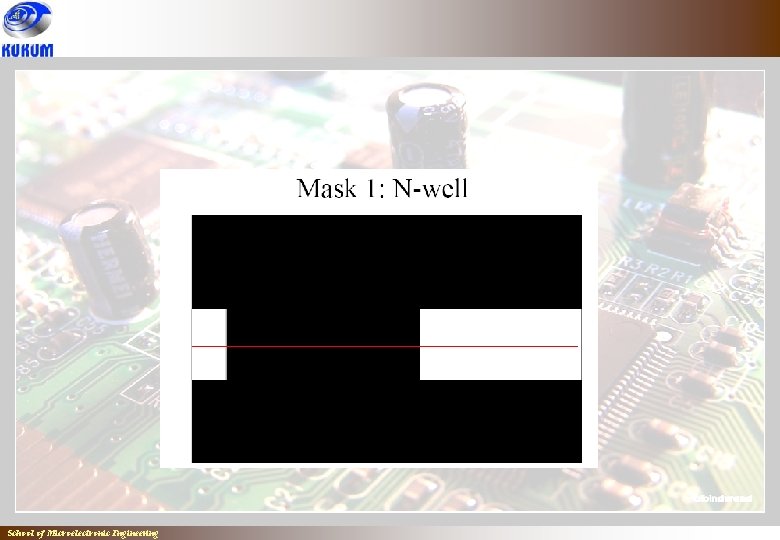

School of Microelectronic Engineering

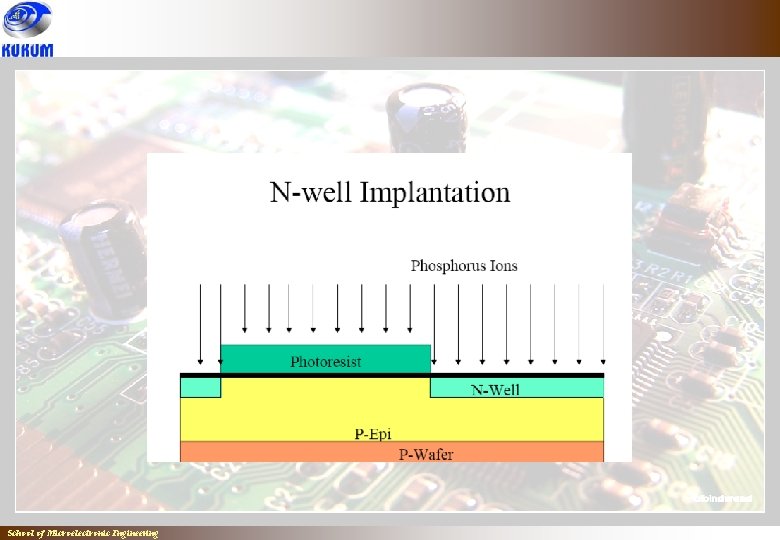

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

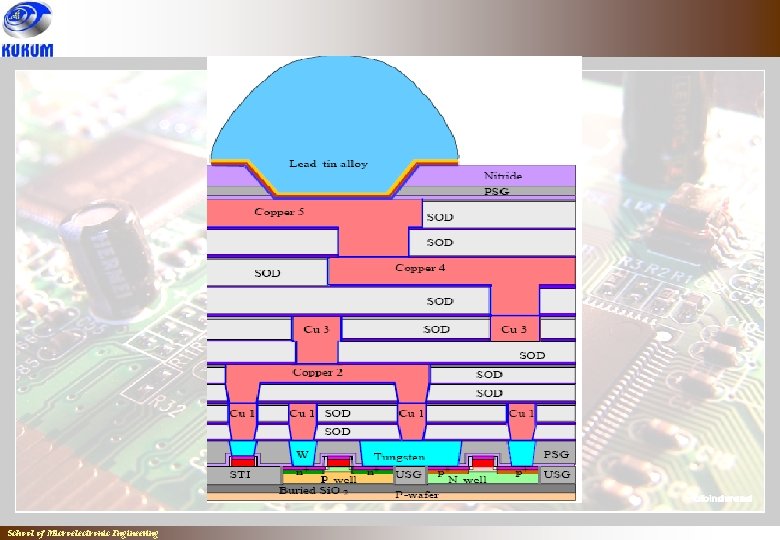

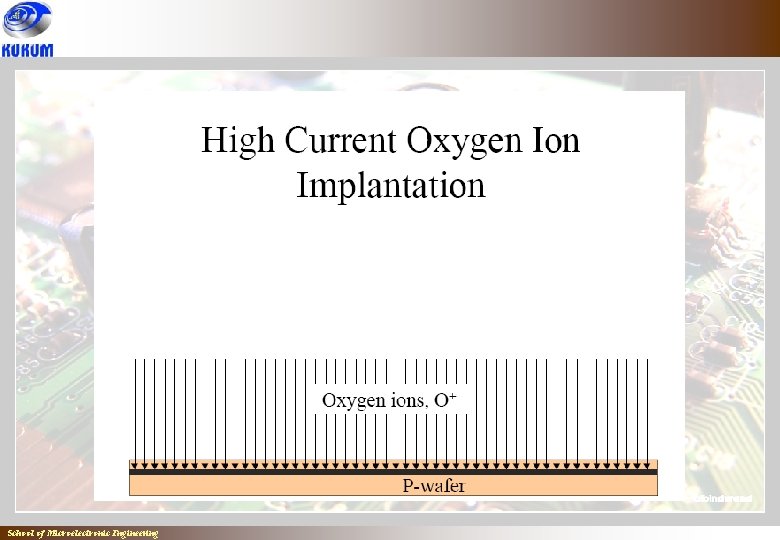

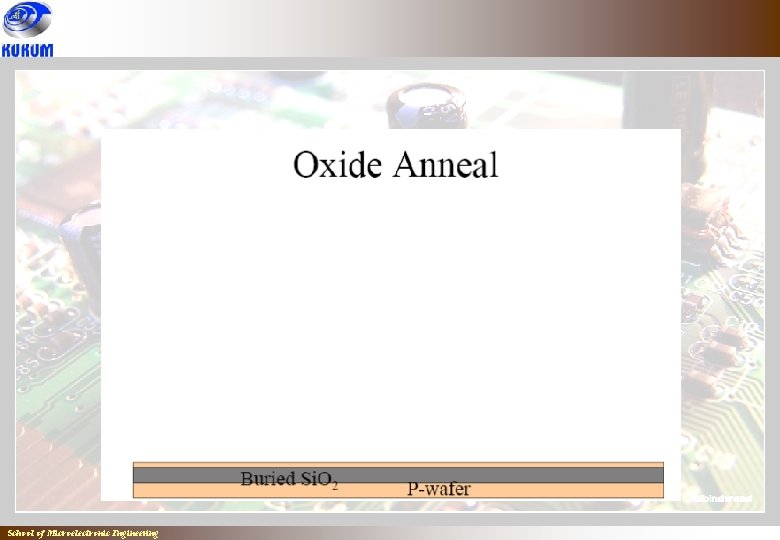

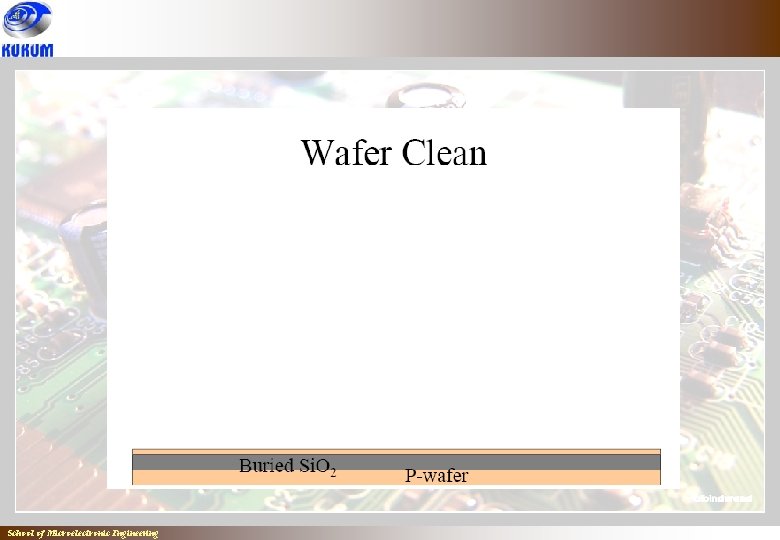

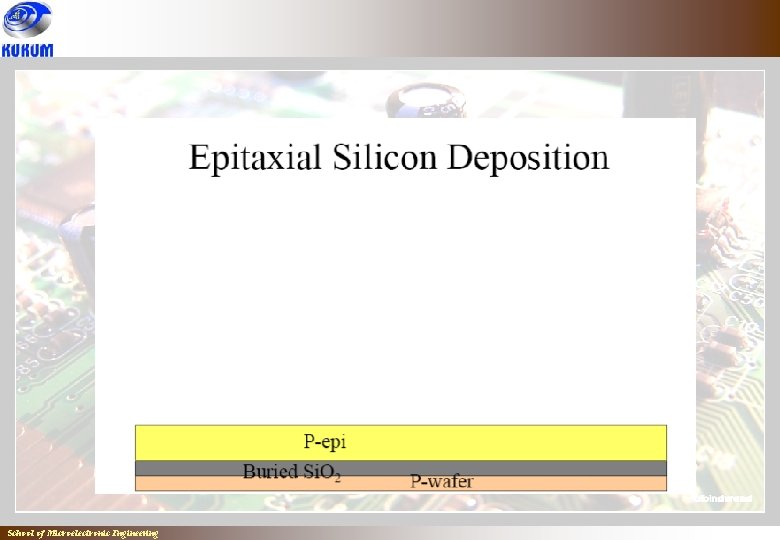

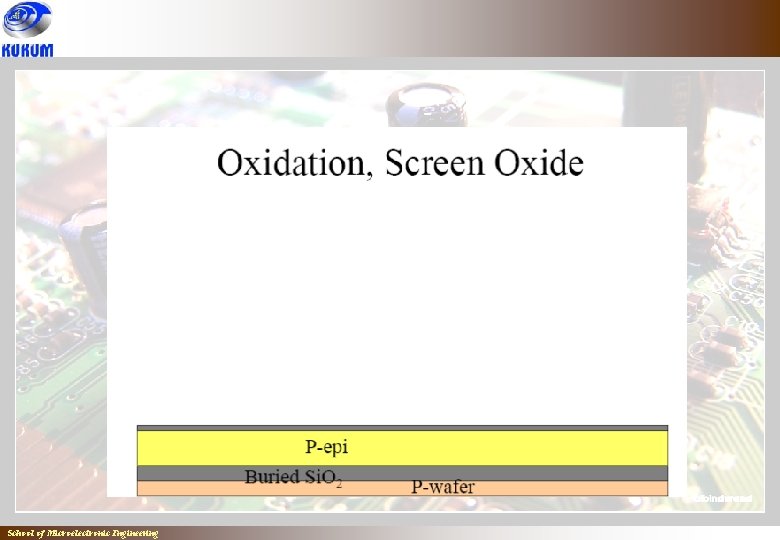

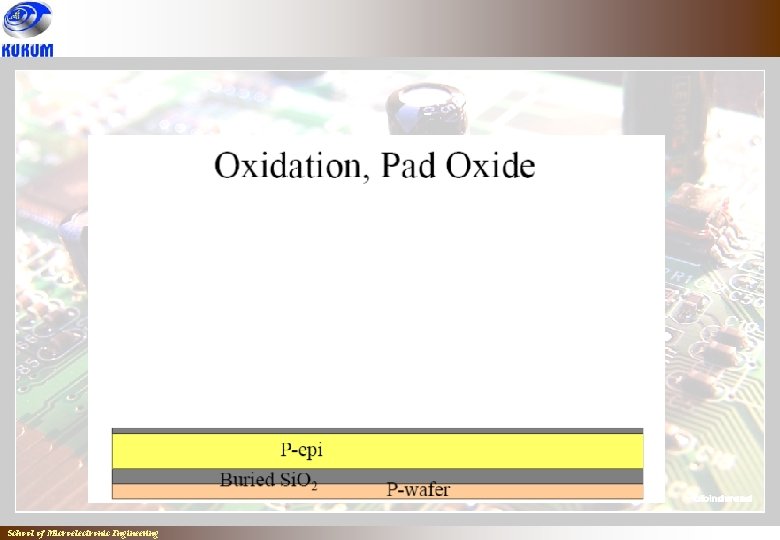

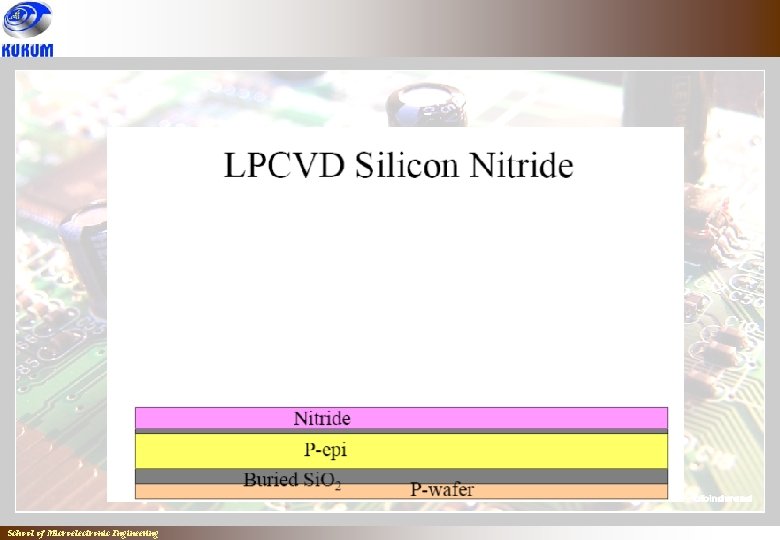

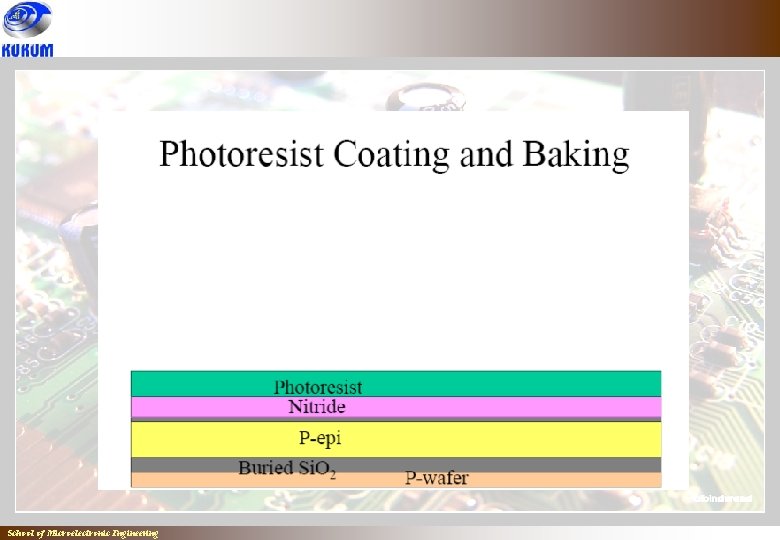

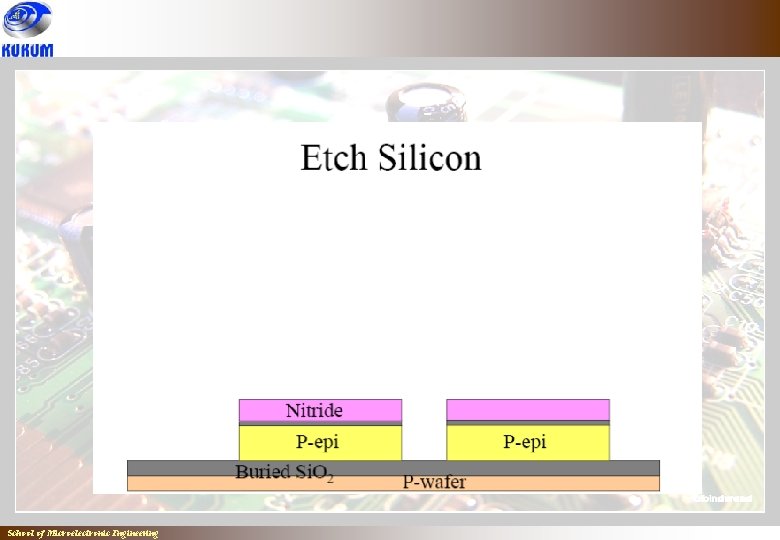

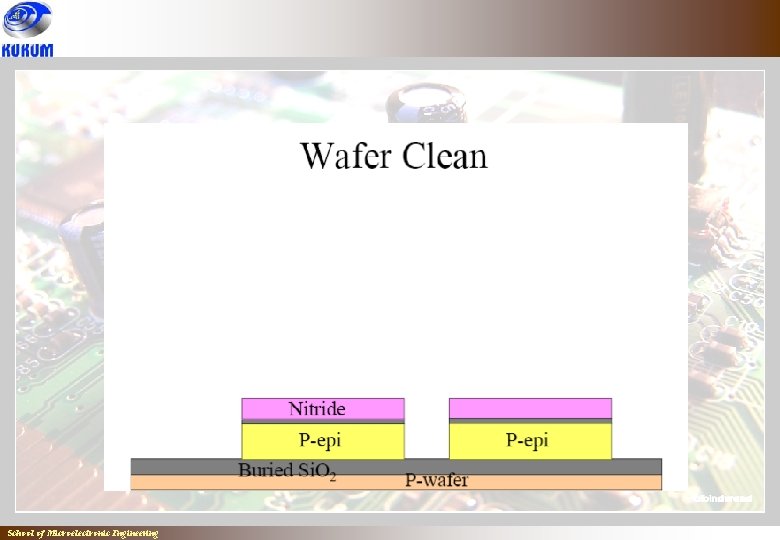

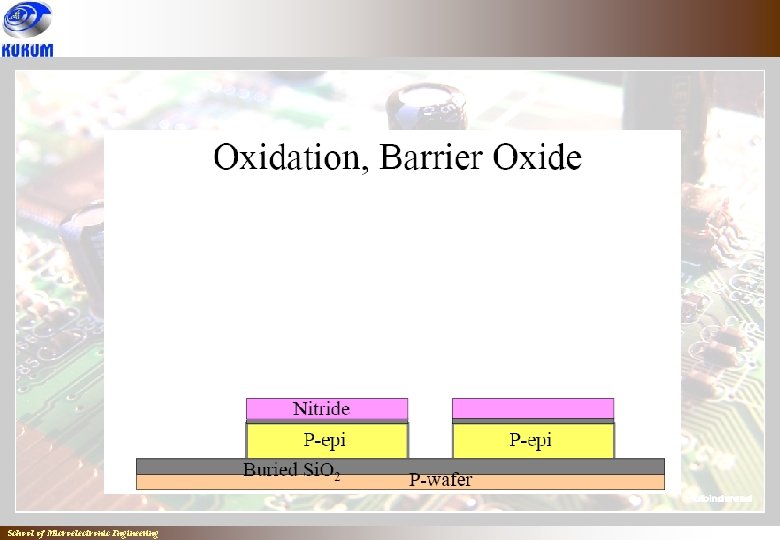

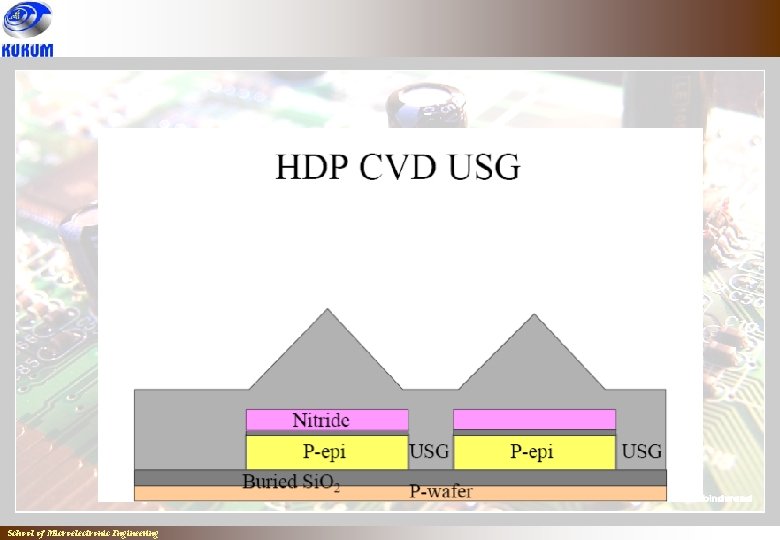

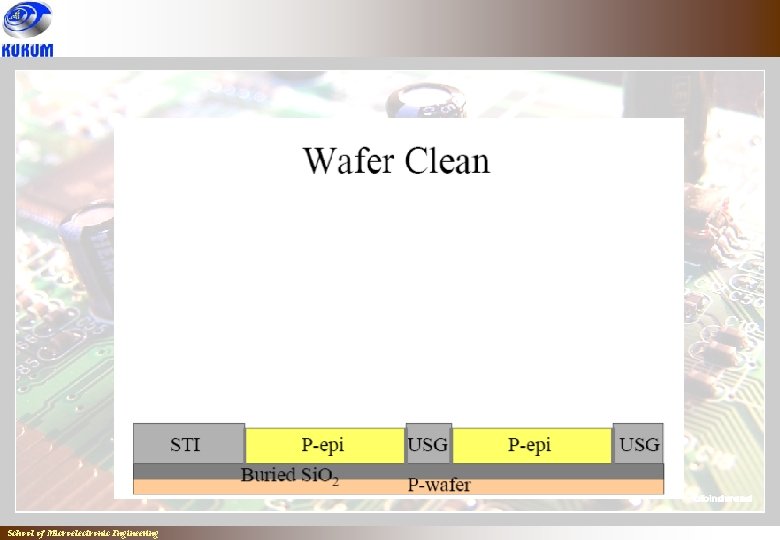

Silicon On Insulator (SOI) with STI Isolation Technology • • Completely isolate the transistor on silicon surface from the bulk silicon substrate. Tremendously increase the packing density of IC chip Mainstream isolation technology for high performance ICs for feature size below 0. 13 um process technology Normally coupled with Copper Interconnect Technology and Low-k Interlevel Dielectric. School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

School of Microelectronic Engineering

- Slides: 93