EMT 248 The Programmable Peripheral Interface Semester II

EMT 248: The Programmable Peripheral Interface Semester II 2013/14 School of Microelectronic Engineering Universiti Malaysia Perlis

What is the Programmable Peripheral Interface (8255 A)? Is a programmable universal I/O interface between MPU to the external devices through both parallel and serial interfaces. Ø Parallel data occur in system that use: § Displays § Keyboard § Printers (old printer) § Etc. Ø Serial data occurs in: § Some printers § Data communications Ø

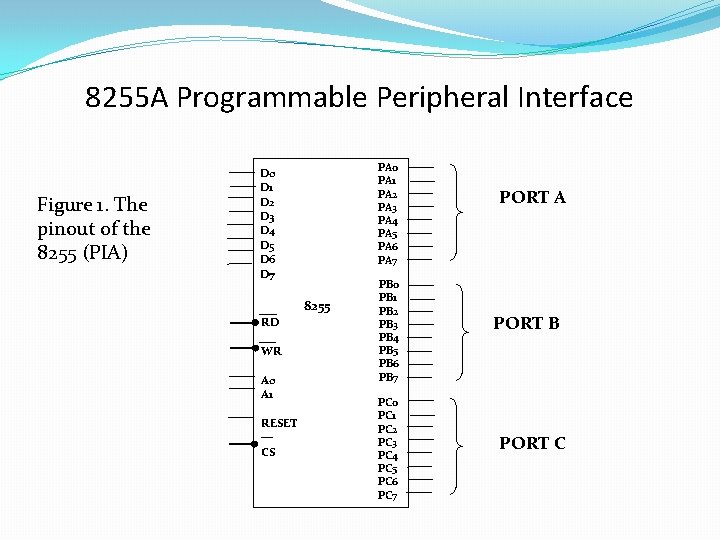

8255 PIA (Peripheral Interface Adapter) Ø 8255 can be programmed for data transfer in multipurpose mode, either as i/o or interrupt. Ø It has 24 I/O pins, that can be divided into two groups of 8 -bit parallel ports: Port A and Port B, and the rest belong to Port C. Ø Port C can be used as an individual bit or group of 4 -bit: § CUPPER (CU) § CLOWER (CL) Ø Figure 1 shows 3 kind of port groups in 8255.

8255 A Programmable Peripheral Interface Figure 1. The pinout of the 8255 (PIA) PA 0 PA 1 PA 2 PA 3 PA 4 PA 5 PA 6 PA 7 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 8255 RD WR A 0 A 1 RESET CS PB 0 PB 1 PB 2 PB 3 PB 4 PB 5 PB 6 PB 7 PC 0 PC 1 PC 2 PC 3 PC 4 PC 5 PC 6 PC 7 PORT A PORT B PORT C

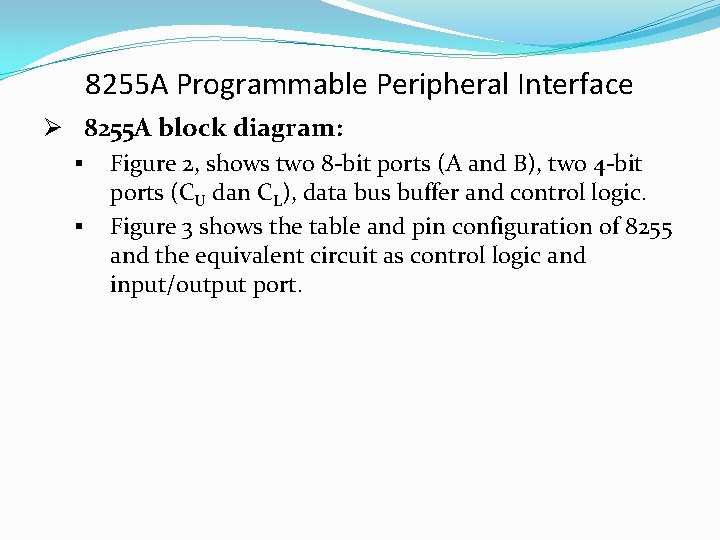

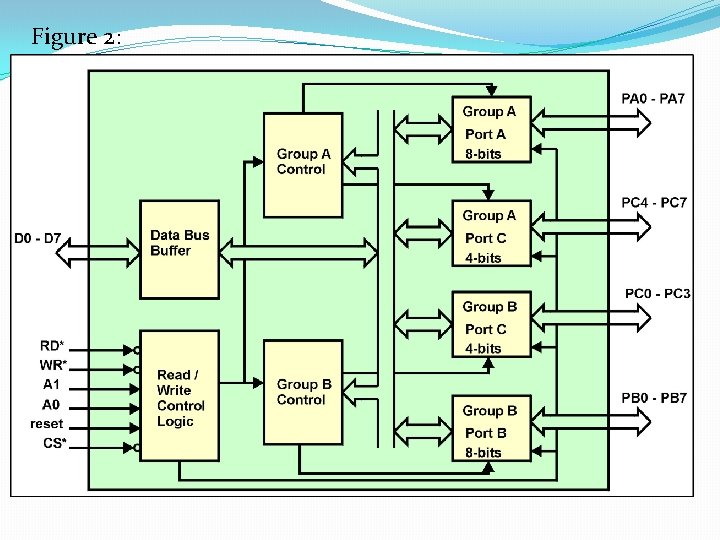

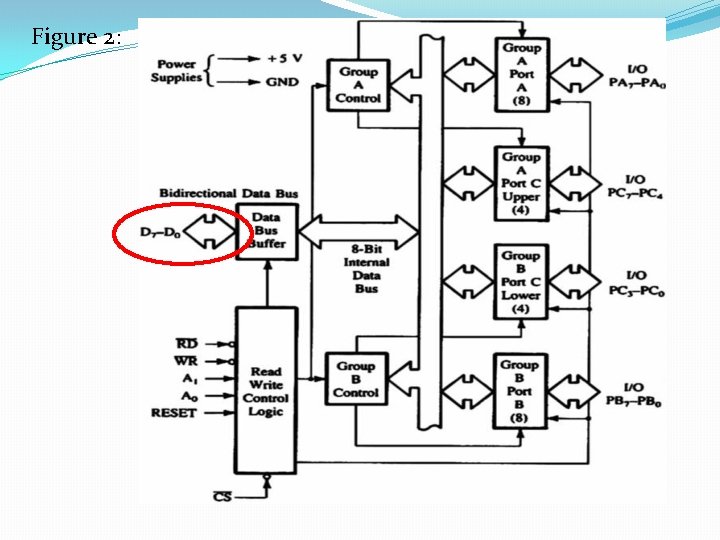

8255 A Programmable Peripheral Interface Ø 8255 A block diagram: § Figure 2, shows two 8 -bit ports (A and B), two 4 -bit ports (CU dan CL), data bus buffer and control logic. § Figure 3 shows the table and pin configuration of 8255 and the equivalent circuit as control logic and input/output port.

Figure 2:

Figure 3:

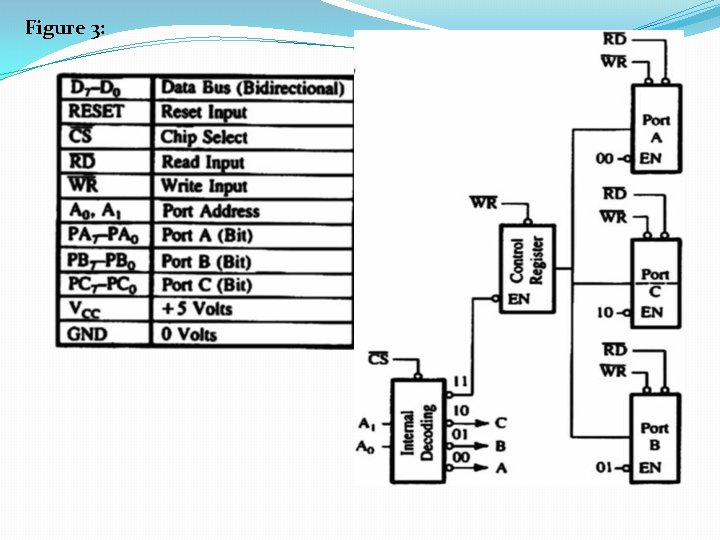

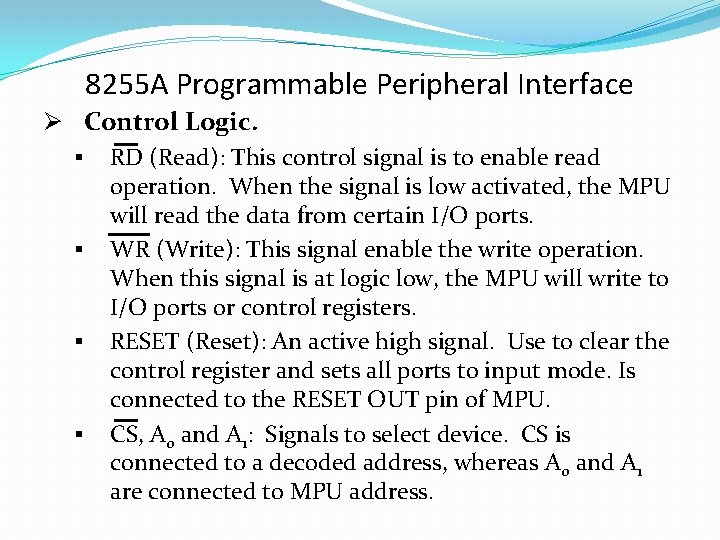

8255 A Programmable Peripheral Interface Ø Control Logic. § RD (Read): This control signal is to enable read operation. When the signal is low activated, the MPU will read the data from certain I/O ports. § WR (Write): This signal enable the write operation. When this signal is at logic low, the MPU will write to I/O ports or control registers. § RESET (Reset): An active high signal. Use to clear the control register and sets all ports to input mode. Is connected to the RESET OUT pin of MPU. § CS, A 0 and A 1: Signals to select device. CS is connected to a decoded address, whereas A 0 and A 1 are connected to MPU address.

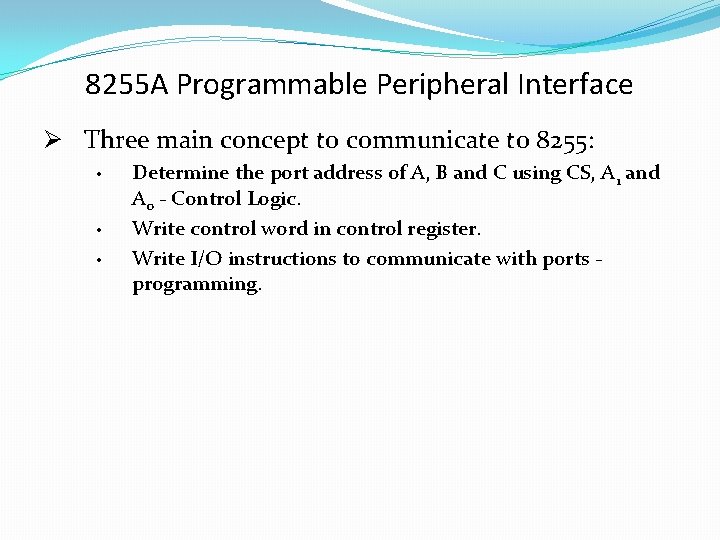

8255 A Programmable Peripheral Interface Ø Three main concept to communicate to 8255: • • • Determine the port address of A, B and C using CS, A 1 and A 0 - Control Logic. Write control word in control register. Write I/O instructions to communicate with ports programming.

Determine the port address of A, B and C using CS, A 1 and A 0 (Control Logic).

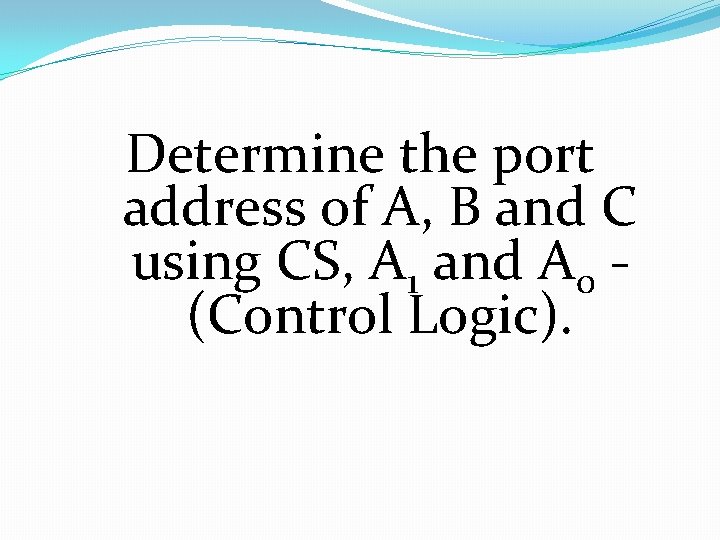

8255 A - 8085 A Interface 8085 MPU

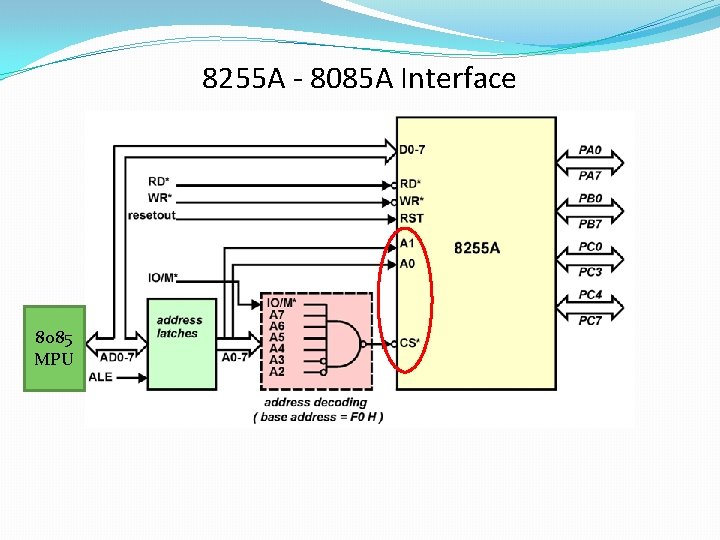

Control Logic Ø CS signal is a Master Chip Select, whereas A 0 and A 1 determine the input/output ports or control registers as tabulated in Table 1: The function of CS, A 0 and A 1 CS 0 A 1 0 A 0 0 Selection port A 0 0 1 port B 0 1 0 port C 0 1 1 Control Register 1 X X 8255 is disabled

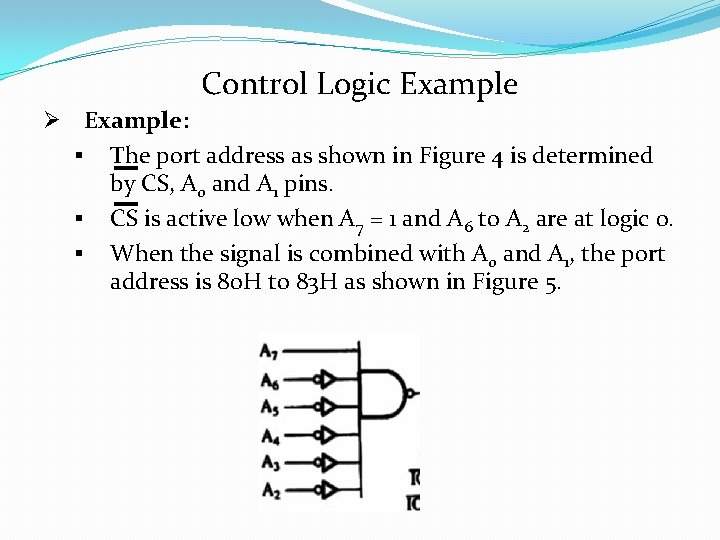

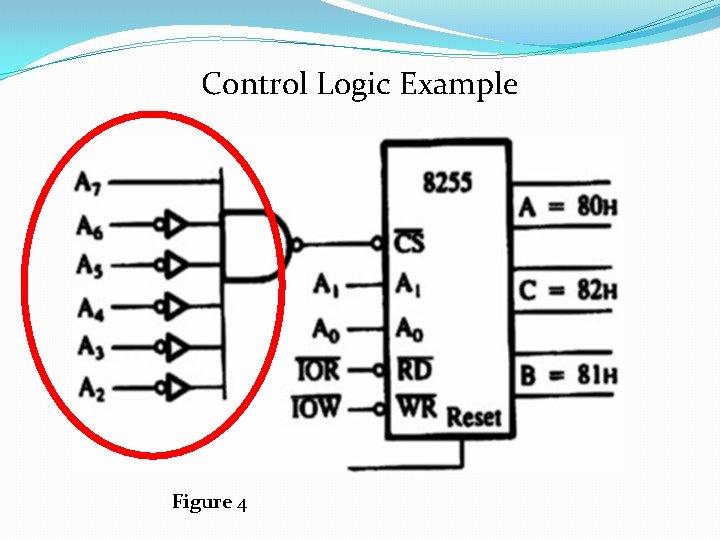

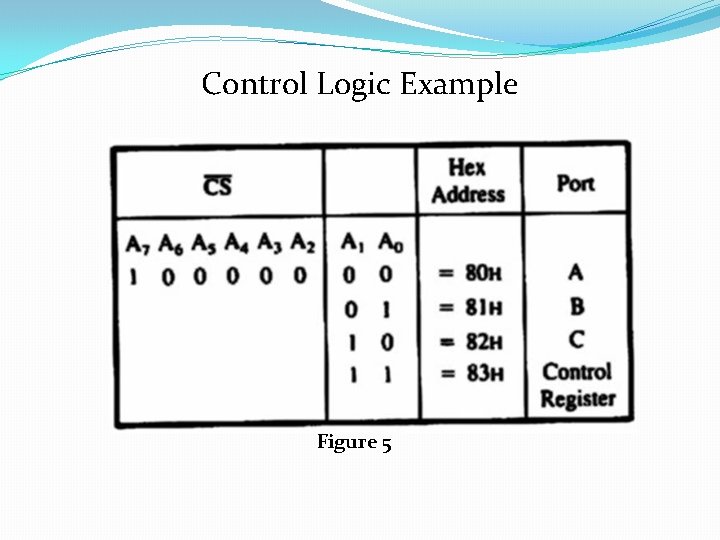

Control Logic Example Ø Example: § The port address as shown in Figure 4 is determined by CS, A 0 and A 1 pins. § CS is active low when A 7 = 1 and A 6 to A 2 are at logic 0. § When the signal is combined with A 0 and A 1, the port address is 80 H to 83 H as shown in Figure 5.

Control Logic Example Figure 4

Control Logic Example Figure 5

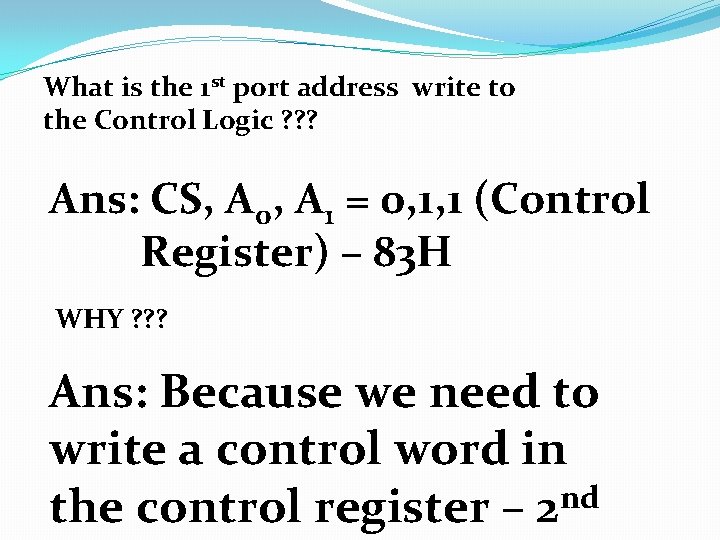

What is the 1 st port address write to the Control Logic ? ? ? Ans: CS, A 0, A 1 = 0, 1, 1 (Control Register) – 83 H WHY ? ? ? Ans: Because we need to write a control word in nd the control register – 2

Write control word in control register.

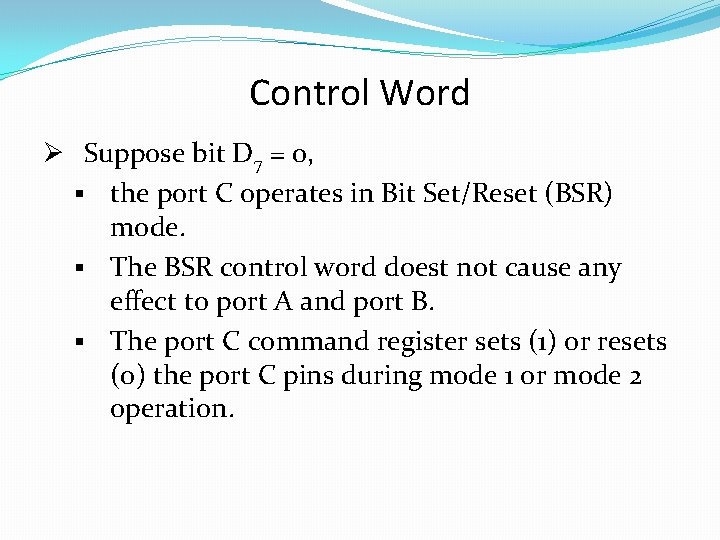

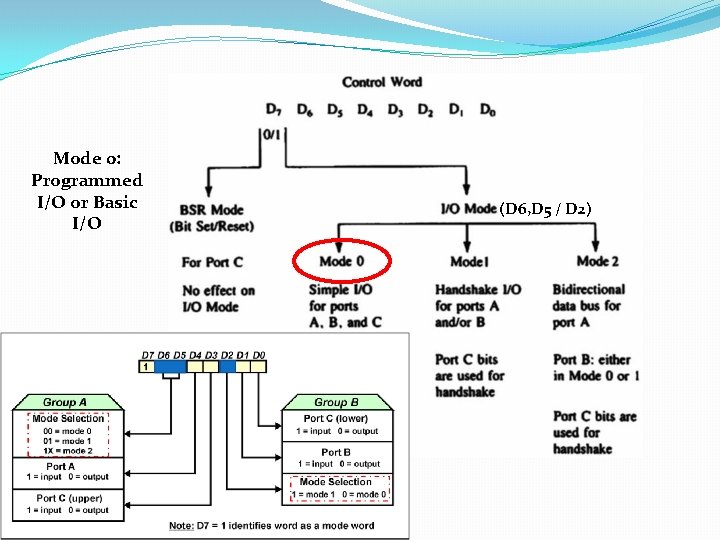

Control Word Ø Figure 6 shows the function of control register, the content in this register is known as Control Word which determines input/output ports. Ø This register is used to write control word when A 0 and A 1 are at logic 1. Ø Bit D 7 in control register determines the I/O function or Set/Reset. If bit D 7 = 1, bits D 6 - D 0 determine the function of I/O in multiple modes as shown in Figure 6.

Control Word Ø Suppose bit D 7 = 0, § the port C operates in Bit Set/Reset (BSR) mode. § The BSR control word doest not cause any effect to port A and port B. § The port C command register sets (1) or resets (0) the port C pins during mode 1 or mode 2 operation.

Figure 6: Functions of Control Word.

Figure 2:

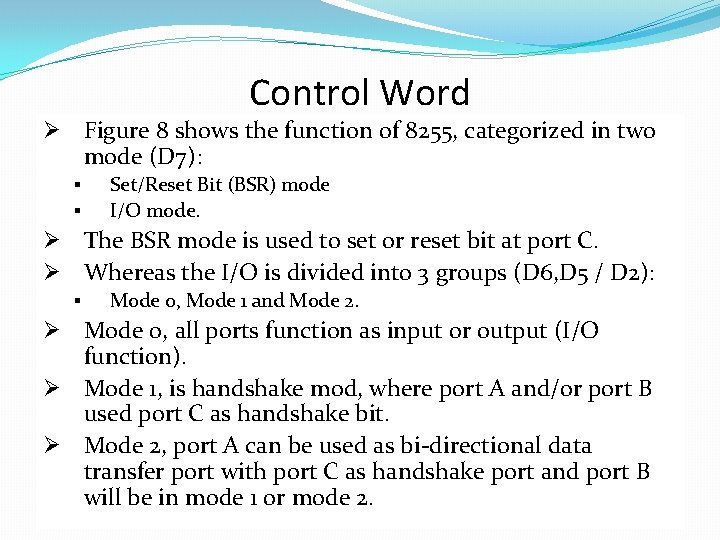

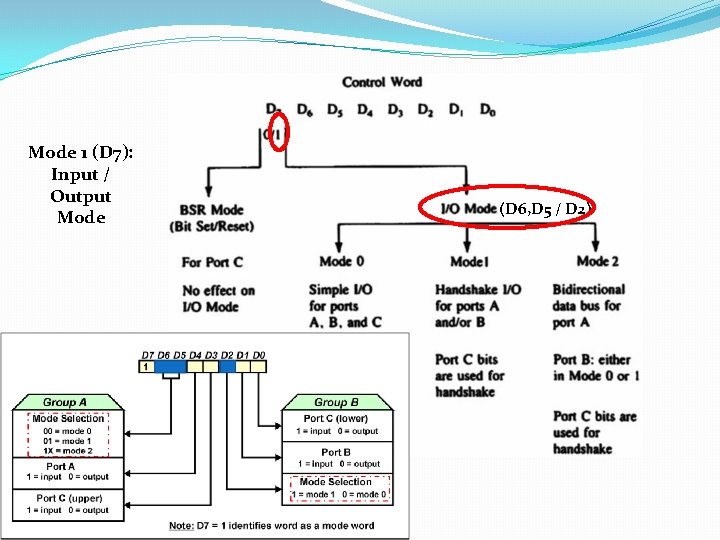

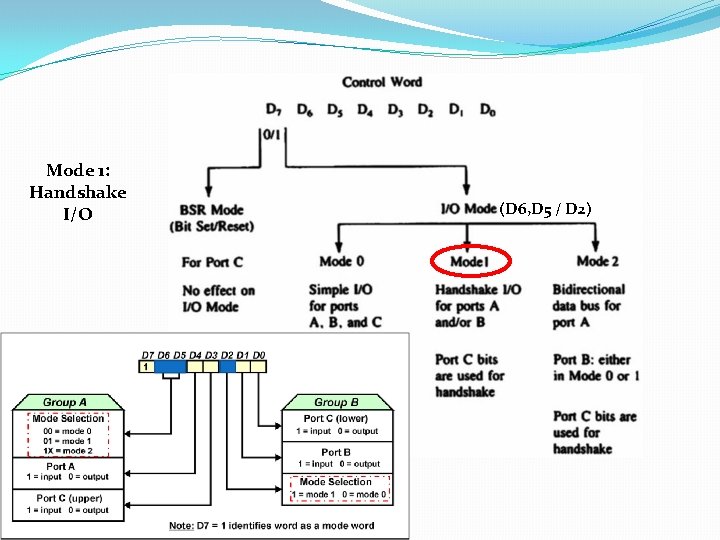

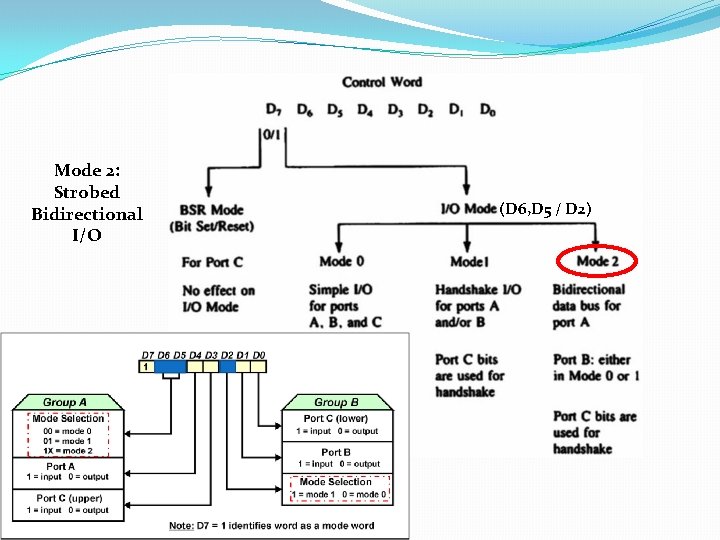

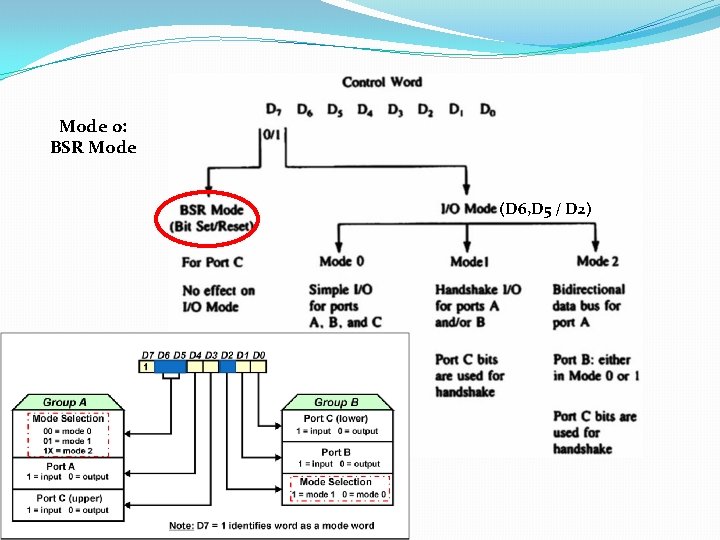

Control Word Ø Figure 8 shows the function of 8255, categorized in two mode (D 7): § § Set/Reset Bit (BSR) mode I/O mode. Ø The BSR mode is used to set or reset bit at port C. Ø Whereas the I/O is divided into 3 groups (D 6, D 5 / D 2): § Mode 0, Mode 1 and Mode 2. Ø Mode 0, all ports function as input or output (I/O function). Ø Mode 1, is handshake mod, where port A and/or port B used port C as handshake bit. Ø Mode 2, port A can be used as bi-directional data transfer port with port C as handshake port and port B will be in mode 1 or mode 2.

Figure 8: Function of 8255 (D 6, D 5 / D 2)

Mode 1 (D 7): Input / Output Mode

Mode 1 (D 7): Input / Output Mode (D 6, D 5 / D 2)

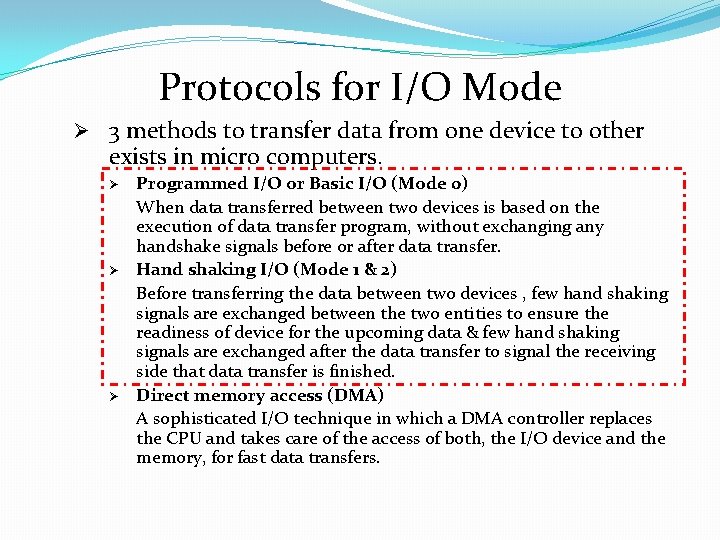

Protocols for I/O Mode Ø 3 methods to transfer data from one device to other exists in micro computers. Ø Ø Ø Programmed I/O or Basic I/O (Mode 0) When data transferred between two devices is based on the execution of data transfer program, without exchanging any handshake signals before or after data transfer. Hand shaking I/O (Mode 1 & 2) Before transferring the data between two devices , few hand shaking signals are exchanged between the two entities to ensure the readiness of device for the upcoming data & few hand shaking signals are exchanged after the data transfer to signal the receiving side that data transfer is finished. Direct memory access (DMA) A sophisticated I/O technique in which a DMA controller replaces the CPU and takes care of the access of both, the I/O device and the memory, for fast data transfers.

Mode 0: Programmed I/O or Basic I/O (D 6, D 5 / D 2)

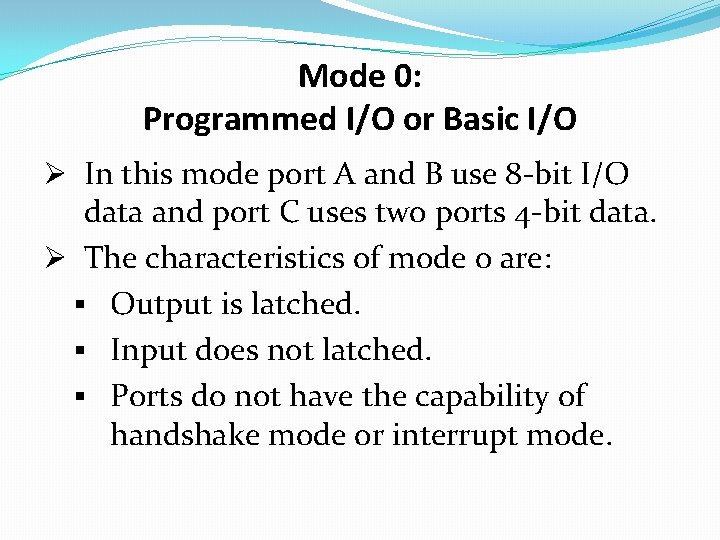

Mode 0: Programmed I/O or Basic I/O Ø In this mode port A and B use 8 -bit I/O data and port C uses two ports 4 -bit data. Ø The characteristics of mode 0 are: § Output is latched. § Input does not latched. § Ports do not have the capability of handshake mode or interrupt mode.

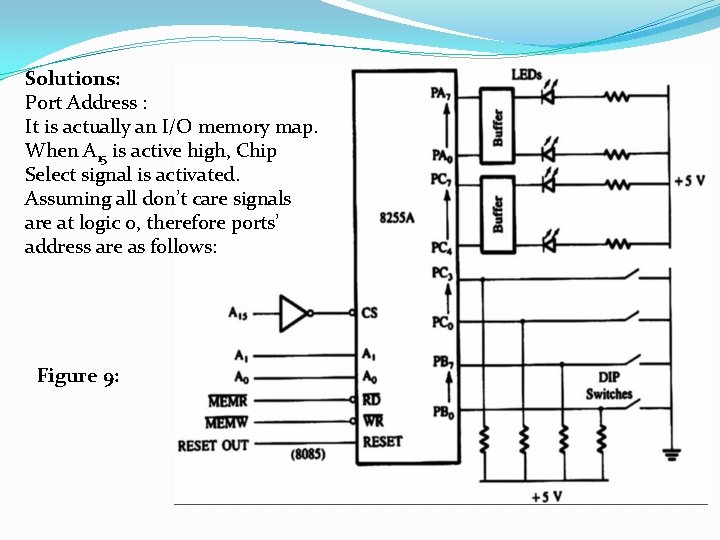

Mode 0: Programmed I/O or Basic I/O Ø Example : § Determine the port address of circuit in Figure 9. § Determine the control word in Mode 0, in order to determine ports A and CU as output port and ports B and CL as input ports. § Write a program to read DIP switch and display the reading from port B to port A, from port CL to port CU.

Solutions: Port Address : It is actually an I/O memory map. When A 15 is active high, Chip Select signal is activated. Assuming all don’t care signals are at logic 0, therefore ports’ address are as follows: Figure 9:

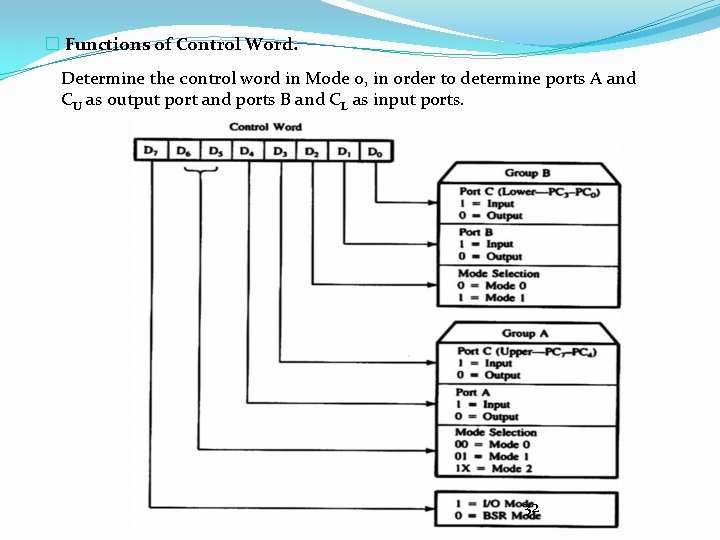

� Functions of Control Word. Determine the control word in Mode 0, in order to determine ports A and CU as output port and ports B and CL as input ports. 32

Ø Write a program to read DIP switch and display the reading from port B to port A, from port CL to port CU.

Mode 1: Handshake I/O (D 6, D 5 / D 2)

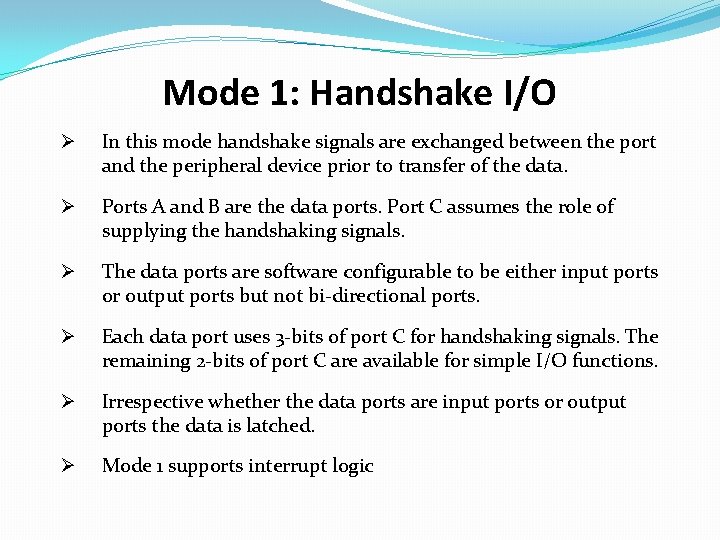

Mode 1: Handshake I/O Ø In this mode handshake signals are exchanged between the port and the peripheral device prior to transfer of the data. Ø Ports A and B are the data ports. Port C assumes the role of supplying the handshaking signals. Ø The data ports are software configurable to be either input ports or output ports but not bi-directional ports. Ø Each data port uses 3 -bits of port C for handshaking signals. The remaining 2 -bits of port C are available for simple I/O functions. Ø Irrespective whether the data ports are input ports or output ports the data is latched. Ø Mode 1 supports interrupt logic

What is Handshaking ? ? ? The handshaking method solves the problem of strobe method by introducing a second control signal that provides a reply to the unit that initiates the transfer.

Principle of Handshaking Ø The basic principle of the two-wire handshaking method of data transfer is as follow: § One control line is in the same direction as the data flows in the bus from the source to destination. It is used by source unit to inform the destination unit whethere a valid data in the bus. The other control line is in the other direction from the destination to the source. It is used by the destination unit to inform the source whether it can accept the data. The sequence of control during the transfer depends on the unit that initiates the transfer.

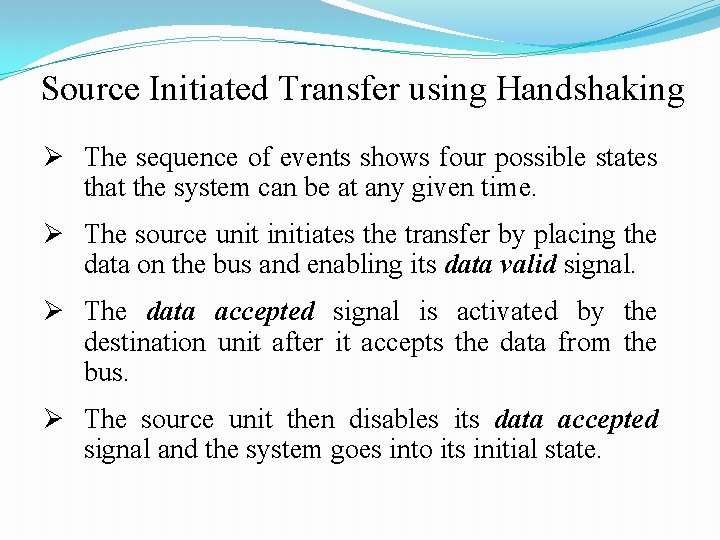

Source Initiated Transfer using Handshaking Ø The sequence of events shows four possible states that the system can be at any given time. Ø The source unit initiates the transfer by placing the data on the bus and enabling its data valid signal. Ø The data accepted signal is activated by the destination unit after it accepts the data from the bus. Ø The source unit then disables its data accepted signal and the system goes into its initial state.

Source Initiated Transfer using Handshaking

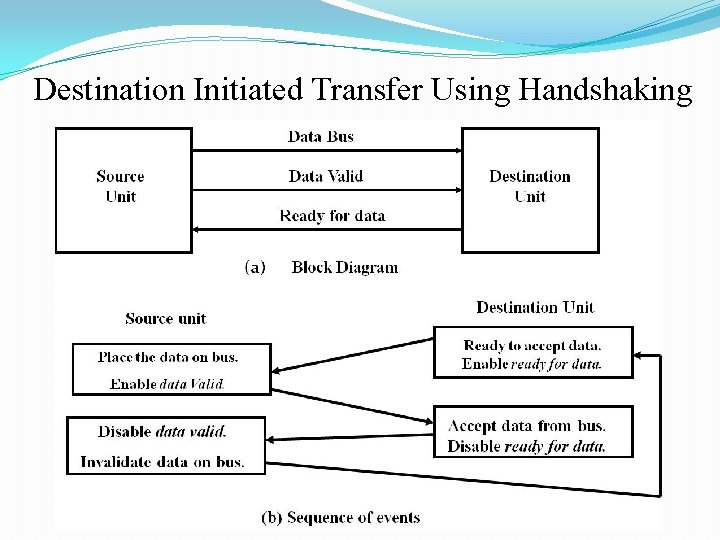

Destination Initiated Transfer Using Handshaking Ø The name of the signal generated by the destination unit has been changed to ready for data to reflects its new meaning. Ø The source unit in this case does not place data on the bus until after it receives the ready for data signal from the destination unit. Ø From there on, the handshaking procedure follows the same pattern as in the source initiated case. Ø The only difference between the Source Initiated and the Destination Initiated transfer is in their choice of Initial sate.

Destination Initiated Transfer Using Handshaking

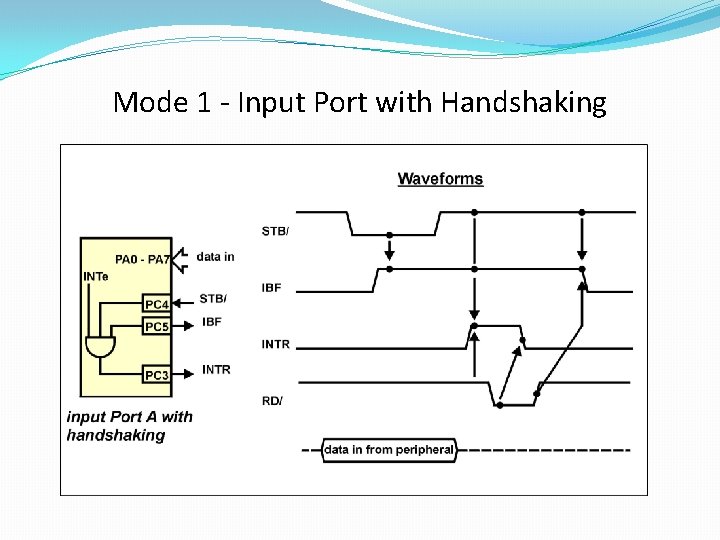

Mode 1 - Input Port with Handshaking

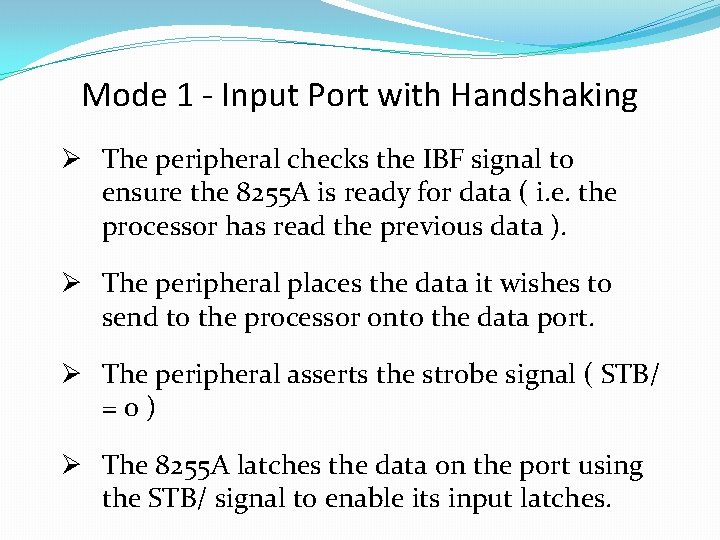

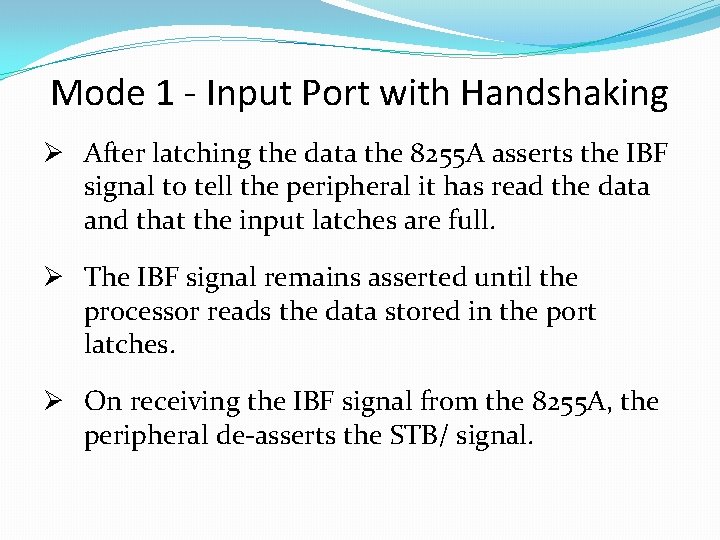

Mode 1 - Input Port with Handshaking Ø The peripheral checks the IBF signal to ensure the 8255 A is ready for data ( i. e. the processor has read the previous data ). Ø The peripheral places the data it wishes to send to the processor onto the data port. Ø The peripheral asserts the strobe signal ( STB/ =0) Ø The 8255 A latches the data on the port using the STB/ signal to enable its input latches.

Mode 1 - Input Port with Handshaking Ø After latching the data the 8255 A asserts the IBF signal to tell the peripheral it has read the data and that the input latches are full. Ø The IBF signal remains asserted until the processor reads the data stored in the port latches. Ø On receiving the IBF signal from the 8255 A, the peripheral de-asserts the STB/ signal.

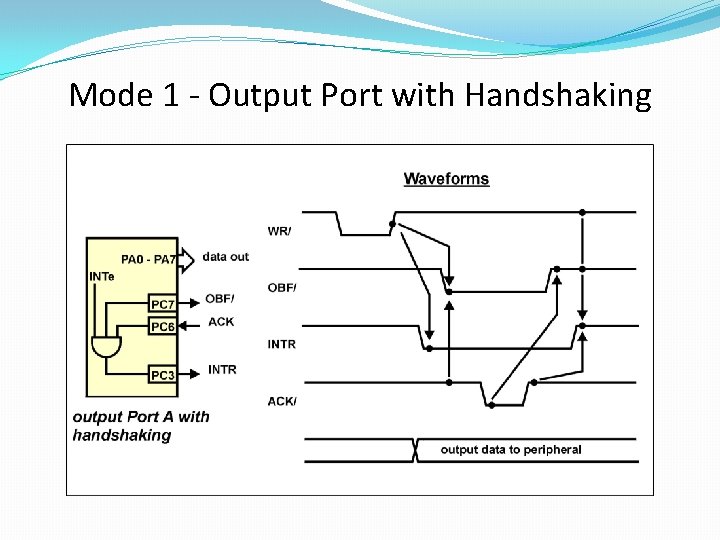

Mode 1 - Output Port with Handshaking

Mode 1 - Output Port with Handshaking Ø An initial state is assumed with the output data latches of the 8255 A empty and the peripheral device is ready to accept data. Ø The processor writes data, destined for the peripheral, to the 8255 A’s data latches. The data is latched into the 8255 A on the rising edge of the WR/ control signal. Ø Loading data into the data latches of the 8255 A clears the interrupt request output of the 8255 A (INTR = 0) and asserts the output buffer full flag (OBF/ = 0). Ø The peripheral device reads the output data of the 8255 A when it sees OBF/ asserted.

Mode 1 - Output Port with Handshaking Ø Once the peripheral has read the data, it generates an ACK/ = 0 pulse to tell the 8255 A that its output data has been read. Ø On the negative edge of the ACK/ signal, the 8255 A clears its OBF/ signal which tells the peripheral device there is no data for it to read. Ø On the rising edge of the ACK/ signal and provided that both WR/ and OBF/ are in the de-asserted state, the 8255 A generates an interrupt to the processor (assuming interrupt mode is being used).

Mode 1 - Output Port with Handshaking Ø This interrupt effectively tells the processor that the peripheral device has read the previous data sample and is ready to receive new data if the processor has data for it. Ø If interrupts are not chosen as the operating mechanism, the status register of the 8255 A can be polled to determine when the peripheral has read the previous data sample.

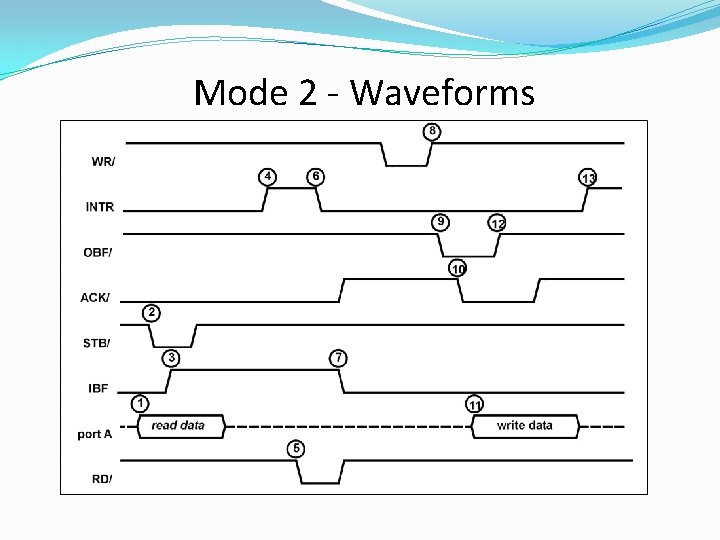

Mode 2: Strobed Bidirectional I/O (D 6, D 5 / D 2)

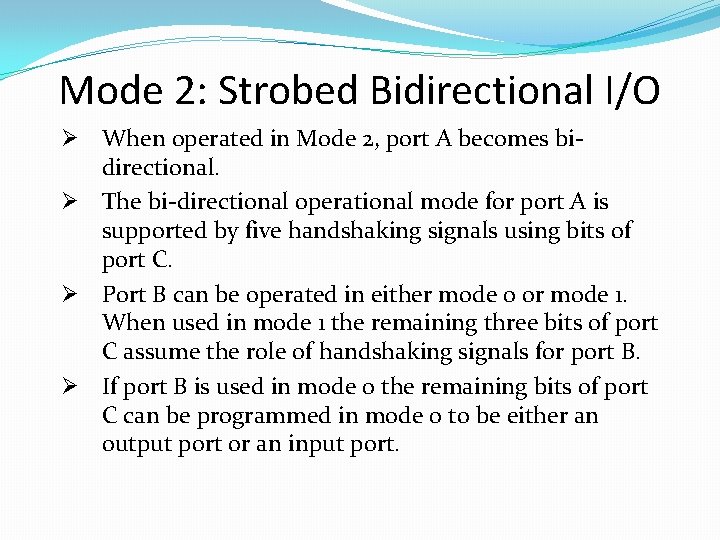

Mode 2: Strobed Bidirectional I/O Ø When operated in Mode 2, port A becomes bidirectional. Ø The bi-directional operational mode for port A is supported by five handshaking signals using bits of port C. Ø Port B can be operated in either mode 0 or mode 1. When used in mode 1 the remaining three bits of port C assume the role of handshaking signals for port B. Ø If port B is used in mode 0 the remaining bits of port C can be programmed in mode 0 to be either an output port or an input port.

Mode 2 – Logic Diagram

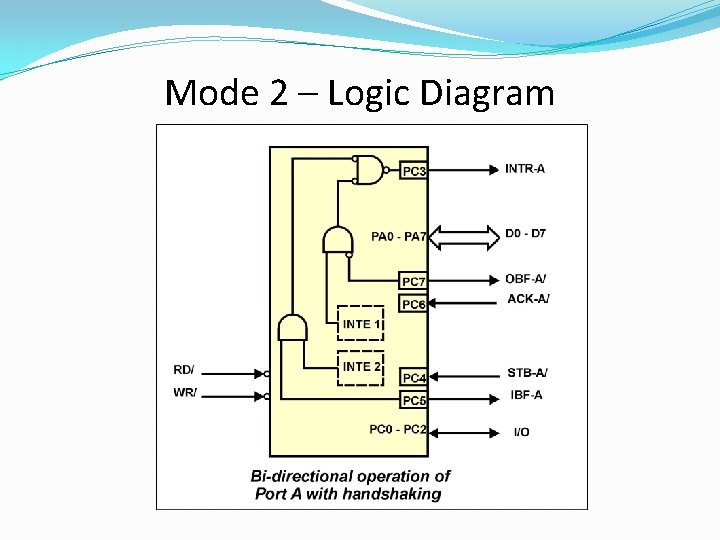

Mode 2 - Waveforms

Mode 2: Strobed Bidirectional I/O Ø Read data from peripheral followed by writing data to peripheral 1. Data is placed on PA 0 - PA 7 by the peripheral 2. Peripheral asserts its STB/ output telling 8255 data to be read. The 8255 A latches the data in its input buffers. 3. The 8255 asserts its IBF output to tell the peripheral the data has been latched but not read by the processor.

Mode 2: Strobed Bidirectional I/O 4. The peripheral de-asserts its STB/ output with IBF still set. The 8255 A requests an interrupt ( assuming interrupts are used) 5. Polling or interrupts are now used to service the 8255 A. The 8255 A input buffers are read by the processor when RD/ goes low. 6. The falling edge of RD/ resets INTR. 7 The rising edge of RD/ resets the IBF flag to tell the peripheral the data has been read by the processor and that it can send the next data sample.

Mode 2: Strobed Bidirectional I/O Ø Processor write sequencing 8. Data is output from the processor and latched by the 8255 A using the WR/ processor signal. 9. The rising edge of WR/ causes the OBF/ to be asserted, telling the peripheral device there is data for it to read. 10. The peripheral enables its input buffers and tells the 8255 A it is ready to receive data by asserting the ACK/ flag.

Mode 2: Strobed Bidirectional I/O 11. On the falling edge of ACK/, the 8255 A releases its latched data onto the lines PA 0 PA 7. The data is read by the peripheral device. 12. The 8255 A de-asserts its OBF/ flag telling the peripheral there is no further data to read. 13. The rising edge of ACK/ causes the 8255 A to generate an interrupt request. ( if this feature is used ). The interrupt tells the processor that the peripheral has read the data and that further data can be written to the 8255 A.

Mode 0: BSR Mode (D 6, D 5 / D 2)

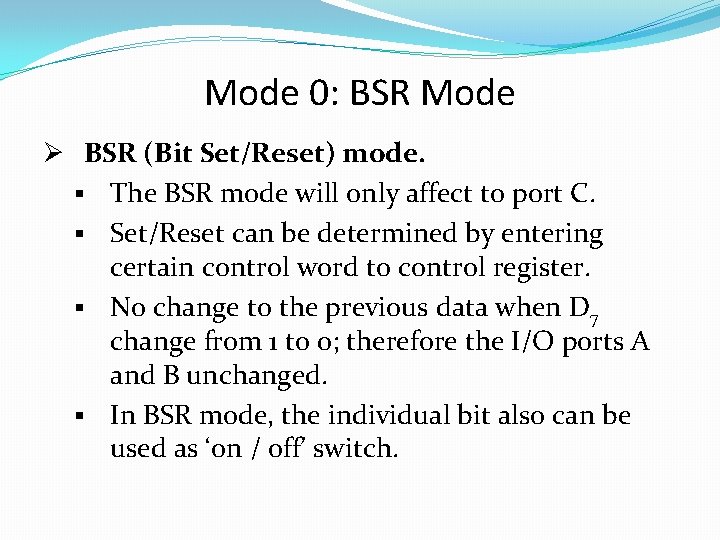

Mode 0: BSR Mode Ø BSR (Bit Set/Reset) mode. § The BSR mode will only affect to port C. § Set/Reset can be determined by entering certain control word to control register. § No change to the previous data when D 7 change from 1 to 0; therefore the I/O ports A and B unchanged. § In BSR mode, the individual bit also can be used as ‘on / off’ switch.

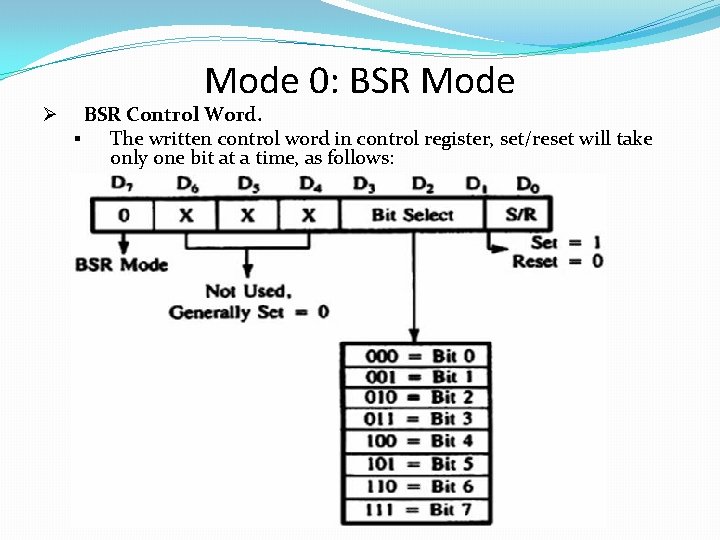

Ø Mode 0: BSR Mode BSR Control Word. § The written control word in control register, set/reset will take only one bit at a time, as follows:

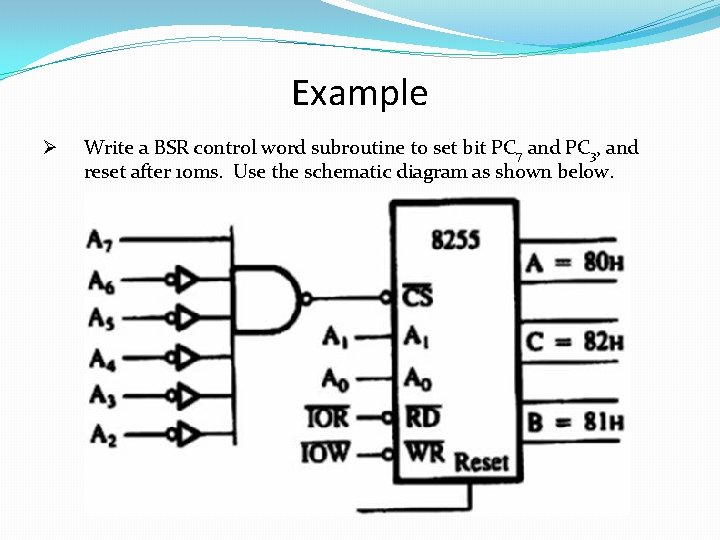

Example Ø Write a BSR control word subroutine to set bit PC 7 and PC 3, and reset after 10 ms. Use the schematic diagram as shown below.

� Solution: � BSR Control Word:

� Solution: � Subroutine: Assuming that the delay subroutine has been determined earlier. 62

Thank you Q&A

- Slides: 63