EMT 245 LECTURE 4 ASSEMBLY LANGUAGE Razaidi Hussin

EMT 245: LECTURE 4: ASSEMBLY LANGUAGE Razaidi Hussin **Notes taken from WAN MOKHDZANI BIN WAN NOR HAIMI and Mr. Ahmad Husni

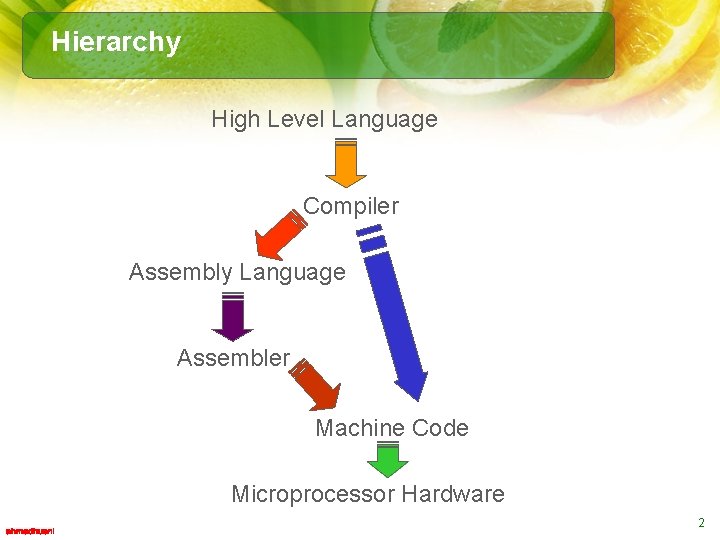

Hierarchy High Level Language Compiler Assembly Language Assembler Machine Code Microprocessor Hardware 2

8085 A Instruction Set • Can be classified into the following five functional categories: – Data transfer (copy) Instruction, – Arithmetic Instruction (add, subtract), – Logical Instruction (and, or), – Branching Instruction (jump, delay), and – Machine-control Instruction (input, output port). 3

8085 A Instruction Set Data Transfer Instruction • Move data between registers or between memory locations and registers. Includes moves, loads, stores and exchanges. v Copies data from a location called a source to another location, called a destination, without modifying the contents of the source. v In technical manuals, the term data transfer is used for this copying function. v The term transfer is misleading; it creates the impression that the contents of a source are destroyed when, in fact, the contents are retained without any modification. 4

8085 A Instruction Set Arithmetic Instruction • Adds, Subtracts, Increments, Decrements data in registers or memory. Logic Instruction • ANDs, ORs, XORs, compares, rotates or complements data in registers or between memory and registers. • These instructions perform various logical operations with the contents of the accumulator. 5

8085 A Instruction Set Branch/Jump Instruction • Initiates conditional or unconditional jumps, calls, returns and restart. • This group of instructions alters the sequence of program execution either conditionally or unconditionally: – Jump - Conditional jumps are an important aspect of the decision-making process in programming. These instructions test for a certain condition (e. g. , Zero or Carry flag) and alter the program sequence when the condition is met. • This set includes an instruction called unconditional jump. • Call, Return, and Restart -These instructions change the sequence of a program either by calling a subroutine or returning from a subroutine. – The conditional Call and Return instructions also can test condition flags. 6

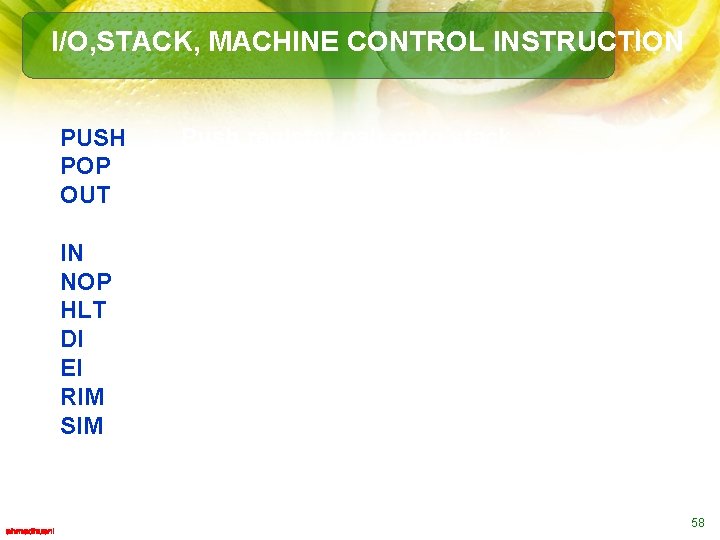

8085 A Instruction Set Stack, I/O and Machine Control Instruction • Includes instructions for maintaining stack, reading from input port, writing to output port, setting and reading interrupt mask and clearing flags. • These instructions control machine functions such as Halt, Interrupt, or do nothing. 7

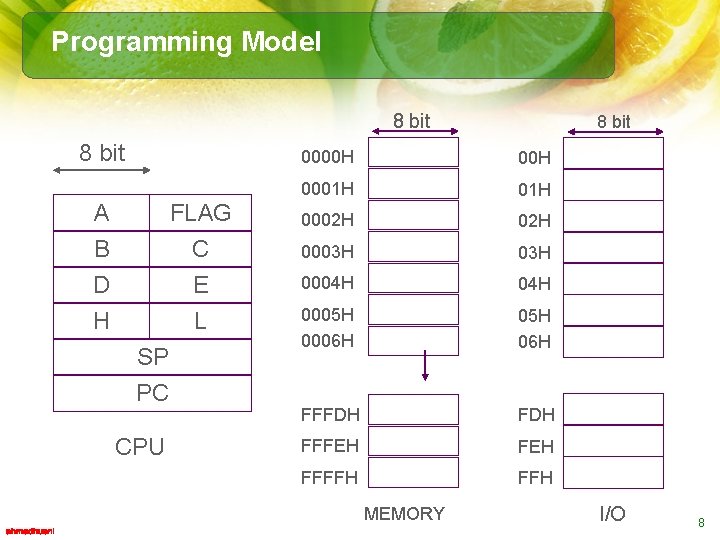

Programming Model 8 bit A B D H FLAG C E L SP PC CPU 8 bit 0000 H 0001 H 0002 H 0003 H 0004 H 0005 H 0006 H 05 H 06 H FFFDH FFFEH FFFFH MEMORY I/O 8

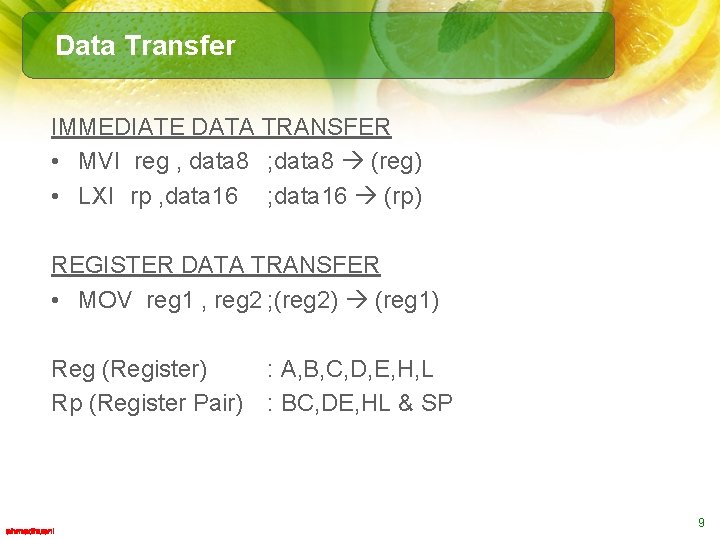

Data Transfer IMMEDIATE DATA TRANSFER • MVI reg , data 8 ; data 8 (reg) • LXI rp , data 16 ; data 16 (rp) REGISTER DATA TRANSFER • MOV reg 1 , reg 2 ; (reg 2) (reg 1) Reg (Register) Rp (Register Pair) : A, B, C, D, E, H, L : BC, DE, HL & SP 9

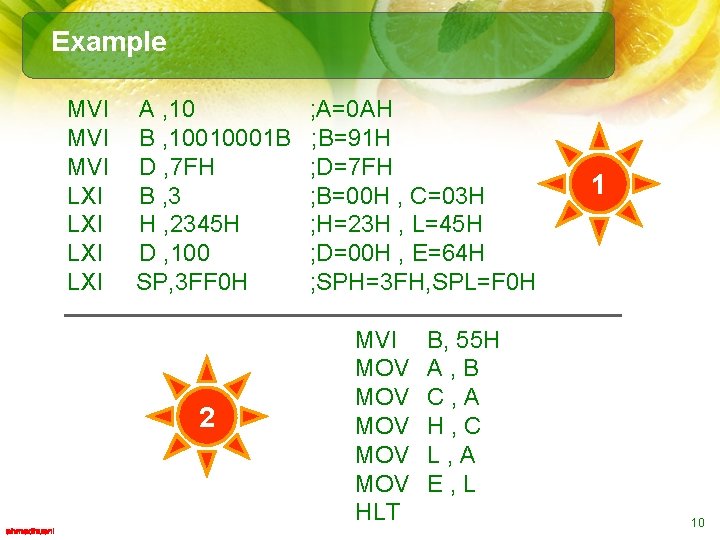

Example MVI MVI LXI LXI A , 10 B , 10010001 B D , 7 FH B , 3 H , 2345 H D , 100 SP, 3 FF 0 H 2 ; A=0 AH ; B=91 H ; D=7 FH ; B=00 H , C=03 H ; H=23 H , L=45 H ; D=00 H , E=64 H ; SPH=3 FH, SPL=F 0 H MVI MOV MOV MOV HLT 1 B, 55 H A, B C, A H, C L, A E, L 10

Direct data transfer • • LDA STA LHLD SHLD address 16 11

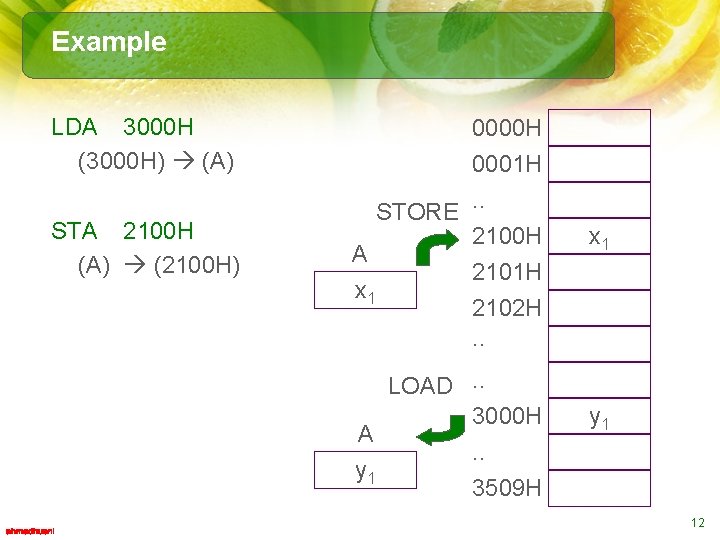

Example LDA 3000 H (3000 H) (A) STA 2100 H (A) (2100 H) 0000 H 0001 H STORE. . 2100 H A 2101 H x 1 2102 H. . LOAD. . 3000 H A. . y 1 3509 H x 1 y 1 12

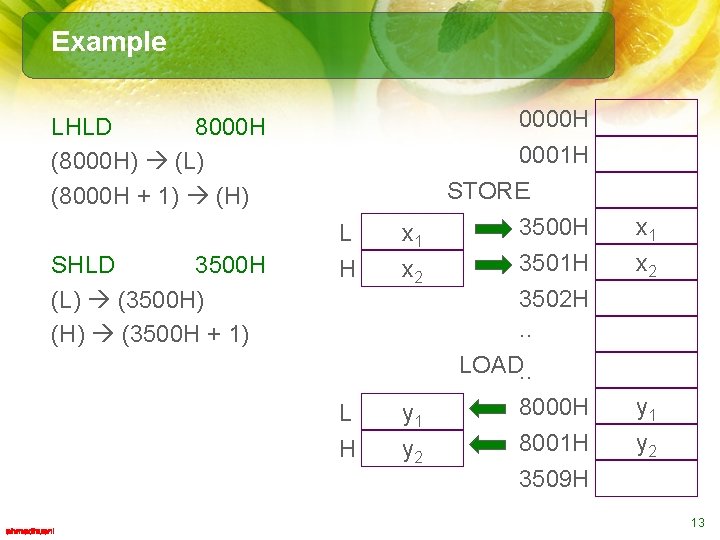

Example 0000 H LHLD 8000 H (8000 H) (L) (8000 H + 1) (H) SHLD 3500 H (L) (3500 H) (H) (3500 H + 1) L H x 1 x 2 0001 H STORE. . 3500 H 3501 H 3502 H. . LOAD. . L H y 1 y 2 8000 H 8001 H 3509 H x 1 x 2 y 1 y 2 13

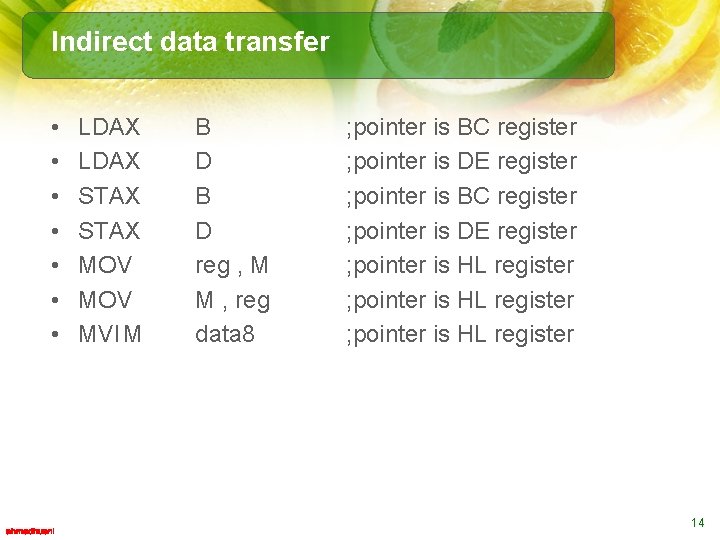

Indirect data transfer • • LDAX STAX MOV MVIM B D reg , M M , reg data 8 ; pointer is BC register ; pointer is DE register ; pointer is HL register 14

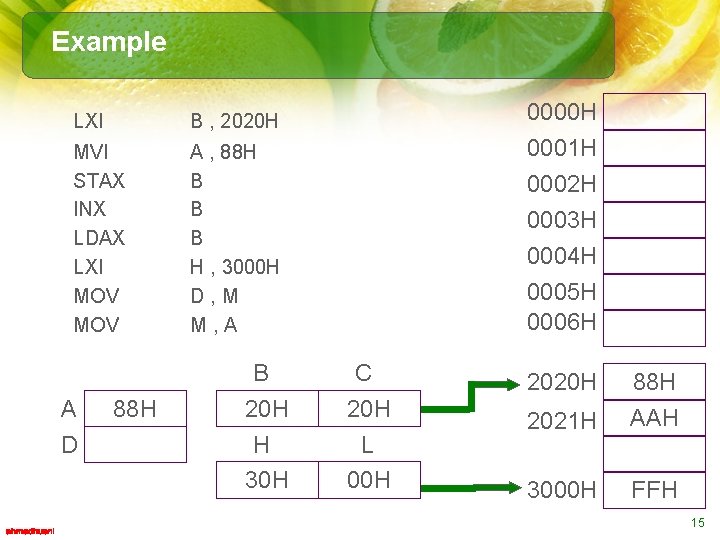

Example LXI B , 2020 H 0000 H MVI STAX INX LDAX LXI MOV A , 88 H B B B H , 3000 H D, M M, A 0001 H 0002 H 0003 H 0004 H 0005 H 0006 H A D 88 H B 20 H H 30 H C 20 H L 00 H 2021 H 88 H AAH 3000 H FFH 15

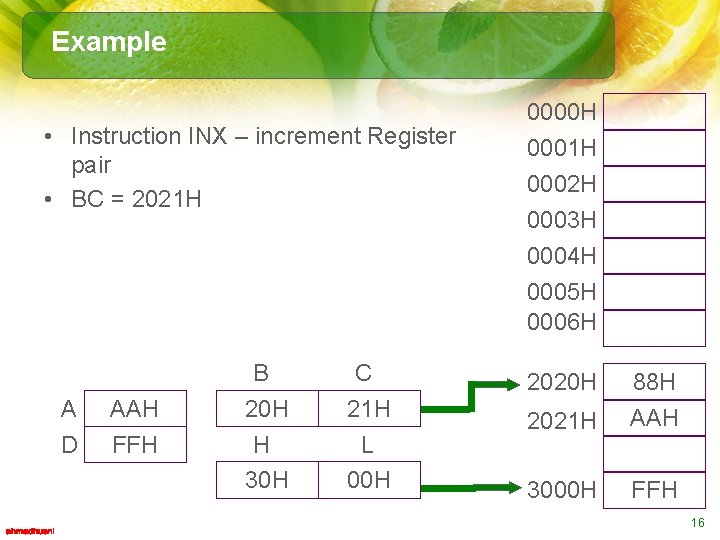

Example • Instruction INX – increment Register pair • BC = 2021 H A D AAH FFH B 20 H H 30 H C 21 H L 00 H 0001 H 0002 H 0003 H 0004 H 0005 H 0006 H 2020 H 2021 H 88 H AAH 3000 H FFH 16

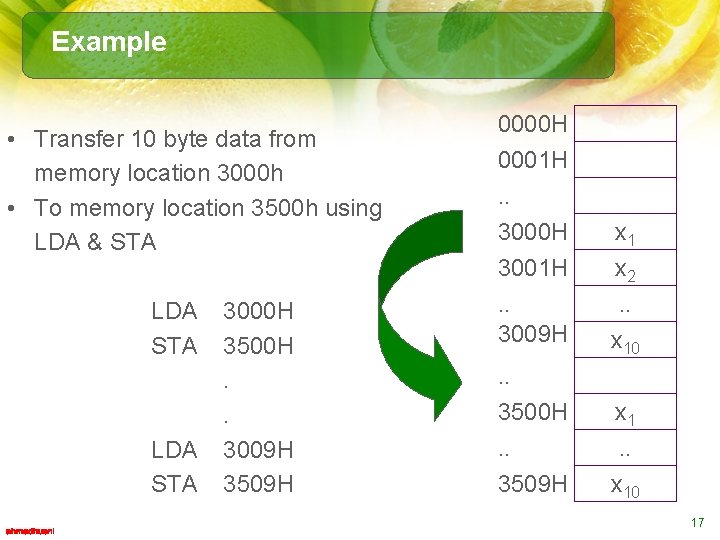

Example • Transfer 10 byte data from memory location 3000 h • To memory location 3500 h using LDA & STA LDA STA 3000 H 3500 H. . 3009 H 3509 H 0000 H 0001 H. . 3000 H 3001 H. . 3009 H x 1 x 2. . x 10 . . 3500 H. . 3509 H x 1. . x 10 17

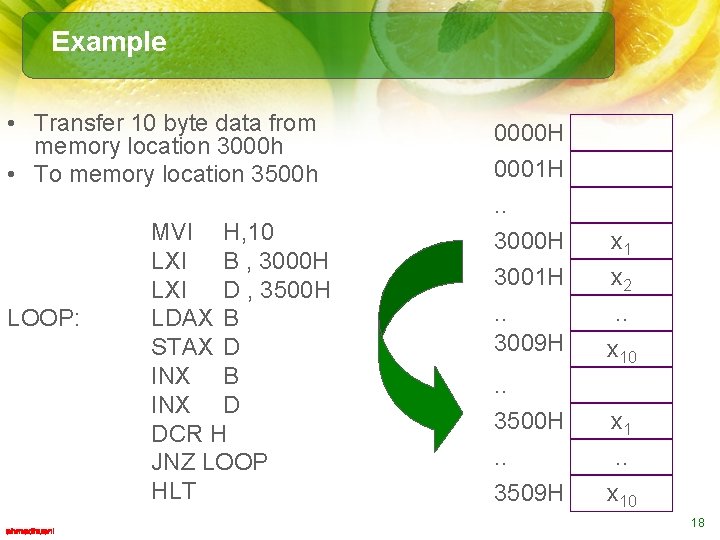

Example • Transfer 10 byte data from memory location 3000 h • To memory location 3500 h LOOP: MVI H, 10 LXI B , 3000 H LXI D , 3500 H LDAX B STAX D INX B INX D DCR H JNZ LOOP HLT 0000 H 0001 H. . 3000 H 3001 H. . 3009 H x 1 x 2. . x 10 . . 3500 H. . 3509 H x 1. . x 10 18

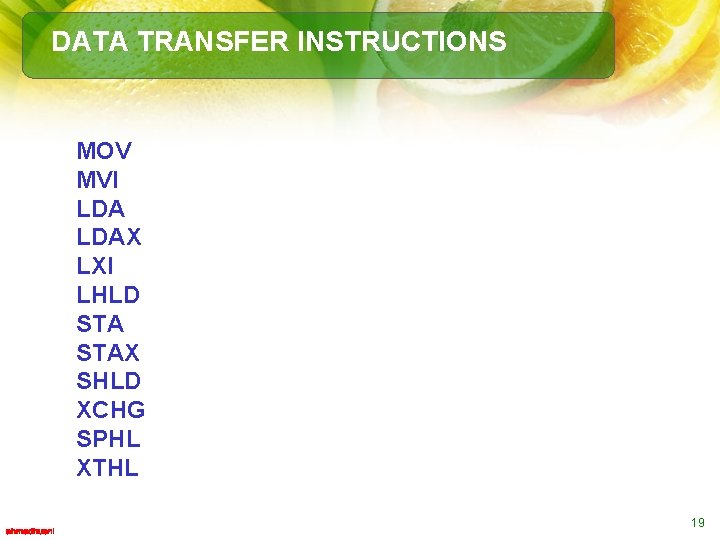

DATA TRANSFER INSTRUCTIONS MOV MVI LDAX LXI LHLD STAX SHLD XCHG SPHL XTHL Copy from source to destination Move immediate 8 -bit Load accumulator indirect Load register pair immediate Load H and L registers direct Store accumulator indirect Store H and L registers direct Exchange H and L with D and E Copy H and L registers to the stack pointer Exchange H and L with top of stack 19

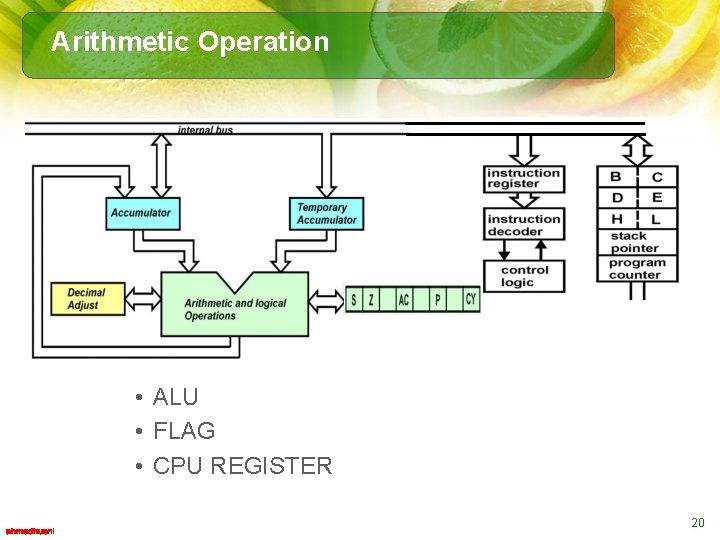

Arithmetic Operation • ALU • FLAG • CPU REGISTER 20

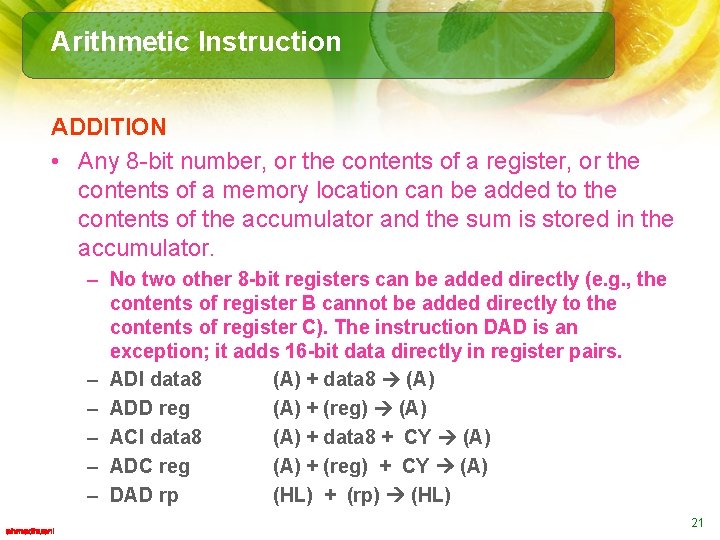

Arithmetic Instruction ADDITION • Any 8 -bit number, or the contents of a register, or the contents of a memory location can be added to the contents of the accumulator and the sum is stored in the accumulator. – No two other 8 -bit registers can be added directly (e. g. , the contents of register B cannot be added directly to the contents of register C). The instruction DAD is an exception; it adds 16 -bit data directly in register pairs. – ADI data 8 (A) + data 8 (A) – ADD reg (A) + (reg) (A) – ACI data 8 (A) + data 8 + CY (A) – ADC reg (A) + (reg) + CY (A) – DAD rp (HL) + (rp) (HL) 21

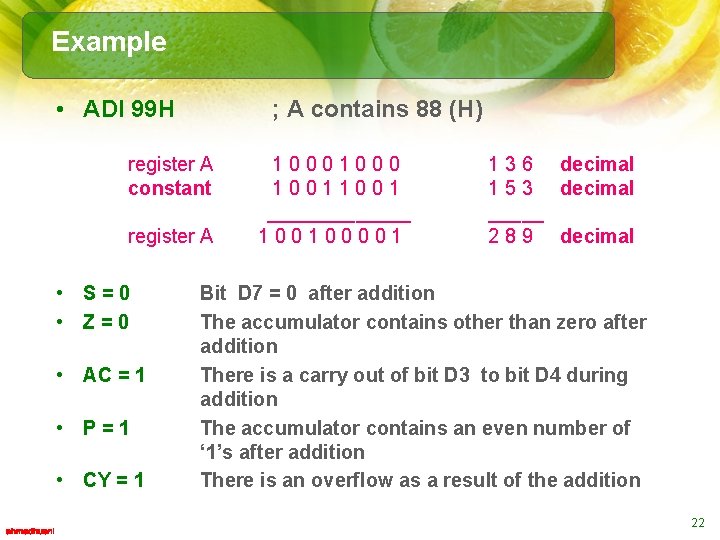

Example • ADI 99 H ; A contains 88 (H) register A constant register A • S=0 • Z=0 • AC = 1 • P=1 • CY = 1 1000 1001 _______ 100100001 1 3 6 decimal 1 5 3 decimal _____ 2 8 9 decimal Bit D 7 = 0 after addition The accumulator contains other than zero after addition There is a carry out of bit D 3 to bit D 4 during addition The accumulator contains an even number of ‘ 1’s after addition There is an overflow as a result of the addition 22

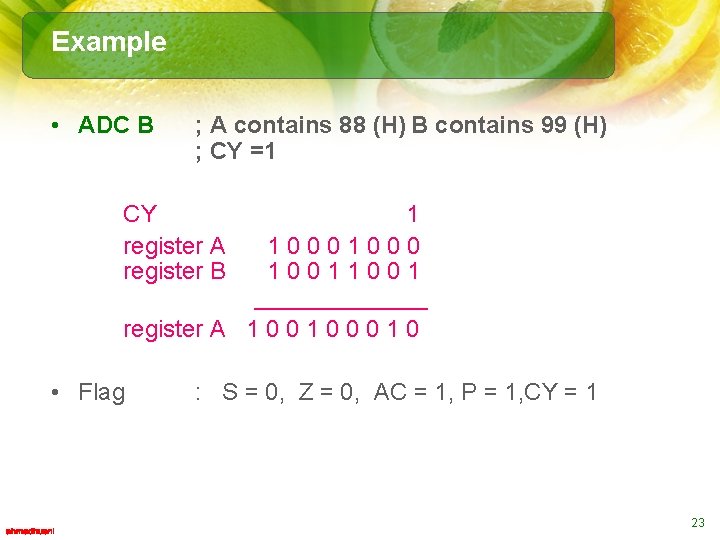

Example • ADC B ; A contains 88 (H) B contains 99 (H) ; CY =1 CY register A register B 1 1000 1001 _______ register A 1 0 0 0 1 0 • Flag : S = 0, Z = 0, AC = 1, P = 1, CY = 1 23

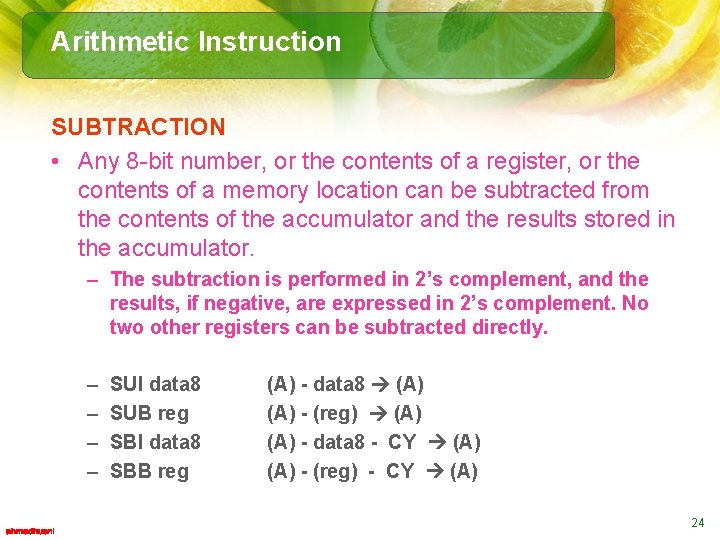

Arithmetic Instruction SUBTRACTION • Any 8 -bit number, or the contents of a register, or the contents of a memory location can be subtracted from the contents of the accumulator and the results stored in the accumulator. – The subtraction is performed in 2’s complement, and the results, if negative, are expressed in 2’s complement. No two other registers can be subtracted directly. – – SUI data 8 SUB reg SBI data 8 SBB reg (A) - data 8 (A) - (reg) (A) - data 8 - CY (A) - (reg) - CY (A) 24

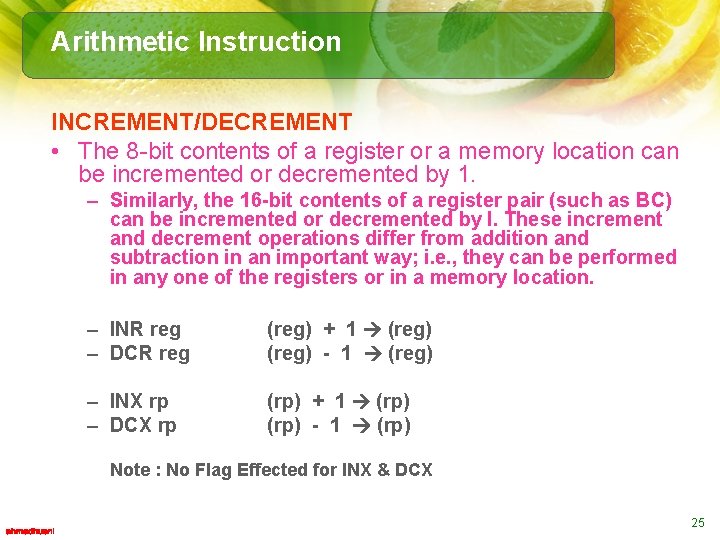

Arithmetic Instruction INCREMENT/DECREMENT • The 8 -bit contents of a register or a memory location can be incremented or decremented by 1. – Similarly, the 16 -bit contents of a register pair (such as BC) can be incremented or decremented by I. These increment and decrement operations differ from addition and subtraction in an important way; i. e. , they can be performed in any one of the registers or in a memory location. – INR reg – DCR reg (reg) + 1 (reg) - 1 (reg) – INX rp – DCX rp (rp) + 1 (rp) - 1 (rp) Note : No Flag Effected for INX & DCX 25

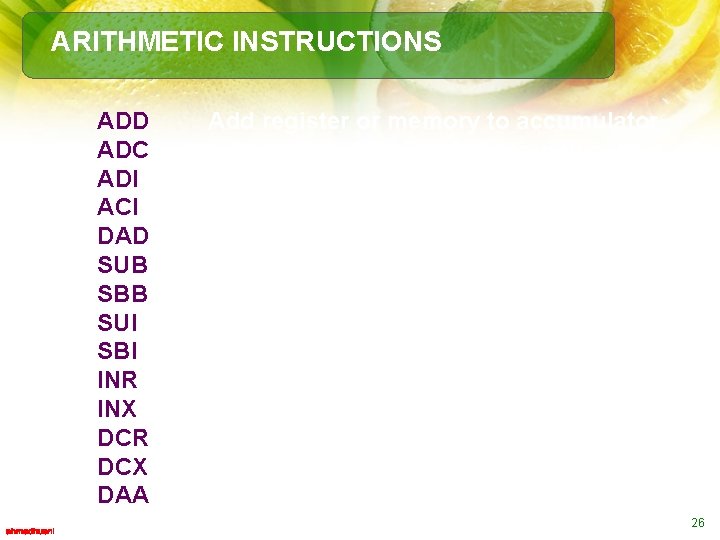

ARITHMETIC INSTRUCTIONS ADD ADC ADI ACI DAD SUB SBB SUI SBI INR INX DCR DCX DAA Add register or memory to accumulator Add register to accumulator with carry Add immediate to accumulator with carry Add register pair to H and L registers Subtract register or memory from A Subtract source and borrow from A Subtract immediate from A with borrow Increment register or memory by 1 Increment register pair by 1 Decrement register or memory by 1 Decrement register pair by 1 Decimal adjust accumulator 26

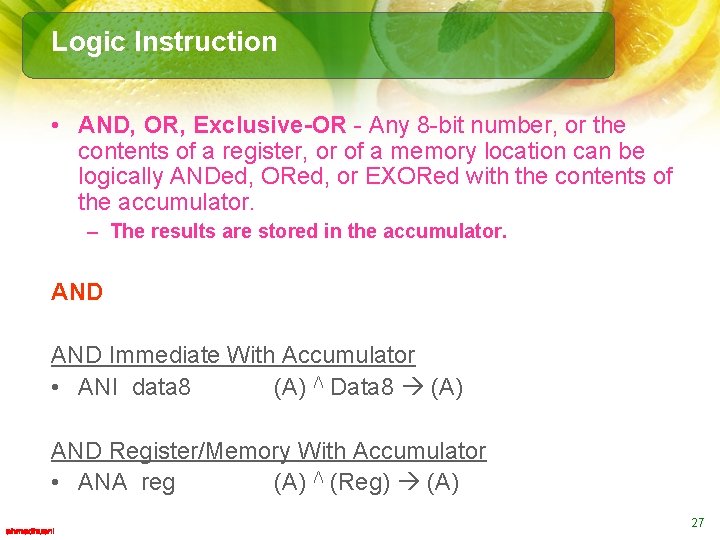

Logic Instruction • AND, OR, Exclusive-OR - Any 8 -bit number, or the contents of a register, or of a memory location can be logically ANDed, ORed, or EXORed with the contents of the accumulator. – The results are stored in the accumulator. AND Immediate With Accumulator • ANI data 8 (A) Λ Data 8 (A) AND Register/Memory With Accumulator • ANA reg (A) Λ (Reg) (A) 27

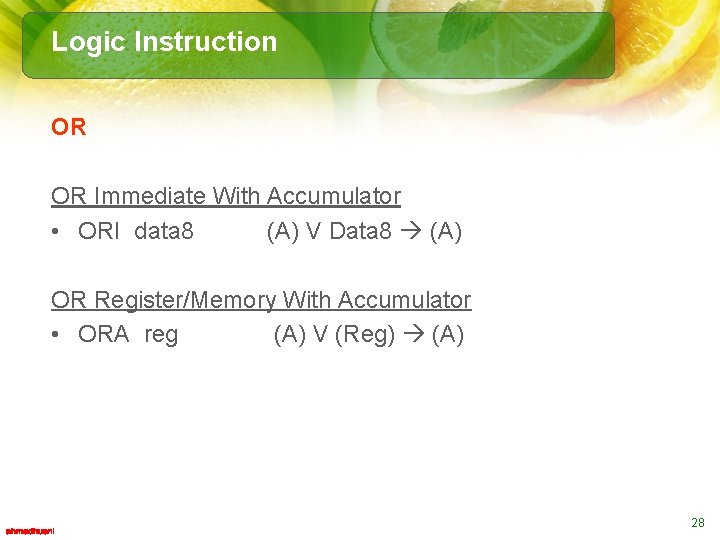

Logic Instruction OR OR Immediate With Accumulator • ORI data 8 (A) V Data 8 (A) OR Register/Memory With Accumulator • ORA reg (A) V (Reg) (A) 28

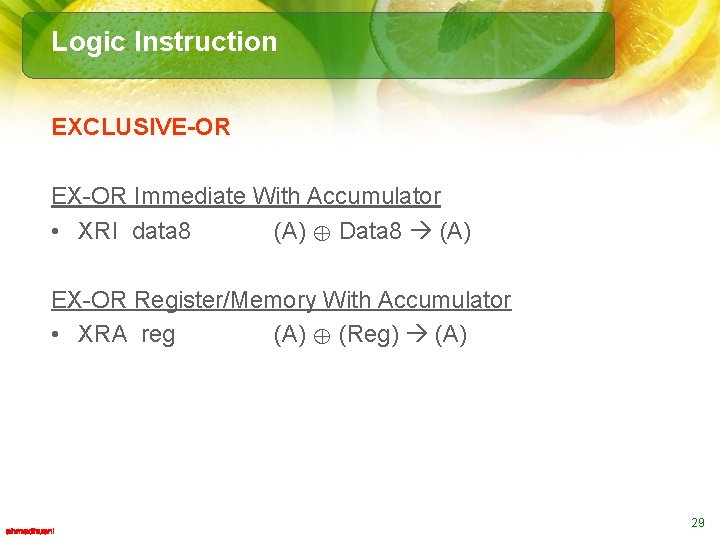

Logic Instruction EXCLUSIVE-OR EX-OR Immediate With Accumulator • XRI data 8 (A) ⊕ Data 8 (A) EX-OR Register/Memory With Accumulator • XRA reg (A) ⊕ (Reg) (A) 29

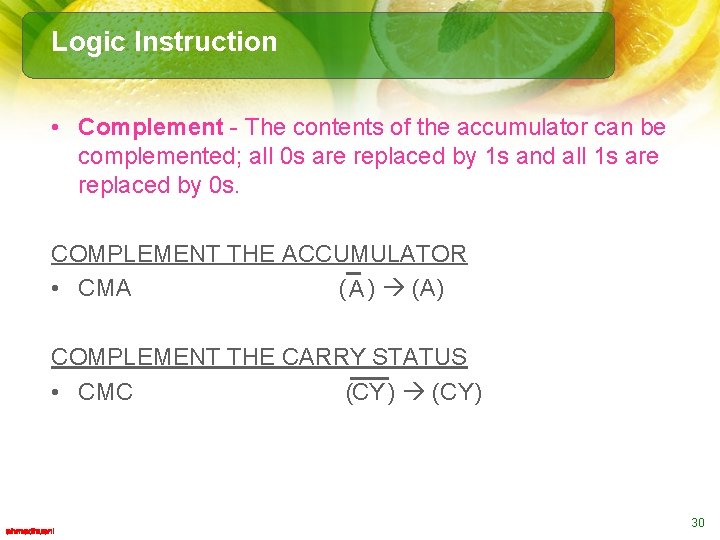

Logic Instruction • Complement - The contents of the accumulator can be complemented; all 0 s are replaced by 1 s and all 1 s are replaced by 0 s. COMPLEMENT THE ACCUMULATOR • CMA ( A ) (A) COMPLEMENT THE CARRY STATUS • CMC (CY ) (CY) 30

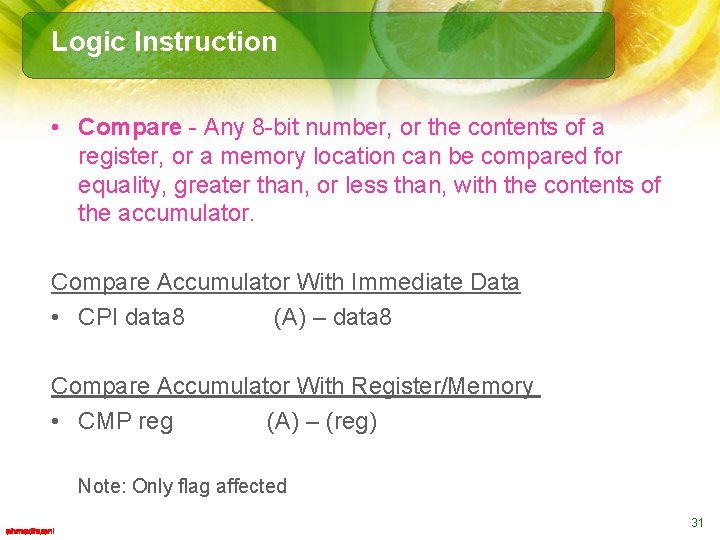

Logic Instruction • Compare - Any 8 -bit number, or the contents of a register, or a memory location can be compared for equality, greater than, or less than, with the contents of the accumulator. Compare Accumulator With Immediate Data • CPI data 8 (A) – data 8 Compare Accumulator With Register/Memory • CMP reg (A) – (reg) Note: Only flag affected 31

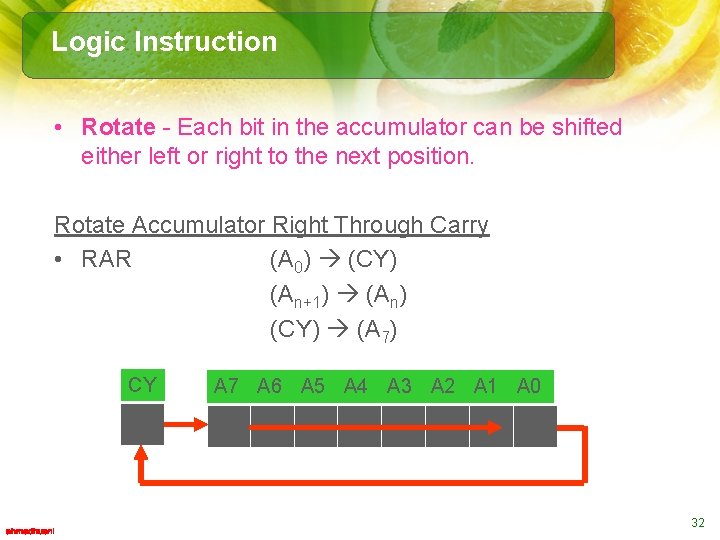

Logic Instruction • Rotate - Each bit in the accumulator can be shifted either left or right to the next position. Rotate Accumulator Right Through Carry • RAR (A 0) (CY) (An+1) (An) (CY) (A 7) CY A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 32

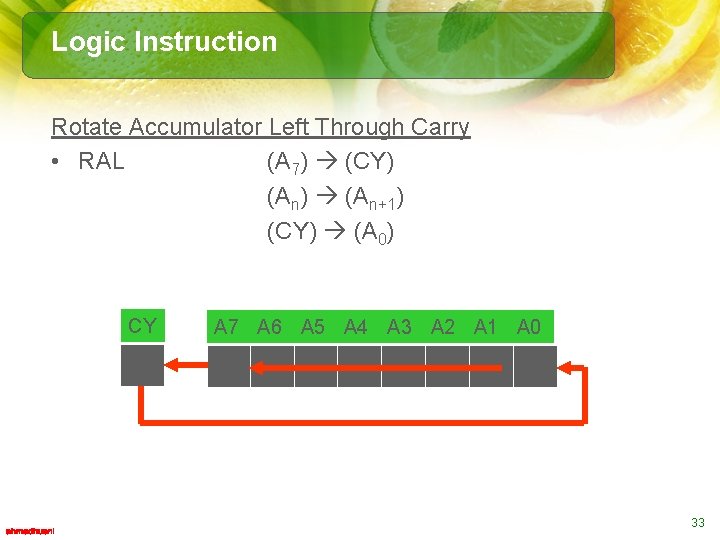

Logic Instruction Rotate Accumulator Left Through Carry • RAL (A 7) (CY) (An) (An+1) (CY) (A 0) CY A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 33

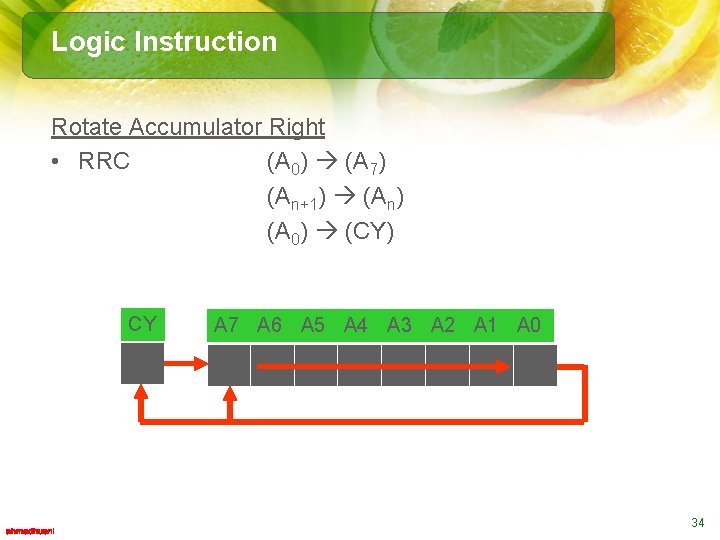

Logic Instruction Rotate Accumulator Right • RRC (A 0) (A 7) (An+1) (An) (A 0) (CY) CY A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 34

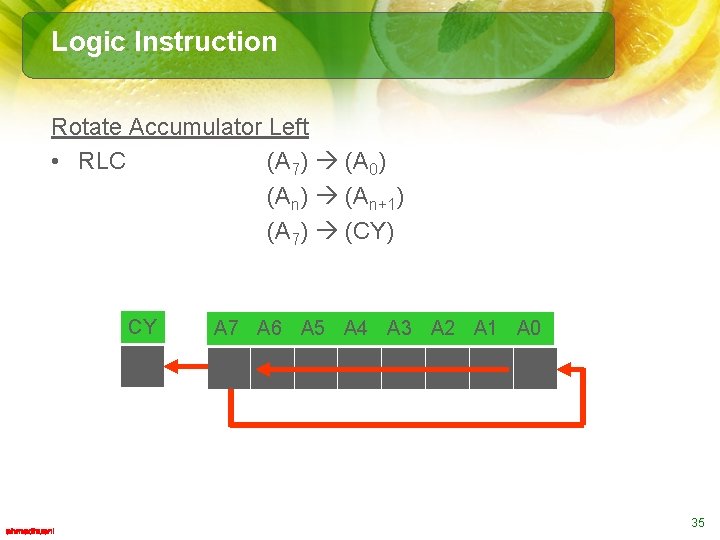

Logic Instruction Rotate Accumulator Left • RLC (A 7) (A 0) (An) (An+1) (A 7) (CY) CY A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 35

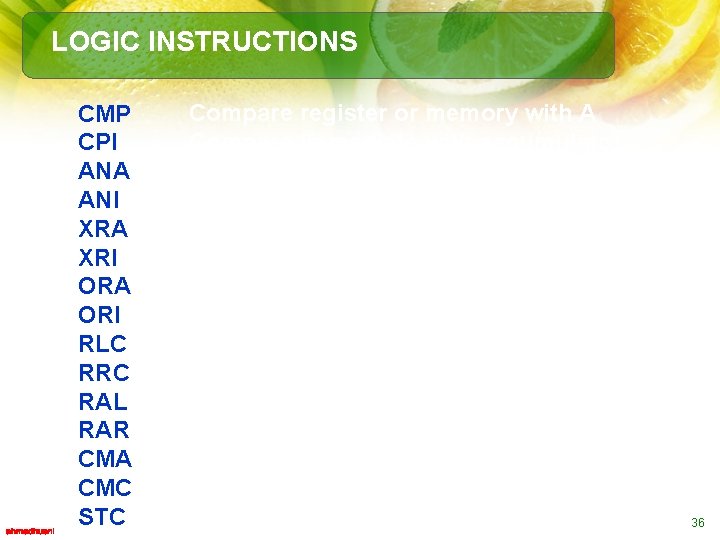

LOGIC INSTRUCTIONS CMP CPI ANA ANI XRA XRI ORA ORI RLC RRC RAL RAR CMA CMC STC Compare register or memory with A Compare immediate with accumulator Logical AND register or memory with A Logical AND immediate with accumulator Exclusive OR register or memory with A Exclusive OR immediate with accumulator Logical OR register or memory with A Logical OR immediate with accumulator Rotate accumulator left Rotate accumulator right Rotate accumulator left through carry Rotate accumulator right through carry Complement accumulator Complement carry Set carry 36

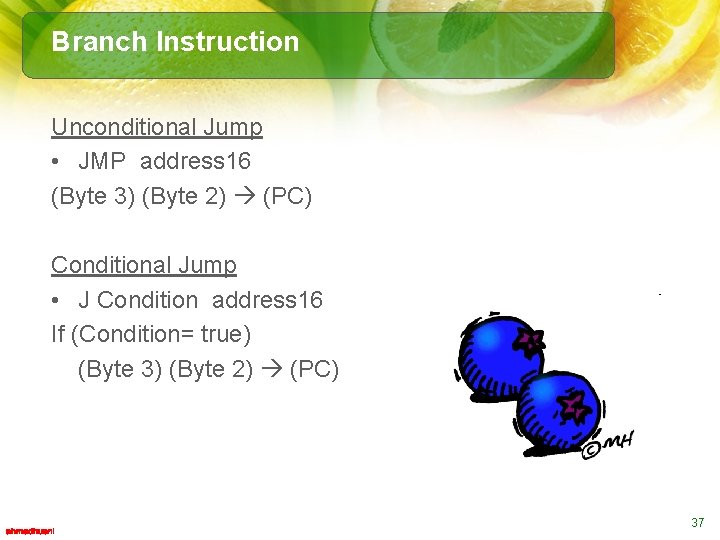

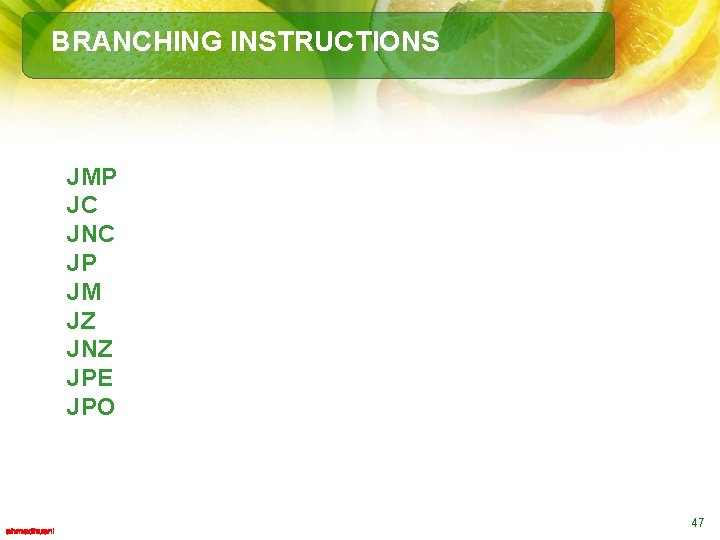

Branch Instruction Unconditional Jump • JMP address 16 (Byte 3) (Byte 2) (PC) Conditional Jump • J Condition address 16 If (Condition= true) (Byte 3) (Byte 2) (PC) 37

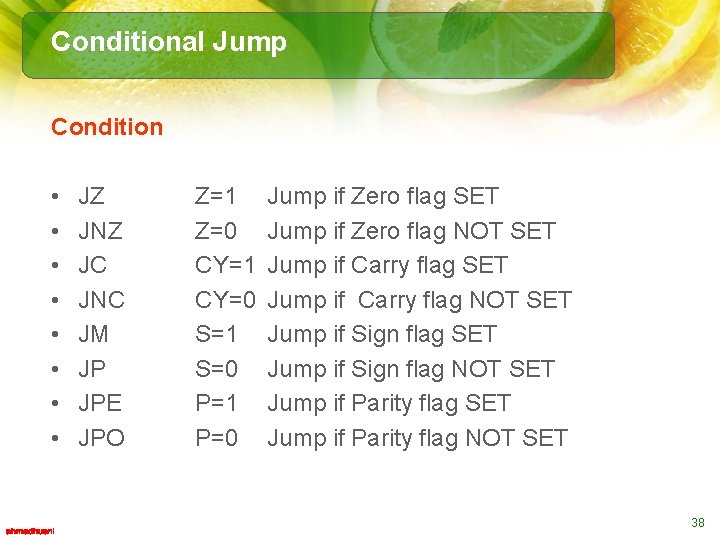

Conditional Jump Condition • • JZ JNZ JC JNC JM JP JPE JPO Z=1 Z=0 CY=1 CY=0 S=1 S=0 P=1 P=0 Jump if Zero flag SET Jump if Zero flag NOT SET Jump if Carry flag NOT SET Jump if Sign flag NOT SET Jump if Parity flag NOT SET 38

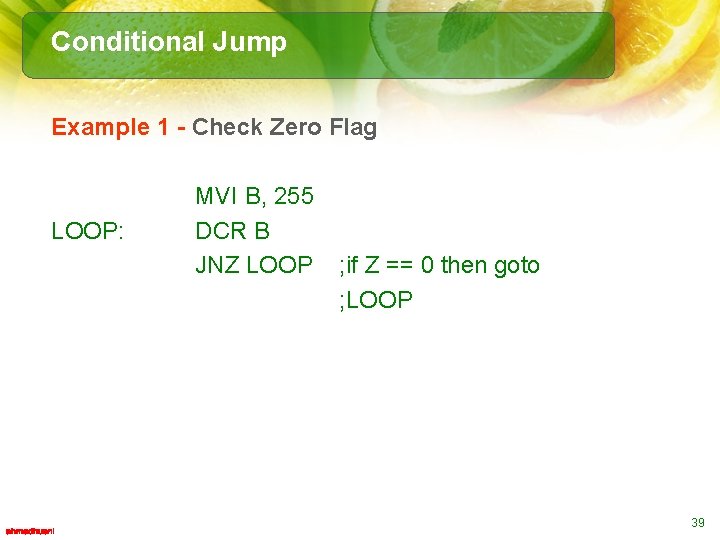

Conditional Jump Example 1 - Check Zero Flag LOOP: MVI B, 255 DCR B JNZ LOOP ; if Z == 0 then goto ; LOOP 39

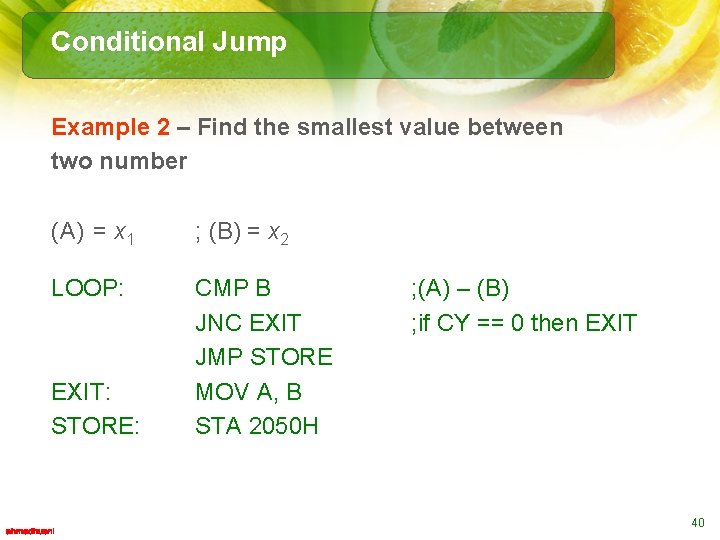

Conditional Jump Example 2 – Find the smallest value between two number (A) = x 1 ; (B) = x 2 LOOP: CMP B JNC EXIT JMP STORE MOV A, B STA 2050 H EXIT: STORE: ; (A) – (B) ; if CY == 0 then EXIT 40

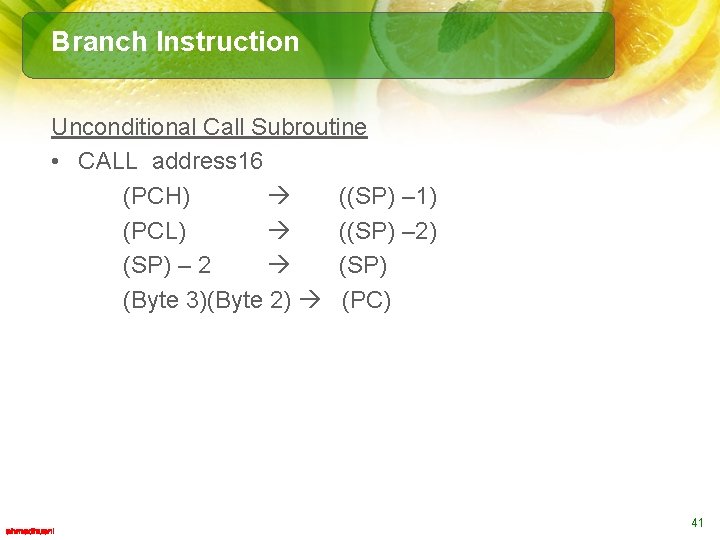

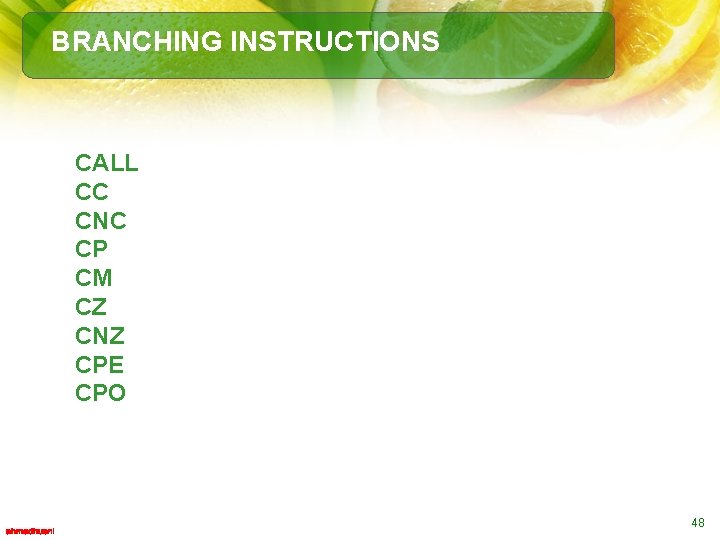

Branch Instruction Unconditional Call Subroutine • CALL address 16 (PCH) ((SP) – 1) (PCL) ((SP) – 2) (SP) – 2 (SP) (Byte 3)(Byte 2) (PC) 41

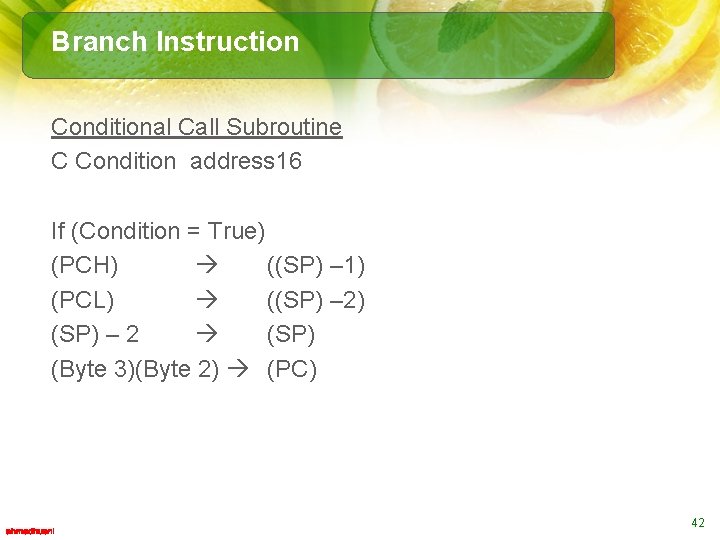

Branch Instruction Conditional Call Subroutine C Condition address 16 If (Condition = True) (PCH) ((SP) – 1) (PCL) ((SP) – 2) (SP) – 2 (SP) (Byte 3)(Byte 2) (PC) 42

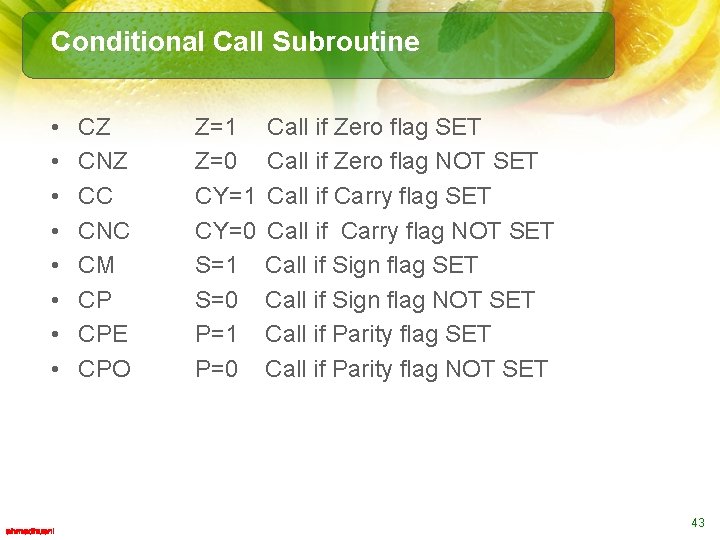

Conditional Call Subroutine • • CZ CNZ CC CNC CM CP CPE CPO Z=1 Z=0 CY=1 CY=0 S=1 S=0 P=1 P=0 Call if Zero flag SET Call if Zero flag NOT SET Call if Carry flag NOT SET Call if Sign flag NOT SET Call if Parity flag NOT SET 43

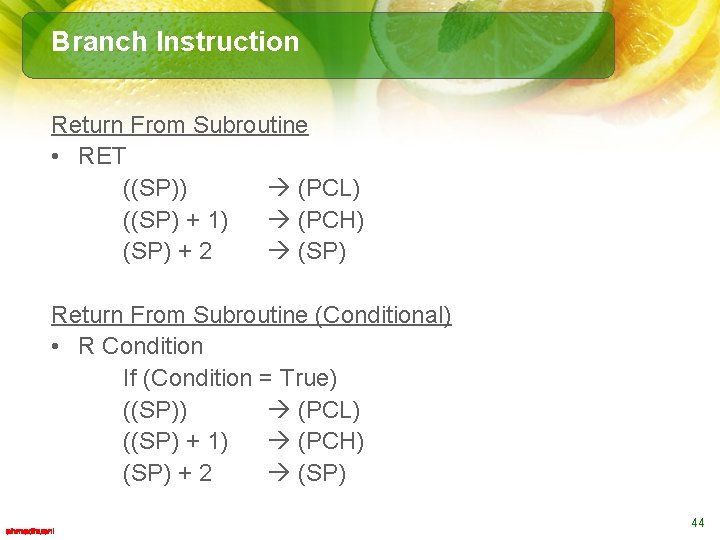

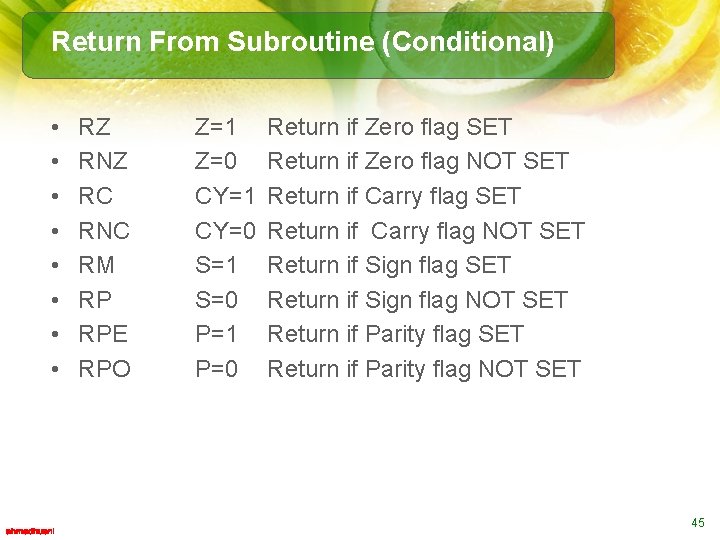

Branch Instruction Return From Subroutine • RET ((SP)) (PCL) ((SP) + 1) (PCH) (SP) + 2 (SP) Return From Subroutine (Conditional) • R Condition If (Condition = True) ((SP)) (PCL) ((SP) + 1) (PCH) (SP) + 2 (SP) 44

Return From Subroutine (Conditional) • • RZ RNZ RC RNC RM RP RPE RPO Z=1 Z=0 CY=1 CY=0 S=1 S=0 P=1 P=0 Return if Zero flag SET Return if Zero flag NOT SET Return if Carry flag NOT SET Return if Sign flag NOT SET Return if Parity flag NOT SET 45

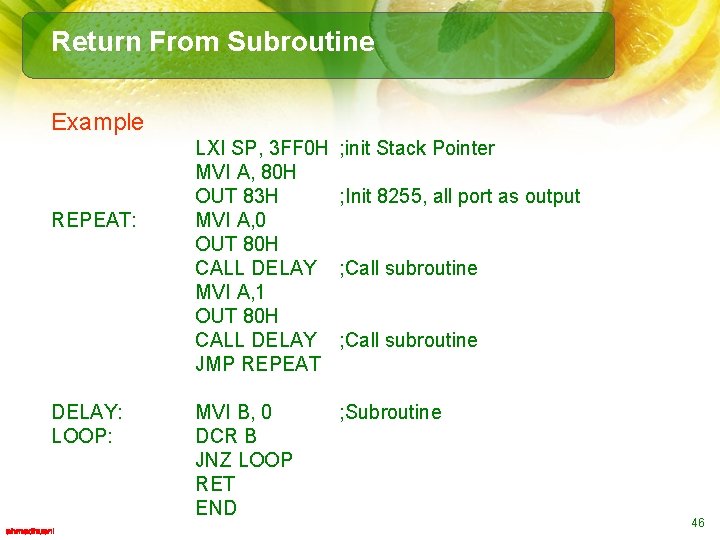

Return From Subroutine Example REPEAT: DELAY: LOOP: LXI SP, 3 FF 0 H MVI A, 80 H OUT 83 H MVI A, 0 OUT 80 H CALL DELAY MVI A, 1 OUT 80 H CALL DELAY JMP REPEAT ; init Stack Pointer MVI B, 0 DCR B JNZ LOOP RET END ; Subroutine ; Init 8255, all port as output ; Call subroutine 46

BRANCHING INSTRUCTIONS JMP JC JNC JP JM JZ JNZ JPE JPO Jump unconditionally Jump on carry Jump on no carry Jump on positive Jump on minus Jump on zero Jump on no zero Jump on parity even Jump on parity odd 47

BRANCHING INSTRUCTIONS CALL CC CNC CP CM CZ CNZ CPE CPO Call unconditionally Call on carry Call on no carry Call on positive Call on minus Call on zero Call on no zero Call on parity even Call on parity odd 48

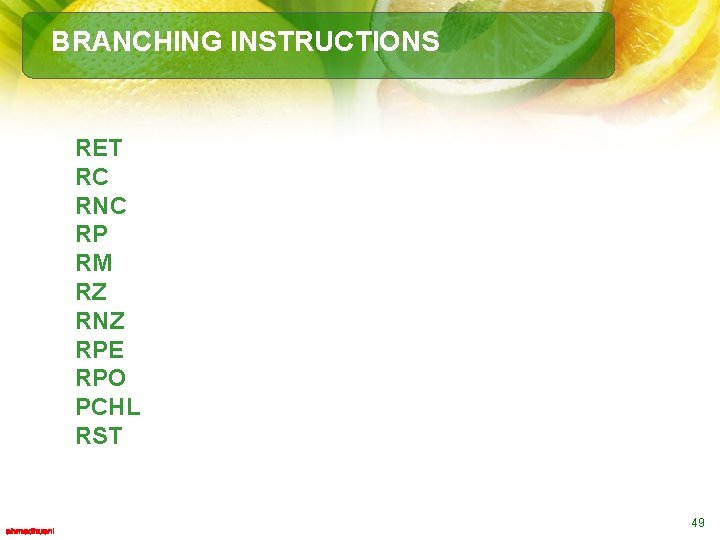

BRANCHING INSTRUCTIONS RET RC RNC RP RM RZ RNZ RPE RPO PCHL RST Return unconditionally Return on carry Return on no carry Return on positive Return on minus Return on zero Return on no zero Return on parity even Return on parity odd Load program counter with HL contents Restart 49

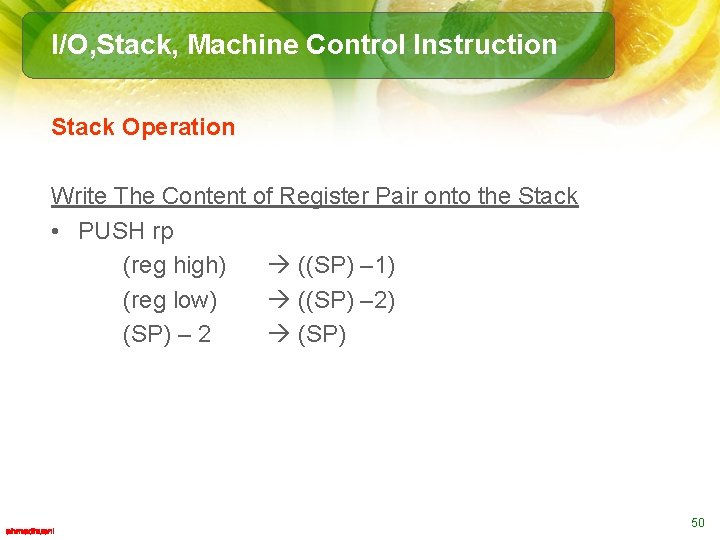

I/O, Stack, Machine Control Instruction Stack Operation Write The Content of Register Pair onto the Stack • PUSH rp (reg high) ((SP) – 1) (reg low) ((SP) – 2) (SP) – 2 (SP) 50

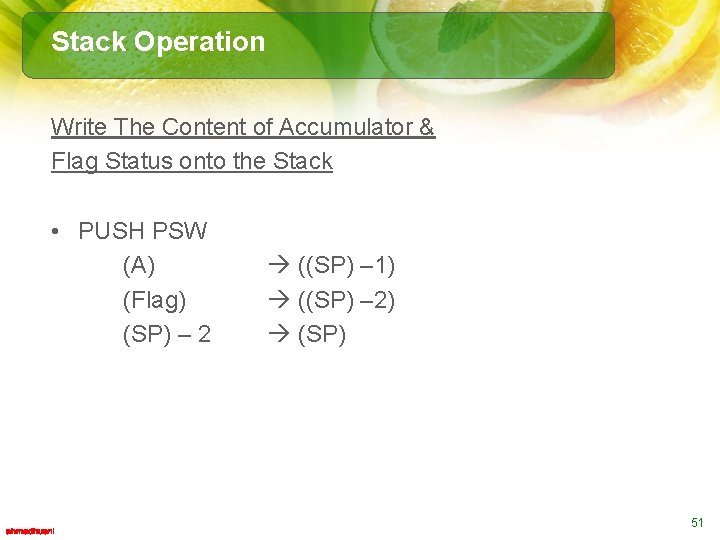

Stack Operation Write The Content of Accumulator & Flag Status onto the Stack • PUSH PSW (A) (Flag) (SP) – 2 ((SP) – 1) ((SP) – 2) (SP) 51

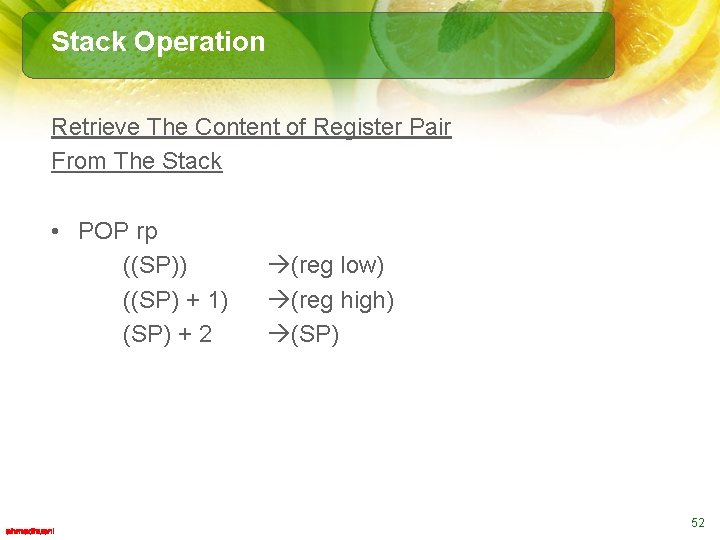

Stack Operation Retrieve The Content of Register Pair From The Stack • POP rp ((SP)) ((SP) + 1) (SP) + 2 (reg low) (reg high) (SP) 52

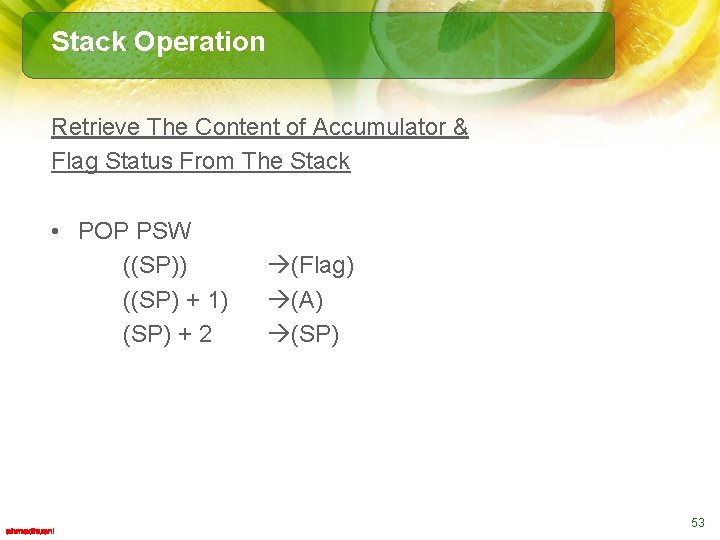

Stack Operation Retrieve The Content of Accumulator & Flag Status From The Stack • POP PSW ((SP)) ((SP) + 1) (SP) + 2 (Flag) (A) (SP) 53

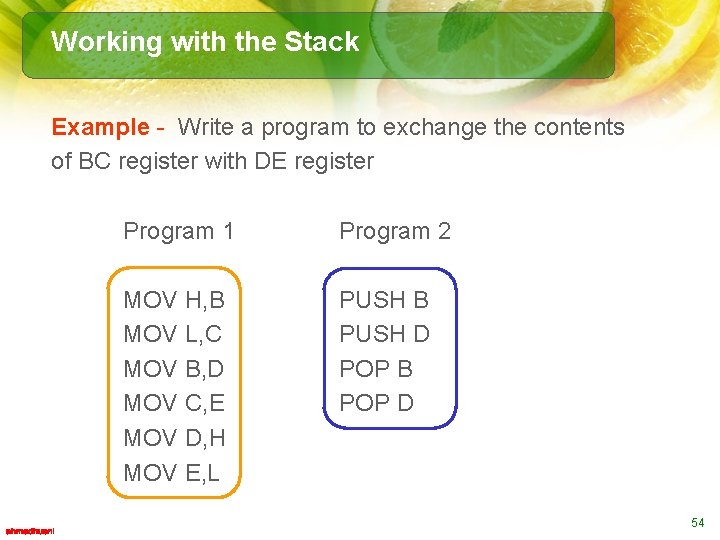

Working with the Stack Example - Write a program to exchange the contents of BC register with DE register Program 1 Program 2 MOV H, B MOV L, C MOV B, D MOV C, E MOV D, H MOV E, L PUSH B PUSH D POP B POP D 54

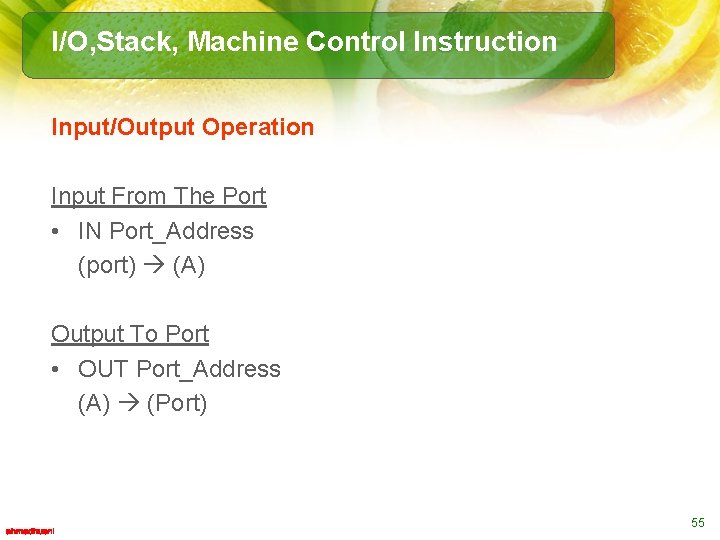

I/O, Stack, Machine Control Instruction Input/Output Operation Input From The Port • IN Port_Address (port) (A) Output To Port • OUT Port_Address (A) (Port) 55

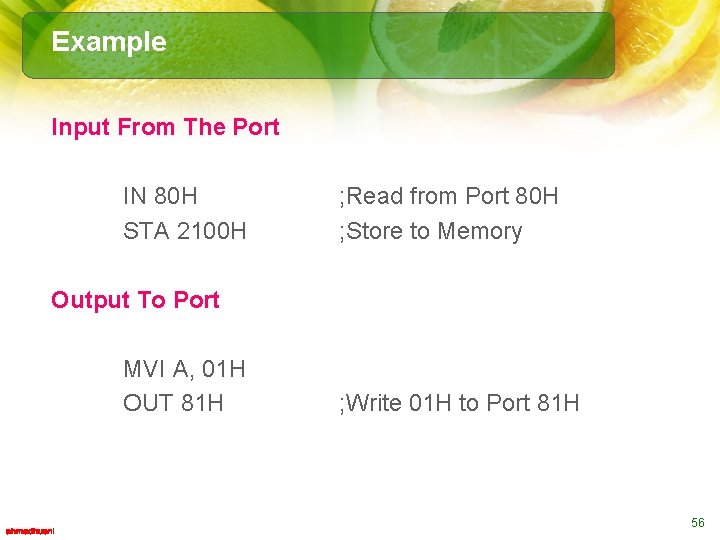

Example Input From The Port IN 80 H STA 2100 H ; Read from Port 80 H ; Store to Memory Output To Port MVI A, 01 H OUT 81 H ; Write 01 H to Port 81 H 56

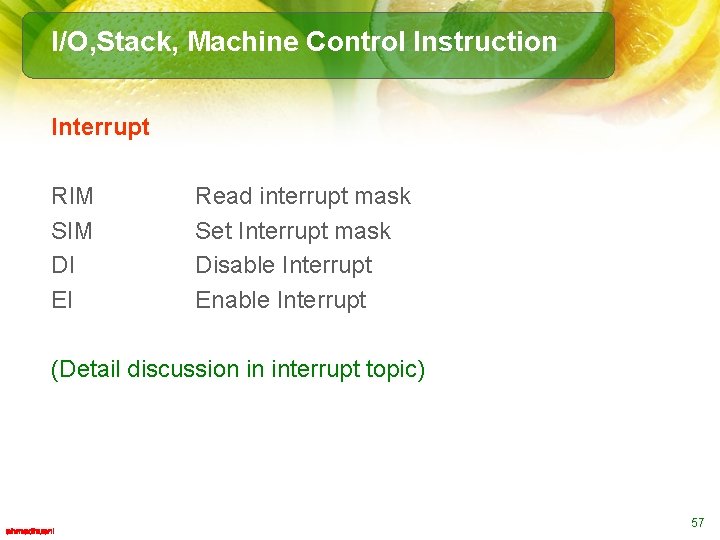

I/O, Stack, Machine Control Instruction Interrupt RIM SIM DI EI Read interrupt mask Set Interrupt mask Disable Interrupt Enable Interrupt (Detail discussion in interrupt topic) 57

I/O, STACK, MACHINE CONTROL INSTRUCTION PUSH POP OUT IN NOP HLT DI EI RIM SIM Push register pair onto stack Pop of stack to register pair Output data from A to a port with 8 -bit address Input data to A from a port with 8 -bit address No operation Halt Disable interrupts Enable interrupts Read interrupt mask Set interrupt mask 58

Common Errors • MOV B, A: Assuming that this copies from B to A. • Incrementing the address in decimal, from 2039 H to 2040 H. • HLT: Not terminating a program. 59

Continue with. . ASSEMBLY LANGUAGE PROGRAMMING 60

- Slides: 60