EMT 235 DIGITAL PRINCIPLES II Memory Basics Weeks

EMT 235 DIGITAL PRINCIPLES II Memory Basics Weeks 13 -14

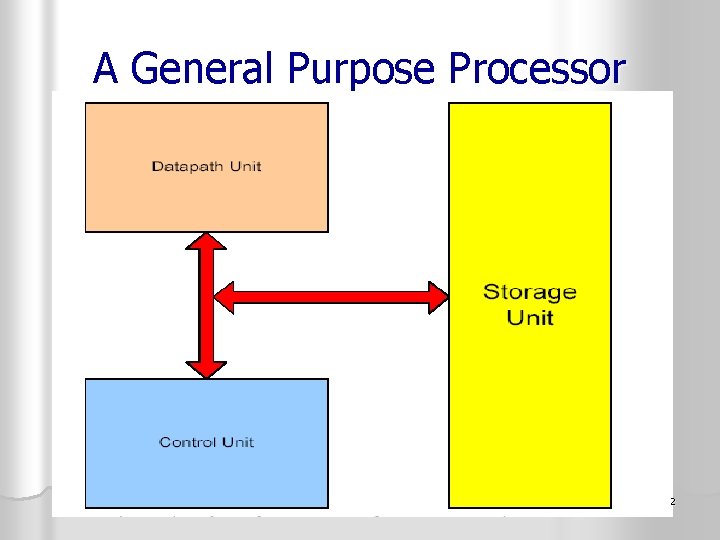

A General Purpose Processor 2

Memory ? ? ? l A major component of a digital computer and many digital systems. l Stores binary data, either permanently or temporarily. l Consists of arrays of elements: latches, capacitors or MOS transistors. 3

l l l l Overview Memory definitions Random Access Memory (RAM) Static RAM (SRAM) integrated circuits l Cells and slices l Cell arrays and coincident selection Arrays of SRAM integrated circuits Dynamic RAM (DRAM) integrated circuits DRAM Types l Synchronous (SDRAM) l Double-Data Rate (DDR SRAM) l RAMBUS DRAM (RDRAM) Arrays of DRAM integrated circuits 4

Memory Definitions l Collection of cells capable of storing binary information. l Contains electronic circuits for storing & retrieving information. l Used to provide temporary or permanent storage capability. l Semiconductor memories consists of arrays of elements that are generally latches, capacitors or MOS transistors. 5

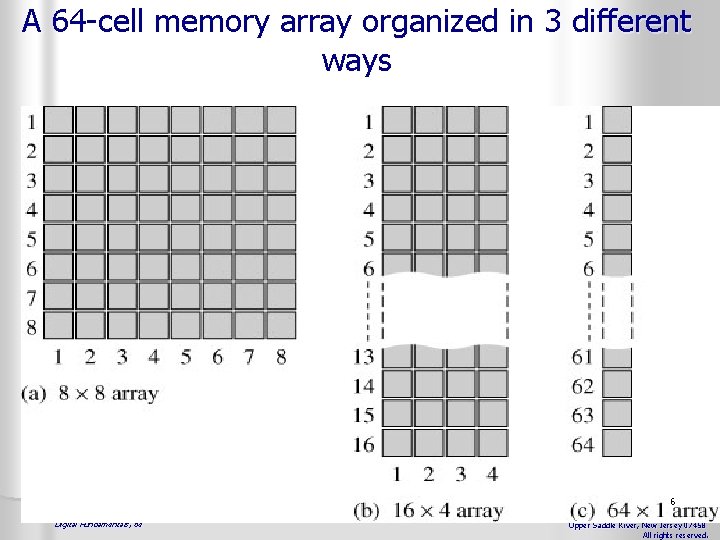

A 64 -cell memory array organized in 3 different ways 6 Thomas L. Floyd Digital Fundamentals, 8 e Copyright © 2003 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Memory Address and Capacity Each memory location needs an address. If the memory is addressed to a cell, then one bit is addressed. But, if the memory is addressed to the Byte or Word, then that is the smallest amount of data that can be addressed. 7

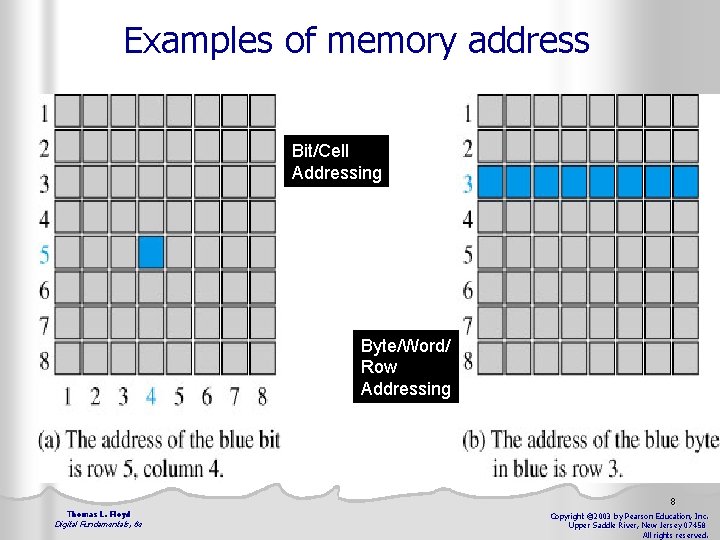

Examples of memory address Bit/Cell Addressing Byte/Word/ Row Addressing 8 Thomas L. Floyd Digital Fundamentals, 8 e Copyright © 2003 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

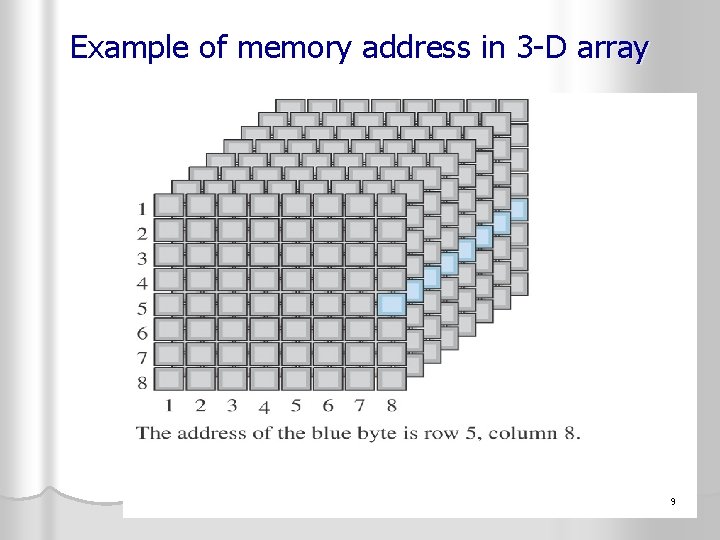

Example of memory address in 3 -D array 9

Memory Units l Bit : a single binary digit. l Nibble : a group of 4 bits accessed together. l Byte : a group of 8 bits accessed together. l Word : a group of binary bits whose size is a typical unit of access for the memory. (e. g. , 1 byte, 2 bytes, 4 bytes, 8 bytes, etc. ) 10

Memory data elements l Memory Data l A bit or a group of bits to be stored into or accessed from memory cells. l Memory Operations l Operations on memory data supported by the memory unit. Typically, read and write operations over some data element (bit, byte, word, etc. ). 11

Basic Memory Operations l Write operation l Puts data into a specified address in memory. l Read Operation l Takes data out of a specified address in memory. 12

Block Diagram of a Memory Unit Bidirectional 13

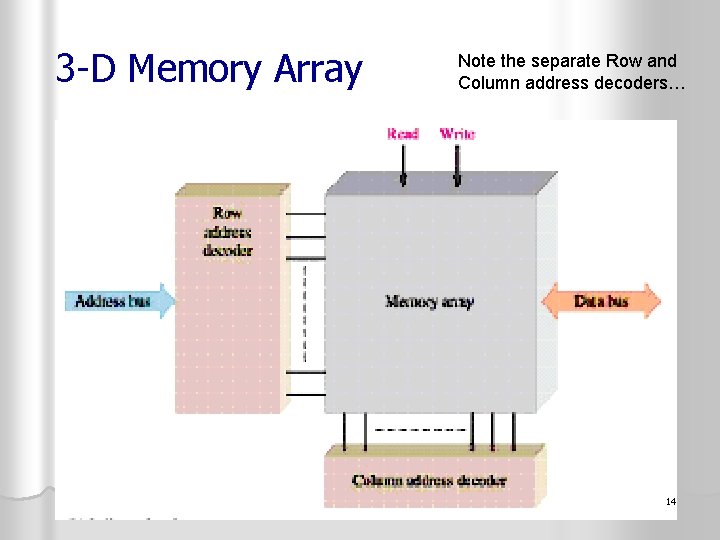

3 -D Memory Array Note the separate Row and Column address decoders… 14

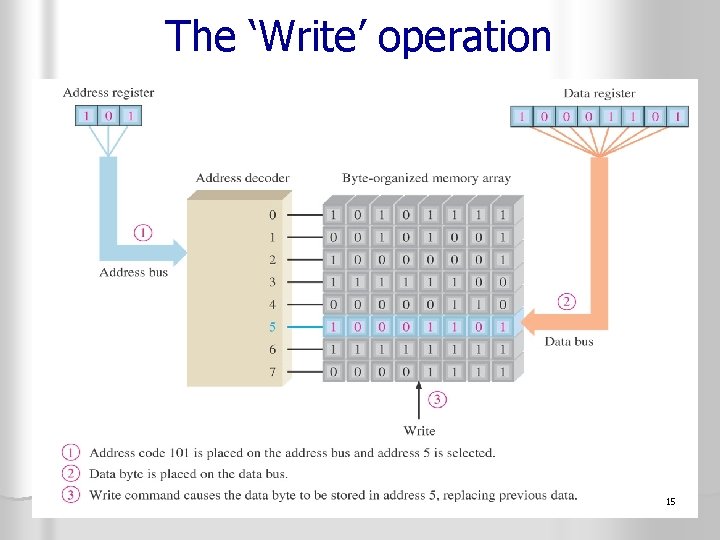

The ‘Write’ operation 15

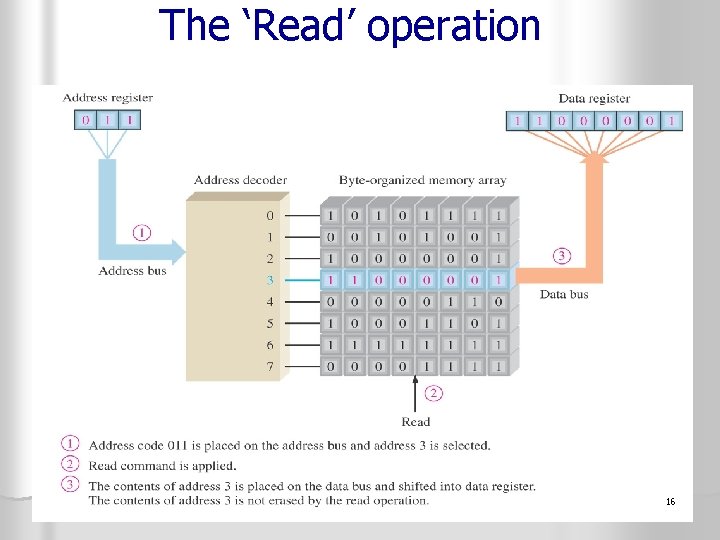

The ‘Read’ operation 16

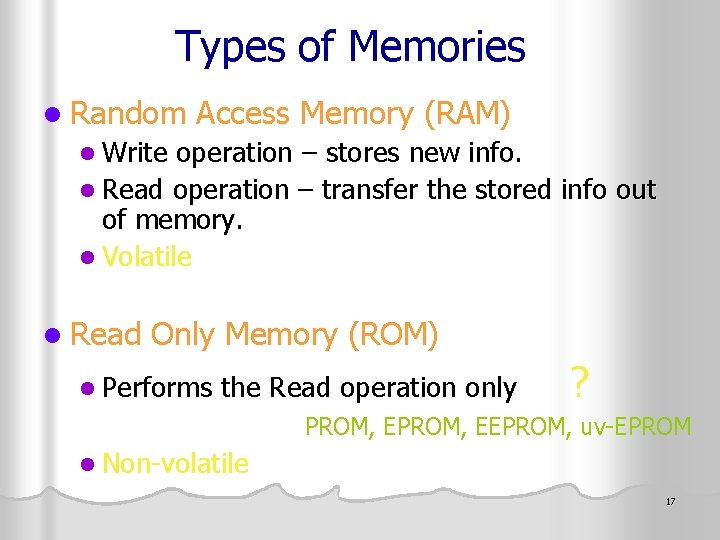

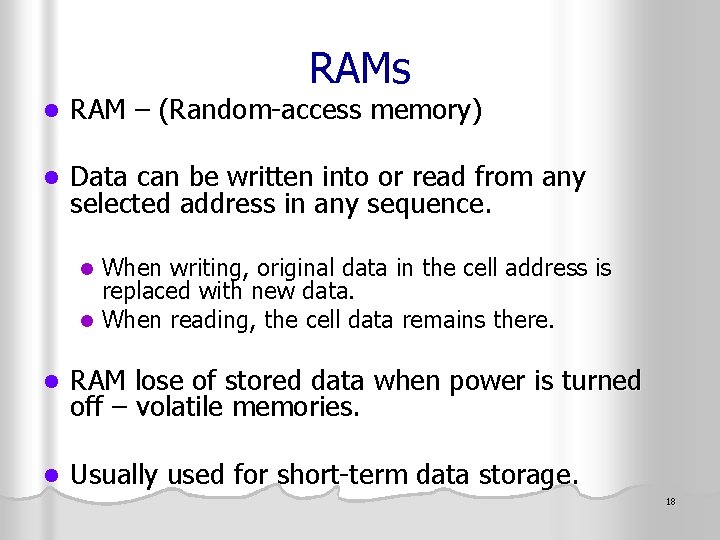

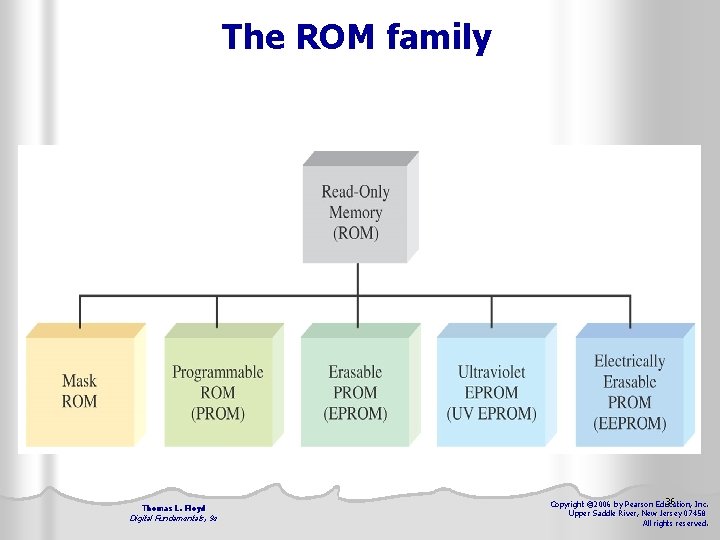

Types of Memories l Random Access Memory (RAM) l Write operation – stores new info. l Read operation – transfer the stored info out of memory. l Volatile l Read Only Memory (ROM) ? l Performs the Read operation only PROM, EEPROM, uv-EPROM l Non-volatile 17

RAMs l RAM – (Random-access memory) l Data can be written into or read from any selected address in any sequence. When writing, original data in the cell address is replaced with new data. l When reading, the cell data remains there. l l RAM lose of stored data when power is turned off – volatile memories. l Usually used for short-term data storage. 18

ROMs l ROM – (Read-only memory) l Data is stored permanently or semi- permanently. l Data is read but a write operation as in a RAM memory is also possible with special equipment. l Still random access like RAM, but ROMs retain data even when power is turned off. 19

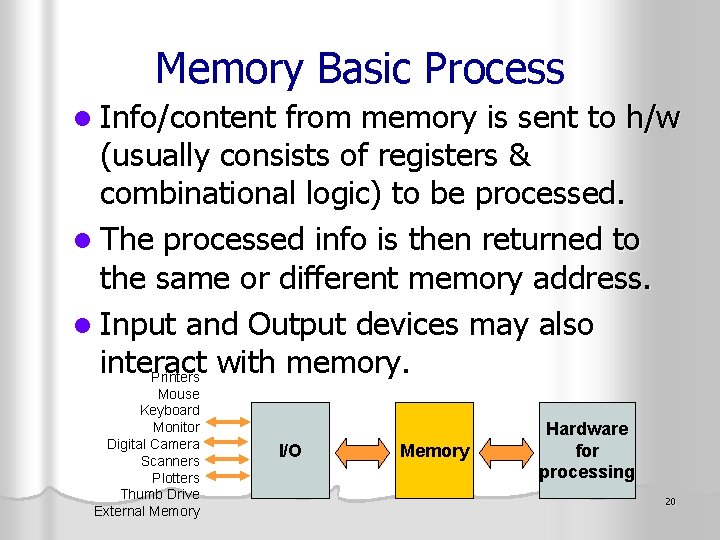

Memory Basic Process l Info/content from memory is sent to h/w (usually consists of registers & combinational logic) to be processed. l The processed info is then returned to the same or different memory address. l Input and Output devices may also interact with memory. Printers Mouse Keyboard Monitor Digital Camera Scanners Plotters Thumb Drive External Memory I/O Memory Hardware for processing 20

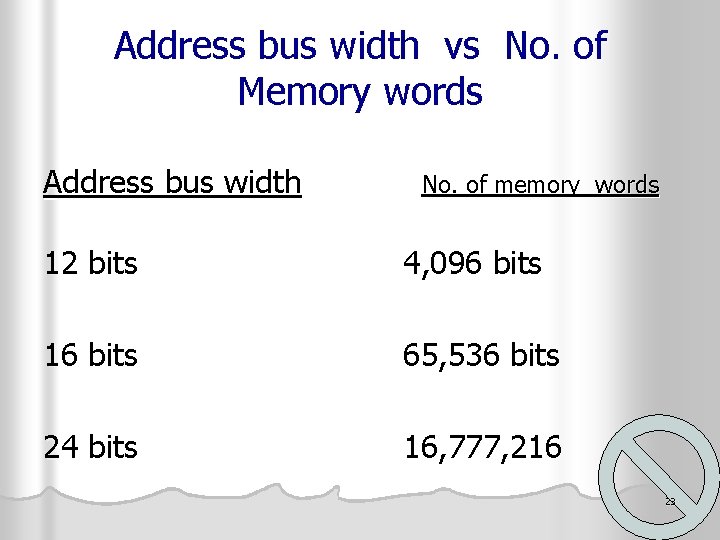

Calculator Exercise l 2 8 = 256 l 2 12 = 4, 096 l 2 16 = 65, 536 l 2 24 = 16, 777, 216 l 2 32 = 4, 294, 967, 296 21

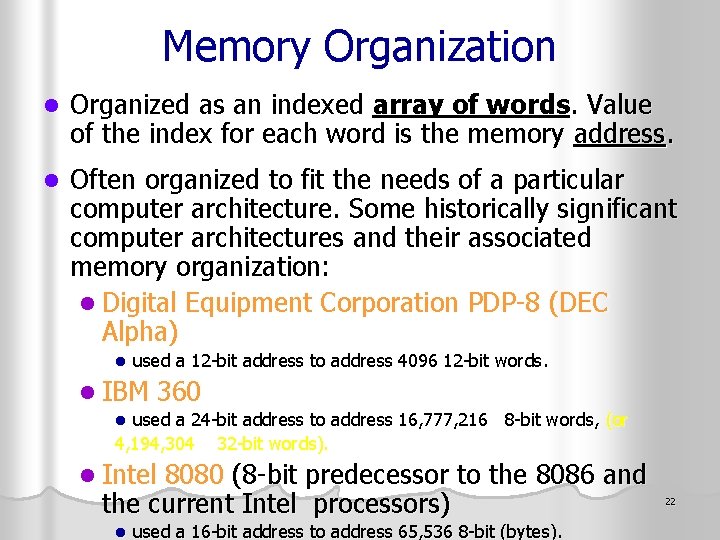

Memory Organization l Organized as an indexed array of words. Value of the index for each word is the memory address. l Often organized to fit the needs of a particular computer architecture. Some historically significant computer architectures and their associated memory organization: l Digital Equipment Corporation PDP-8 (DEC Alpha) l used a 12 -bit address to address 4096 12 -bit words. l IBM 360 used a 24 -bit address to address 16, 777, 216 8 -bit words, (or 4, 194, 304 32 -bit words). l l Intel 8080 (8 -bit predecessor to the 8086 and the current Intel processors) l used a 16 -bit address to address 65, 536 8 -bit (bytes). 22

Address bus width vs No. of Memory words Address bus width No. of memory words 12 bits 4, 096 bits 16 bits 65, 536 bits 24 bits 16, 777, 216 23

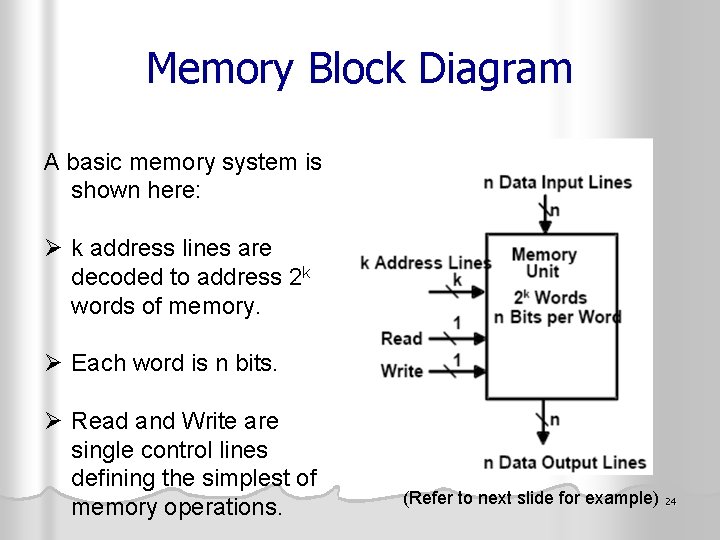

Memory Block Diagram A basic memory system is shown here: Ø k address lines are decoded to address 2 k words of memory. Ø Each word is n bits. Ø Read and Write are single control lines defining the simplest of memory operations. (Refer to next slide for example) 24

Memory Organization Example of memory contents above: • No. of data bits = 8; n = 8 • No. of address bits = 3; k = 3 • Therefore the number of address lines = m = (2 k); 23 = 8 • Address range: 0 to 2 k -1; therefore 0 to 23 – 1, Add. Range: 0 to 7 • 1 word is the size of the memory content; so the memory above 25 has 8 words of 8 -bit data

The ‘Write’ operation k=3 No. of columns = No. of Data bits n = No. of Data input & ouput lines n=8 No. of add. Rows (locations) m = 2 k = 8 n-bits per word 26

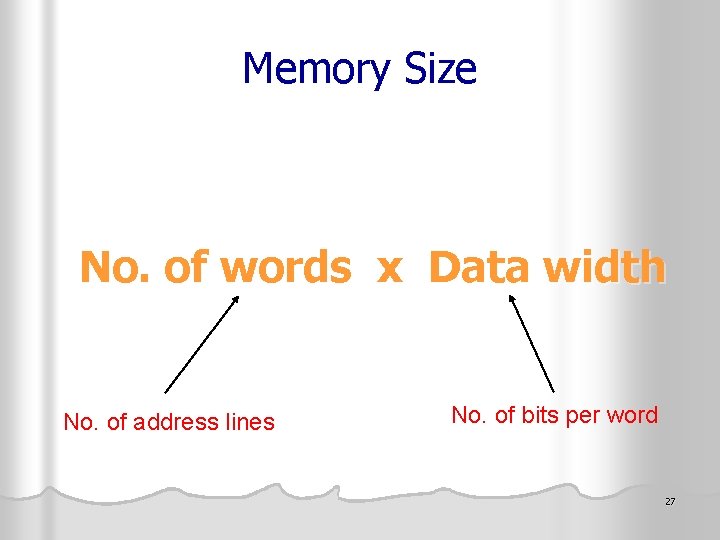

Memory Size No. of words x Data width No. of address lines No. of bits per word 27

Memory Size Units l K (Kilo) = 210 l M (Mega) = 220 l G (Giga) = 230 Examples : l 64 K = 216 = (26 * 210) l 2 M = 221 = (21 * 220) l 4 G = 232 = (22 * 230) 28

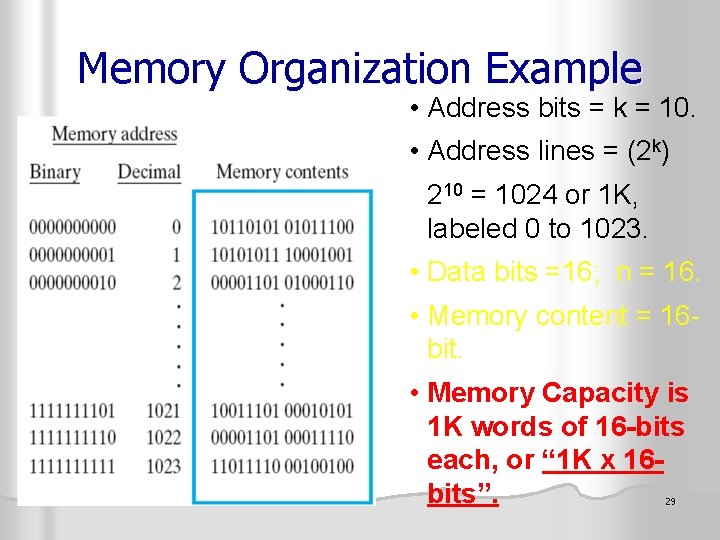

Memory Organization Example • Address bits = k = 10. • Address lines = (2 k) 210 = 1024 or 1 K, labeled 0 to 1023. • Data bits =16; n = 16. • Memory content = 16 bit. • Memory Capacity is 1 K words of 16 -bits each, or “ 1 K x 16 bits”. 29

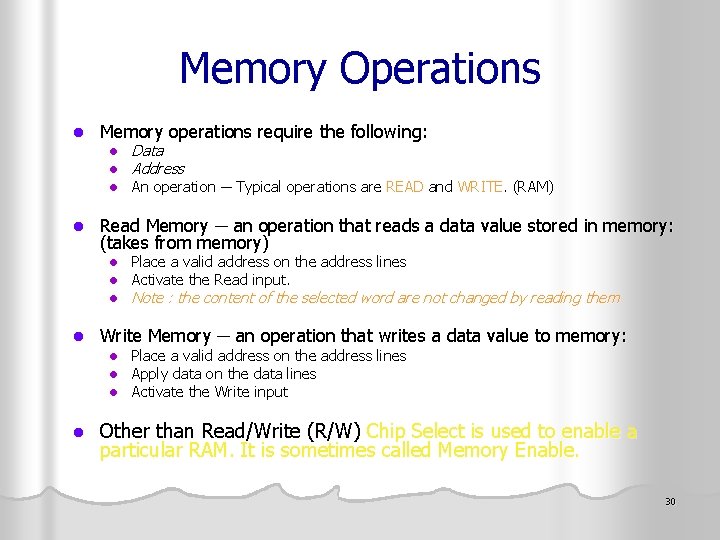

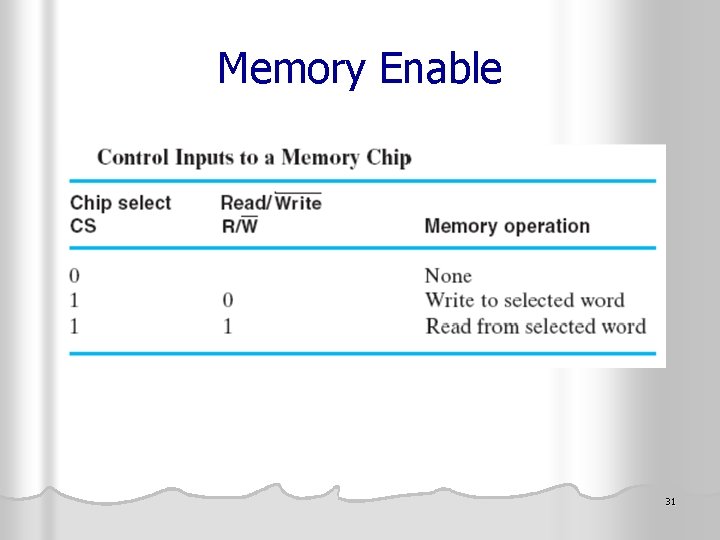

Memory Operations l Memory operations require the following: l l Place a valid address on the address lines Activate the Read input. Note : the content of the selected word are not changed by reading them Write Memory ─ an operation that writes a data value to memory: l l An operation ─ Typical operations are READ and WRITE. (RAM) Read Memory ─ an operation that reads a data value stored in memory: (takes from memory) l l Data Address Place a valid address on the address lines Apply data on the data lines Activate the Write input Other than Read/Write (R/W) Chip Select is used to enable a particular RAM. It is sometimes called Memory Enable. 30

Memory Enable 31

Exercise Questions 1. How many address lines and data lines are needed for each of the following memories? l 16 K x 8 l 256 K x 16 l 64 M x 32 l 2 G x 8 32

… Exercise Questions 2. Sketch the memory organisation for each of the following memories. l 16 K x 8 l 256 K x 16 l 64 M x 32 l 2 G x 8 33

… Exercise Questions 3. Give the no. of bytes stored in each of the following memories. l 16 K x 8 l 256 K x 16 l 64 M x 32 l 2 G x 8 34

ROM Read Only Memory 35

The ROM family Thomas L. Floyd Digital Fundamentals, 9 e 36 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

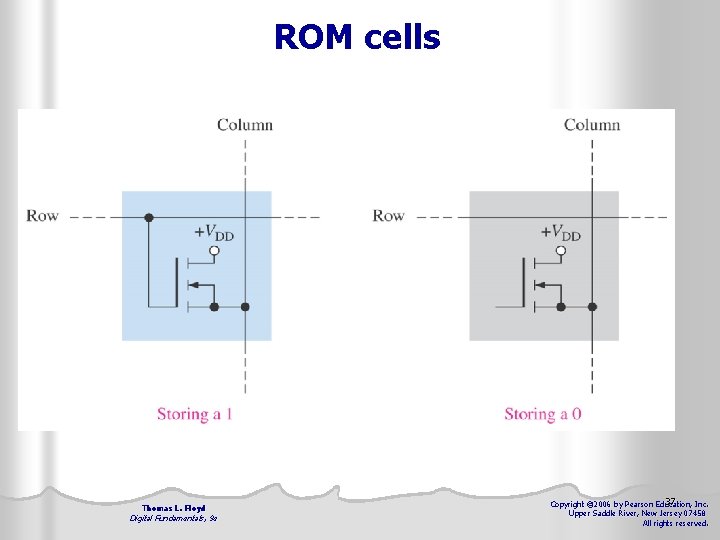

ROM cells Thomas L. Floyd Digital Fundamentals, 9 e 37 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

A representation of a 16 x 8 -bit ROM array Thomas L. Floyd Digital Fundamentals, 9 e 38 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

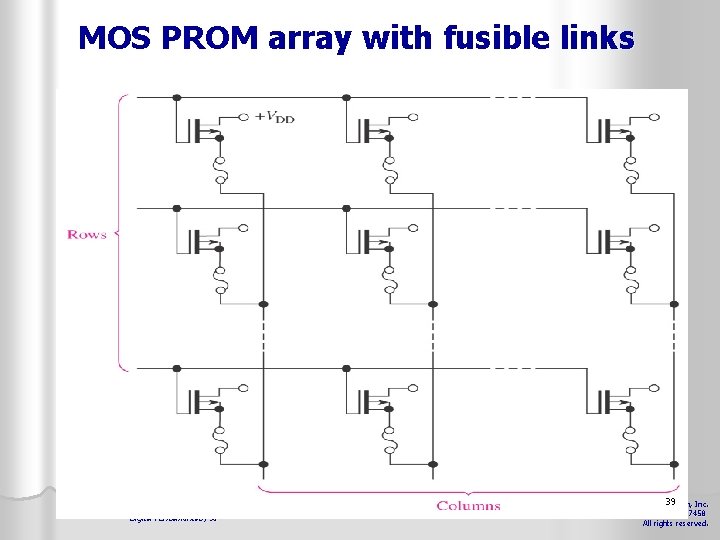

MOS PROM array with fusible links Thomas L. Floyd Digital Fundamentals, 9 e 39 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

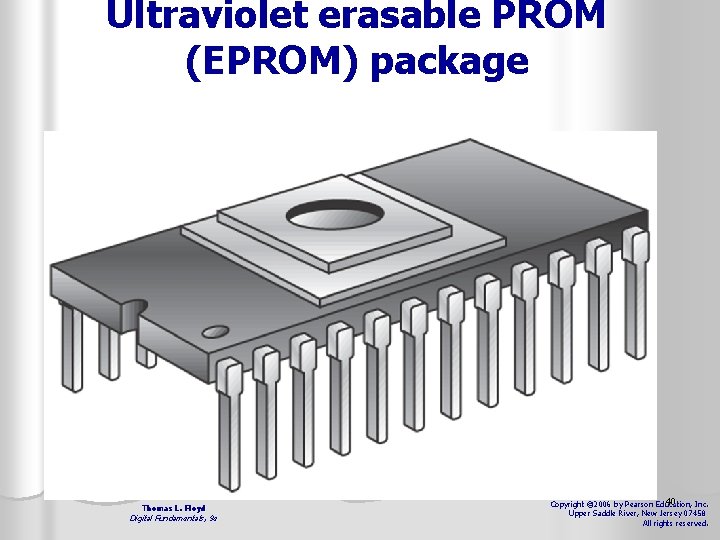

Ultraviolet erasable PROM (EPROM) package Thomas L. Floyd Digital Fundamentals, 9 e 40 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

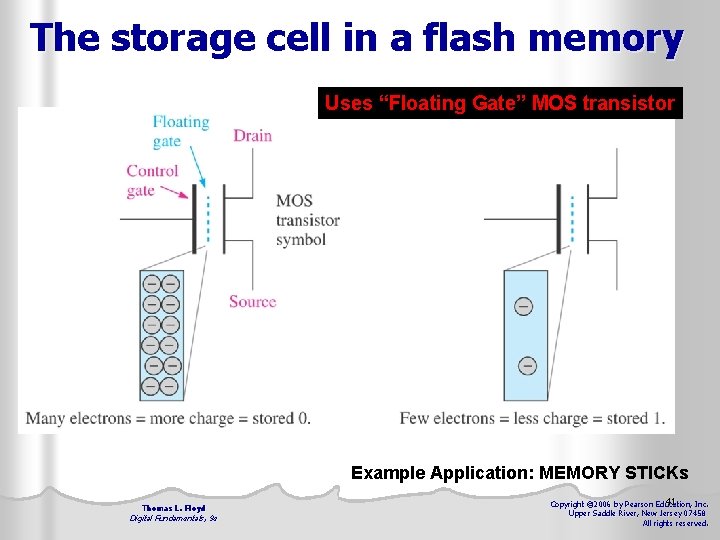

The storage cell in a flash memory Uses “Floating Gate” MOS transistor Example Application: MEMORY STICKs Thomas L. Floyd Digital Fundamentals, 9 e 41 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

RAM Random Access Memory 42

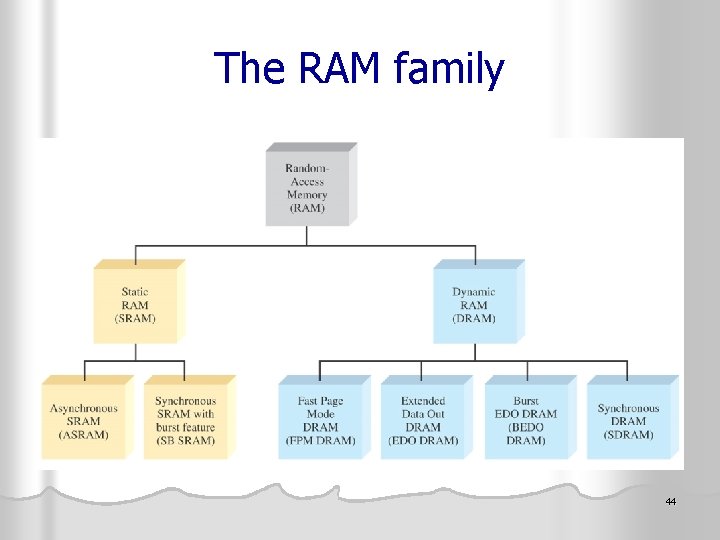

RAM Integrated Circuit l Types of random access memory (RAM) Static – information stored in latches l Dynamic – information stored as electrical charges on l capacitors l Charge “leaks” off l Periodic “refresh” of charge required l Dependence on Power Supply l Volatile – loses stored information when power is turned off (example : FPGA – Flex 10 K). Both static and dynamic RAM are volatile. 43

The RAM family 44

SRAM ICs SRAM = Static RAM 45

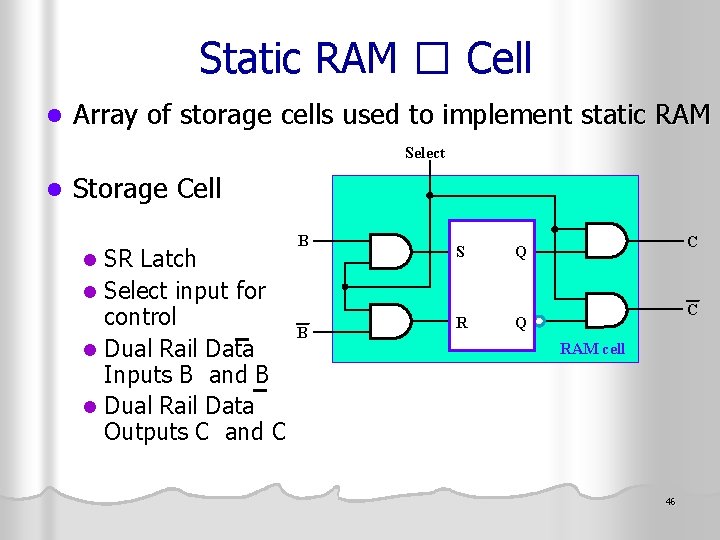

Static RAM � Cell l Array of storage cells used to implement static RAM Select l Storage Cell SR Latch l Select input for control l Dual Rail Data Inputs B and B l Dual Rail Data Outputs C and C l B B S Q R Q C C RAM cell 46

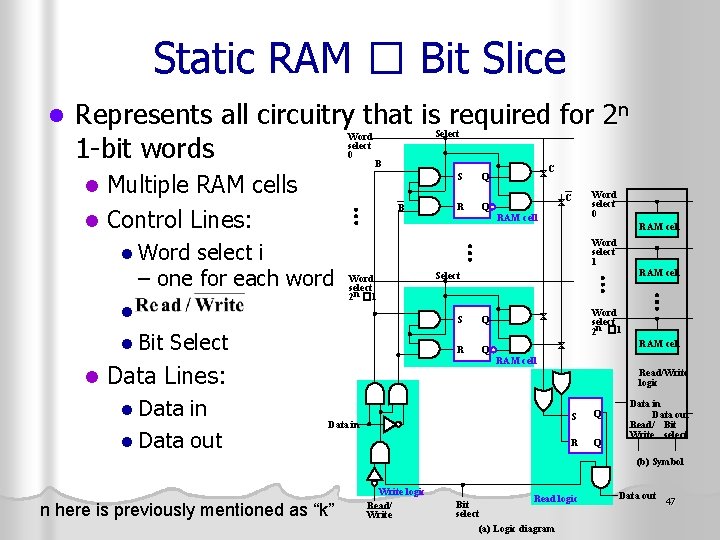

Static RAM � Bit Slice l Represents all circuitry that is required for 2 n 1 -bit words Word select 0 Select B Multiple RAM cells l Control Lines: l B S Q R Q XC C X RAM cell Word select 1 l Word select i – one for each word l l Bit Select l Word select 2 n � 1 Data Lines: l Data in l Data out Word select 0 RAM cell Select S Q R Q Word select 2 n � 1 X RAM cell Read/Write logic Data in S Q R Q Data in Data out Read/ Bit Write select (b) Symbol n here is previously mentioned as “k” Write logic Read/ Write Read logic Bit select (a) Logic diagram Data out 47

n 2 -Word 1 -Bit RAM IC l To build a RAM IC A 3 from a RAM slice, A 2 we need: A 1 l Decoder � decodes A 0 the n address lines to 2 n word select lines input Data l A 3 -state buffer � A 3 A 2 A 1 16 x 1 RAM Data output l on the data output Read/ Write permits RAM ICs to. Memory enable be combined into a RAM with c 2 n words A 0 Word select 4 -to-16 Decoder 0 1 23 2 RAM cell 3 22 4 5 21 6 RAM cell 0 7 2 8 9 10 11 12 13 14 15 RAM cell Read/Write logic (a) Symbol Data input Data in Data out Read/ Bit Write select Read/Write n here is previously mentioned as “k” Data output 48 Chip select (b) Block diagram

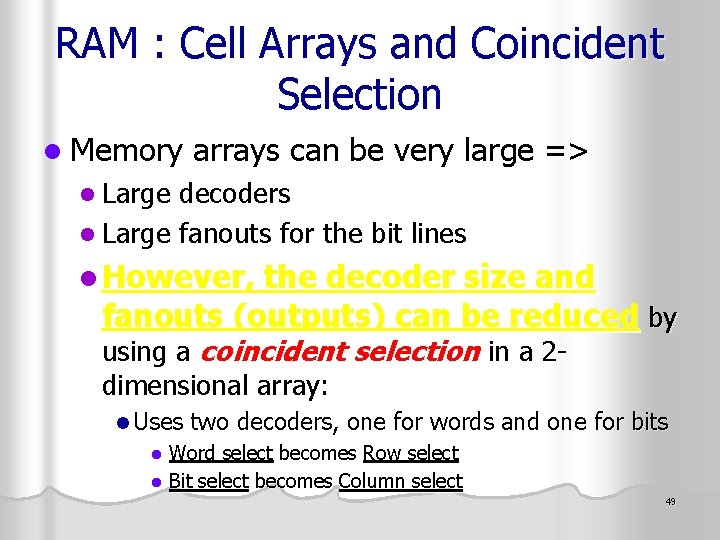

RAM : Cell Arrays and Coincident Selection l Memory arrays can be very large => l Large decoders l Large fanouts for the bit lines l However, the decoder size and fanouts (outputs) can be reduced by using a coincident selection in a 2 dimensional array: l Uses two decoders, one for words and one for bits l Word select becomes Row select l Bit select becomes Column select 49

Coincident… ? ? 50

Previous 16 x 1 RAM 51

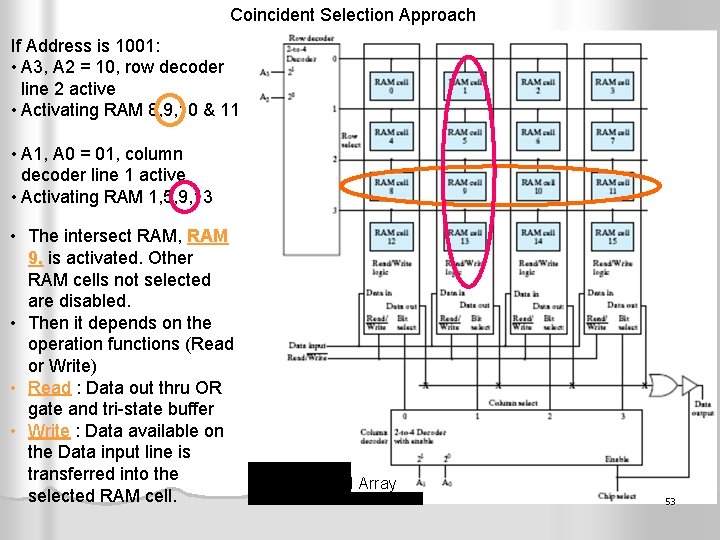

Coincident Selection Approach for the 16 X 1 RAM Chip • 4 bit address [A 3. . A 0] thus 24 = 16 RAM cells • The column decoder is enabled with the CS input • When CS =0, column decoder is disabled and all o/p’s are 0 and NONE of the cells are selected l A 3 and A 2 used for Row select l A 1 and A 0 for Column select 16 X 1 RAM using 4 X 4 RAM Cell Array 52

Coincident Selection Approach If Address is 1001: • A 3, A 2 = 10, row decoder line 2 active • Activating RAM 8, 9, 10 & 11 • A 1, A 0 = 01, column decoder line 1 active • Activating RAM 1, 5, 9, 13 • The intersect RAM, RAM 9, is activated. Other RAM cells not selected are disabled. • Then it depends on the operation functions (Read or Write) • Read : Data out thru OR gate and tri-state buffer • Write : Data available on the Data input line is transferred into the selected RAM cell. 4 x 4 RAM Cell Array 53

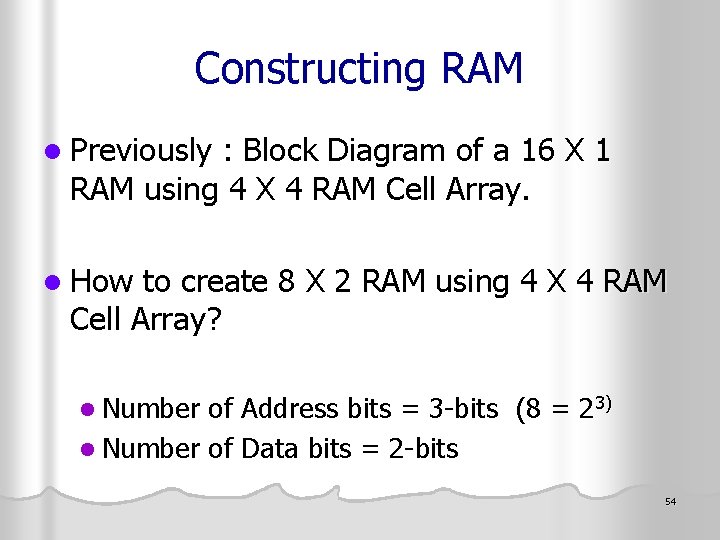

Constructing RAM l Previously : Block Diagram of a 16 X 1 RAM using 4 X 4 RAM Cell Array. l How to create 8 X 2 RAM using 4 X 4 RAM Cell Array? l Number of Address bits = 3 -bits (8 = 23) l Number of Data bits = 2 -bits 54

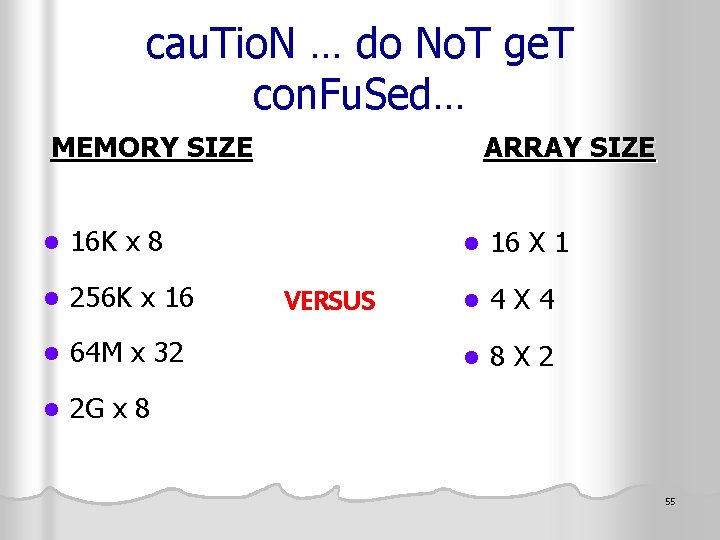

cau. Tio. N … do No. T ge. T con. Fu. Sed… MEMORY SIZE l 16 K x 8 l 256 K x 16 l 64 M x 32 l 2 G x 8 ARRAY SIZE VERSUS l 16 X 1 l 4 X 4 l 8 X 2 55

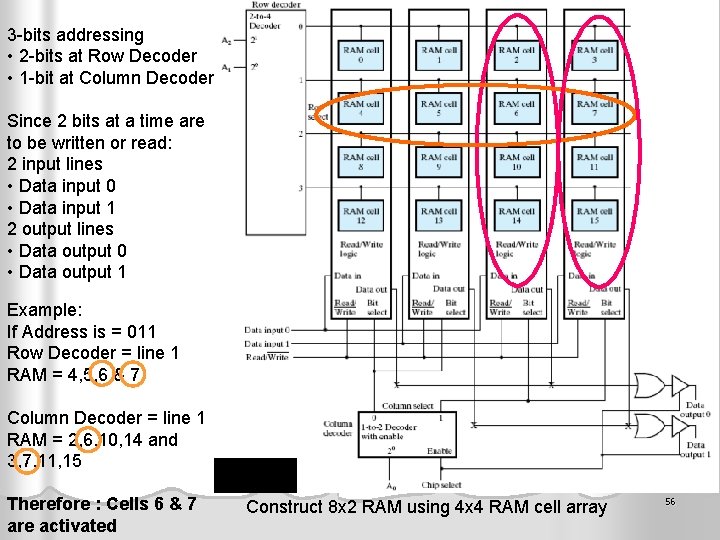

3 -bits addressing • 2 -bits at Row Decoder • 1 -bit at Column Decoder Since 2 bits at a time are to be written or read: 2 input lines • Data input 0 • Data input 1 2 output lines • Data output 0 • Data output 1 Example: If Address is = 011 Row Decoder = line 1 RAM = 4, 5, 6 & 7 Column Decoder = line 1 RAM = 2, 6, 10, 14 and 3, 7, 11, 15 Therefore : Cells 6 & 7 are activated Construct 8 x 2 RAM using 4 x 4 RAM cell array 56

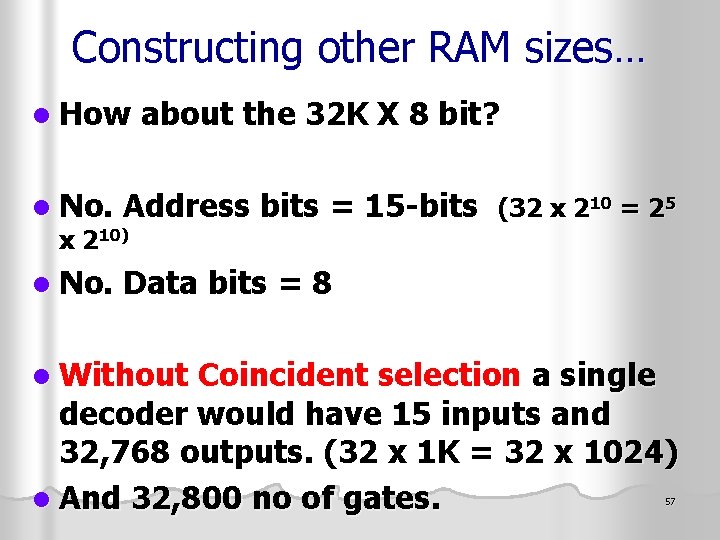

Constructing other RAM sizes… l How about the 32 K X 8 bit? l No. Address x 210) l No. bits = 15 -bits (32 x 210 = 25 Data bits = 8 l Without Coincident selection a single decoder would have 15 inputs and 32, 768 outputs. (32 x 1 K = 32 x 1024) l And 32, 800 no of gates. 57

… Constructing RAM l With Coincident selection: l Make row and column equal l Total no. of RAM cells = 32 K x 8 = 256 K = 262, 144 l Take Square Root of 262144 = 512 l (No. columns = No. Rows) l 512 = 29 , meaning 9 -bits is fed to the ROW Decoder. l Remaining 6 -bits is fed to the COLUMN Decoder. l Row Decoder : 9 to 512 line decoder l Column Decoder : 6 to 64 line decoder l No of gates = 608 58

Expansion of Memory u. Sin. G Array of SRAM ICs … ? - Making Larger or Wider Memories from Smaller Ones… 59

Memory Expansion Increase word length, or word capacity, or both 60

Make wider memories … 61

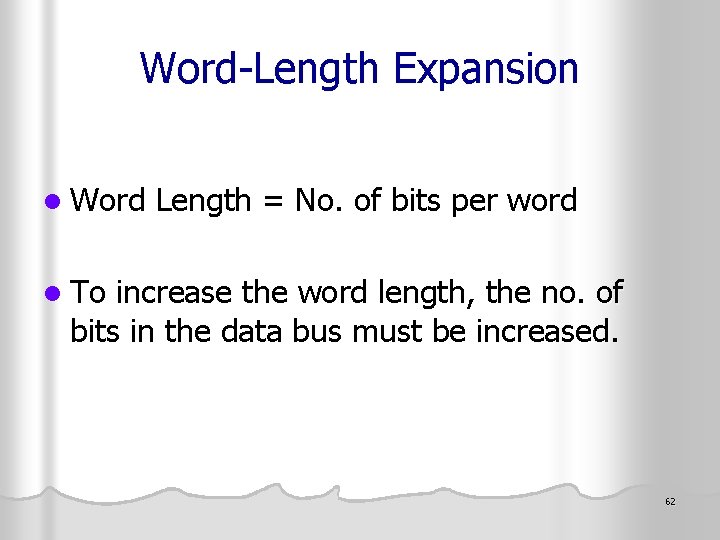

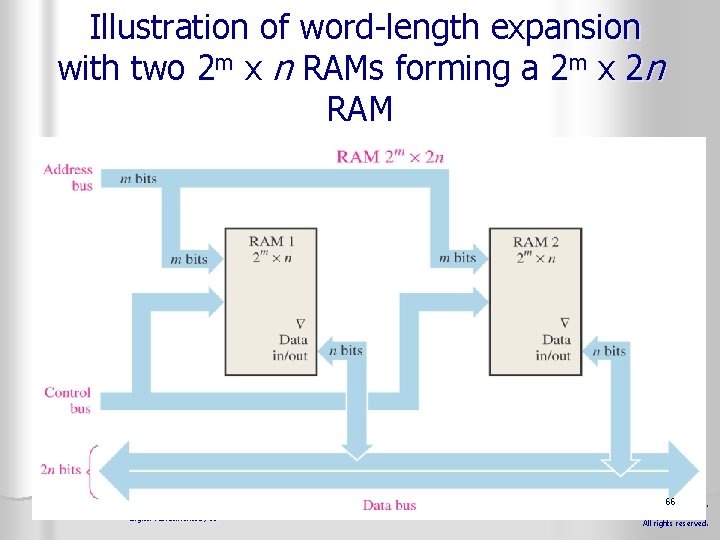

Word-Length Expansion l Word Length = No. of bits per word l To increase the word length, the no. of bits in the data bus must be increased. 62

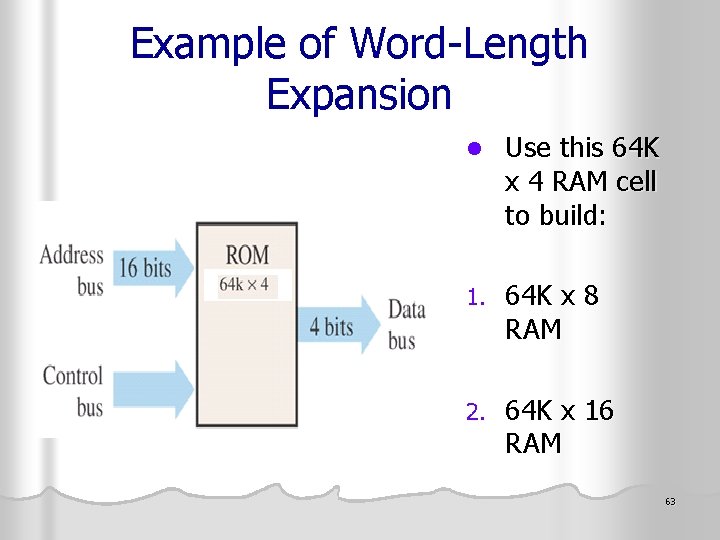

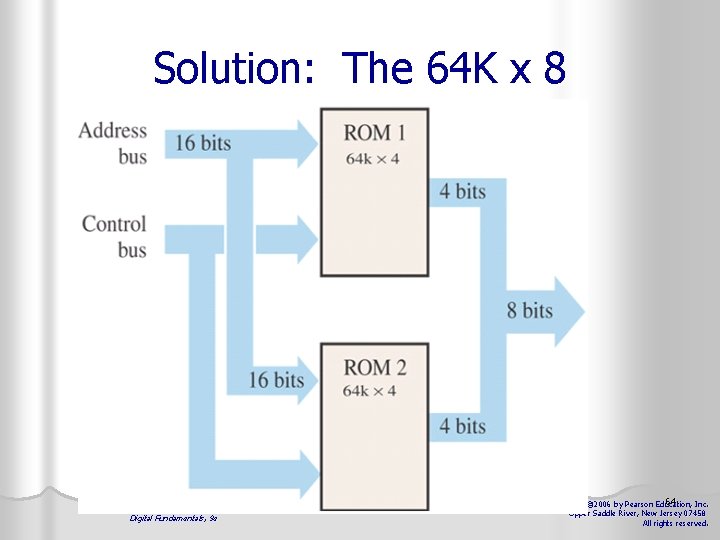

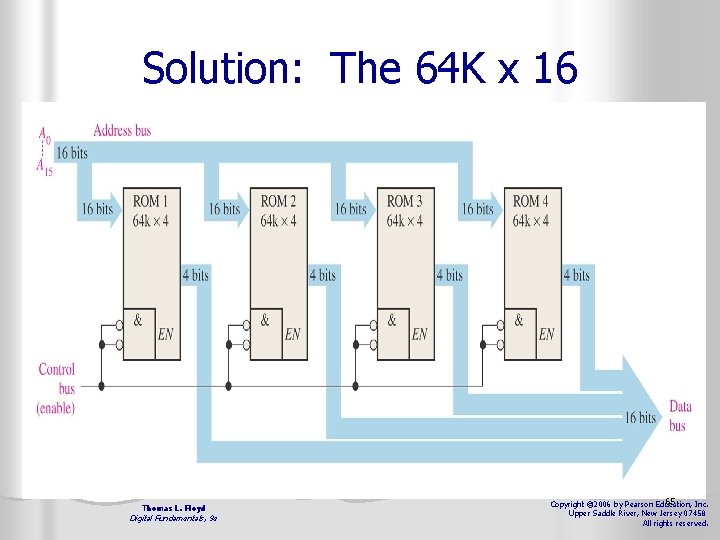

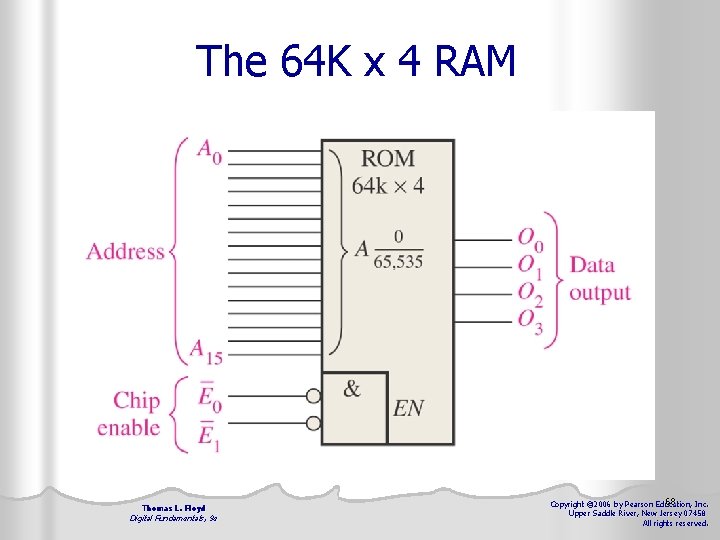

Example of Word-Length Expansion l Use this 64 K x 4 RAM cell to build: 1. 64 K x 8 RAM 2. 64 K x 16 RAM 63

Solution: The 64 K x 8 Thomas L. Floyd Digital Fundamentals, 9 e 64 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Solution: The 64 K x 16 Thomas L. Floyd Digital Fundamentals, 9 e 65 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Illustration of word-length expansion with two 2 m x n RAMs forming a 2 m x 2 n RAM Thomas L. Floyd Digital Fundamentals, 9 e 66 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

In Detailed Block Diagram form 67

The 64 K x 4 RAM Thomas L. Floyd Digital Fundamentals, 9 e 68 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

The 64 K x 8 RAM Thomas L. Floyd Digital Fundamentals, 9 e 69 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

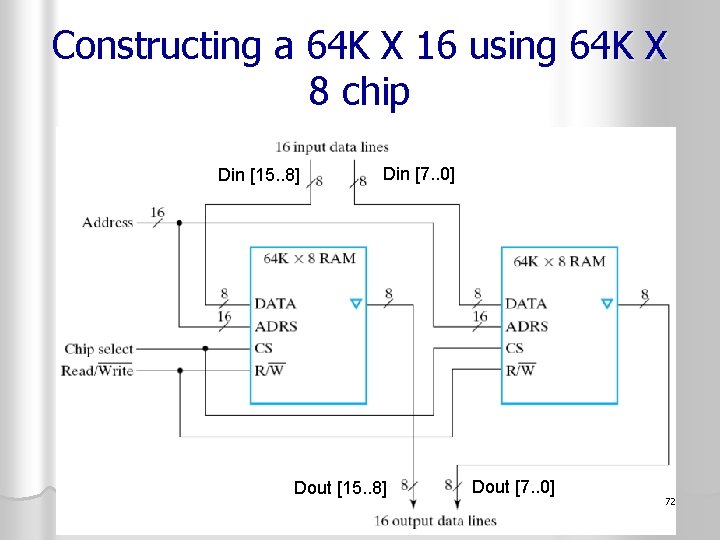

Expand the word size? Example : 64 K X 16 using 64 K X 8 chips. No. of chips to be used refers to the word size. In this case, 16 -bits is to be constructed from 8 -bit words. l Therefore 2 of 64 K X 8 Chip is to be used. l l Connections: l l Address line is input to both chips CS is common to both chips R/W control input is also common to both chips INPUT & OUTPUT DATA LINE is SPLIT 70

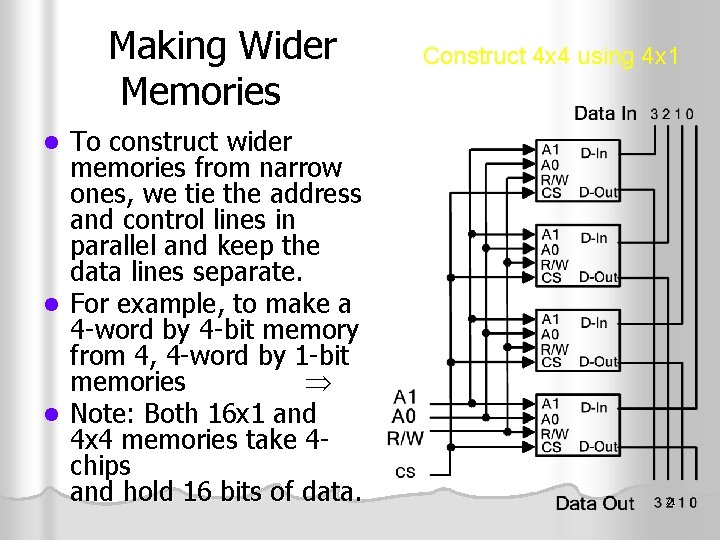

Making Wider Memories To construct wider memories from narrow ones, we tie the address and control lines in parallel and keep the data lines separate. l For example, to make a 4 -word by 4 -bit memory from 4, 4 -word by 1 -bit memories l Note: Both 16 x 1 and 4 x 4 memories take 4 chips and hold 16 bits of data. Construct 4 x 4 using 4 x 1 l 71

Constructing a 64 K X 16 using 64 K X 8 chip Din [15. . 8] Din [7. . 0] Dout [15. . 8] Dout [7. . 0] 72

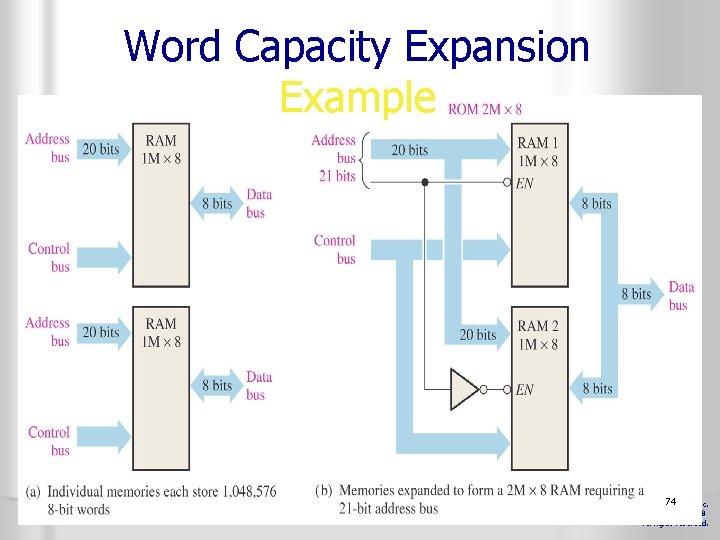

Word-Capacity Expansion l Word Capacity = No. of words l To increase the word capacity, the no. of address locations is increased. l To achieve this, the no. of address bits must be increased. 73

Word Capacity Expansion Example Thomas L. Floyd Digital Fundamentals, 9 e 74 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

In block diagram form Thomas L. Floyd Digital Fundamentals, 9 e 75 Copyright © 2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Conclude… l 1 M x 8 l 220 20 -bits of address lines l 2 M x 8 l 2 x 220 = 221 21 -bits of address lines l Adding 1 -bit to the address line results in doubling the no. of words 76

ARRAY of SRAM ICs If an application is larger than the capacity of one chip, then l There is a need to combine a number of chips in an array to form a required size of memory. l Depends on 2 parameters l No. of words l No. of bits per word l l No. of address lines No. of words l l 1 -bit added to the address would double the no. of words No. of bits per word No. of data input & output lines l If 1 -bit is added to the word size, 1 data input & output line must be added 77

Bigger. . h. OW ? l To make wider memories (bigger memory data size) l No. of bits per word No. of data input & output lines l If 1 -bit is added to the word size, 1 data input & output line must be added l To make larger memories (more address locations) l No. of address lines No. of words l 1 -bit added to the address would double the no. of words 78

Make Larger memories … 79

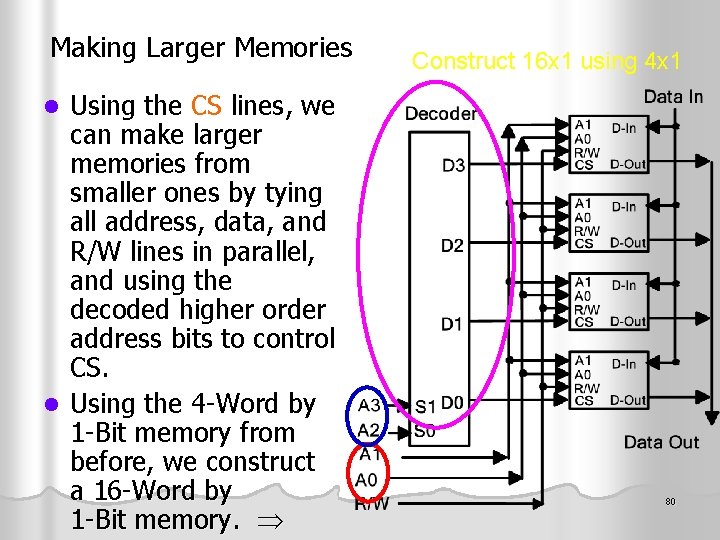

Making Larger Memories Using the CS lines, we can make larger memories from smaller ones by tying all address, data, and R/W lines in parallel, and using the decoded higher order address bits to control CS. l Using the 4 -Word by 1 -Bit memory from before, we construct a 16 -Word by 1 -Bit memory. Construct 16 x 1 using 4 x 1 l 80

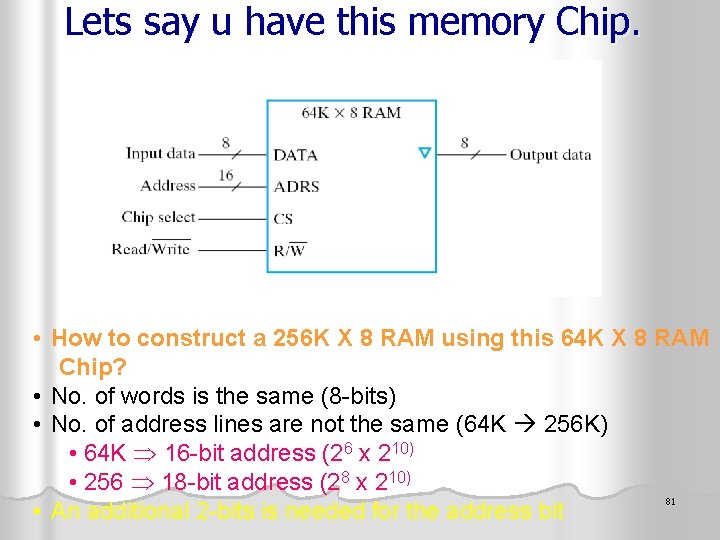

Lets say u have this memory Chip. • How to construct a 256 K X 8 RAM using this 64 K X 8 RAM Chip? • No. of words is the same (8 -bits) • No. of address lines are not the same (64 K 256 K) • 64 K 16 -bit address (26 x 210) • 256 18 -bit address (28 x 210) 81 • An additional 2 -bits is needed for the address bit

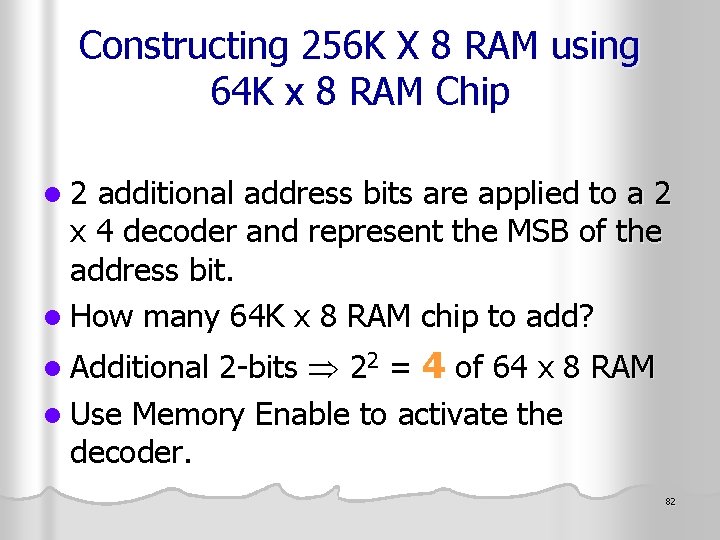

Constructing 256 K X 8 RAM using 64 K x 8 RAM Chip l 2 additional address bits are applied to a 2 x 4 decoder and represent the MSB of the address bit. l How many 64 K x 8 RAM chip to add? l Additional 2 -bits 22 = 4 of 64 x 8 RAM l Use Memory Enable to activate the decoder. 82

Constructing 256 K X 8 RAM using 64 K x 8 RAM Chip When bit 17 and 16 = 00 The first 64 x 8 RAM is activated Address : 0 – 65, 535 When bit 17 and 16 = 01 The 2 nd 64 x 8 RAM is activated Address : 65, 536 – 131, 071 When bit 17 and 16 = 10 The 3 rd 64 x 8 RAM is activated Address : 131, 071 – 196, 607 When bit 17 and 16 = 11 The 4 th 64 x 8 RAM is activated Address : 196, 608 – 262, 143 Construct 256 Kx 8 using 64 Kx 8 83

Conclude… l Add 2 more extra bits to the address input and get ? 4 l ____ times more no. of words (address locations). l From 64 K to 256 K 84

Exercise To be handed in … 85

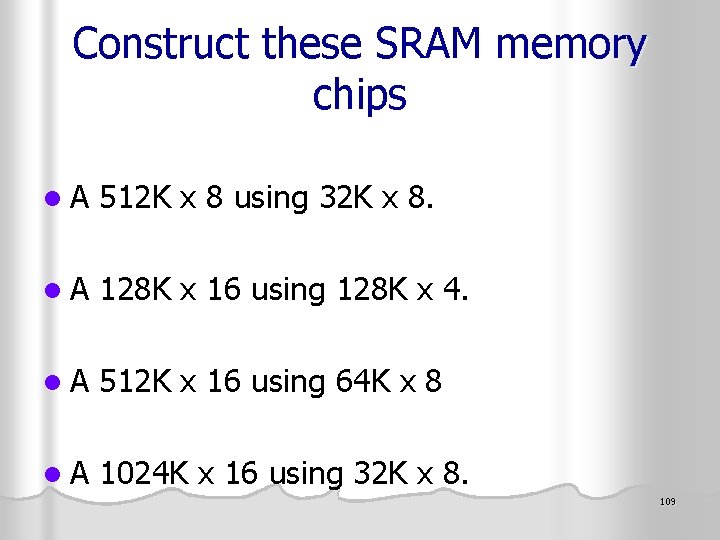

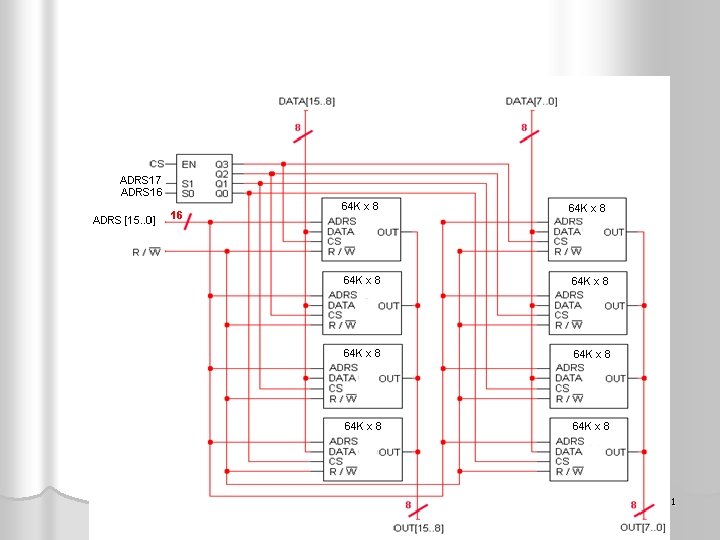

Construct these SRAM memory chips l A 512 K x 8 using 32 K x 8. l A 128 K x 16 using 128 K x 4. l A 512 K x 16 using 64 K x 8 l A 1024 K x 16 using 32 K x 8. 86

Dynamic RAM (DRAM) 87

Dynamic RAM (DRAM) l Basic Principle: Storage of information on capacitors. l Charge and discharge of capacitor to change stored value l Use of transistor as “switch” to: l Store charge l Charge or discharge l See next slide for circuit, hydraulic analogy, and logical model. 88

DRAM ICs l Provide high storage capacity at low cost, it dominates the high-capacity memory applications, e. g : Primary RAM in computers l DRAM in many ways similar to SRAM except it must be periodically “refreshed” 89

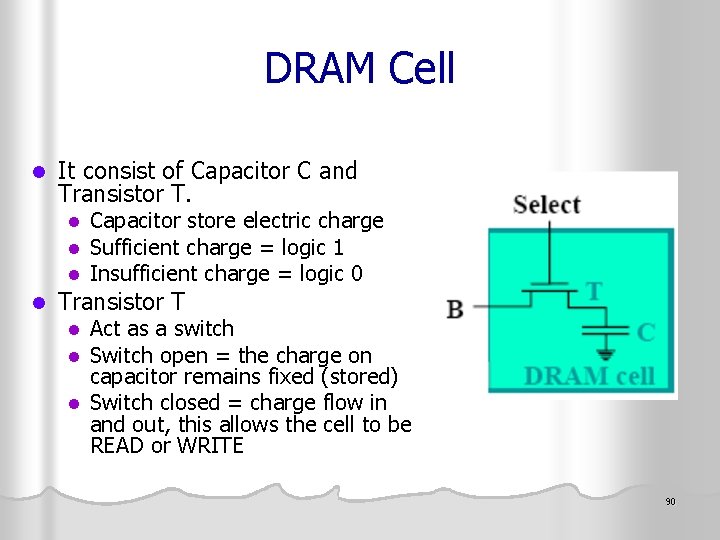

DRAM Cell l It consist of Capacitor C and Transistor T. l l Capacitor store electric charge Sufficient charge = logic 1 Insufficient charge = logic 0 Transistor T Act as a switch Switch open = the charge on capacitor remains fixed (stored) l Switch closed = charge flow in and out, this allows the cell to be READ or WRITE l l 90

Dynamic RAM (continued) Select T B Stored 0 Stored 1 To Pump C DRAM cell (b) (a) (c) Write 1 Write 0 Select B D Q C C (d) (e) Read 1 Read 0 DRAM cell model (h) (f) (g) 91

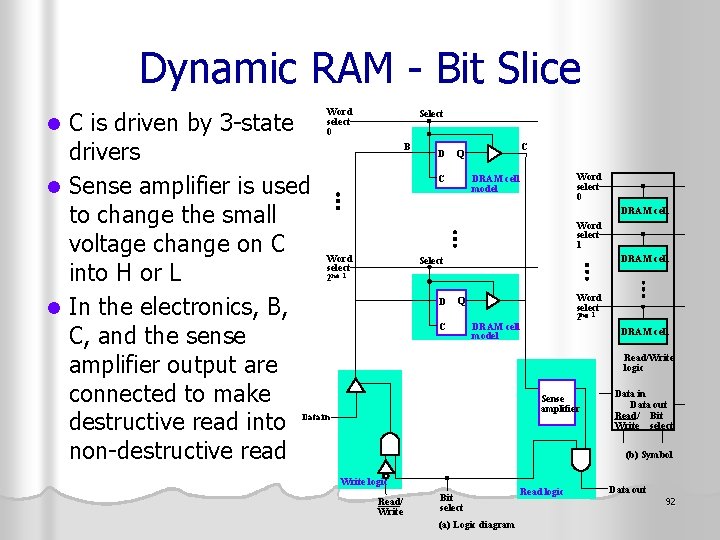

Dynamic RAM - Bit Slice C is driven by 3 -state drivers l Sense amplifier is used to change the small voltage change on C into H or L l In the electronics, B, C, and the sense amplifier output are connected to make destructive read into non-destructive read l Word select 0 Select B D C Q C Word select 0 DRAM cell model DRAM cell Word select 1 Word select 2 n 2 1 DRAM cell Select D Word select 2 n 2 1 Q C DRAM cell model DRAM cell Read/Write logic Sense amplifier Data in Data out Read/ Bit Write select (b) Symbol Write logic Read/ Write Bit select (a) Logic diagram Read logic Data out 92

Hydraulic Analogy for DRAM Cell (b) Small tank full = storing logic 1 (c) Small tank empty = storing logic 0 In this state the valve is closed 93

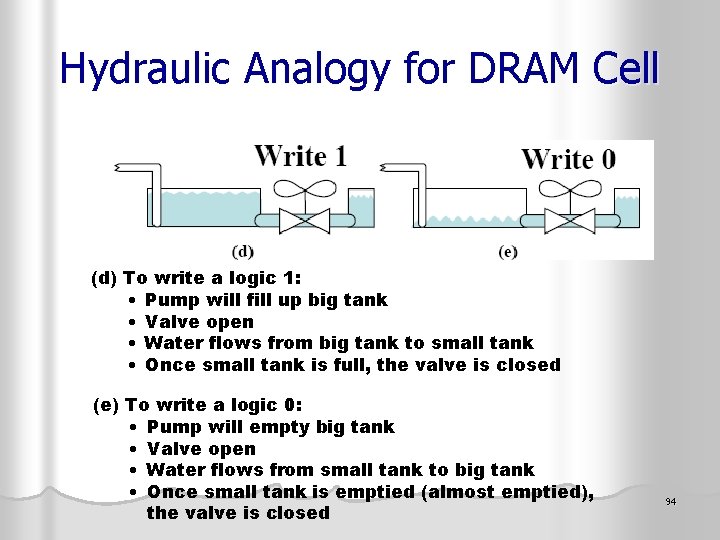

Hydraulic Analogy for DRAM Cell (d) To write a logic 1: • Pump will fill up big tank • Valve open • Water flows from big tank to small tank • Once small tank is full, the valve is closed (e) To write a logic 0: • Pump will empty big tank • Valve open • Water flows from small tank to big tank • Once small tank is emptied (almost emptied), the valve is closed 94

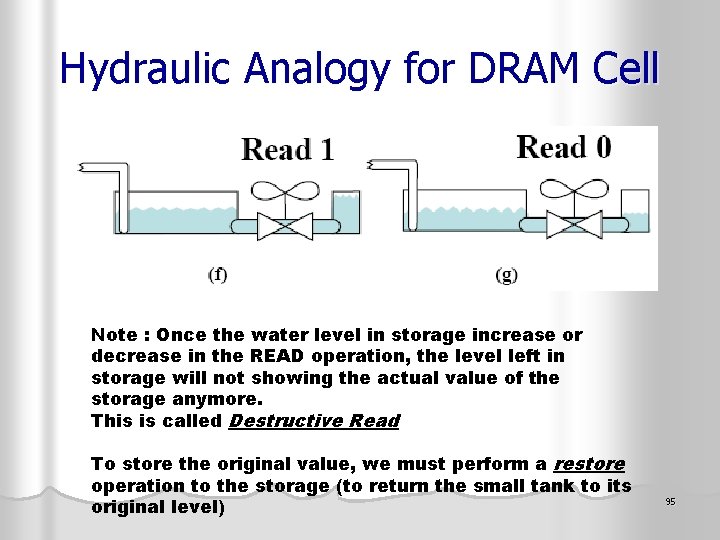

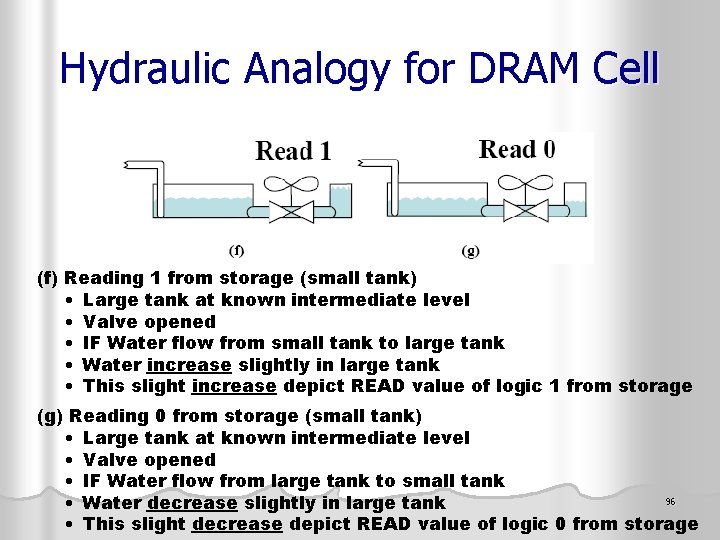

Hydraulic Analogy for DRAM Cell Note : Once the water level in storage increase or decrease in the READ operation, the level left in storage will not showing the actual value of the storage anymore. This is called Destructive Read To store the original value, we must perform a restore operation to the storage (to return the small tank to its original level) 95

Hydraulic Analogy for DRAM Cell (f) Reading 1 from storage (small tank) • Large tank at known intermediate level • Valve opened • IF Water flow from small tank to large tank • Water increase slightly in large tank • This slight increase depict READ value of logic 1 from storage (g) Reading 0 from storage (small tank) • Large tank at known intermediate level • Valve opened • IF Water flow from large tank to small tank 96 • Water decrease slightly in large tank • This slight decrease depict READ value of logic 0 from storage

Logic Model of DRAM Dynamic RAM cell circuit Logic Model of DRAM • In actual, there is another consideration for dynamic RAM. • The analogous leakage (due to the use of capacitors) • Due to this leaks, a full storage tank will eventually drain to a point which an increase in the level of the large tank on a READ operation cannot be observed. • To compensate, a refresh is needed. 97

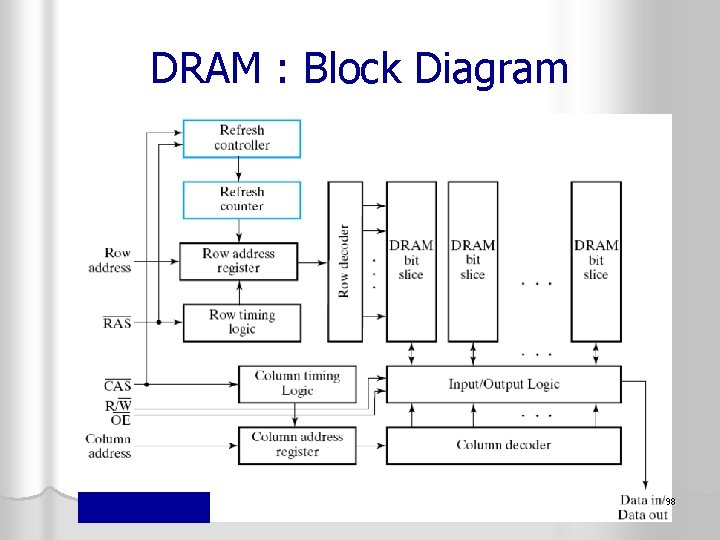

DRAM : Block Diagram 98

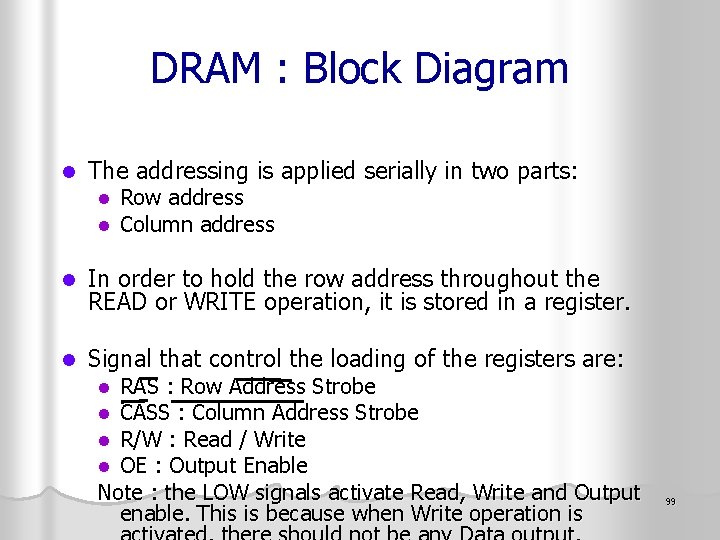

DRAM : Block Diagram l The addressing is applied serially in two parts: l l Row address Column address l In order to hold the row address throughout the READ or WRITE operation, it is stored in a register. l Signal that control the loading of the registers are: RAS : Row Address Strobe CASS : Column Address Strobe R/W : Read / Write OE : Output Enable Note : the LOW signals activate Read, Write and Output enable. This is because when Write operation is l l 99

DRAM : Block Diagram The refresh counter and refresh controller is used to control the refresh rate for the DRAM. l Typical refresh rate is between 16 to 64 milliseconds l 2 types of refresh: l Distributed refresh (more commonly used) l Burst refresh l 100

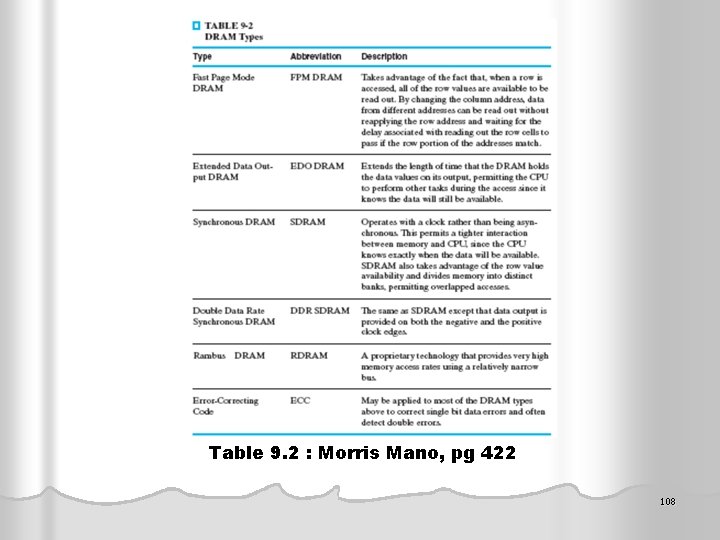

DRAM Types l l l FPM DRAM (Fast Page Mode DRAM) EDO DRAM (Extended Data Output DRAM) SDRAM (Synchronous DRAM) DDR SDRAM (Double Data Rate SDRAM) RDRAM (Rambus® DRAM) ECC (Error Correcting Code) 101

DRAM Types l Types to be discussed l Synchronous DRAM (SDRAM) l Double Data Rate SDRAM (DDR SDRAM) l RAMBUS® DRAM (RDRAM) l Justification for effectiveness of these types l DRAM often used as a part of a memory hierarchy (See details in chapter 14) l Reads from DRAM bring data into lower levels of the hierarchy l Transfers from DRAM involve multiple consecutively addressed words l Many words are internally read within the DRAM ICs using 102 a single row address and captured within the memory

DRAM Types (continued) l Justification for effectiveness of these types (continued) l These words are then transferred out over the memory data bus using a series of clocked transfers l These transfers have a low delay, so several can be done in a short time l The column address is captured and used by a synchronous counter within the DRAM to provide consecutive column addresses for the transfers l burst read – the resulting multiple word read from consecutive addresses 103

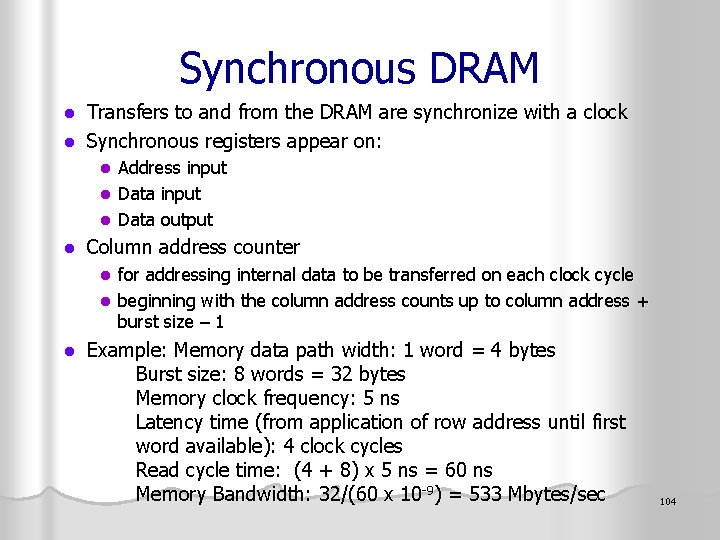

Synchronous DRAM Transfers to and from the DRAM are synchronize with a clock l Synchronous registers appear on: l Address input l Data output l l Column address counter for addressing internal data to be transferred on each clock cycle l beginning with the column address counts up to column address + burst size – 1 l l Example: Memory data path width: 1 word = 4 bytes Burst size: 8 words = 32 bytes Memory clock frequency: 5 ns Latency time (from application of row address until first word available): 4 clock cycles Read cycle time: (4 + 8) x 5 ns = 60 ns Memory Bandwidth: 32/(60 x 10 -9) = 533 Mbytes/sec 104

Double Data Rate Synchronous DRAM l Transfers data on both edges of the clock l Provides a transfer rate of 2 data words per clock cycle l Example: Same as for synchronous DRAM l Read cycle time = 60 ns l Memory Bandwidth: (2 x 32)/(60 x 10 -9) = 1. 066 Mbytes/sec 105

RAMBUS DRAM (RDRAM) Uses a packet-based bus for interaction between the RDRAM ICs and the memory bus to the processor l The bus consists of: l A 3 -bit row address bus l A 5 -bit column address bus l A 16 or 18 -bit (for error correction) data bus l The bus is synchronous and transfers on both edges of the clock l Packets are 4 -clock cycles long giving 8 transfers per packet representing: l A 12 -bit row address packet l A 20 -bit column address packet l A 128 or 144 -bit data packet l Multiple memory banks are used to permit concurrent memory accesses with different row addresses l The electronic design is sophisticated permitting very fast clock speeds 106 l

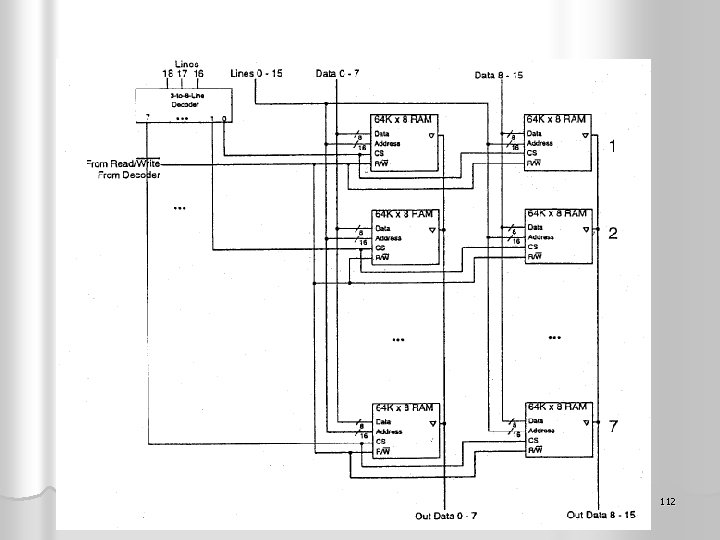

Arrays of DRAM Integrated Circuits l Similar to arrays of SRAM ICs, but there are differences typically handled by an IC called a DRAM controller: l Separation of the address into row address and column address and timing their application l Providing RAS and CAS and timing their application l Performing refresh operations at required intervals l Providing status signals to the rest of the system (e. g. , indicating whether or not the memory is active or is busy performing refresh) 107

Table 9. 2 : Morris Mano, pg 422 108

Construct these SRAM memory chips l A 512 K x 8 using 32 K x 8. l A 128 K x 16 using 128 K x 4. l A 512 K x 16 using 64 K x 8 l A 1024 K x 16 using 32 K x 8. 109

THANK YOU 110

111

112

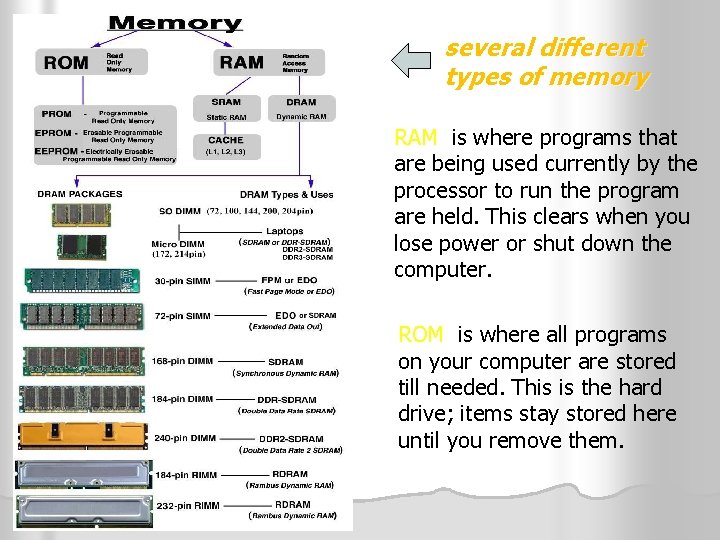

several different types of memory RAM is where programs that are being used currently by the processor to run the program are held. This clears when you lose power or shut down the computer. ROM is where all programs on your computer are stored till needed. This is the hard drive; items stay stored here until you remove them.

Fast-write memory targets low-cost black-box recorders June 29, 2011 // Julien Happich A system using STMicroelectronics' M 35 B 32 EEPROM is able to store a significant amount of vital information (2 Kbits) in less than one millisecond, and hence can react when the onset of a system failure or an accident is detected. In cases such as a power failure, this super-fast data storage can save the information needed to recover the system before the power supply voltage falls to an unusable level. Major applications for this high-speed memory include games, battery powered gadgets, utility meters, smart-grid equipment, industrial systems and medical devices. Compared to alternative non-volatile memories, the M 35 B 32 is about forty-times faster than a standard 32 -Kbit EEPROM and matches the write speed of Flash, says the manufacturer. Consuming approximately onetenth the energy of Flash, ST’s new memory allows designers to specify a voltage supply backup capacitor of one-tenth the size needed to operate the memory long enough to finish writing if system power is lost unexpectedly. This translates into significant savings both in cost and printed -circuit-board area. The M 35 B 32’s EEPROM technology also has cost and quality advantages compared to high-speed FRAM technology. The M 35 B 32 has a 32 -Kbit capacity, which is divided into two sectors for event recording and regular system EEPROM. The sector sizes are user adjustable to suit various application requirements. The large page size of 256 bytes allows a large amount of data to be written in a single page-write cycle and, when addressing the event recording sector, this information can be programmed in less than 1 ms. This enhances system performance and saves software overhead. The M 35 B 32 is accessed via a standard SPI serial connection, and so can be used as a direct replacement for standard SPI serial memories. The M 35 B 32 is in production now, in SO 8 N, 114 TSSOP 8 and FPN 2 x 3 mm compact surface-mount packages.

- Slides: 115