EMT 182 ANALOGUE ELECTRONICS I Basic Field Effect

EMT 182 ANALOGUE ELECTRONICS I Basic Field Effect Transistors Amplifiers

MOSFET AMPLIFIER q q Graphical Analysis, Load Lines Small-signal Parameters

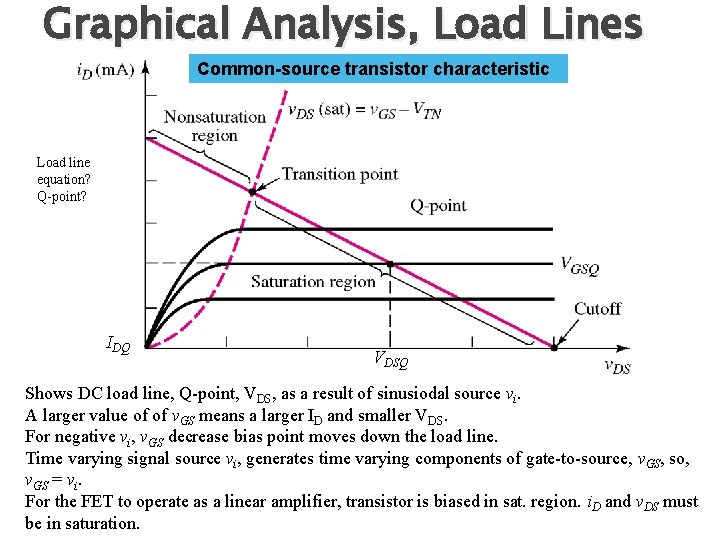

Graphical Analysis, Load Lines Common-source transistor characteristic Load line equation? Q-point? IDQ VDSQ Shows DC load line, Q-point, VDS, as a result of sinusiodal source vi. A larger value of of v. GS means a larger ID and smaller VDS. For negative vi, v. GS decrease bias point moves down the load line. Time varying signal source vi, generates time varying components of gate-to-source, v. GS, so, v. GS = vi. For the FET to operate as a linear amplifier, transistor is biased in sat. region. i. D and v. DS must be in saturation.

If VGS less than VTN, ID=0 (cut-off). If VGS > VTN, transistor turns-on and biased in sat. region. If VGS increases, Q-point moves up the load line. Transition points-boundary between sat. and non-sat. region, defined as VDS = VDS (sat) = VGS – VTN. As VGS increases above transition point, transistor biased in non-sat. region.

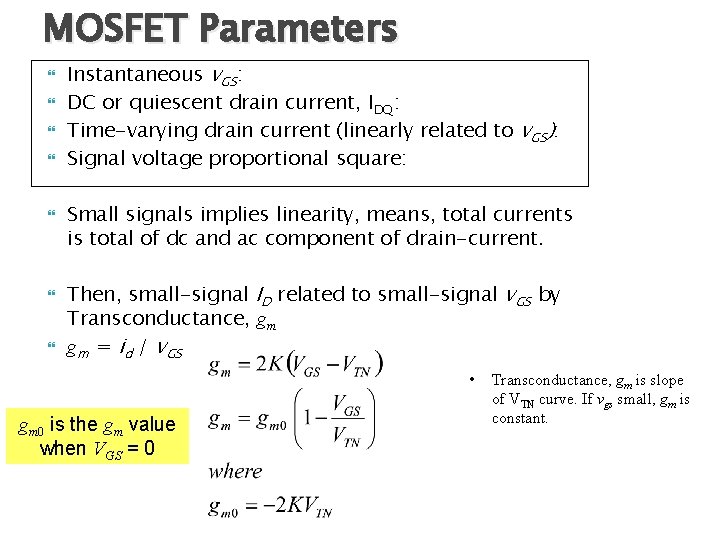

MOSFET Parameters Instantaneous v. GS: DC or quiescent drain current, IDQ: Time-varying drain current (linearly related to v. GS): Signal voltage proportional square: Small signals implies linearity, means, total currents is total of dc and ac component of drain-current. Then, small-signal ID related to small-signal v. GS by Transconductance, gm gm = id / v. GS • gm 0 is the gm value when VGS = 0 Transconductance, gm is slope of VTN curve. If vgs small, gm is constant.

Small-signal: linearize the ac equivalent circuit. Linear amplifier: the use of superposition so that the dc an ac analysis/signal of the circuits can be performed separately. Total response is the summation.

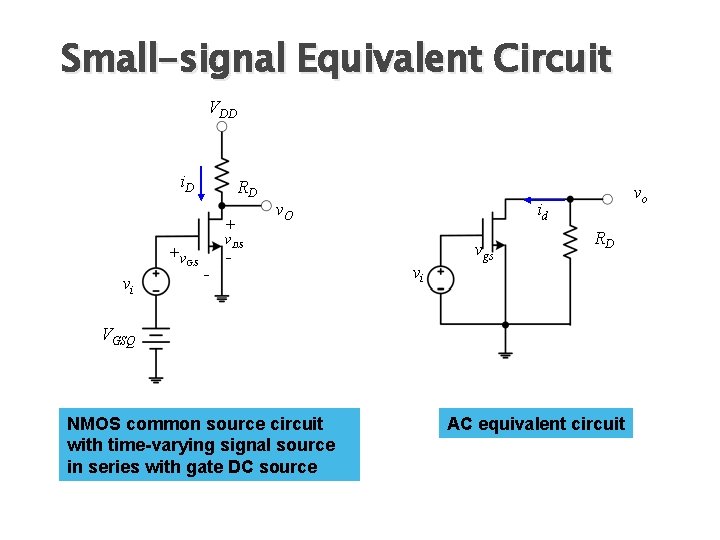

Small-signal Equivalent Circuit VDD i. D +v GS vi RD + v. DS - v. O - vo id vi vgs RD VGSQ NMOS common source circuit with time-varying signal source in series with gate DC source AC equivalent circuit

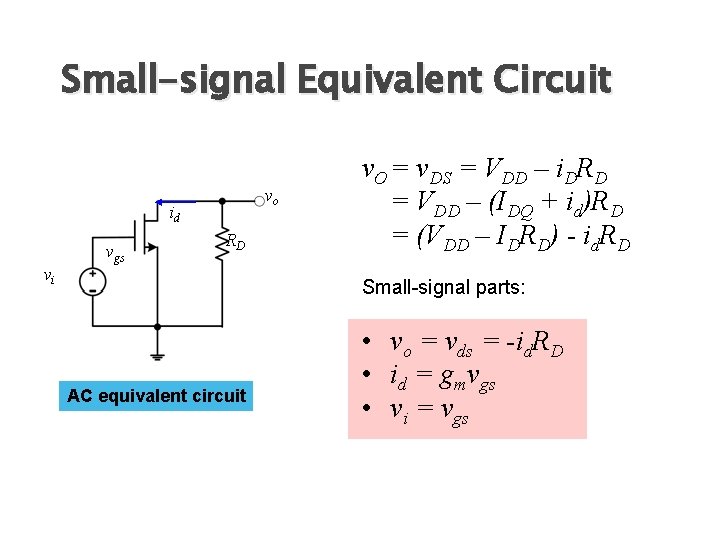

Small-signal Equivalent Circuit vo id vi vgs RD v. O = v. DS = VDD – i. DRD = VDD – (IDQ + id)RD = (VDD – IDRD) - id. RD Small-signal parts: AC equivalent circuit • vo = vds = -id. RD • id = gmvgs • vi = vgs

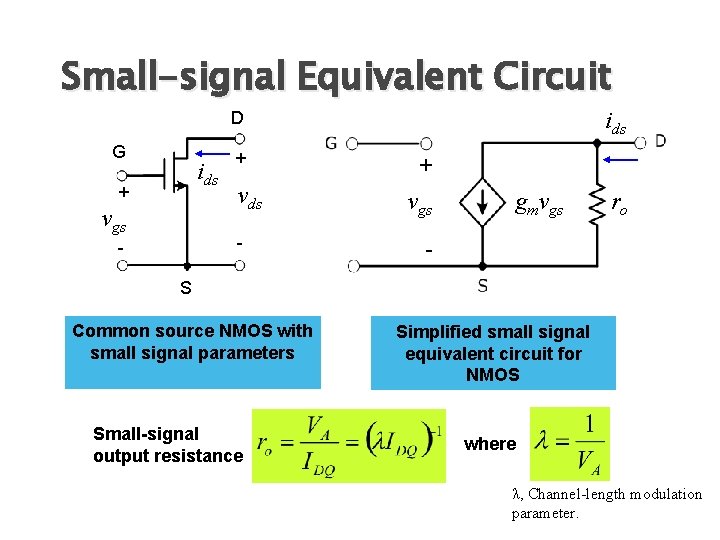

Small-signal Equivalent Circuit ids D G ids + vgs + vds - - + vgs gmvgs ro - S Common source NMOS with small signal parameters Small-signal output resistance Simplified small signal equivalent circuit for NMOS where λ, Channel-length modulation parameter.

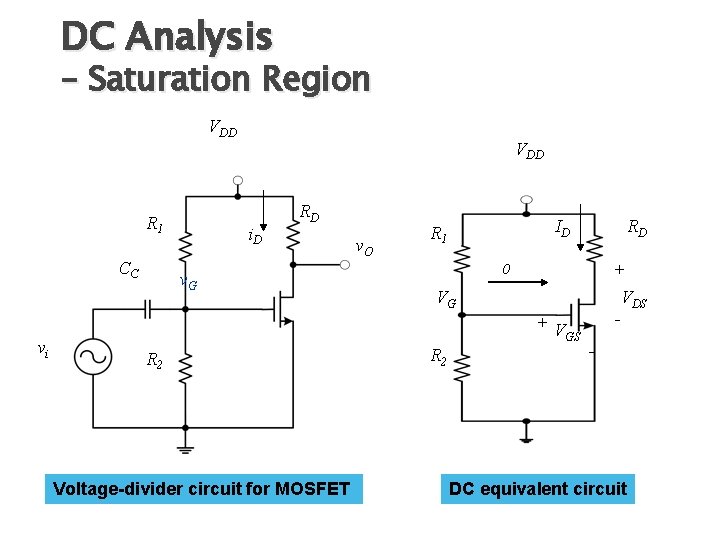

DC Analysis – Saturation Region VDD R 1 CC VDD i. D RD v. G v. O ID R 1 0 + VG VDS + vi R 2 Voltage-divider circuit for MOSFET RD R 2 - VGS - DC equivalent circuit

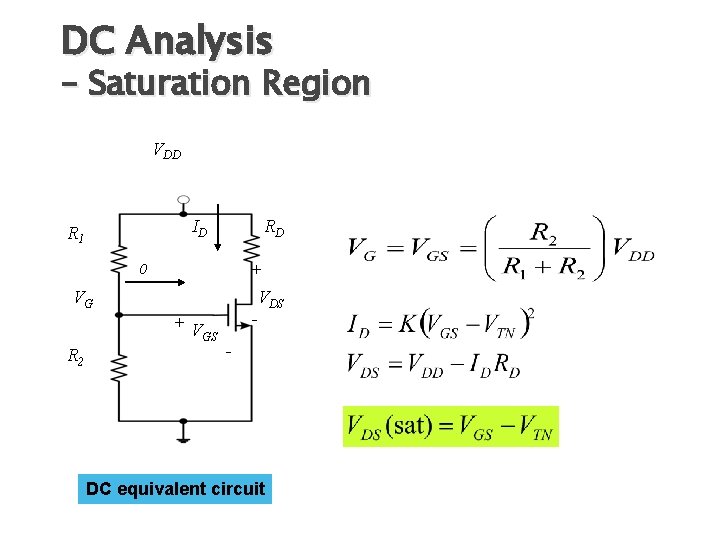

DC Analysis – Saturation Region VDD ID R 1 RD 0 + VG VDS + R 2 - VGS - DC equivalent circuit

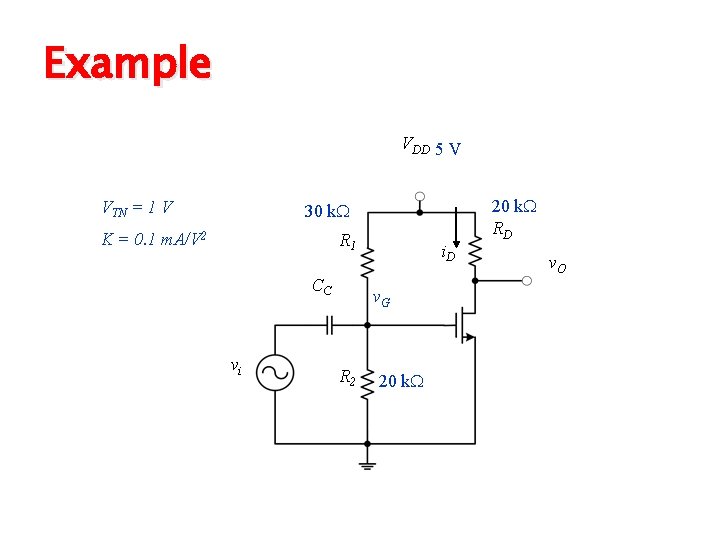

Example VDD 5 V VTN = 1 V 30 k K = 0. 1 m. A/V 2 R 1 CC vi i. D v. G R 2 20 k RD v. O

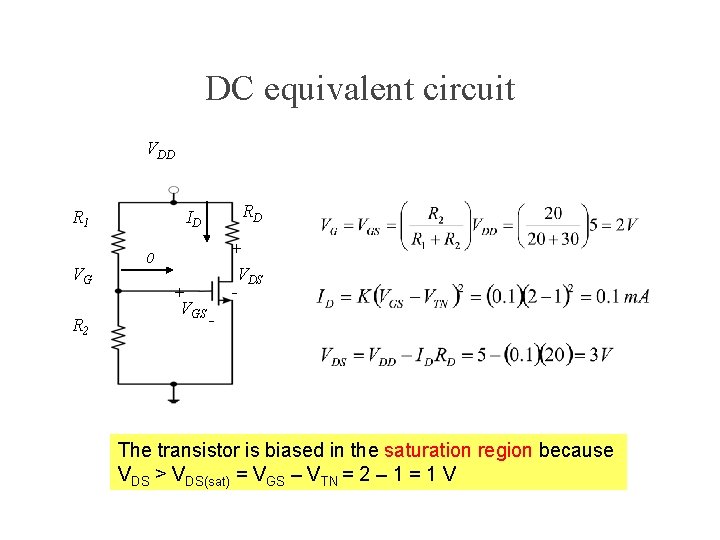

DC equivalent circuit VDD R 1 VG R 2 RD ID + 0 VDS + VGS - The transistor is biased in the saturation region because VDS > VDS(sat) = VGS – VTN = 2 – 1 = 1 V

MOSFET AMPLIFIER q Common-Source Amplifier q Equivalent circuit q With source resistor q With source bypass capacitor q q Common-Drain Amplifier Common-Gate Amplifier

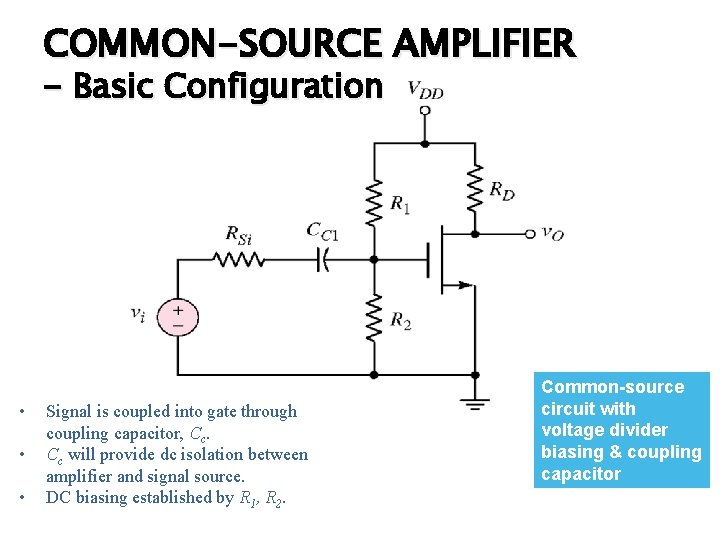

COMMON-SOURCE AMPLIFIER - Basic Configuration • • • Signal is coupled into gate through coupling capacitor, Cc. Cc will provide dc isolation between amplifier and signal source. DC biasing established by R 1, R 2. Common-source circuit with voltage divider biasing & coupling capacitor

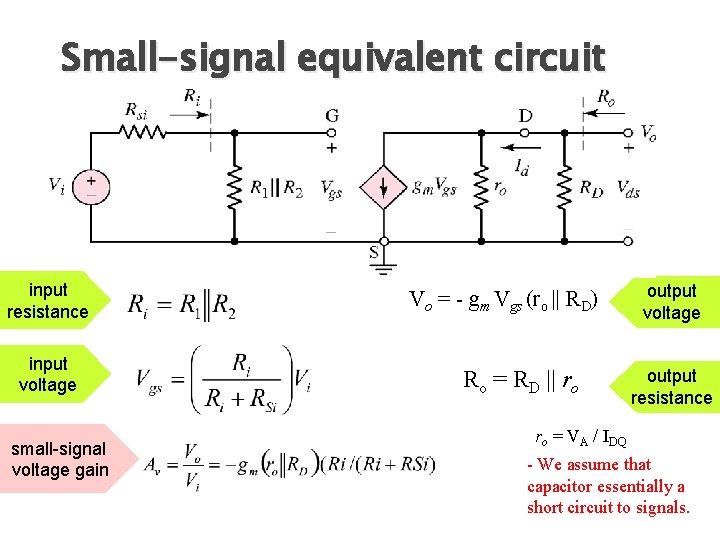

Small-signal equivalent circuit input resistance input voltage small-signal voltage gain Vo = - gm Vgs (ro || RD) Ro = RD || ro output voltage output resistance ro = VA / IDQ - We assume that capacitor essentially a short circuit to signals.

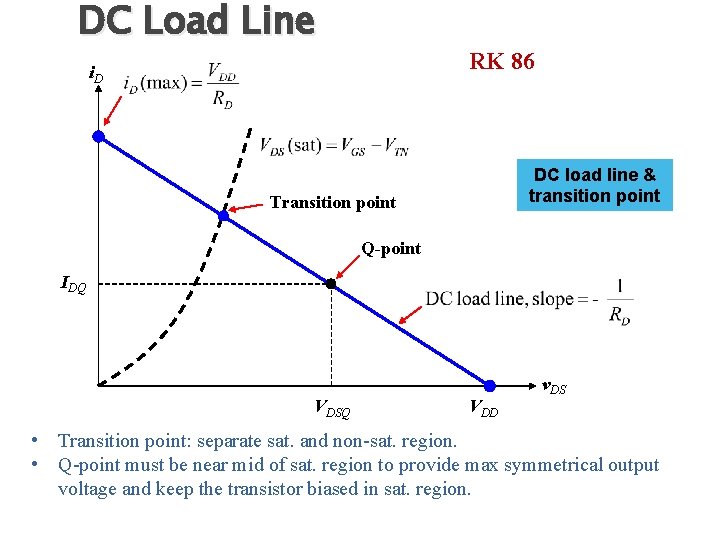

DC Load Line RK 86 i. D DC load line & transition point Transition point Q-point IDQ VDSQ VDD v. DS • Transition point: separate sat. and non-sat. region. • Q-point must be near mid of sat. region to provide max symmetrical output voltage and keep the transistor biased in sat. region.

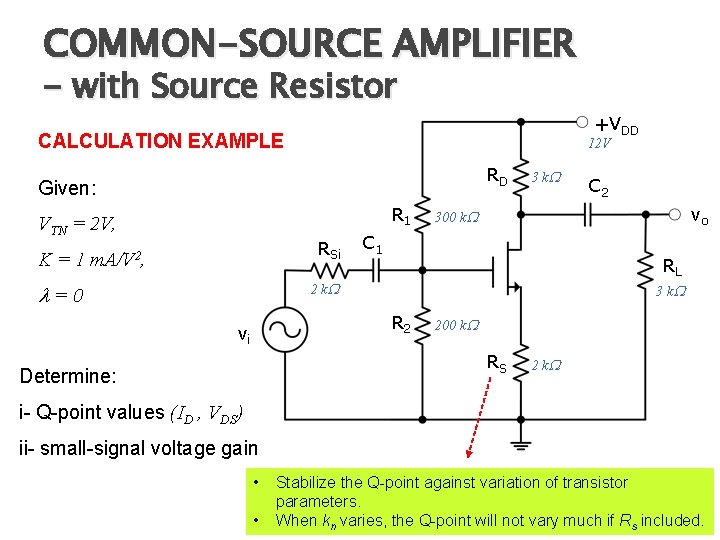

COMMON-SOURCE AMPLIFIER - with Source Resistor +VDD CALCULATION EXAMPLE 12 V RD Given: R 1 VTN = 2 V, K=1 RSi m. A/V 2, 3 k vo 300 k C 1 RL 2 k =0 3 k R 2 vi 200 k RS Determine: C 2 2 k i- Q-point values (ID , VDS) ii- small-signal voltage gain • • Stabilize the Q-point against variation of transistor parameters. When kn varies, the Q-point will not vary much if Rs included.

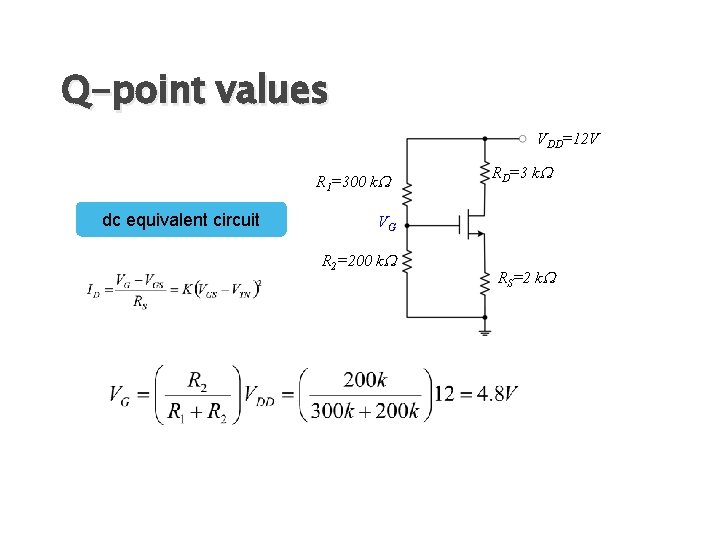

Q-point values VDD=12 V R 1=300 k dc equivalent circuit RD=3 k VG R 2=200 k RS=2 k

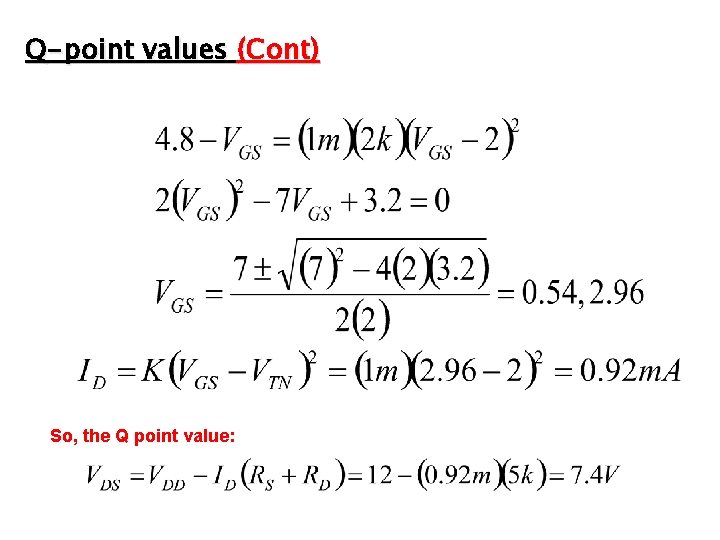

Q-point values (Cont) So, the Q point value:

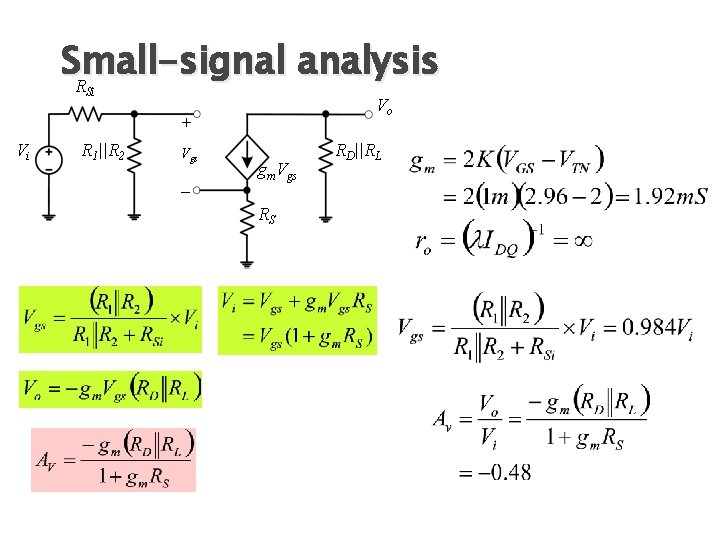

Small-signal analysis R Si Vo + Vi R 1||R 2 Vgs _ gm. Vgs RS RD||RL

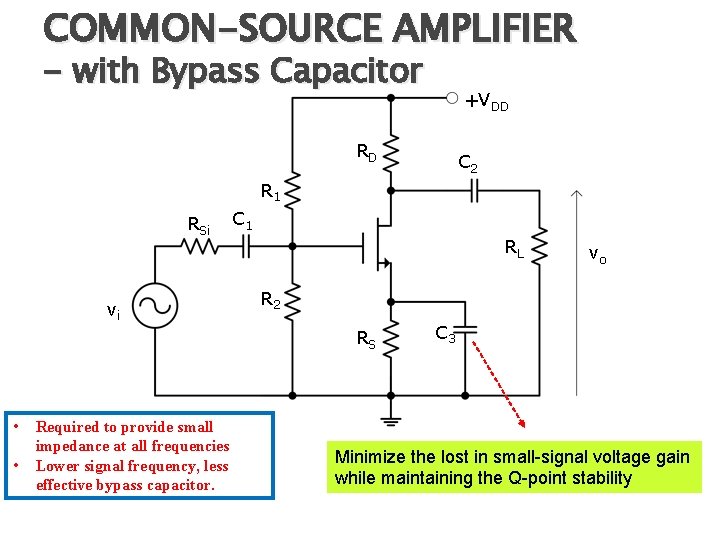

COMMON-SOURCE AMPLIFIER - with Bypass Capacitor +VDD RD C 2 R 1 RSi vi C 1 RL R 2 RS • • Required to provide small impedance at all frequencies Lower signal frequency, less effective bypass capacitor. vo C 3 Minimize the lost in small-signal voltage gain while maintaining the Q-point stability

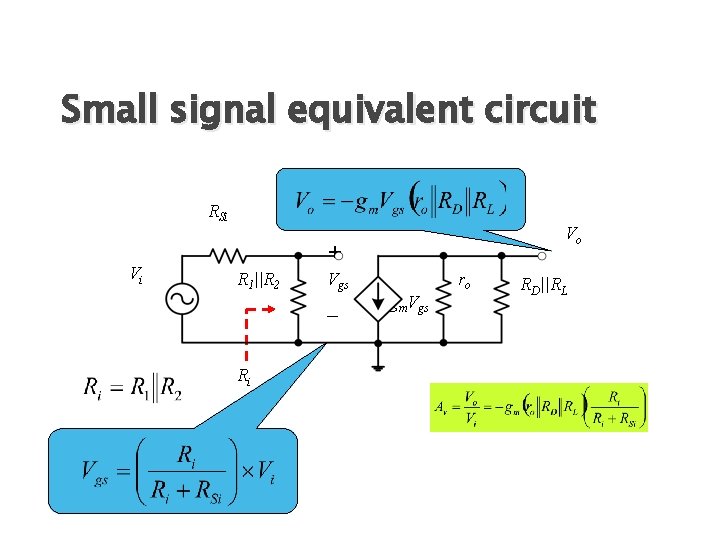

Small signal equivalent circuit RSi Vo + Vi R 1||R 2 Vgs _ Ri ro gm. Vgs RD||RL

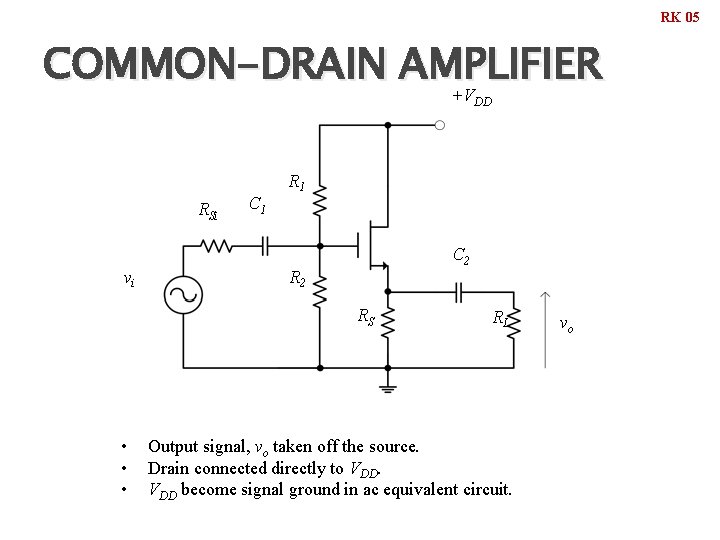

RK 05 COMMON-DRAIN AMPLIFIER +VDD RSi vi C 1 R 1 C 2 RS • • • RL Output signal, vo taken off the source. Drain connected directly to VDD become signal ground in ac equivalent circuit. vo

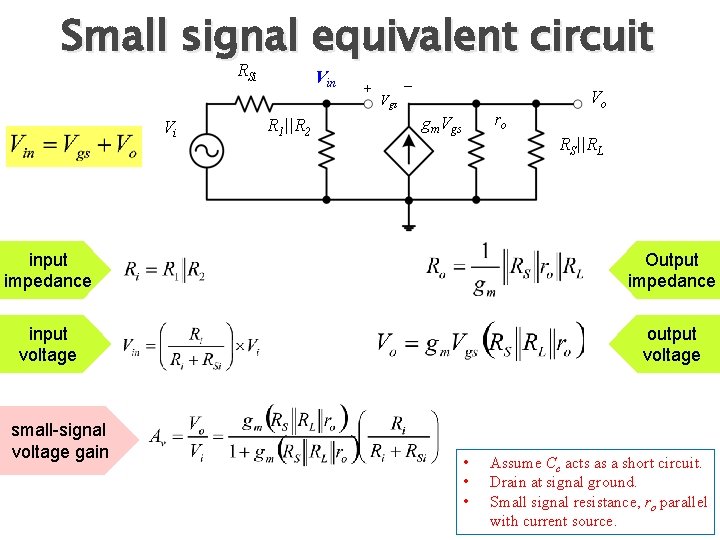

Small signal equivalent circuit RSi Vi Vin R 1||R 2 + _ Vgs ro gm. Vgs Vo RS||RL input impedance Output impedance input voltage output voltage small-signal voltage gain • • • Assume Cc acts as a short circuit. Drain at signal ground. Small signal resistance, ro parallel with current source.

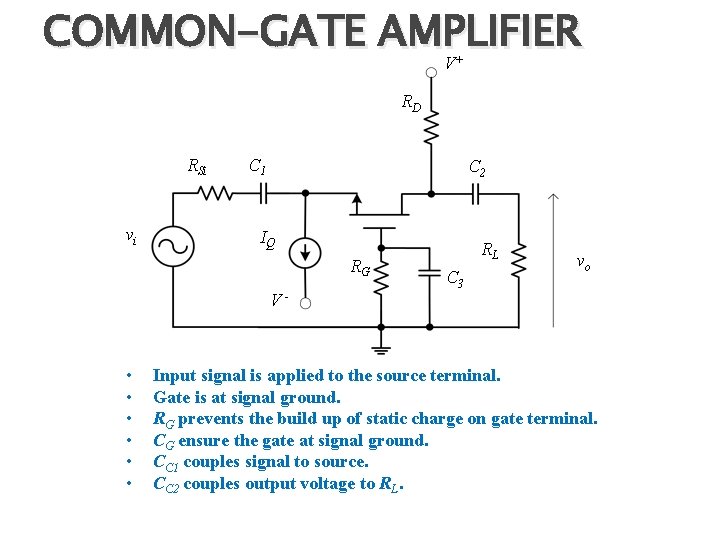

COMMON-GATE AMPLIFIER V+ RD RSi vi C 1 C 2 IQ RG V- • • • RL C 3 vo Input signal is applied to the source terminal. Gate is at signal ground. RG prevents the build up of static charge on gate terminal. CG ensure the gate at signal ground. CC 1 couples signal to source. CC 2 couples output voltage to RL.

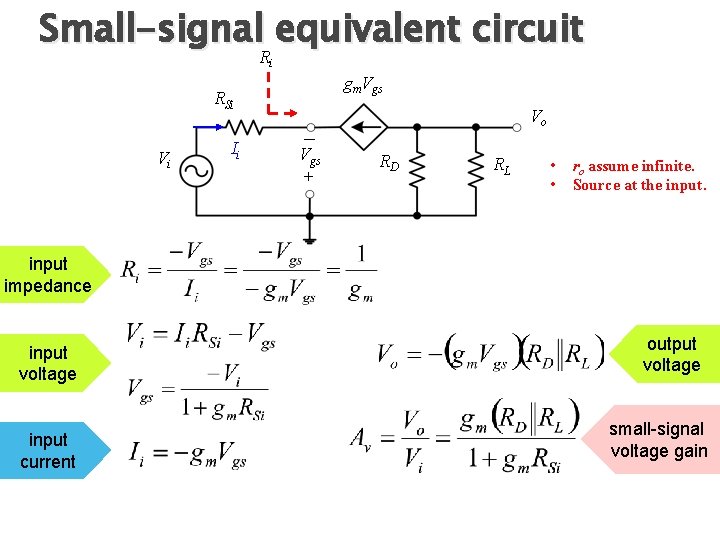

Small-signal equivalent circuit Ri gm. Vgs RSi Vi Ii _ Vgs + Vo RD RL • • ro assume infinite. Source at the input impedance input voltage input current output voltage small-signal voltage gain

- Slides: 27