EMITTERCOUPLED LOGIC INEL 4207 Differential Pair as basic

EMITTER-COUPLED LOGIC INEL 4207

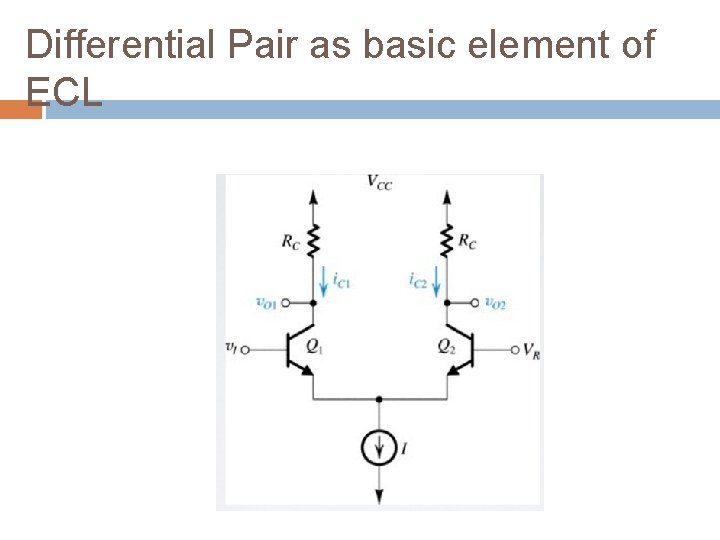

Differential Pair as basic element of ECL

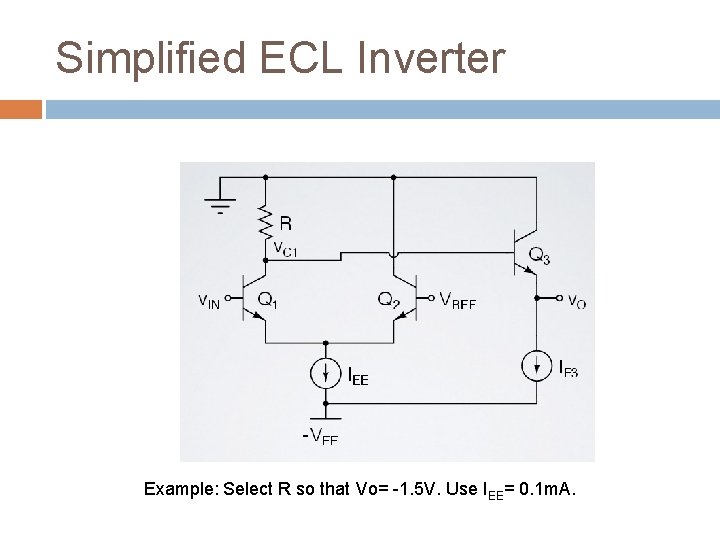

Simplified ECL Inverter Example: Select R so that Vo= -1. 5 V. Use IEE= 0. 1 m. A.

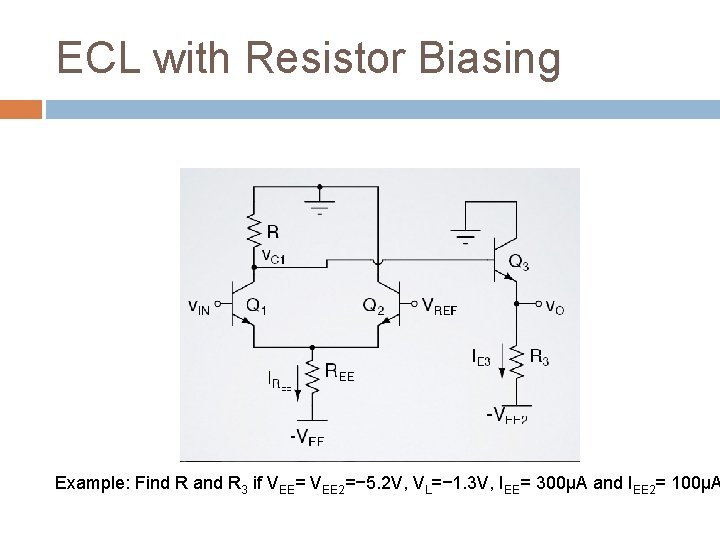

ECL with Resistor Biasing Example: Find R and R 3 if VEE= VEE 2=− 5. 2 V, VL=− 1. 3 V, IEE= 300μA and IEE 2= 100μA

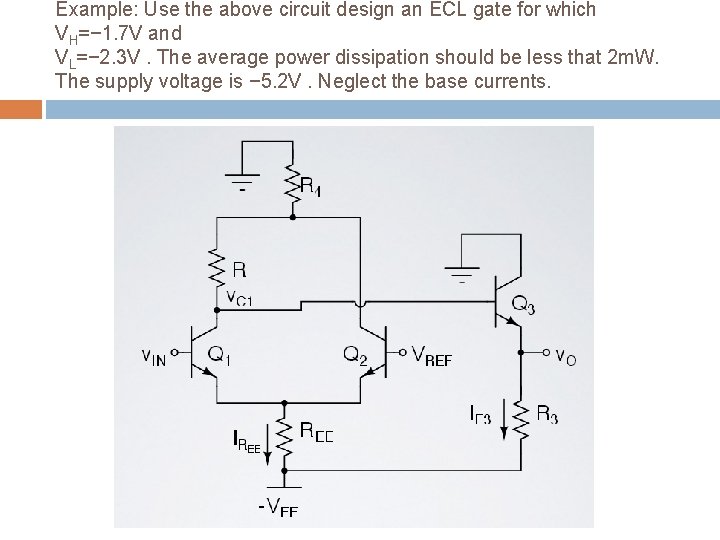

Example: Use the above circuit design an ECL gate for which VH=− 1. 7 V and VL=− 2. 3 V. The average power dissipation should be less that 2 m. W. The supply voltage is − 5. 2 V. Neglect the base currents.

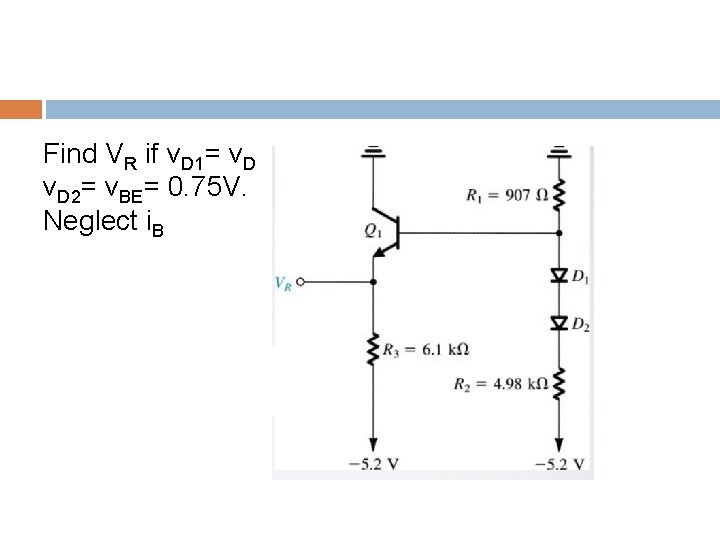

Find VR if v. D 1= v. D 2= v. BE= 0. 75 V. Neglect i. B

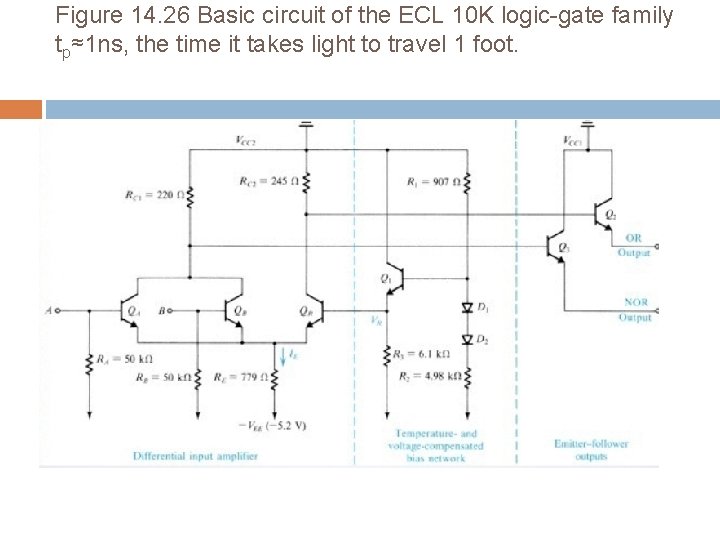

Figure 14. 26 Basic circuit of the ECL 10 K logic-gate family tp≈1 ns, the time it takes light to travel 1 foot.

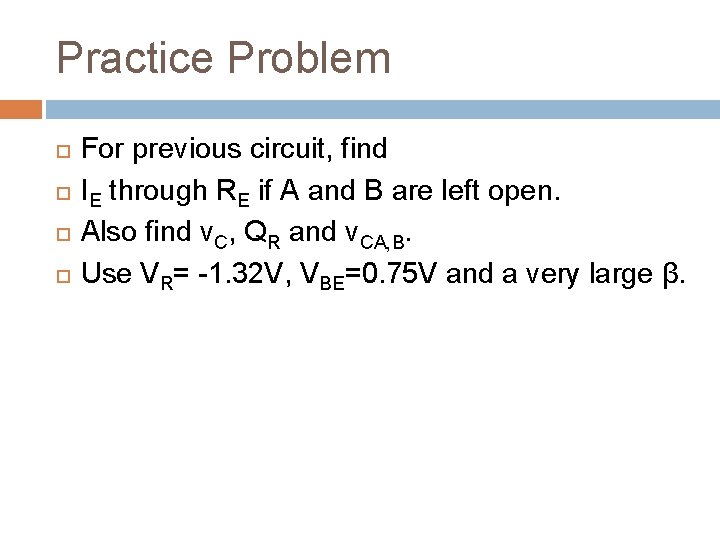

Practice Problem For previous circuit, find IE through RE if A and B are left open. Also find v. C, QR and v. CA, B. Use VR= -1. 32 V, VBE=0. 75 V and a very large β.

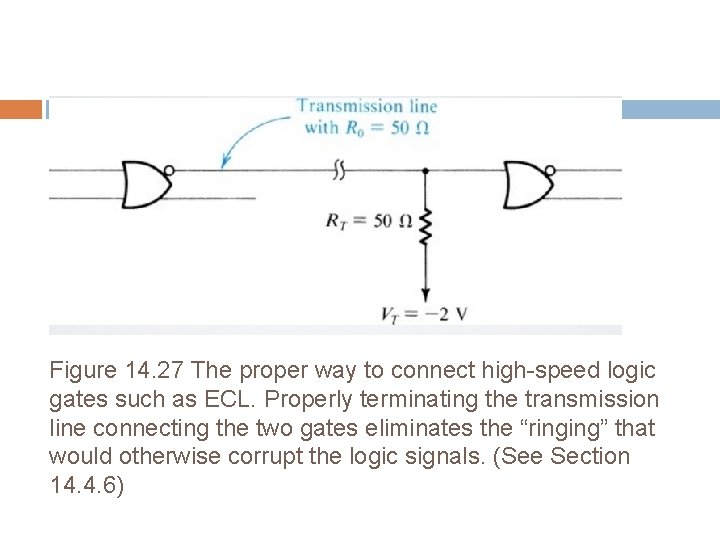

Figure 14. 27 The proper way to connect high-speed logic gates such as ECL. Properly terminating the transmission line connecting the two gates eliminates the “ringing” that would otherwise corrupt the logic signals. (See Section 14. 4. 6)

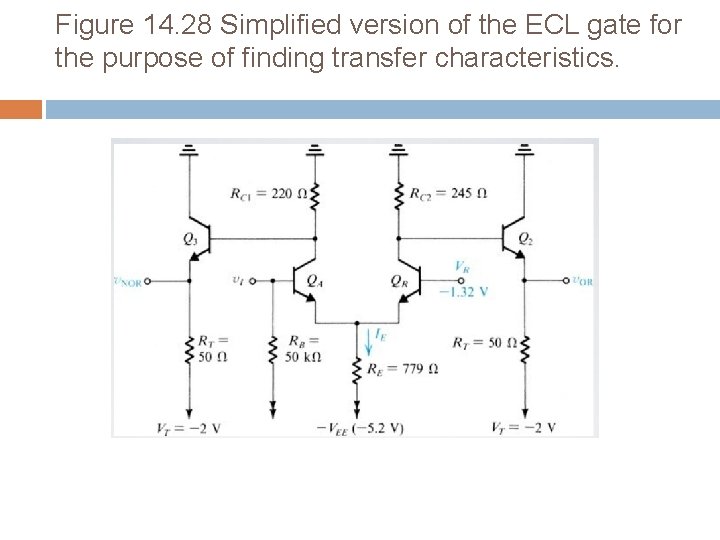

Figure 14. 28 Simplified version of the ECL gate for the purpose of finding transfer characteristics.

Practice Problems Find VOL and VOH (neglect i. C of QR) if β=100. Then find NMH and NML if VIL and VIH are defined as the conditions for which IE, IEQA= 99% of IE when VI=VIH and IEQA=1% when VI=VIL

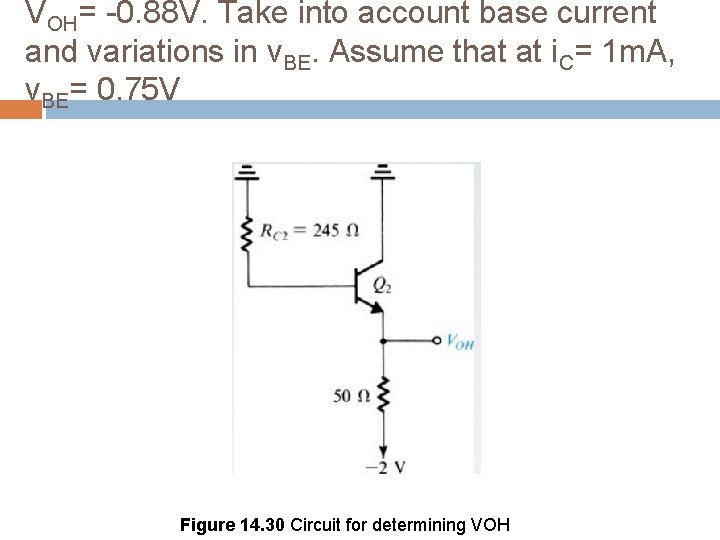

VOH= -0. 88 V. Take into account base current and variations in v. BE. Assume that at i. C= 1 m. A, v. BE= 0. 75 V Figure 14. 30 Circuit for determining VOH

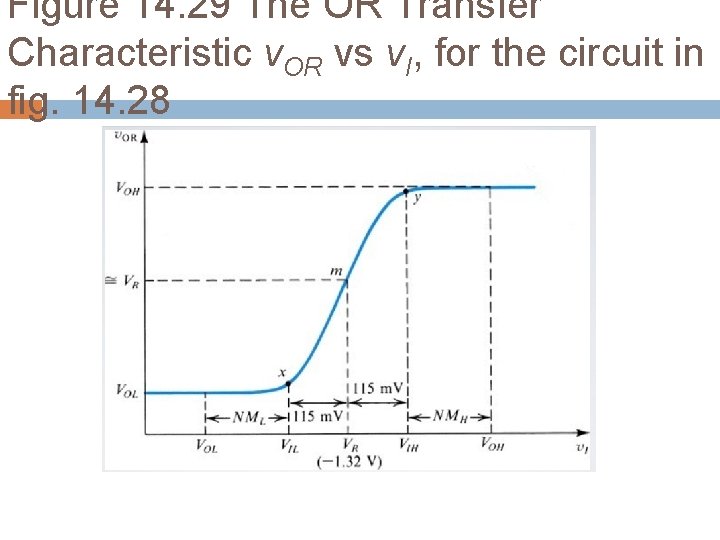

Figure 14. 29 The OR Transfer Characteristic v. OR vs v. I, for the circuit in fig. 14. 28

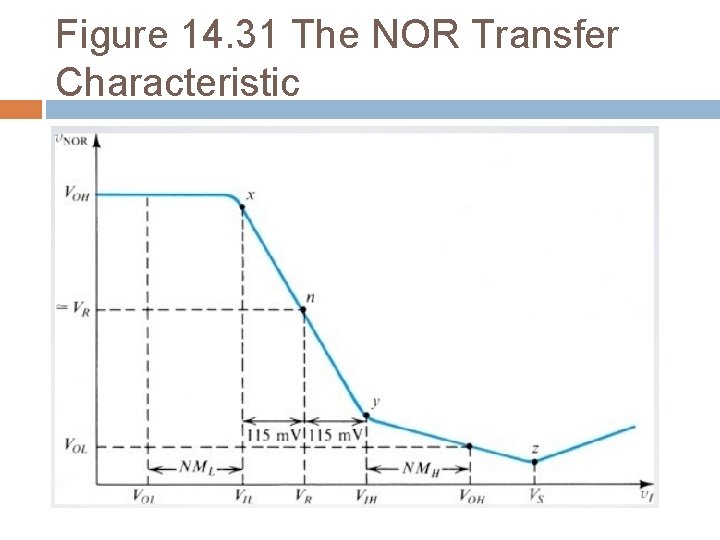

Figure 14. 31 The NOR Transfer Characteristic

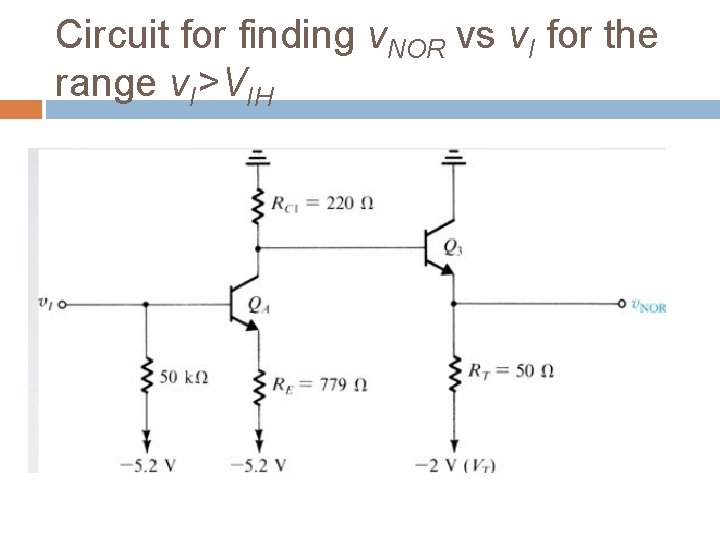

Circuit for finding v. NOR vs v. I for the range v. I>VIH

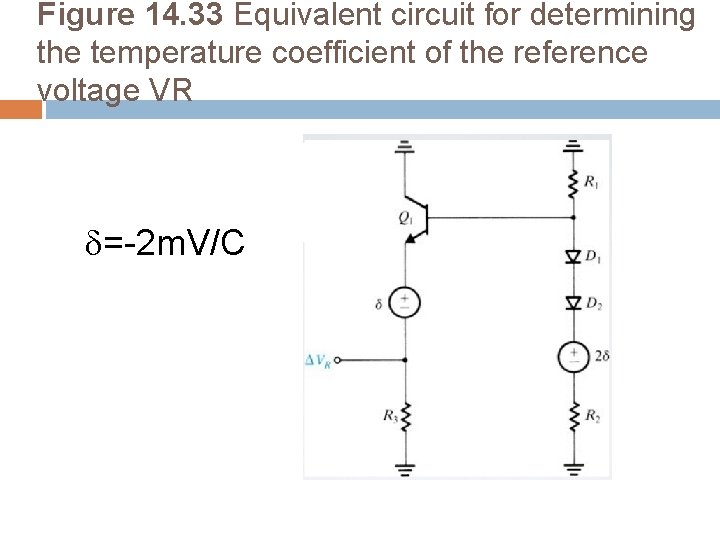

Figure 14. 33 Equivalent circuit for determining the temperature coefficient of the reference voltage VR d=-2 m. V/C

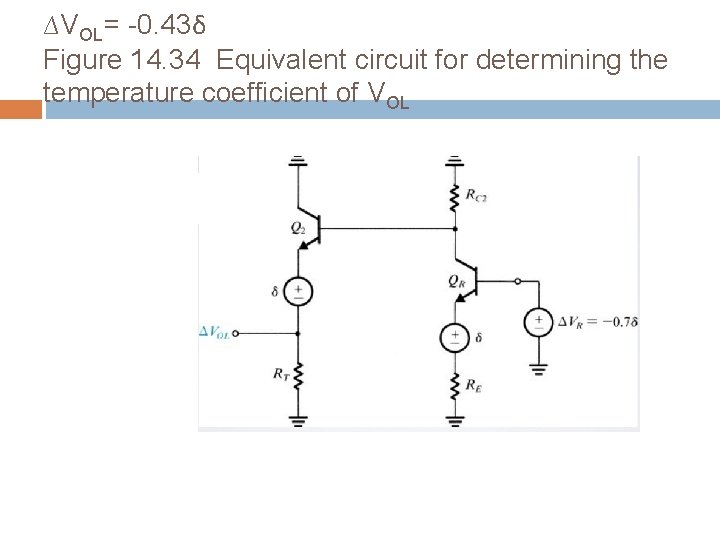

∆VOL= -0. 43δ Figure 14. 34 Equivalent circuit for determining the temperature coefficient of VOL

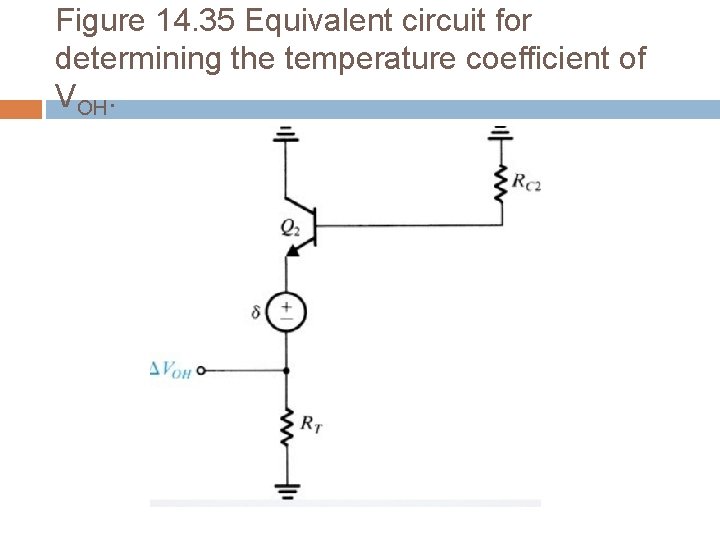

Figure 14. 35 Equivalent circuit for determining the temperature coefficient of VOH.

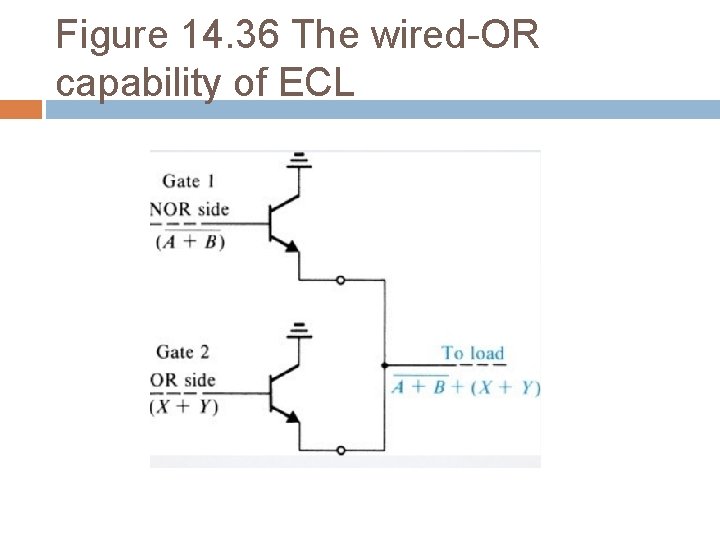

Figure 14. 36 The wired-OR capability of ECL

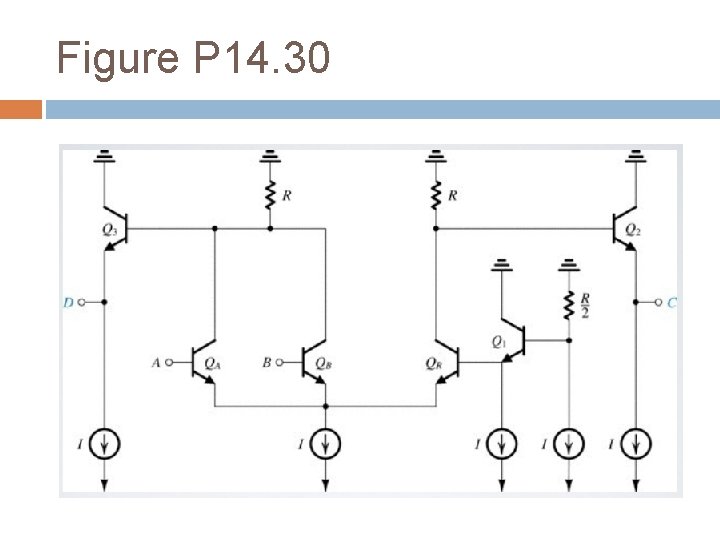

Figure P 14. 30

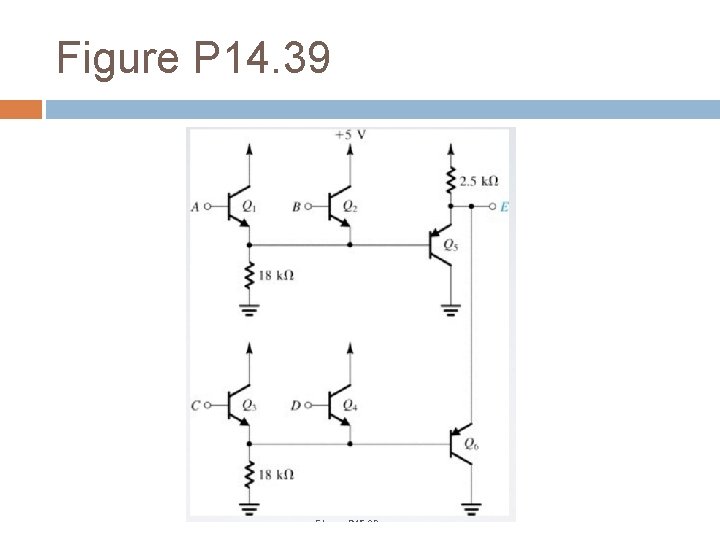

Figure P 14. 39

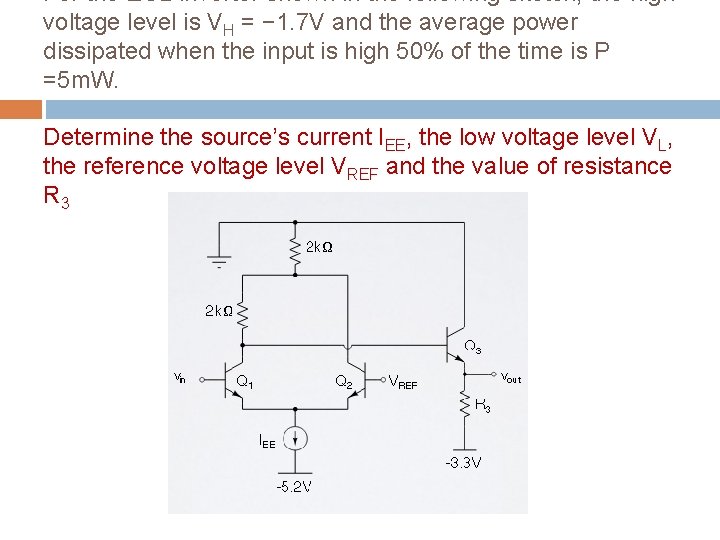

For the ECL inverter shown in the following sketch, the high voltage level is VH = − 1. 7 V and the average power dissipated when the input is high 50% of the time is P =5 m. W. Determine the source’s current IEE, the low voltage level VL, the reference voltage level VREF and the value of resistance R 3

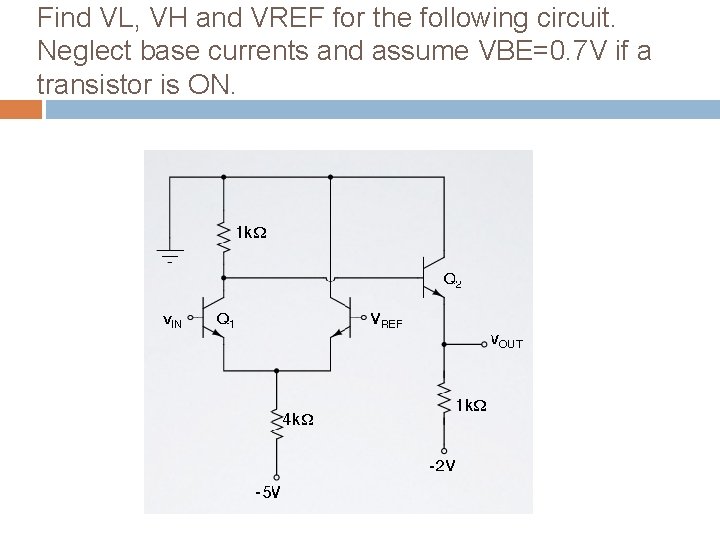

Find VL, VH and VREF for the following circuit. Neglect base currents and assume VBE=0. 7 V if a transistor is ON.

- Slides: 23