Emerging Standards in the Electronic Design Automation EDA

- Slides: 9

Emerging Standards in the Electronic Design Automation (EDA) Industry Phil Fisher (SEMATECH) Don Cottrell (Si 2) UC Berkeley October 20, 1999

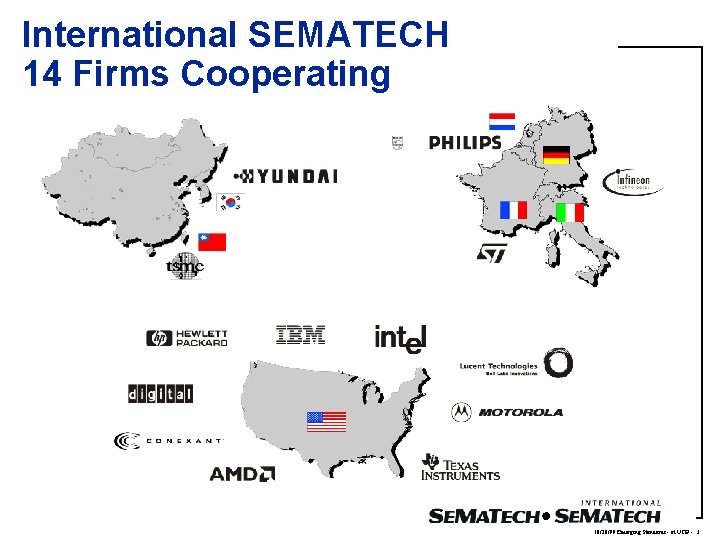

SEMATECH/International SEMATECH • 14 global semiconductor companies: AMD Intel Conexant Lucent Technologies Compaq (Digital) Motorola Hewlett-Packard Philips Hyundai STMicroelectronics IBM Texas Instruments Infineon Technologies TSMC • Mission: The members of International SEMATECH will gain a manufacturing advantage through cooperative work on semiconductor manufacturing technology • Technical programs cover a broad range of advanced and tactical projects, focusing on wafer processing 10/20/99 Emerging Standards - at UCB - 2

International SEMATECH 14 Firms Cooperating 10/20/99 Emerging Standards - at UCB - 3

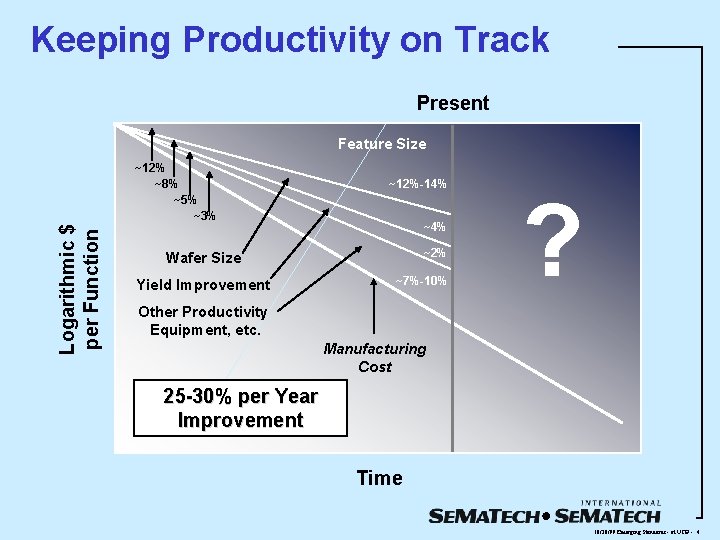

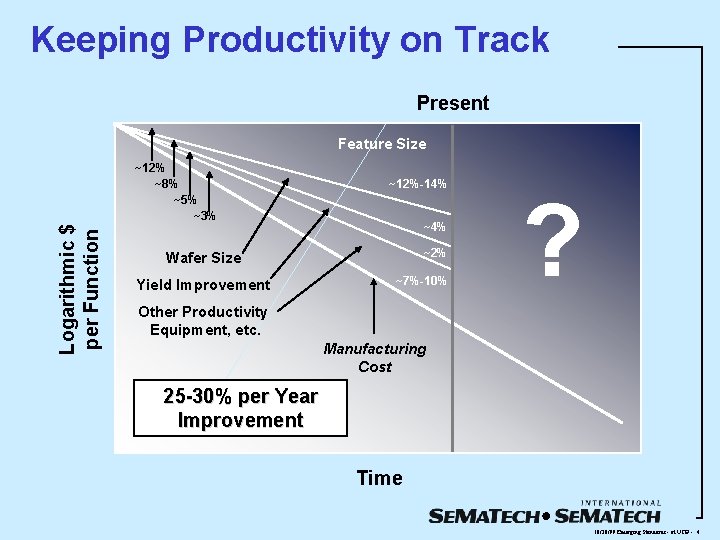

Keeping Productivity on Track Present Feature Size Logarithmic $ per Function ~12% ~8% ~5% ~3% ~12%-14% ~2% Wafer Size Yield Improvement ~7%-10% ? Other Productivity Equipment, etc. Manufacturing Cost 25 -30% per Year Improvement Time 10/20/99 Emerging Standards - at UCB - 4

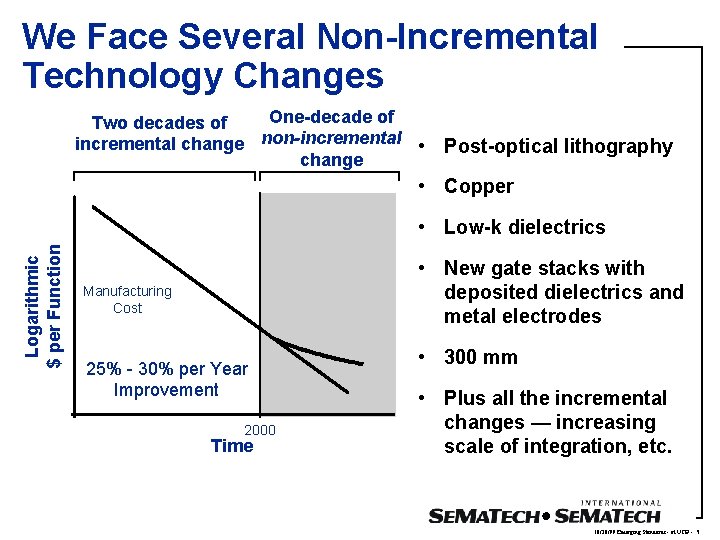

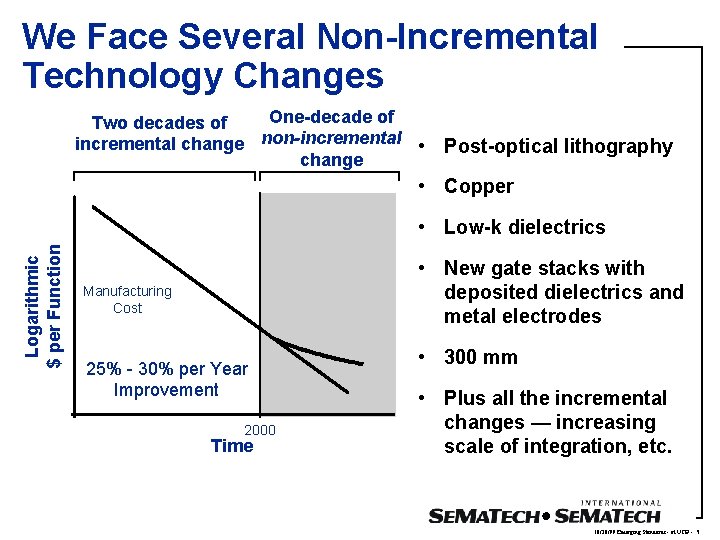

We Face Several Non-Incremental Technology Changes One-decade of Two decades of incremental change non-incremental • change Post-optical lithography • Copper Logarithmic $ per Function • Low-k dielectrics • New gate stacks with deposited dielectrics and metal electrodes Manufacturing Cost 25% - 30% per Year Improvement 2000 Time • 300 mm • Plus all the incremental changes — increasing scale of integration, etc. 10/20/99 Emerging Standards - at UCB - 5

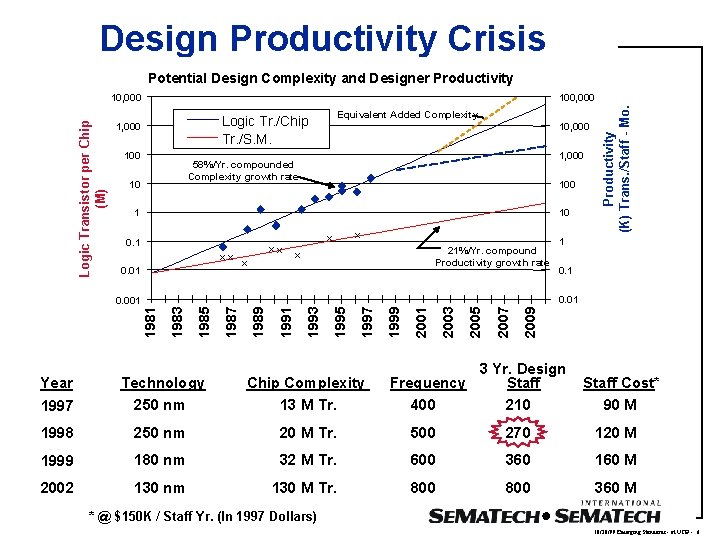

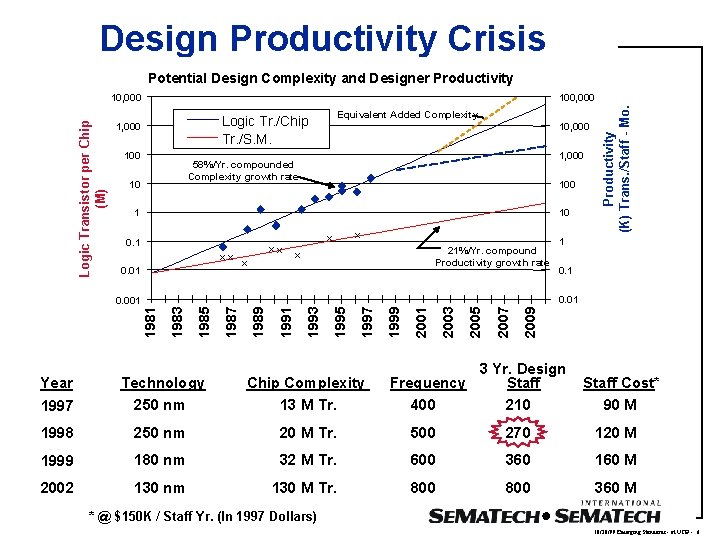

Design Productivity Crisis Potential Design Complexity and Designer Productivity 100, 000, 000 Logic Transistor per Chip (M) Equivalent Added Complexity Logic Tr. /Chip Tr. /S. M. 1, 000, 000 100, 000 10, 000 1, 000, 000 58%/Yr. compounded Complexity growth rate 10, 00010 100, 000 1, 0001 x x 2009 2007 2005 2001 1999 1997 1995 2003 21%/Yr. compound Productivity growth rate x 1993 x 1991 1987 1985 1983 1981 xx 1989 xx 0. 01 10 0. 001 1 Year 10 10, 000 0. 1 100 Productivity (K) Trans. /Staff - Mo. 10, 000, 000 1 1, 000 0. 1 100 0. 01 10 3 Yr. Design Frequency Staff 400 210 1997 Technology 250 nm Chip Complexity 13 M Tr. Staff Cost* 90 M 1998 250 nm 20 M Tr. 500 270 120 M 1999 180 nm 32 M Tr. 600 360 160 M 2002 130 nm 130 M Tr. 800 360 M * @ $150 K / Staff Yr. (In 1997 Dollars) 10/20/99 Emerging Standards - at UCB - 6

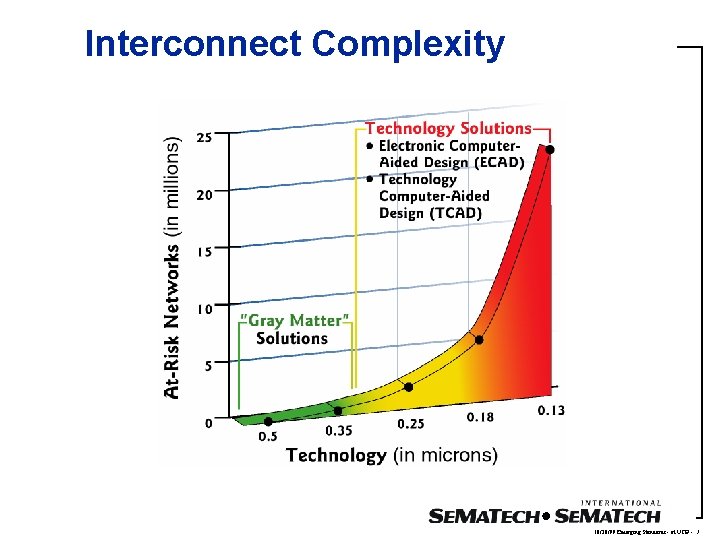

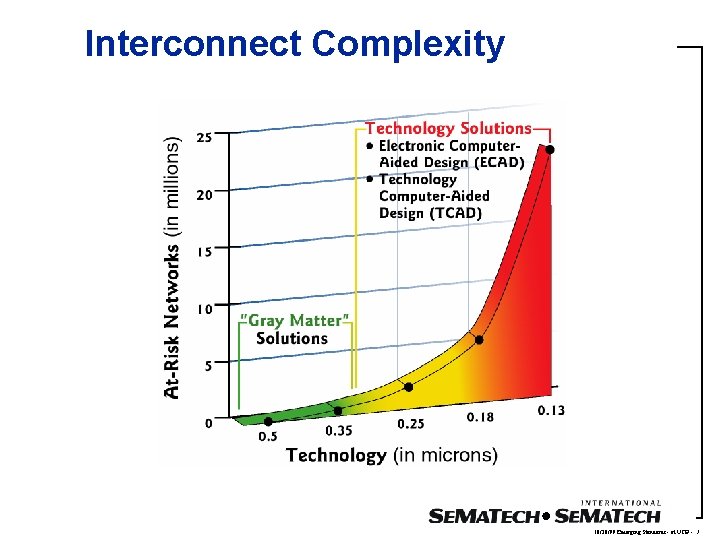

Interconnect Complexity 10/20/99 Emerging Standards - at UCB - 7

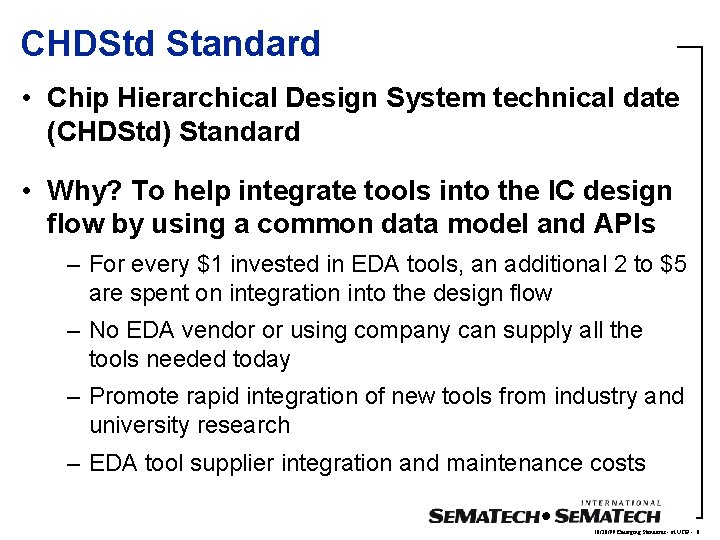

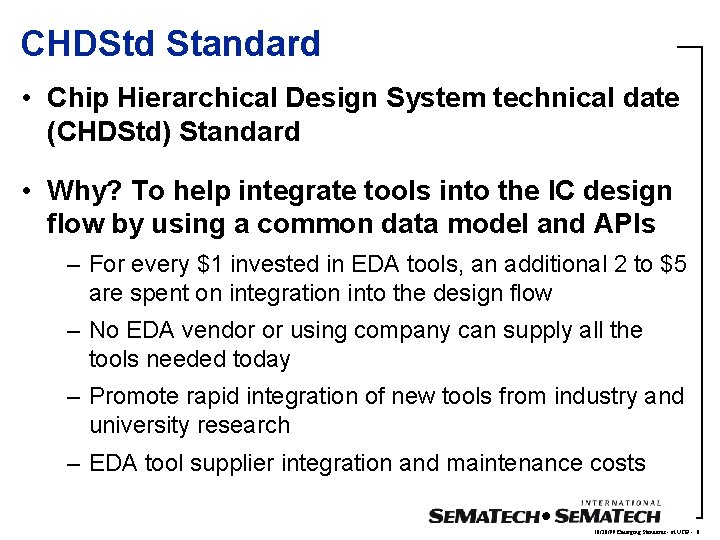

CHDStd Standard • Chip Hierarchical Design System technical date (CHDStd) Standard • Why? To help integrate tools into the IC design flow by using a common data model and APIs – For every $1 invested in EDA tools, an additional 2 to $5 are spent on integration into the design flow – No EDA vendor or using company can supply all the tools needed today – Promote rapid integration of new tools from industry and university research – EDA tool supplier integration and maintenance costs 10/20/99 Emerging Standards - at UCB - 8

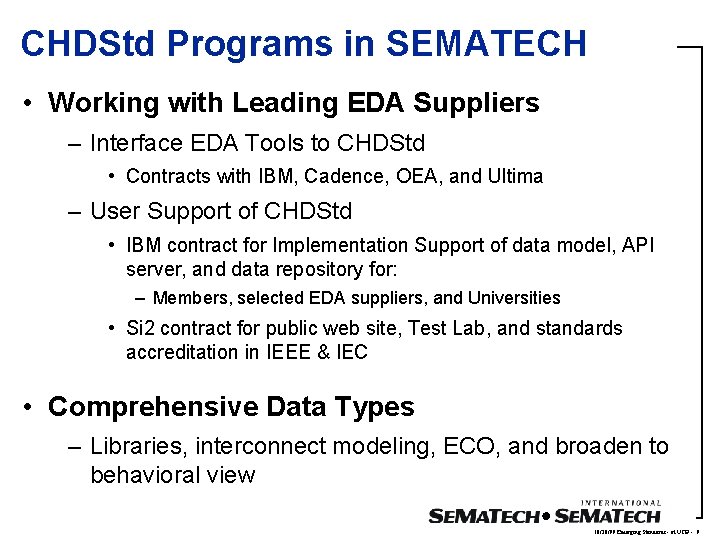

CHDStd Programs in SEMATECH • Working with Leading EDA Suppliers – Interface EDA Tools to CHDStd • Contracts with IBM, Cadence, OEA, and Ultima – User Support of CHDStd • IBM contract for Implementation Support of data model, API server, and data repository for: – Members, selected EDA suppliers, and Universities • Si 2 contract for public web site, Test Lab, and standards accreditation in IEEE & IEC • Comprehensive Data Types – Libraries, interconnect modeling, ECO, and broaden to behavioral view 10/20/99 Emerging Standards - at UCB - 9