Embedded Systems Modeling Simulation and Exploration Andy D

Embedded Systems: Modeling, Simulation, and Exploration Andy D. Pimentel System and Network Engineering (SNE) group University of Amsterdam System and Network Engineering, Andy D. Pimentel

Embedded Systems are ubiquitous! System and Network Engineering, Andy D. Pimentel 2

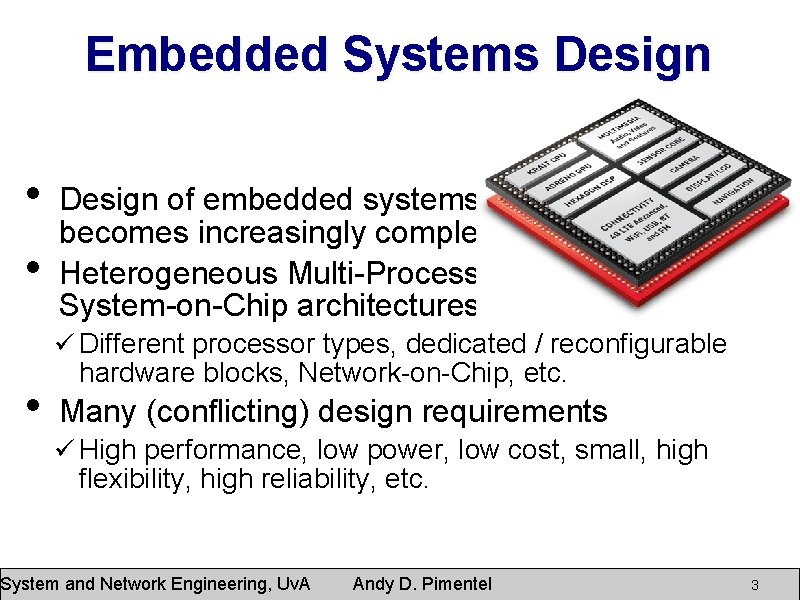

Embedded Systems Design • • Design of embedded systems becomes increasingly complex Heterogeneous Multi-Processor System-on-Chip architectures ü Different processor types, dedicated / reconfigurable • hardware blocks, Network-on-Chip, etc. Many (conflicting) design requirements ü High performance, low power, low cost, small, high flexibility, high reliability, etc. System and Network Engineering, Uv. A Andy D. Pimentel 3

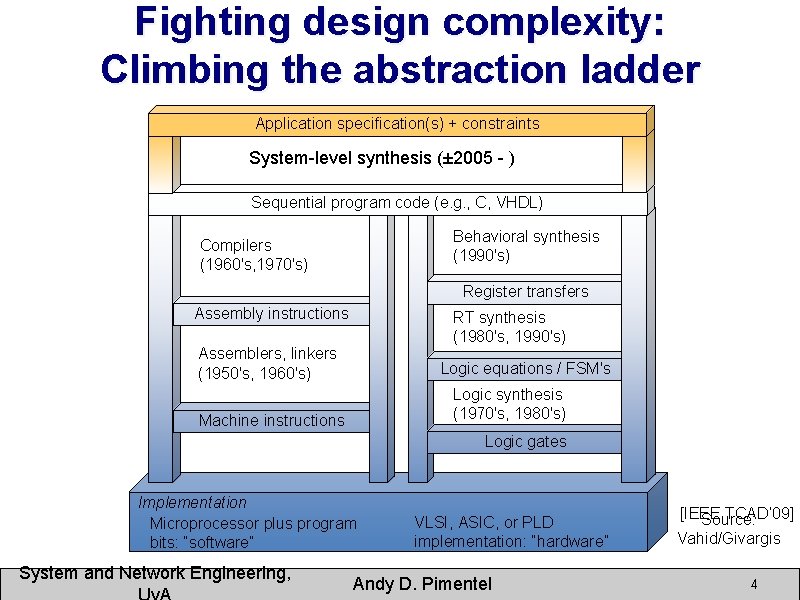

Fighting design complexity: Climbing the abstraction ladder Application specification(s) + constraints System-level synthesis (± 2005 - ) Sequential program code (e. g. , C, VHDL) Behavioral synthesis (1990's) Compilers (1960's, 1970's) Register transfers Assembly instructions RT synthesis (1980's, 1990's) Assemblers, linkers (1950's, 1960's) Logic equations / FSM's Logic synthesis (1970's, 1980's) Machine instructions Logic gates Implementation Microprocessor plus program bits: “software” System and Network Engineering, VLSI, ASIC, or PLD implementation: “hardware” Andy D. Pimentel [IEEE TCAD’ 09] Source: Vahid/Givargis 4

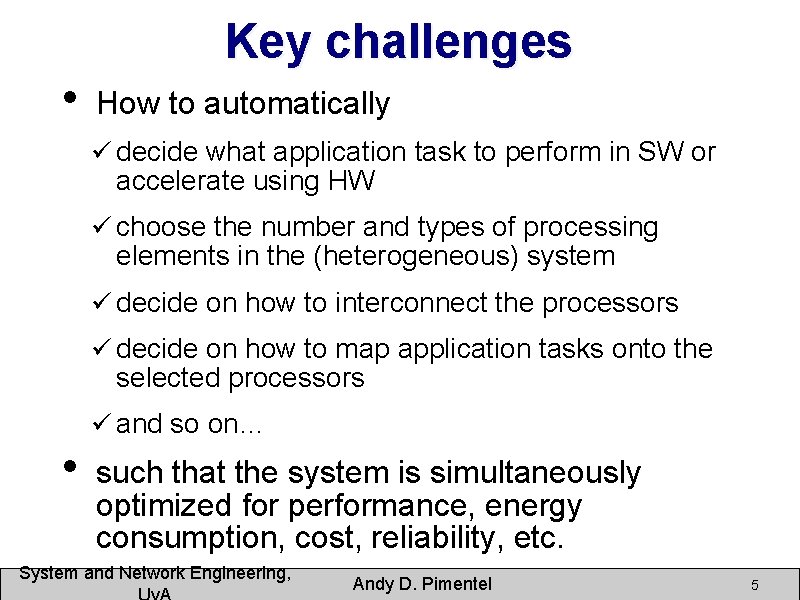

• Key challenges How to automatically ü decide what application task to perform in SW or accelerate using HW ü choose the number and types of processing elements in the (heterogeneous) system ü decide on how to interconnect the processors ü decide on how to map application tasks onto the selected processors • ü and so on… such that the system is simultaneously optimized for performance, energy consumption, cost, reliability, etc. System and Network Engineering, Andy D. Pimentel 5

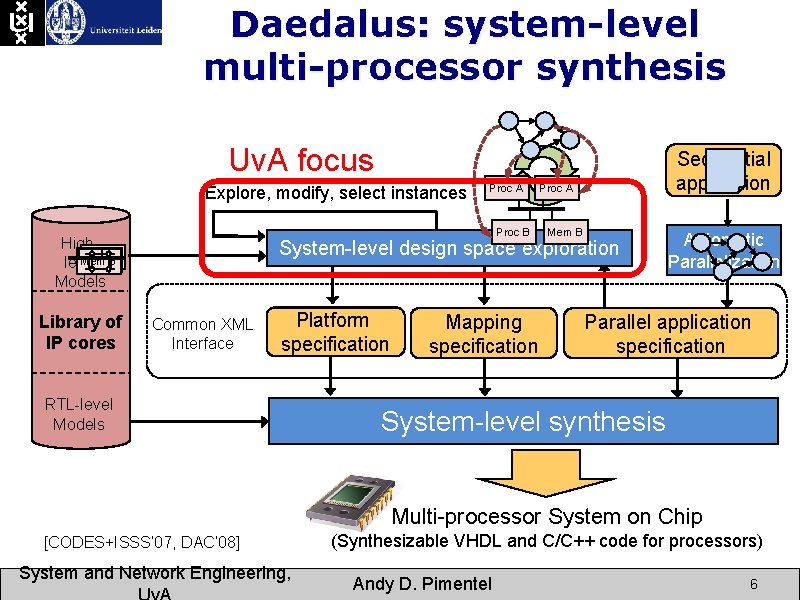

Daedalus: system-level multi-processor synthesis Uv. A focus Explore, modify, select instances Proc B High. Proc. A Mem Proc BA level Models Library of IP cores Proc A Sequential application Proc A Mem B System-level design space exploration Common XML Interface Platform specification RTL-level Models Mapping specification Automatic Parallelization Parallel application specification System-level synthesis Multi-processor System on Chip [CODES+ISSS’ 07, DAC’ 08] System and Network Engineering, (Synthesizable VHDL and C/C++ code for processors) Andy D. Pimentel 6

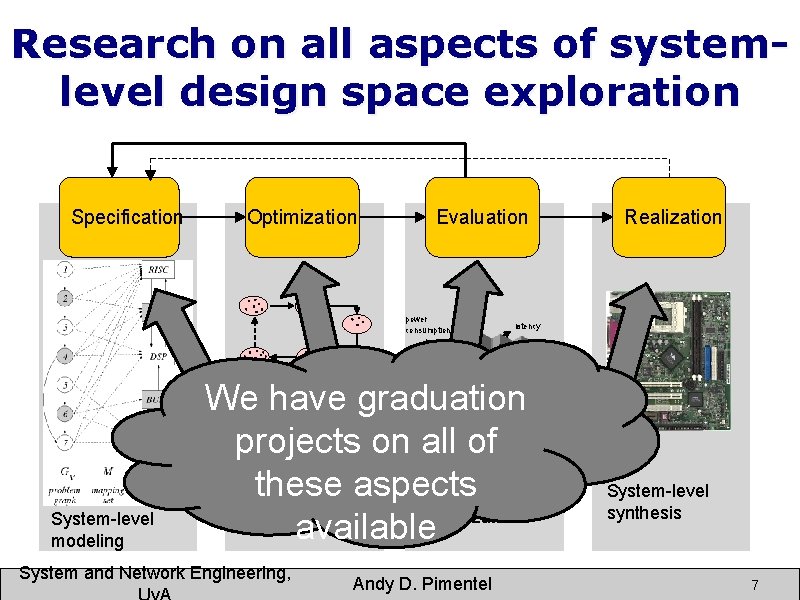

Research on all aspects of systemlevel design space exploration Specification Optimization Evaluation power consumption Realization latency We have graduation Heuristic Search projects on all of Algorithms Metrics + these aspects + System-level Visualization simulation available cost System-level modeling System and Network Engineering, Andy D. Pimentel System-level synthesis 7

- Slides: 7