Embedded Systems Design A Unified HardwareSoftware Introduction Chapter

Embedded Systems Design: A Unified Hardware/Software Introduction Chapter 3 General-Purpose Processors: Software 1

Introduction • Processor designed for a variety of computation tasks – Low unit cost, in part because manufacturer spreads NRE over large numbers of units • Motorola sold half a billion 68 HC 05 microcontrollers in 1996 alone – Carefully designed since higher NRE is acceptable • Can yield good performance, size and power – Low NRE cost, short time-to-market/prototype, high flexibility • User just writes software; no processor design Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 2

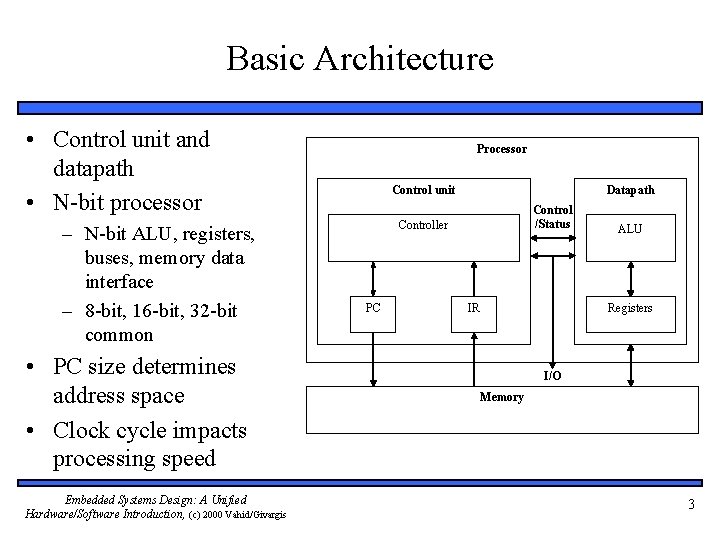

Basic Architecture • Control unit and datapath • N-bit processor – N-bit ALU, registers, buses, memory data interface – 8 -bit, 16 -bit, 32 -bit common • PC size determines address space • Clock cycle impacts processing speed Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Processor Control unit Datapath Control /Status Controller PC IR ALU Registers I/O Memory 3

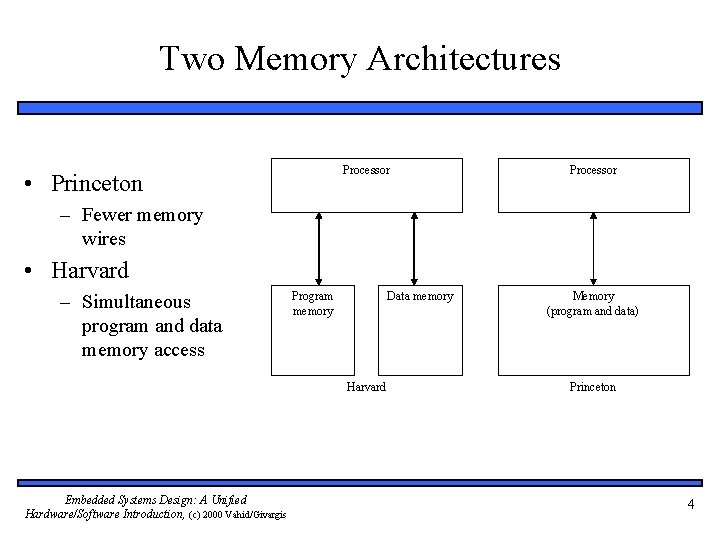

Two Memory Architectures Processor • Princeton Processor – Fewer memory wires • Harvard – Simultaneous program and data memory access Program memory Data memory Harvard Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Memory (program and data) Princeton 4

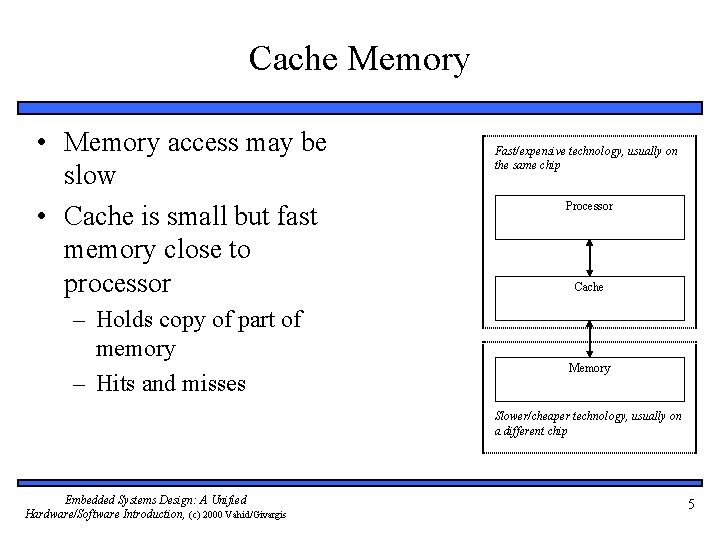

Cache Memory • Memory access may be slow • Cache is small but fast memory close to processor – Holds copy of part of memory – Hits and misses Fast/expensive technology, usually on the same chip Processor Cache Memory Slower/cheaper technology, usually on a different chip Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 5

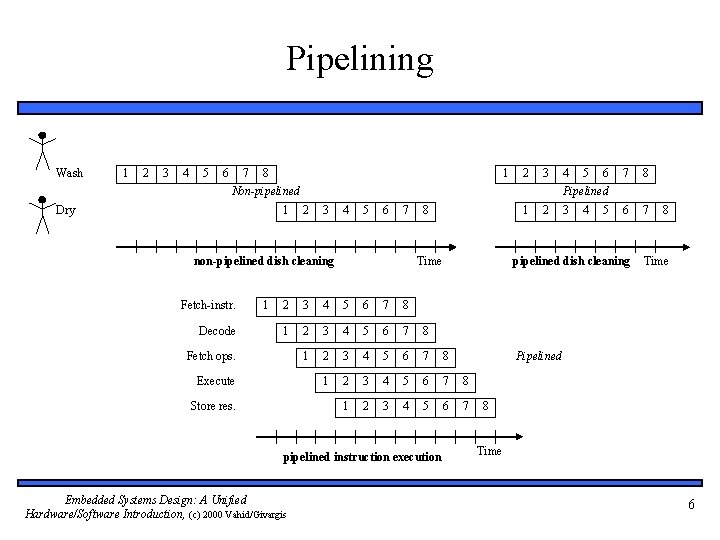

Pipelining Wash 1 2 3 4 5 6 7 8 1 2 3 Non-pipelined Dry 1 Decode 1 2 3 4 5 6 7 8 1 Time 3 4 5 6 7 8 1 2 3 4 5 6 7 Execute Store res. pipelined instruction execution Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 6 7 8 2 3 4 5 6 7 pipelined dish cleaning 2 Fetch ops. 5 Pipelined non-pipelined dish cleaning Fetch-instr. 4 8 Time Pipelined 8 Time 6

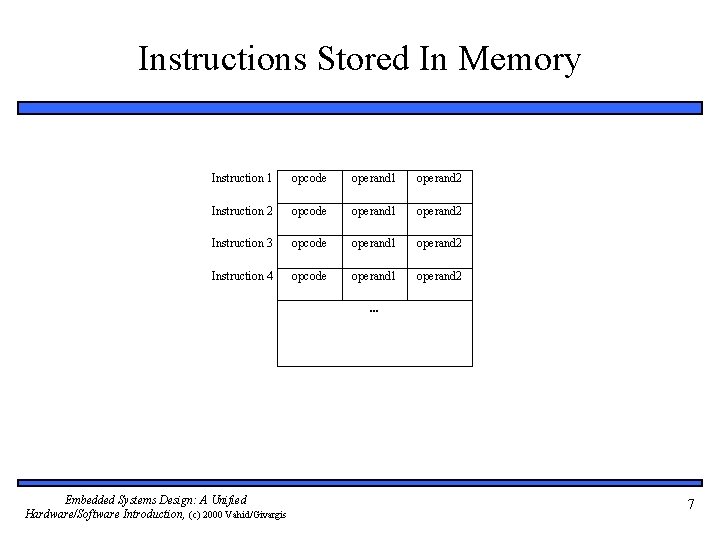

Instructions Stored In Memory Instruction 1 opcode operand 1 operand 2 Instruction 2 opcode operand 1 operand 2 Instruction 3 opcode operand 1 operand 2 Instruction 4 opcode operand 1 operand 2 . . . Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 7

Addressing Modes Addressing mode Operand field Immediate Data Register-direct Register-file contents Memory contents Register address Data Register indirect Register address Memory address Direct Memory address Data Indirect Memory address Data Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 8

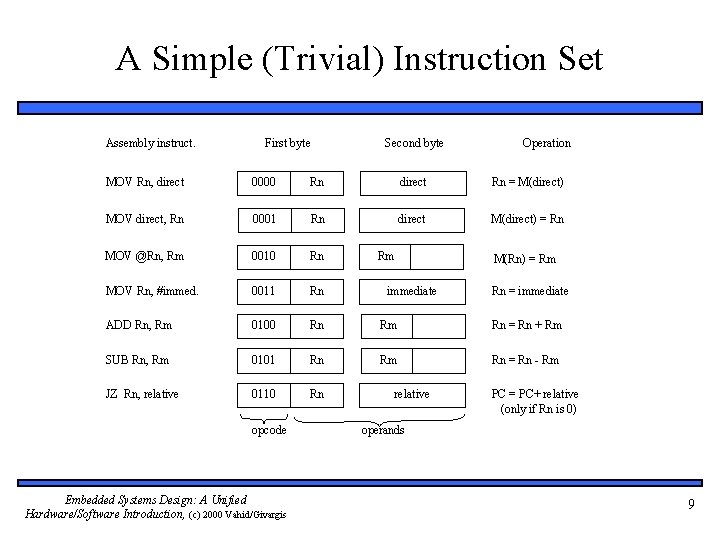

A Simple (Trivial) Instruction Set Assembly instruct. First byte Second byte Operation MOV Rn, direct 0000 Rn direct Rn = M(direct) MOV direct, Rn 0001 Rn direct M(direct) = Rn MOV @Rn, Rm 0010 Rn MOV Rn, #immed. 0011 Rn ADD Rn, Rm 0100 Rn Rm Rn = Rn + Rm SUB Rn, Rm 0101 Rn Rm Rn = Rn - Rm JZ Rn, relative 0110 Rn opcode Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Rm immediate relative M(Rn) = Rm Rn = immediate PC = PC+ relative (only if Rn is 0) operands 9

Sample Programs C program int total = 0; for (int i=10; i!=0; i--) total += i; // next instructions. . . Equivalent assembly program 0 MOV R 0, #0; // total = 0 1 MOV R 1, #10; // i = 10 2 MOV R 2, #1; // constant 1 3 MOV R 3, #0; // constant 0 Loop: JZ R 1, Next; // Done if i=0 5 ADD R 0, R 1; // total += i 6 SUB R 1, R 2; // i-- 7 JZ R 3, Loop; // Jump always Next: Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis // next instructions. . . 10

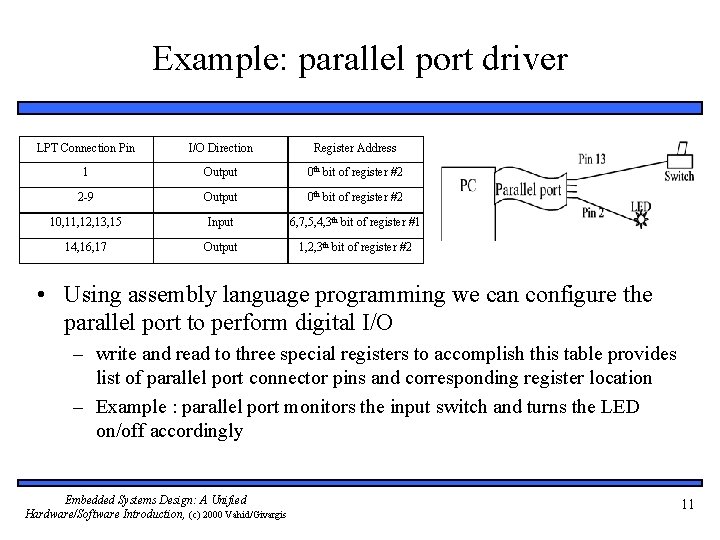

Example: parallel port driver LPT Connection Pin I/O Direction Register Address 1 Output 0 th bit of register #2 2 -9 Output 0 th bit of register #2 10, 11, 12, 13, 15 Input 6, 7, 5, 4, 3 th bit of register #1 14, 16, 17 Output 1, 2, 3 th bit of register #2 • Using assembly language programming we can configure the parallel port to perform digital I/O – write and read to three special registers to accomplish this table provides list of parallel port connector pins and corresponding register location – Example : parallel port monitors the input switch and turns the LED on/off accordingly Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 11

Parallel Port Example ; ; This program consists of a sub-routine that reads the state of the input pin, determining the on/off state of our switch and asserts the output pin, turning the LED on/off accordingly. 386 Check. Port push dx mov in and cmp jne proc ax ; ; dx, 3 BCh + 1 ; al, dx ; al, 10 h ; al, 0 ; Switch. On ; save the content base + 1 for register #1 read register #1 mask out all but bit # 4 is it 0? if not, we need to turn the LED on Switch. Off: mov in and out jmp dx, 3 BCh + 0 ; base + 0 for register #0 al, dx ; read the current state of the port al, f 7 h ; clear first bit (masking) dx, al ; write it out to the port Done ; we are done Switch. On: mov in or out dx, al, dx, Done: pop Check. Port extern “C” Check. Port(void); // defined in // assembly void main(void) { while( 1 ) { Check. Port(); } } dx ax endp 3 BCh + 0 ; base + 0 for register #0 dx ; read the current state of the port 01 h ; set first bit (masking) al ; write it out to the port ; restore the content Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 12

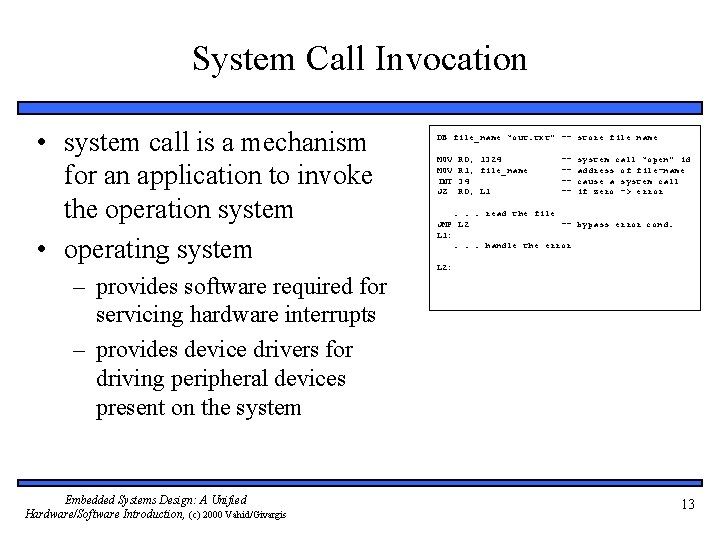

System Call Invocation • system call is a mechanism for an application to invoke the operation system • operating system – provides software required for servicing hardware interrupts – provides device drivers for driving peripheral devices present on the system Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis DB file_name “out. txt” -- store file name MOV INT JZ R 0, 1324 R 1, file_name 34 R 0, L 1 ----- system call “open” id address of file-name cause a system call if zero -> error . . . read the file JMP L 2 -- bypass error cond. L 1: . . . handle the error L 2: 13

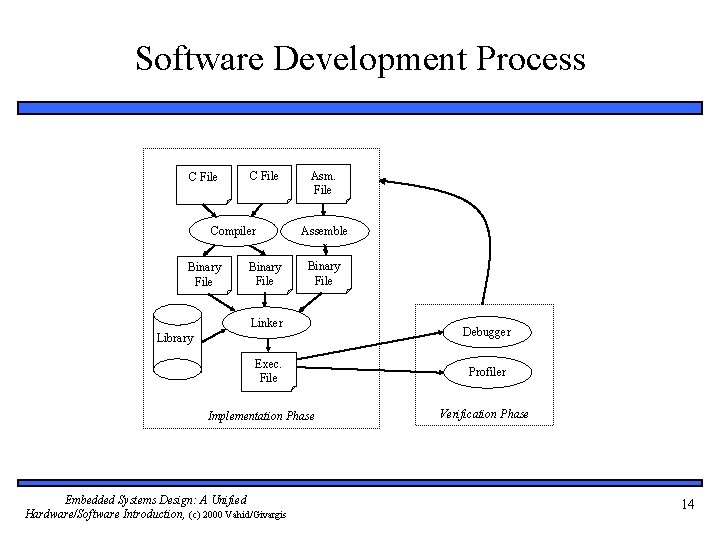

Software Development Process C File Compiler Binary File Asm. File Assemble r Binary File Linker Library Exec. File Implementation Phase Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Debugger Profiler Verification Phase 14

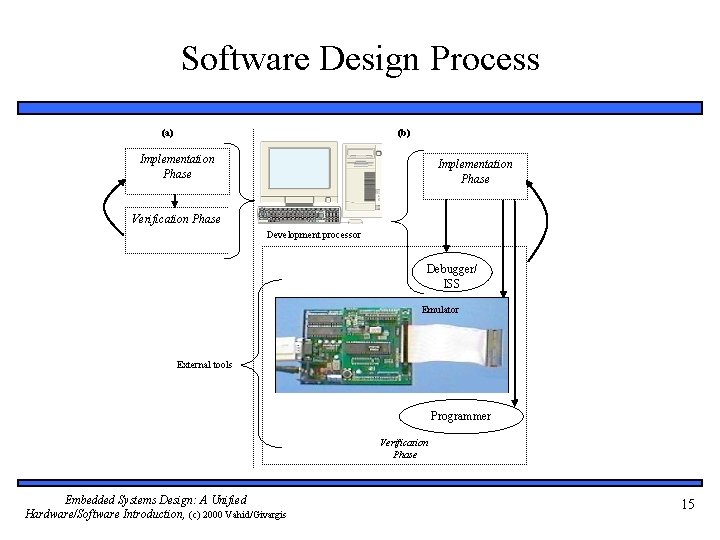

Software Design Process (a) (b) Implementation Phase Verification Phase Development processor Debugger/ ISS Emulator External tools Programmer Verification Phase Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 15

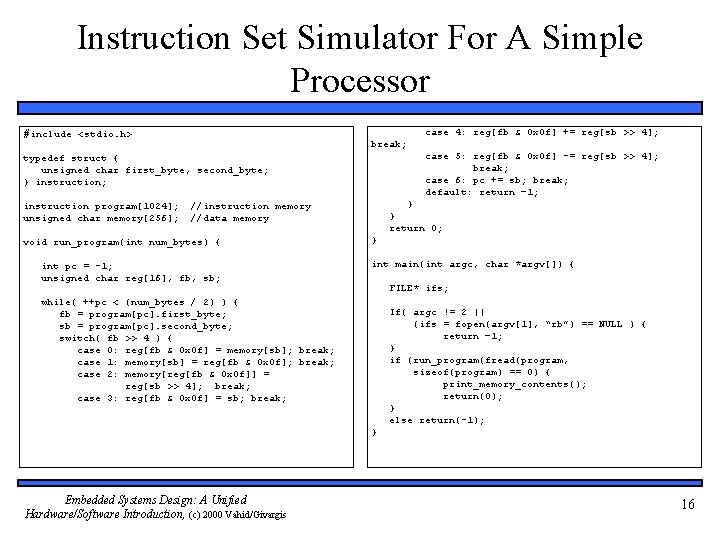

Instruction Set Simulator For A Simple Processor case 4: reg[fb & 0 x 0 f] += reg[sb >> 4]; #include <stdio. h> break; case 5: reg[fb & 0 x 0 f] -= reg[sb >> 4]; break; case 6: pc += sb; break; default: return – 1; typedef struct { unsigned char first_byte, second_byte; } instruction; instruction program[1024]; unsigned char memory[256]; } } return 0; //instruction memory //data memory void run_program(int num_bytes) { int pc = -1; unsigned char reg[16], fb, sb; } int main(int argc, char *argv[]) { FILE* ifs; while( ++pc < (num_bytes / 2) ) { fb = program[pc]. first_byte; sb = program[pc]. second_byte; switch( fb >> 4 ) { case 0: reg[fb & 0 x 0 f] = memory[sb]; break; case 1: memory[sb] = reg[fb & 0 x 0 f]; break; case 2: memory[reg[fb & 0 x 0 f]] = reg[sb >> 4]; break; case 3: reg[fb & 0 x 0 f] = sb; break; If( argc != 2 || (ifs = fopen(argv[1], “rb”) == NULL ) { return – 1; } if (run_program(fread(program, sizeof(program) == 0) { print_memory_contents(); return(0); } else return(-1); } Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 16

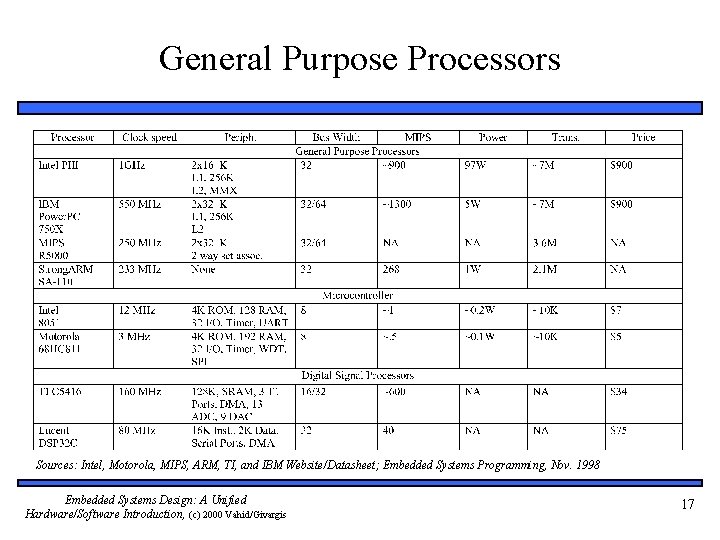

General Purpose Processors Sources: Intel, Motorola, MIPS, ARM, TI, and IBM Website/Datasheet; Embedded Systems Programming, Nov. 1998 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 17

![A Simple Microprocessor FSMD Declarations: bit PC[16], IR[16]; bit M[64 k][16], RF[16]; Aliases: op A Simple Microprocessor FSMD Declarations: bit PC[16], IR[16]; bit M[64 k][16], RF[16]; Aliases: op](http://slidetodoc.com/presentation_image_h2/adfb9281250f0500b429341554fe7a4f/image-18.jpg)

A Simple Microprocessor FSMD Declarations: bit PC[16], IR[16]; bit M[64 k][16], RF[16]; Aliases: op IR[15. . 12] rn IR[11. . 8] rm IR[7. . 4] FSM operations that replace the FSMD operations after a datapath is created Reset PC=0; PCclr=1; Fetch IR=M[PC]; PC=PC+1 MS=10; Irld=1; Mre=1; PCinc=1; Decode from states below dir IR[7. . 0] imm IR[7. . 0] rel IR[7. . 0] Mov 1 RF[rn] = M[dir] to Fetch RFwa=rn; RFwe=1; RFs=01; Mre=1; Mov 2 M[dir] = RF[rn] to Fetch RFr 1 a=rn; RFr 1 e=1; Ms=01; Mwe=1; Mov 3 M[rn] = RF[rm] to Fetch RFr 1 a=rn; RFr 1 e=1; Ms=10; Mwe=1; Mov 4 RF[rn]= imm to Fetch RFwa=rn; RFwe=1; RFs=10; Add RF[rn] =RF[rn]+RF[rm] to Fetch RFwa=rn; RFwe=1; RFs=00; RFr 1 a=rn; RFr 1 e=1; RFr 2 a=rm; RFr 2 e=1; ALUs=00 Sub RF[rn] = RF[rn]-RF[rm] to Fetch RFwa=rn; RFwe=1; RFs=00; RFr 1 a=rn; RFr 1 e=1; RFr 2 a=rm; RFr 2 e=1; ALUs=01 Jz PC=(RF[rn]=0) ? rel : PC to Fetch PCld= ALUz; RFrla=rn; RFrle=1; op = 0000 0001 0010 0011 0100 0101 0110 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 18

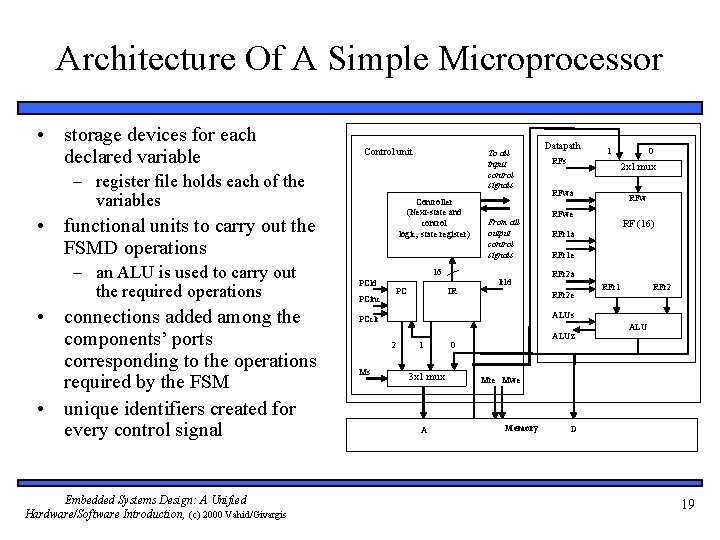

Architecture Of A Simple Microprocessor • storage devices for each declared variable Control unit – register file holds each of the variables Controller (Next-state and control logic; state register) • functional units to carry out the FSMD operations – an ALU is used to carry out the required operations • connections added among the components’ ports corresponding to the operations required by the FSM • unique identifiers created for every control signal Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis To all input control signals 16 PCld PCinc PC IR From all output control signals Irld RFs 1 0 2 x 1 mux RFwa RFwe RF (16) RFr 1 a RFr 1 e RFr 2 a RFr 2 e RFr 1 RFr 2 ALUs PCclr 2 Ms Datapath 1 3 x 1 mux A ALUz 0 ALU Mre Mwe Memory D 19

- Slides: 19