Embedded Systems Design A Unified HardwareSoftware Introduction Chapter

Embedded Systems Design: A Unified Hardware/Software Introduction Chapter 5 Memory 1

Introduction • Embedded system’s functionality aspects – Processing • processors • transformation of data – Storage • memory • retention of data – Communication • buses • transfer of data Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 2

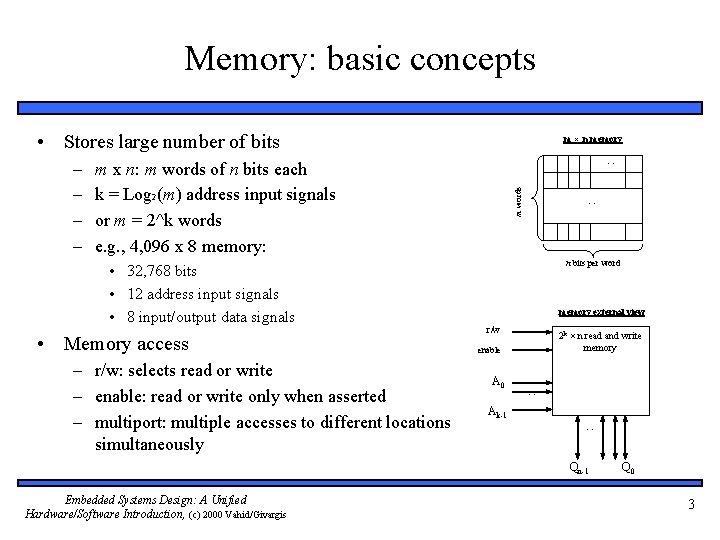

Memory: basic concepts • Stores large number of bits … m x n: m words of n bits each k = Log 2(m) address input signals or m = 2^k words e. g. , 4, 096 x 8 memory: • 32, 768 bits • 12 address input signals • 8 input/output data signals • Memory access – r/w: selects read or write – enable: read or write only when asserted – multiport: multiple accesses to different locations simultaneously m words – – m × n memory … n bits per word memory external view r/w 2 k × n read and write memory enable A 0 … Ak-1 … Qn-1 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Q 0 3

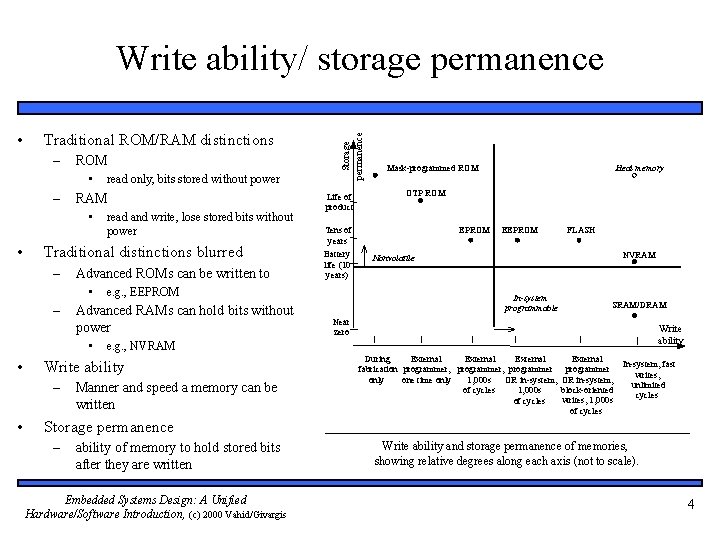

• Traditional ROM/RAM distinctions – ROM • – RAM • • Advanced ROMs can be written to • – Tens of years Battery life (10 years) Mask-programmed ROM Ideal memory OTP ROM EPROM EEPROM FLASH NVRAM Nonvolatile In-system programmable SRAM/DRAM Near zero Write ability e. g. , NVRAM Write ability – Life of product e. g. , EEPROM Advanced RAMs can hold bits without power • • read and write, lose stored bits without power Traditional distinctions blurred – • read only, bits stored without power Storage permanence Write ability/ storage permanence Manner and speed a memory can be written During External fabrication programmer, programmer 1, 000 s OR in-system, only one time only 1, 000 s of cycles External In-system, fast programmer writes, OR in-system, unlimited block-oriented cycles writes, 1, 000 s of cycles Storage permanence – ability of memory to hold stored bits after they are written Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Write ability and storage permanence of memories, showing relative degrees along each axis (not to scale). 4

Write ability • Ranges of write ability – High end • processor writes to memory simply and quickly • e. g. , RAM – Middle range • processor writes to memory, but slower • e. g. , FLASH, EEPROM – Lower range • special equipment, “programmer”, must be used to write to memory • e. g. , EPROM, OTP ROM – Low end • bits stored only during fabrication • e. g. , Mask-programmed ROM • In-system programmable memory – Can be written to by a processor in the embedded system using the memory – Memories in high end and middle range of write ability Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 5

Storage permanence • Range of storage permanence – High end • essentially never loses bits • e. g. , mask-programmed ROM – Middle range • holds bits days, months, or years after memory’s power source turned off • e. g. , NVRAM – Lower range • holds bits as long as power supplied to memory • e. g. , SRAM – Low end • begins to lose bits almost immediately after written • e. g. , DRAM • Nonvolatile memory – Holds bits after power is no longer supplied – High end and middle range of storage permanence Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 6

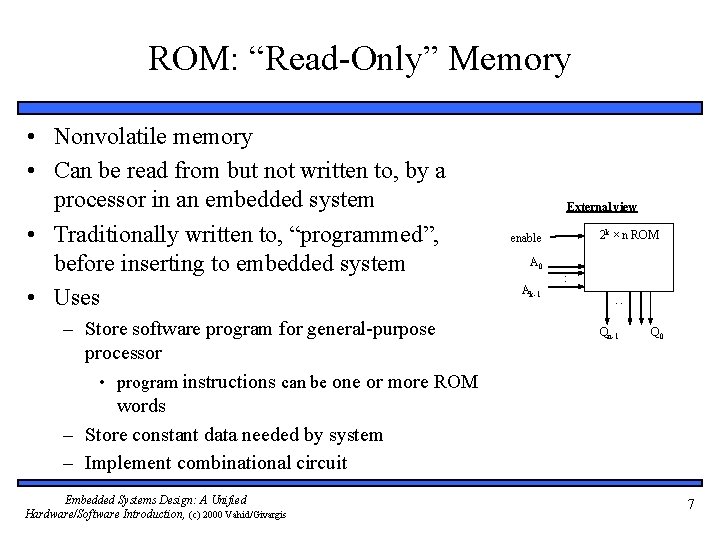

ROM: “Read-Only” Memory – Store software program for general-purpose processor • program instructions can be one or more ROM words – Store constant data needed by system – Implement combinational circuit Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis External view 2 k × n ROM enable A 0 Ak-1 … • Nonvolatile memory • Can be read from but not written to, by a processor in an embedded system • Traditionally written to, “programmed”, before inserting to embedded system • Uses … Qn-1 Q 0 7

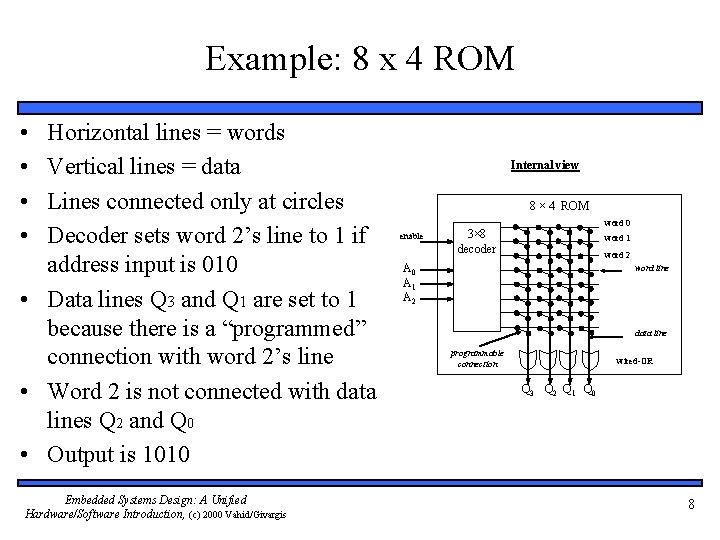

Example: 8 x 4 ROM • • Horizontal lines = words Vertical lines = data Lines connected only at circles Decoder sets word 2’s line to 1 if address input is 010 • Data lines Q 3 and Q 1 are set to 1 because there is a “programmed” connection with word 2’s line • Word 2 is not connected with data lines Q 2 and Q 0 • Output is 1010 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Internal view 8 × 4 ROM enable word 0 3× 8 decoder word 1 word 2 A 0 A 1 A 2 word line data line programmable connection wired-OR Q 3 Q 2 Q 1 Q 0 8

9

Mask-programmed ROM • Connections “programmed” at fabrication – set of masks • Lowest write ability – only once • Highest storage permanence – bits never change unless damaged • Typically used for final design of high-volume systems – spread out NRE cost for a low unit cost Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 10

OTP ROM: One-time programmable ROM • Connections “programmed” after manufacture by user – – user provides file of desired contents of ROM file input to machine called ROM programmer each programmable connection is a fuse ROM programmer blows fuses where connections should not exist • Very low write ability – typically written only once and requires ROM programmer device • Very high storage permanence – bits don’t change unless reconnected to programmer and more fuses blown • Commonly used in final products – cheaper, harder to inadvertently modify Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 11

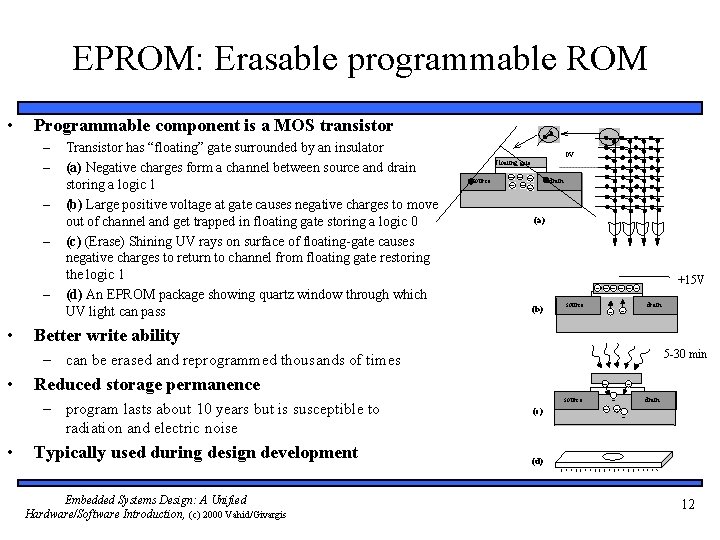

EPROM: Erasable programmable ROM • Programmable component is a MOS transistor – – – • Transistor has “floating” gate surrounded by an insulator (a) Negative charges form a channel between source and drain storing a logic 1 (b) Large positive voltage at gate causes negative charges to move out of channel and get trapped in floating gate storing a logic 0 (c) (Erase) Shining UV rays on surface of floating-gate causes negative charges to return to channel from floating gate restoring the logic 1 (d) An EPROM package showing quartz window through which UV light can pass 0 V floating gate drain source (a) +15 V (b) source drain Better write ability 5 -30 min – can be erased and reprogrammed thousands of times • Reduced storage permanence – program lasts about 10 years but is susceptible to radiation and electric noise • Typically used during design development Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis source drain (c) (d) . 12

EEPROM: Electrically erasable programmable ROM • Programmed and erased electronically – typically by using higher than normal voltage – can program and erase individual words • Better write ability – can be in-system programmable with built-in circuit to provide higher than normal voltage • built-in memory controller commonly used to hide details from memory user – writes very slow due to erasing and programming • “busy” pin indicates to processor EEPROM still writing – can be erased and programmed tens of thousands of times • Similar storage permanence to EPROM (about 10 years) • Far more convenient than EPROMs, but more expensive Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 13

Flash Memory • Extension of EEPROM – Same floating gate principle – Same write ability and storage permanence • Fast erase – Large blocks of memory erased at once, rather than one word at a time – Blocks typically several thousand bytes large • Writes to single words may be slower – Entire block must be read, word updated, then entire block written back • Used with embedded systems storing large data items in nonvolatile memory – e. g. , digital cameras, TV set-top boxes, cell phones Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 14

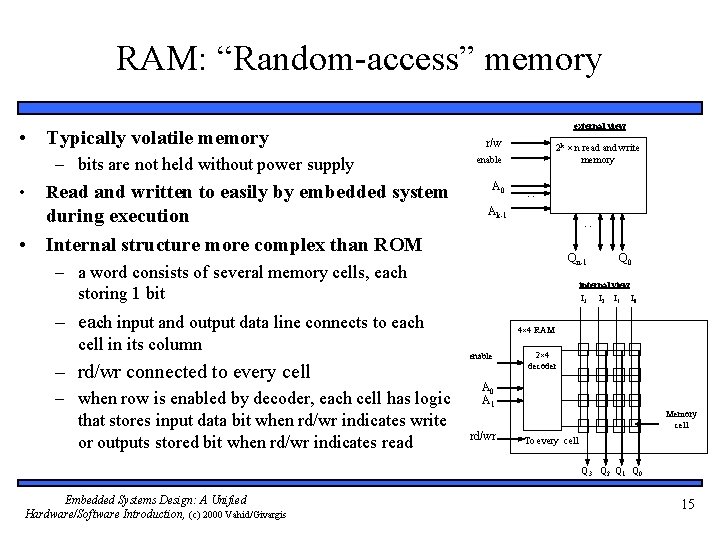

RAM: “Random-access” memory • Typically volatile memory – bits are not held without power supply • Read and written to easily by embedded system during execution • Internal structure more complex than ROM external view r/w 2 k × n read and write memory enable A 0 … Ak-1 … Qn-1 – a word consists of several memory cells, each storing 1 bit internal view I 3 I 2 I 1 I 0 – each input and output data line connects to each cell in its column – rd/wr connected to every cell – when row is enabled by decoder, each cell has logic that stores input data bit when rd/wr indicates write or outputs stored bit when rd/wr indicates read Q 0 4× 4 RAM enable 2× 4 decoder A 0 A 1 rd/wr Memory cell To every cell Q 3 Q 2 Q 1 Q 0 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 15

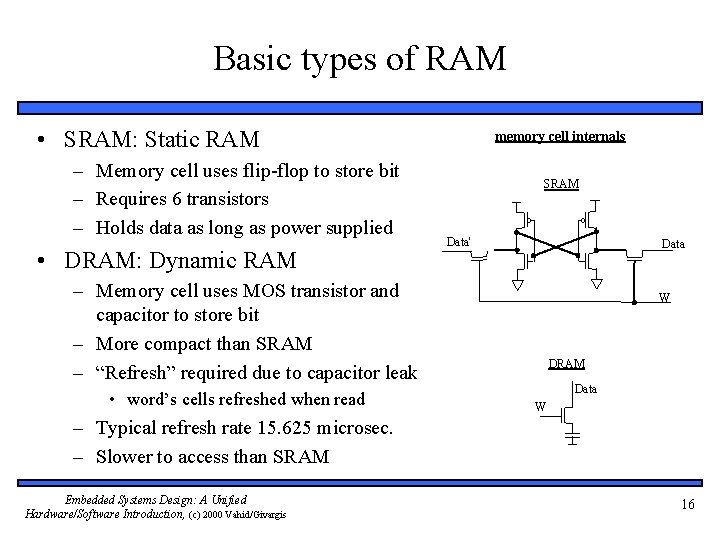

Basic types of RAM • SRAM: Static RAM – Memory cell uses flip-flop to store bit – Requires 6 transistors – Holds data as long as power supplied • DRAM: Dynamic RAM memory cell internals SRAM Data' Data – Memory cell uses MOS transistor and capacitor to store bit – More compact than SRAM – “Refresh” required due to capacitor leak • word’s cells refreshed when read W DRAM Data W – Typical refresh rate 15. 625 microsec. – Slower to access than SRAM Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 16

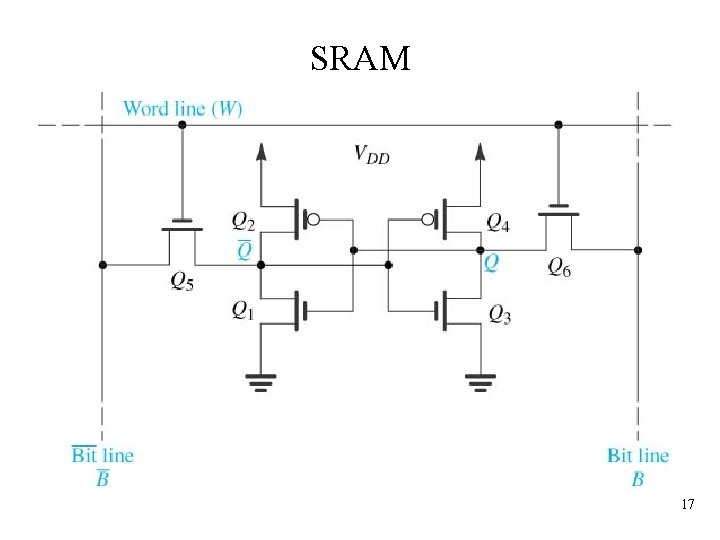

SRAM 17

DRAM 18

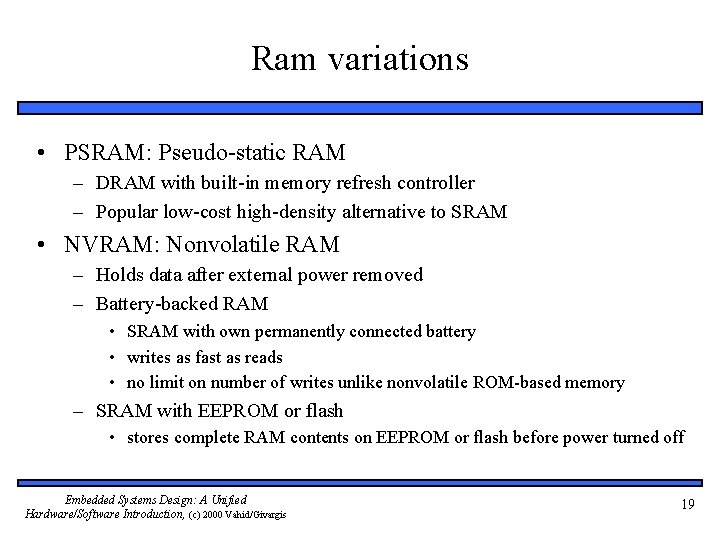

Ram variations • PSRAM: Pseudo-static RAM – DRAM with built-in memory refresh controller – Popular low-cost high-density alternative to SRAM • NVRAM: Nonvolatile RAM – Holds data after external power removed – Battery-backed RAM • SRAM with own permanently connected battery • writes as fast as reads • no limit on number of writes unlike nonvolatile ROM-based memory – SRAM with EEPROM or flash • stores complete RAM contents on EEPROM or flash before power turned off Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 19

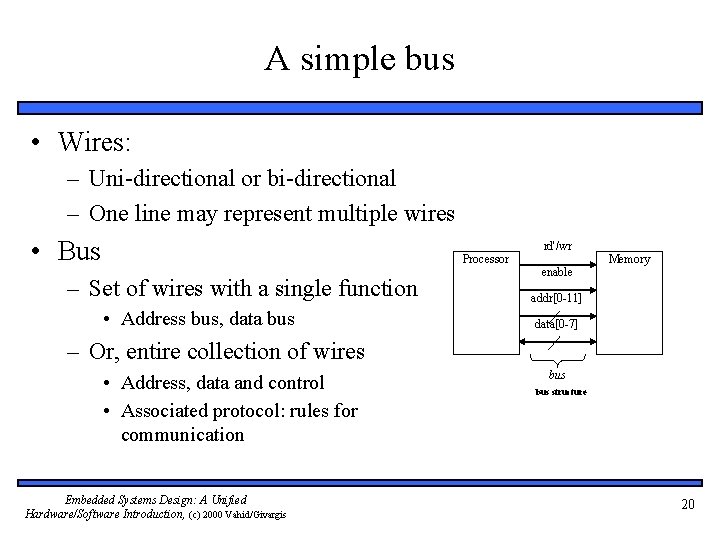

A simple bus • Wires: – Uni-directional or bi-directional – One line may represent multiple wires • Bus Processor – Set of wires with a single function • Address bus, data bus rd'/wr enable Memory addr[0 -11] data[0 -7] – Or, entire collection of wires • Address, data and control • Associated protocol: rules for communication Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis bus structure 20

![Ports Processor port rd'/wr Memory enable addr[0 -11] data[0 -7] • • • Conducting Ports Processor port rd'/wr Memory enable addr[0 -11] data[0 -7] • • • Conducting](http://slidetodoc.com/presentation_image_h2/71b8a3d1b9ab5b4fc35a1f1b5771510d/image-21.jpg)

Ports Processor port rd'/wr Memory enable addr[0 -11] data[0 -7] • • • Conducting device on periphery Connects bus to processor or memory Often referred to as a pin bus – Actual pins on periphery of IC package that plug into socket on printed-circuit board – Sometimes metallic balls instead of pins – Today, metal “pads” connecting processors and memories within single IC • Single wire or set of wires with single function – E. g. , 12 -wire address port Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 21

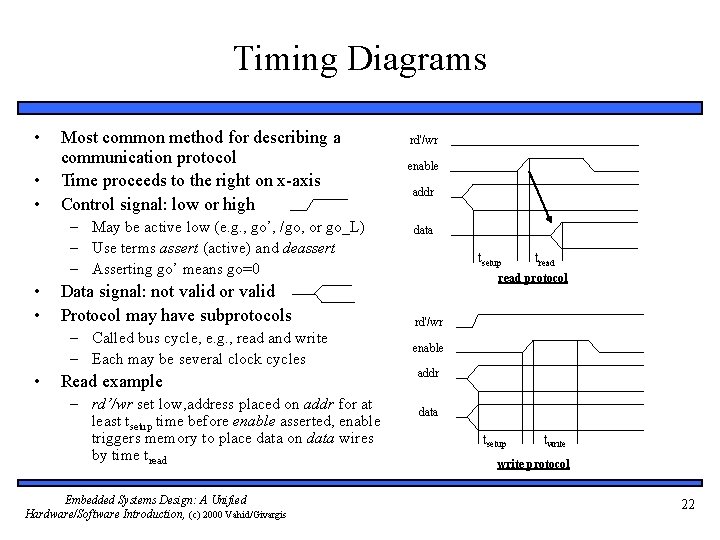

Timing Diagrams • • • Most common method for describing a communication protocol Time proceeds to the right on x-axis Control signal: low or high – May be active low (e. g. , go’, /go, or go_L) – Use terms assert (active) and deassert – Asserting go’ means go=0 • • Data signal: not valid or valid Protocol may have subprotocols – Called bus cycle, e. g. , read and write – Each may be several clock cycles • Read example – rd’/wr set low, address placed on addr for at least tsetup time before enable asserted, enable triggers memory to place data on data wires by time tread Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis rd'/wr enable addr data tsetup tread protocol rd'/wr enable addr data tsetup twrite protocol 22

RAM timing diagrams 23

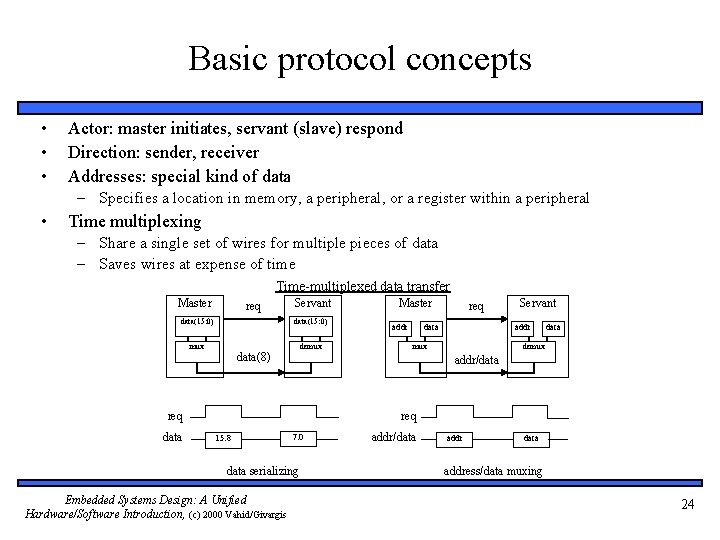

Basic protocol concepts • • • Actor: master initiates, servant (slave) respond Direction: sender, receiver Addresses: special kind of data – Specifies a location in memory, a peripheral, or a register within a peripheral • Time multiplexing – Share a single set of wires for multiple pieces of data – Saves wires at expense of time Time-multiplexed data transfer Master req data(15: 0) Servant data(15: 0) mux demux data(8) addr req data Servant addr mux data demux addr/data req data Master req 15: 8 7: 0 data serializing Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis addr/data address/data muxing 24

25

26

27

28

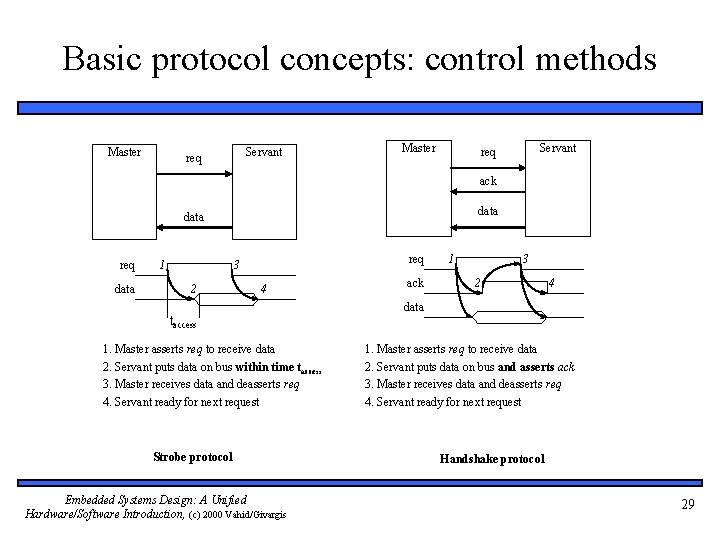

Basic protocol concepts: control methods Master Servant req ack data req data 1 req 3 2 4 taccess 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess 3. Master receives data and deasserts req 4. Servant ready for next request Strobe protocol Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis ack 1 3 2 4 data 1. Master asserts req to receive data 2. Servant puts data on bus and asserts ack 3. Master receives data and deasserts req 4. Servant ready for next request Handshake protocol 29

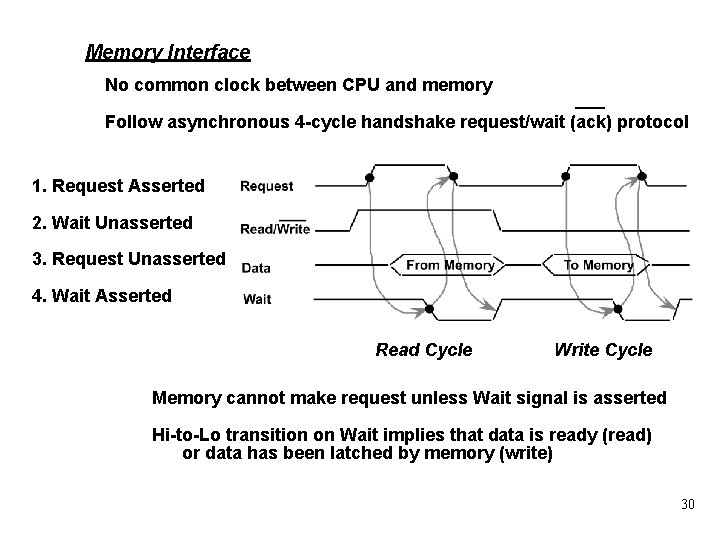

Memory Interface No common clock between CPU and memory Follow asynchronous 4 -cycle handshake request/wait (ack) protocol 1. Request Asserted 2. Wait Unasserted 3. Request Unasserted 4. Wait Asserted Read Cycle Write Cycle Memory cannot make request unless Wait signal is asserted Hi-to-Lo transition on Wait implies that data is ready (read) or data has been latched by memory (write) 30

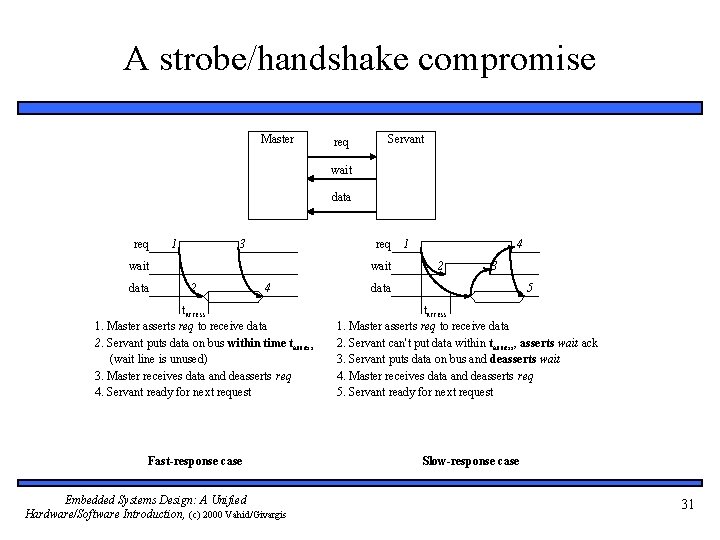

A strobe/handshake compromise Master req Servant wait data req 1 3 req 1 wait data wait 2 4 taccess 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess (wait line is unused) 3. Master receives data and deasserts req 4. Servant ready for next request Fast-response case Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 4 2 3 data 5 taccess 1. Master asserts req to receive data 2. Servant can't put data within taccess, asserts wait ack 3. Servant puts data on bus and deasserts wait 4. Master receives data and deasserts req 5. Servant ready for next request Slow-response case 31

Microprocessor interfacing: I/O addressing • A microprocessor communicates with other devices using some of its pins – Port-based I/O (parallel I/O) • Processor has one or more N-bit ports • Processor’s software reads and writes a port just like a register • E. g. , P 0 = 0 x. FF; v = P 1. 2; -- P 0 and P 1 are 8 -bit ports – Bus-based I/O • Processor has address, data and control ports that form a single bus • Communication protocol is built into the processor • A single instruction carries out the read or write protocol on the bus Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 32

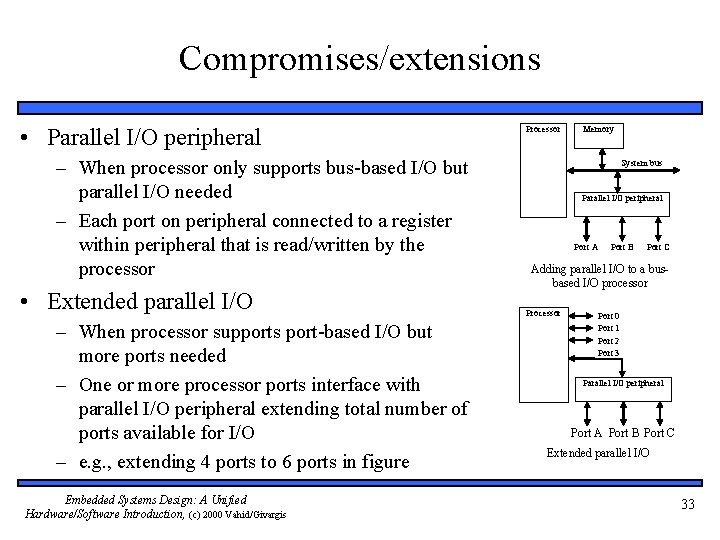

Compromises/extensions • Parallel I/O peripheral – When processor only supports bus-based I/O but parallel I/O needed – Each port on peripheral connected to a register within peripheral that is read/written by the processor • Extended parallel I/O – When processor supports port-based I/O but more ports needed – One or more processor ports interface with parallel I/O peripheral extending total number of ports available for I/O – e. g. , extending 4 ports to 6 ports in figure Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Processor Memory System bus Parallel I/O peripheral Port A Port B Port C Adding parallel I/O to a busbased I/O processor Port 0 Port 1 Port 2 Port 3 Parallel I/O peripheral Port A Port B Port C Extended parallel I/O 33

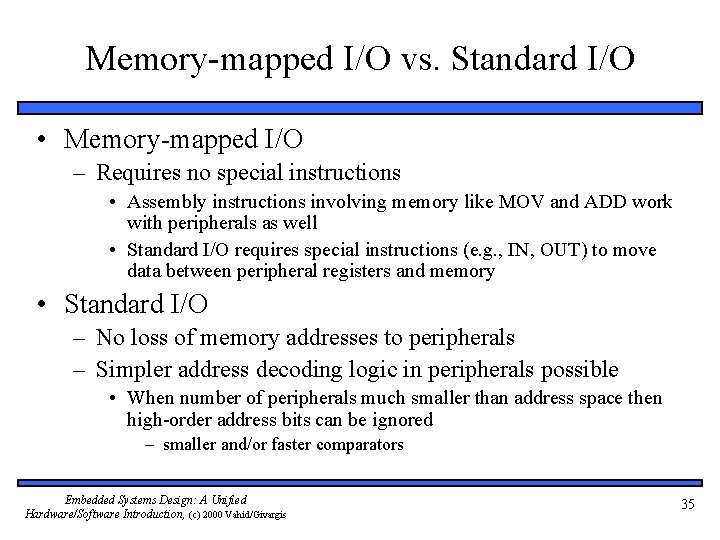

Types of bus-based I/O: memory-mapped I/O and standard I/O • Processor talks to both memory and peripherals using same bus – two ways to talk to peripherals – Memory-mapped I/O • Peripheral registers occupy addresses in same address space as memory • e. g. , Bus has 16 -bit address – lower 32 K addresses may correspond to memory – upper 32 k addresses may correspond to peripherals – Standard I/O (I/O-mapped I/O) • Additional pin (M/IO) on bus indicates whether a memory or peripheral access • e. g. , Bus has 16 -bit address – all 64 K addresses correspond to memory when M/IO set to 0 – all 64 K addresses correspond to peripherals when M/IO set to 1 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 34

Memory-mapped I/O vs. Standard I/O • Memory-mapped I/O – Requires no special instructions • Assembly instructions involving memory like MOV and ADD work with peripherals as well • Standard I/O requires special instructions (e. g. , IN, OUT) to move data between peripheral registers and memory • Standard I/O – No loss of memory addresses to peripherals – Simpler address decoding logic in peripherals possible • When number of peripherals much smaller than address space then high-order address bits can be ignored – smaller and/or faster comparators Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 35

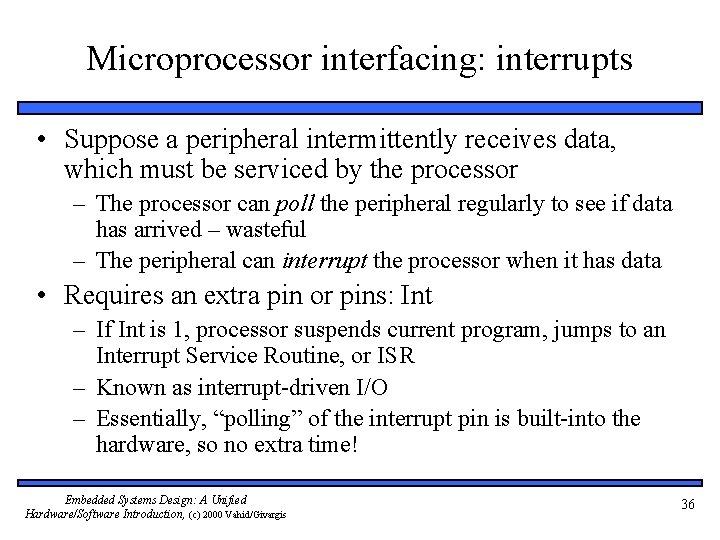

Microprocessor interfacing: interrupts • Suppose a peripheral intermittently receives data, which must be serviced by the processor – The processor can poll the peripheral regularly to see if data has arrived – wasteful – The peripheral can interrupt the processor when it has data • Requires an extra pin or pins: Int – If Int is 1, processor suspends current program, jumps to an Interrupt Service Routine, or ISR – Known as interrupt-driven I/O – Essentially, “polling” of the interrupt pin is built-into the hardware, so no extra time! Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 36

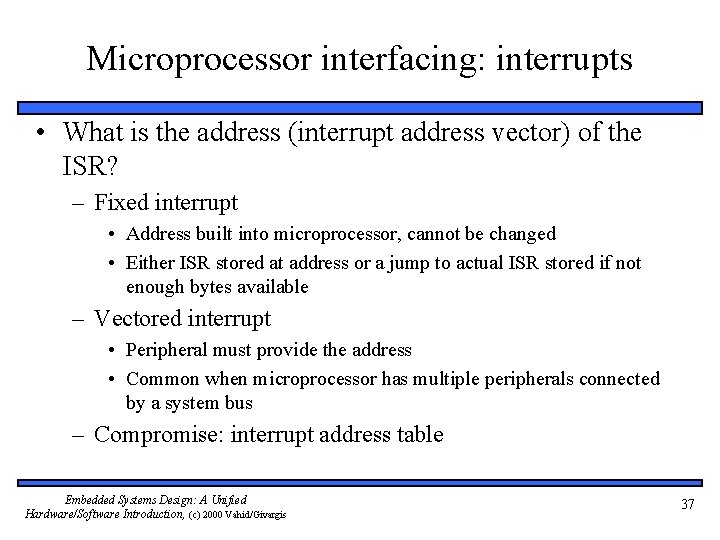

Microprocessor interfacing: interrupts • What is the address (interrupt address vector) of the ISR? – Fixed interrupt • Address built into microprocessor, cannot be changed • Either ISR stored at address or a jump to actual ISR stored if not enough bytes available – Vectored interrupt • Peripheral must provide the address • Common when microprocessor has multiple peripherals connected by a system bus – Compromise: interrupt address table Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 37

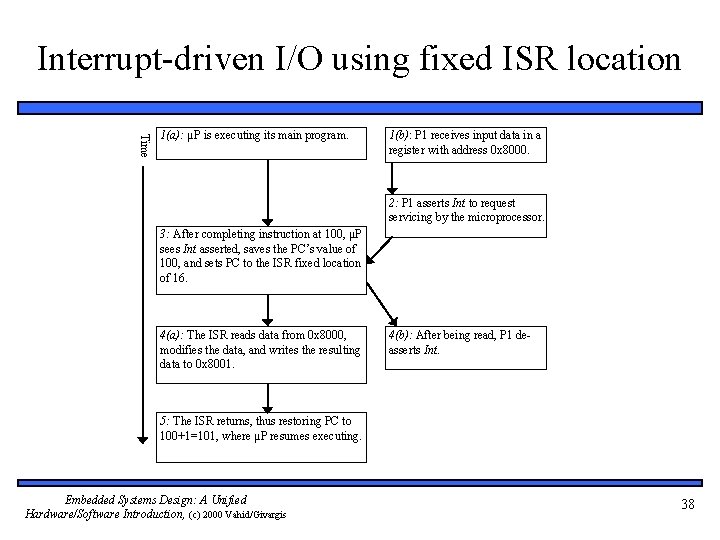

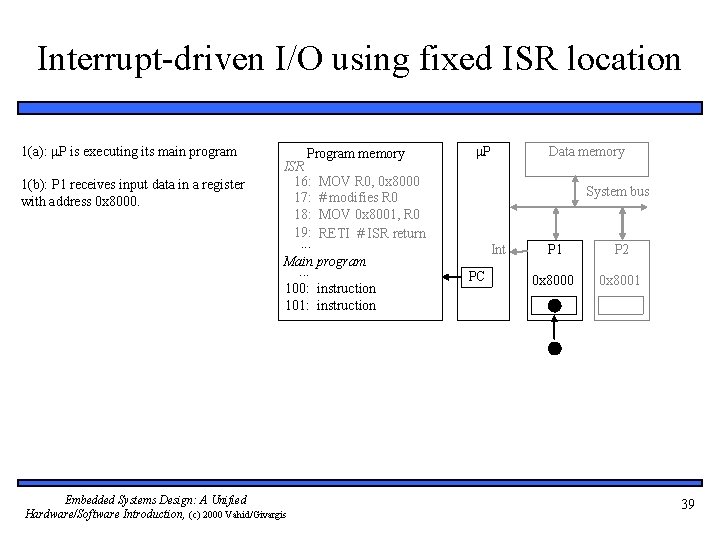

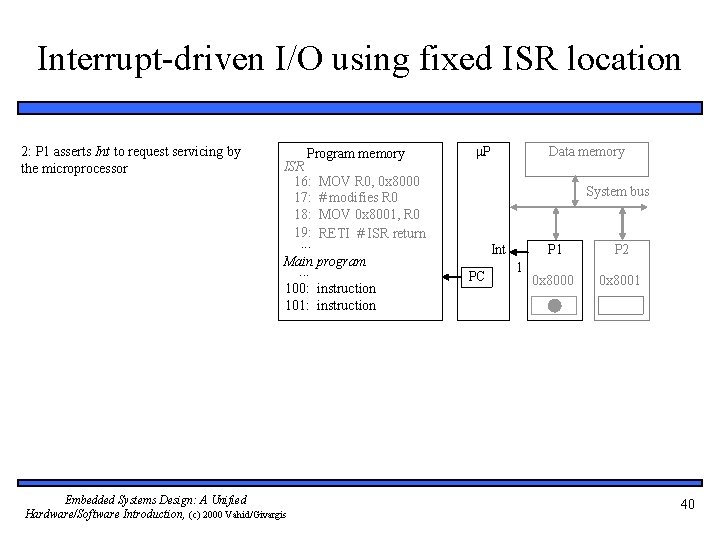

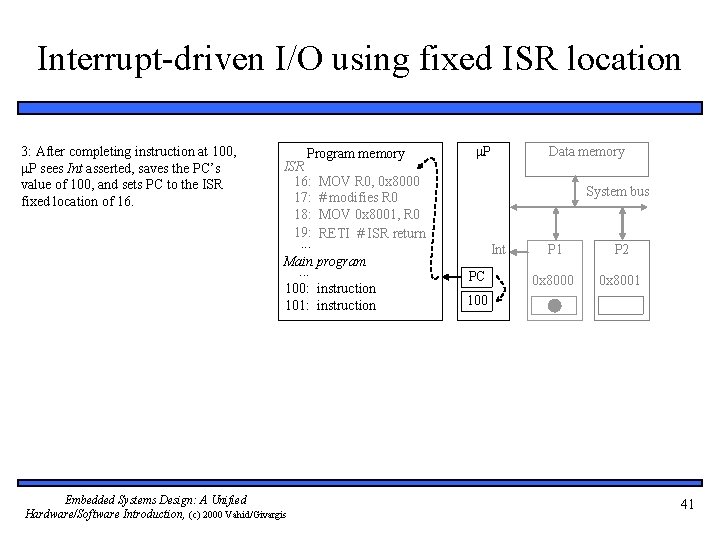

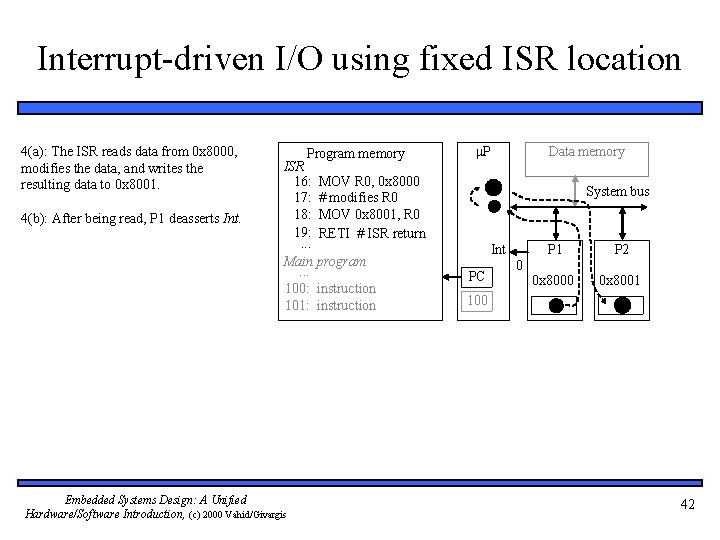

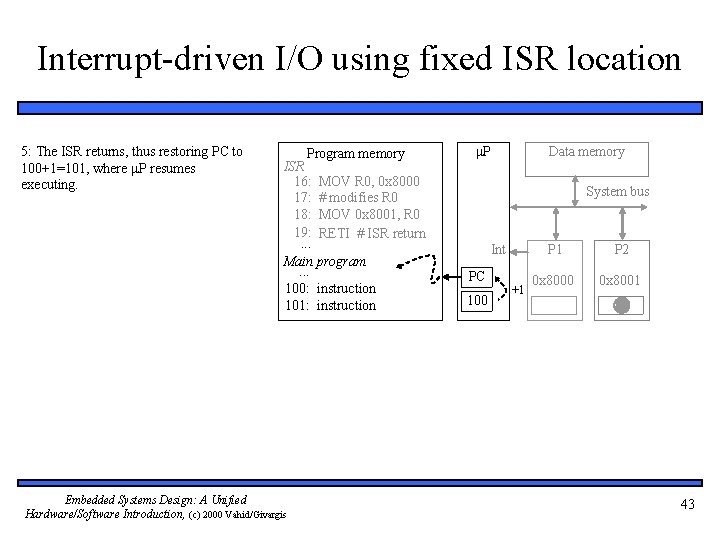

Interrupt-driven I/O using fixed ISR location Time 1(a): μP is executing its main program. 1(b): P 1 receives input data in a register with address 0 x 8000. 2: P 1 asserts Int to request servicing by the microprocessor. 3: After completing instruction at 100, μP sees Int asserted, saves the PC’s value of 100, and sets PC to the ISR fixed location of 16. 4(a): The ISR reads data from 0 x 8000, modifies the data, and writes the resulting data to 0 x 8001. 4(b): After being read, P 1 deasserts Int. 5: The ISR returns, thus restoring PC to 100+1=101, where μP resumes executing. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 38

Interrupt-driven I/O using fixed ISR location 1(a): P is executing its main program 1(b): P 1 receives input data in a register with address 0 x 8000. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Data memory System bus Int PC P 1 P 2 0 x 8000 0 x 8001 39

Interrupt-driven I/O using fixed ISR location 2: P 1 asserts Int to request servicing by the microprocessor Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Data memory System bus Int PC 1 P 2 0 x 8000 0 x 8001 40

Interrupt-driven I/O using fixed ISR location 3: After completing instruction at 100, P sees Int asserted, saves the PC’s value of 100, and sets PC to the ISR fixed location of 16. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Data memory System bus Int PC P 1 P 2 0 x 8000 0 x 8001 100 41

Interrupt-driven I/O using fixed ISR location 4(a): The ISR reads data from 0 x 8000, modifies the data, and writes the resulting data to 0 x 8001. 4(b): After being read, P 1 deasserts Int. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Data memory System bus Int PC 0 P 1 P 2 0 x 8000 0 x 8001 100 42

Interrupt-driven I/O using fixed ISR location 5: The ISR returns, thus restoring PC to 100+1=101, where P resumes executing. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Data memory System bus Int PC 100 +1 P 2 0 x 8000 0 x 8001 43

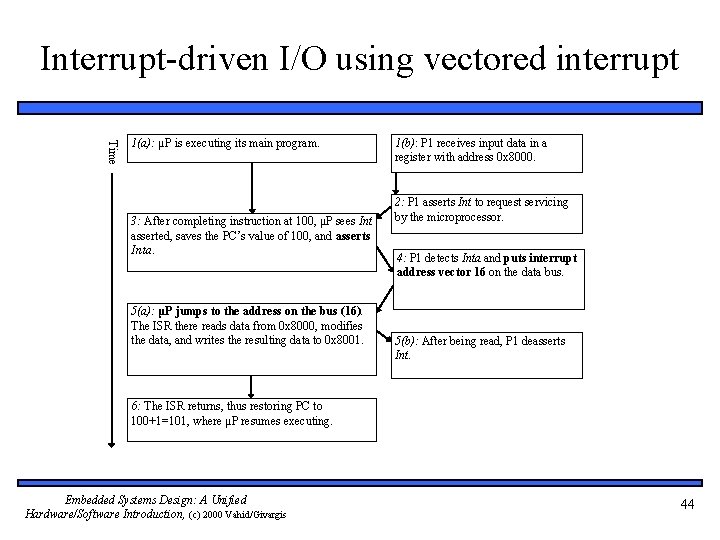

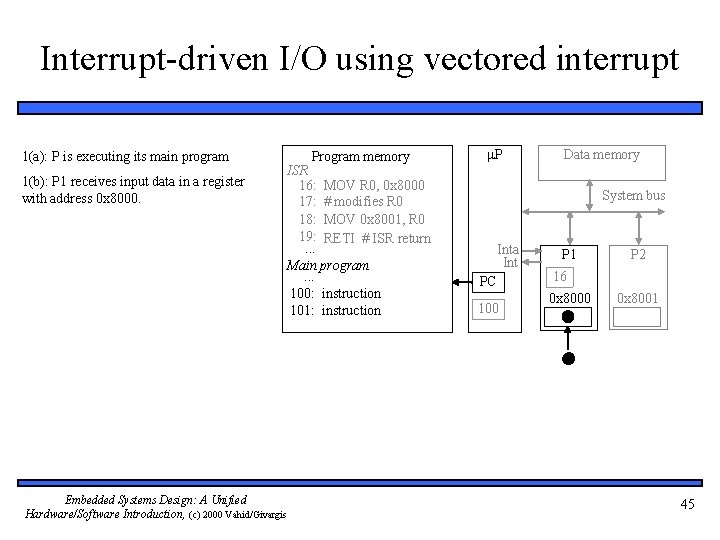

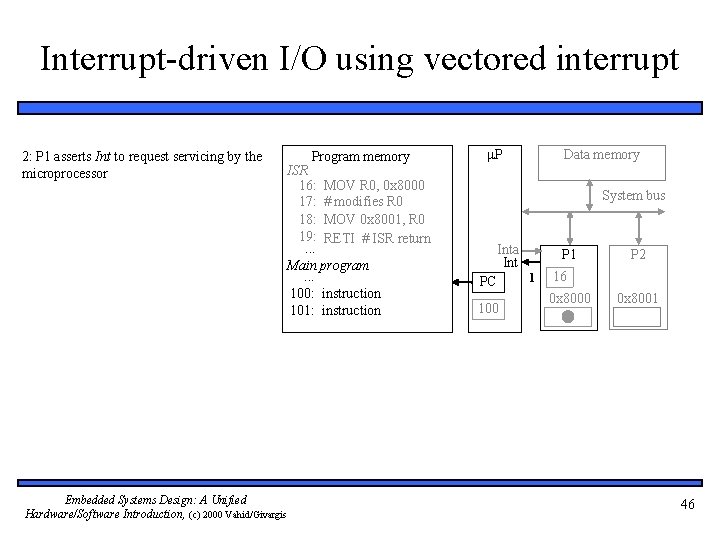

Interrupt-driven I/O using vectored interrupt Time 1(a): μP is executing its main program. 3: After completing instruction at 100, μP sees Int asserted, saves the PC’s value of 100, and asserts Inta. 5(a): μP jumps to the address on the bus (16). The ISR there reads data from 0 x 8000, modifies the data, and writes the resulting data to 0 x 8001. 1(b): P 1 receives input data in a register with address 0 x 8000. 2: P 1 asserts Int to request servicing by the microprocessor. 4: P 1 detects Inta and puts interrupt address vector 16 on the data bus. 5(b): After being read, P 1 deasserts Int. 6: The ISR returns, thus restoring PC to 100+1=101, where μP resumes executing. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 44

Interrupt-driven I/O using vectored interrupt 1(a): P is executing its main program 1(b): P 1 receives input data in a register with address 0 x 8000. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus Inta Int PC 100 P 1 P 2 16 0 x 8000 0 x 8001 45

Interrupt-driven I/O using vectored interrupt 2: P 1 asserts Int to request servicing by the microprocessor Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus Inta Int PC 100 P 1 1 P 2 16 0 x 8000 0 x 8001 46

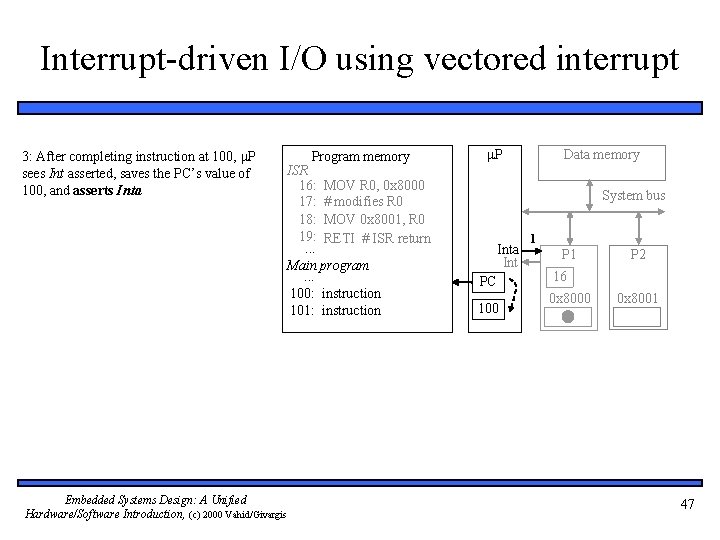

Interrupt-driven I/O using vectored interrupt 3: After completing instruction at 100, μP sees Int asserted, saves the PC’s value of 100, and asserts Inta Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus Inta Int PC 100 1 P 2 16 0 x 8000 0 x 8001 47

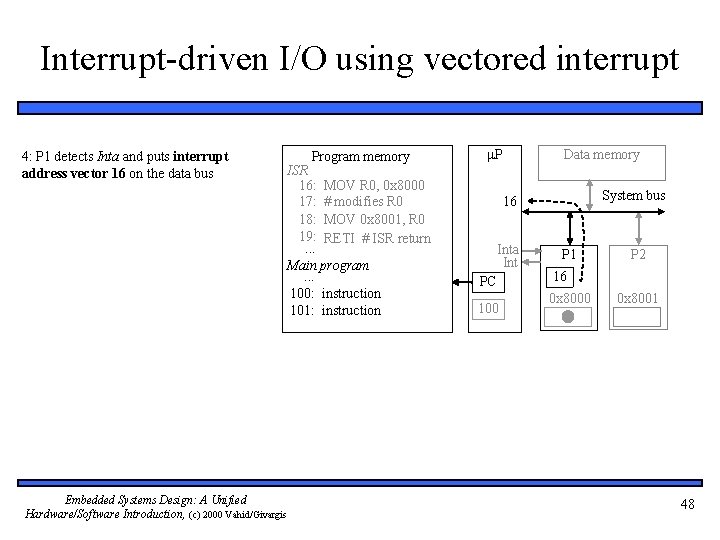

Interrupt-driven I/O using vectored interrupt 4: P 1 detects Inta and puts interrupt address vector 16 on the data bus Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus 16 Inta Int PC 100 P 1 P 2 16 0 x 8000 0 x 8001 48

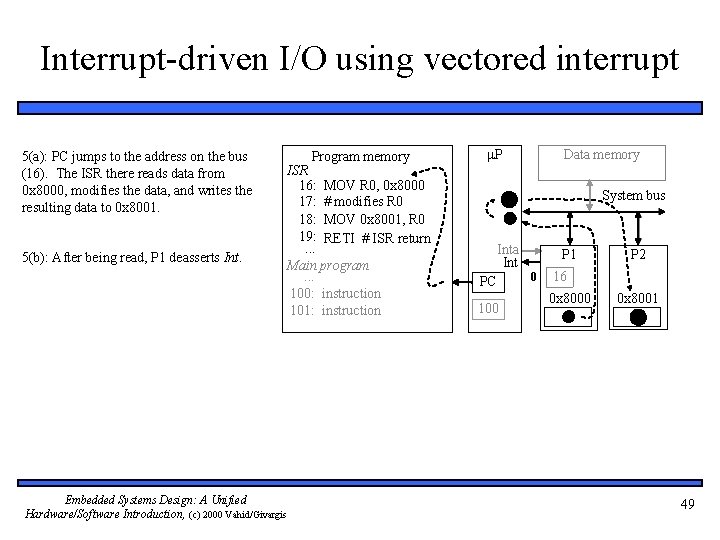

Interrupt-driven I/O using vectored interrupt 5(a): PC jumps to the address on the bus (16). The ISR there reads data from 0 x 8000, modifies the data, and writes the resulting data to 0 x 8001. 5(b): After being read, P 1 deasserts Int. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus Inta Int PC 100 P 1 0 P 2 16 0 x 8000 0 x 8001 49

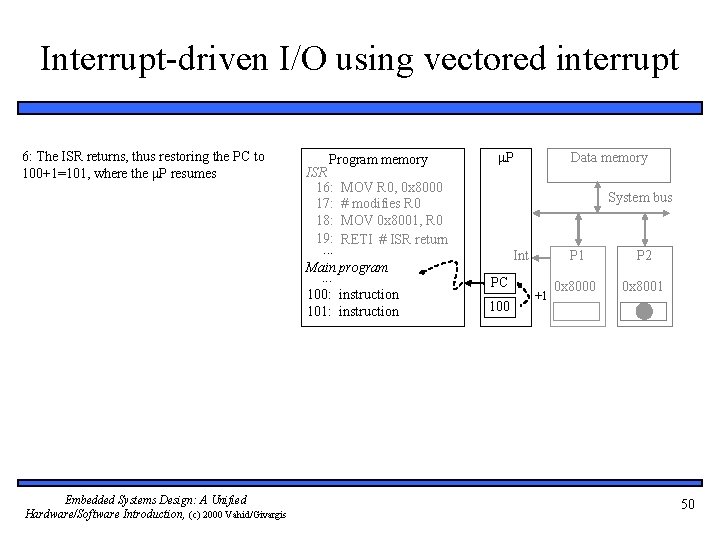

Interrupt-driven I/O using vectored interrupt 6: The ISR returns, thus restoring the PC to 100+1=101, where the μP resumes Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory System bus Int PC 100 +1 P 2 0 x 8000 0 x 8001 50

Interrupt address table • Compromise between fixed and vectored interrupts – One interrupt pin – Table in memory holding ISR addresses (maybe 256 words) – Peripheral doesn’t provide ISR address, but rather index into table • Fewer bits are sent by the peripheral • Can move ISR location without changing peripheral Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 51

Additional interrupt issues • Maskable vs. non-maskable interrupts – Maskable: programmer can set bit that causes processor to ignore interrupt • Important when in the middle of time-critical code – Non-maskable: a separate interrupt pin that can’t be masked • Typically reserved for drastic situations, like power failure requiring immediate backup of data to non-volatile memory • Jump to ISR – Some microprocessors treat jump same as call of any subroutine • Complete state saved (PC, registers) – may take hundreds of cycles – Others only save partial state, like PC only • Thus, ISR must not modify registers, or else must save them first • Assembly-language programmer must be aware of which registers stored Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 52

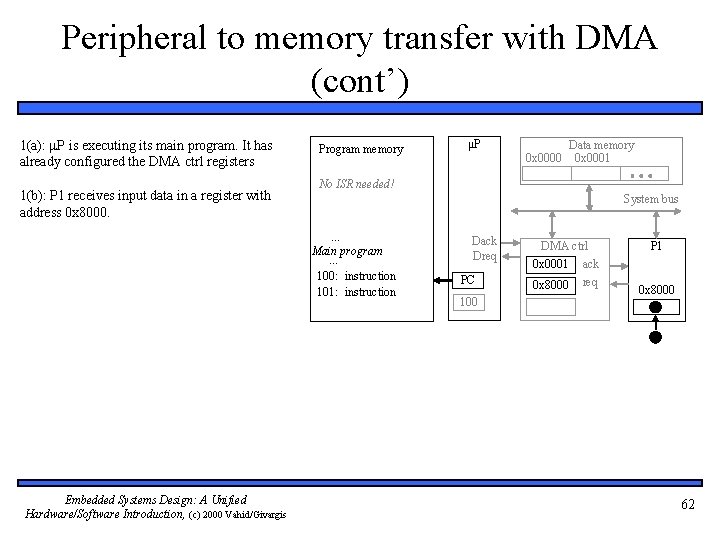

Direct memory access • Buffering – Temporarily storing data in memory before processing – Data accumulated in peripherals commonly buffered • Microprocessor could handle this with ISR – Storing and restoring microprocessor state inefficient – Regular program must wait • DMA controller more efficient – Separate single-purpose processor – Microprocessor relinquishes control of system bus to DMA controller – Microprocessor can meanwhile execute its regular program • No inefficient storing and restoring state due to ISR call • Regular program need not wait unless it requires the system bus – Harvard archictecture – processor can fetch and execute instructions as long as they don’t access data memory – if they do, processor stalls Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 53

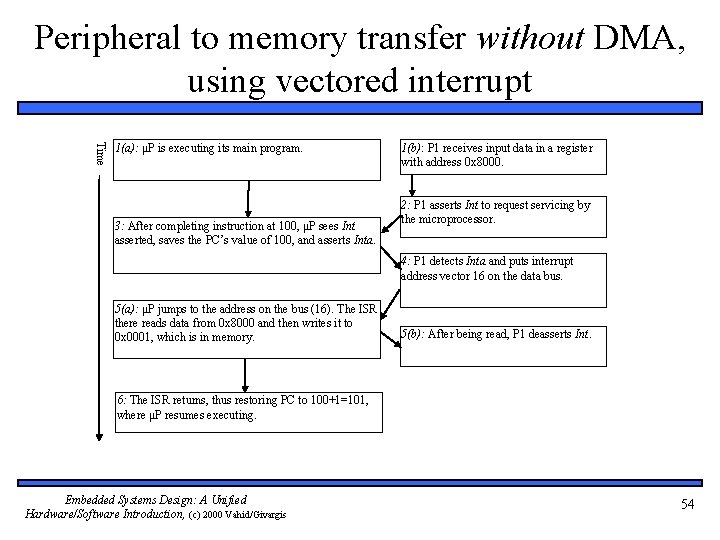

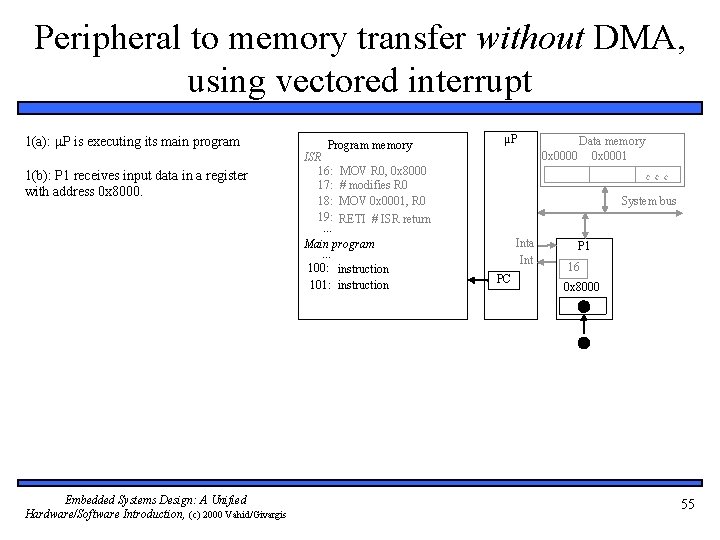

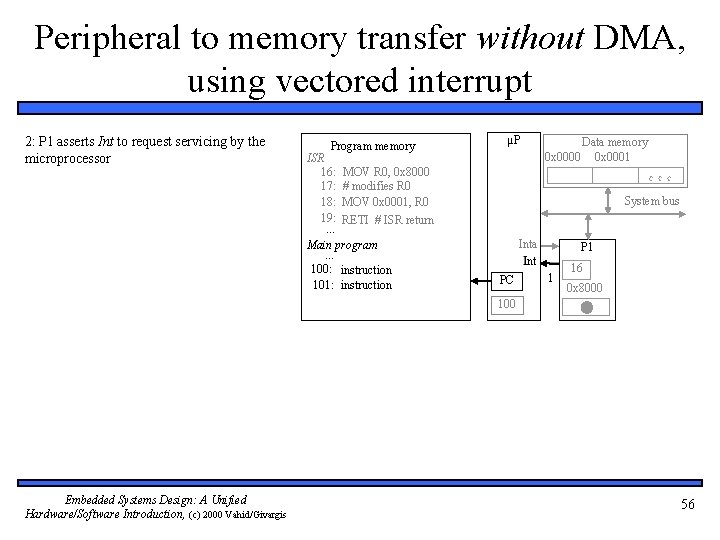

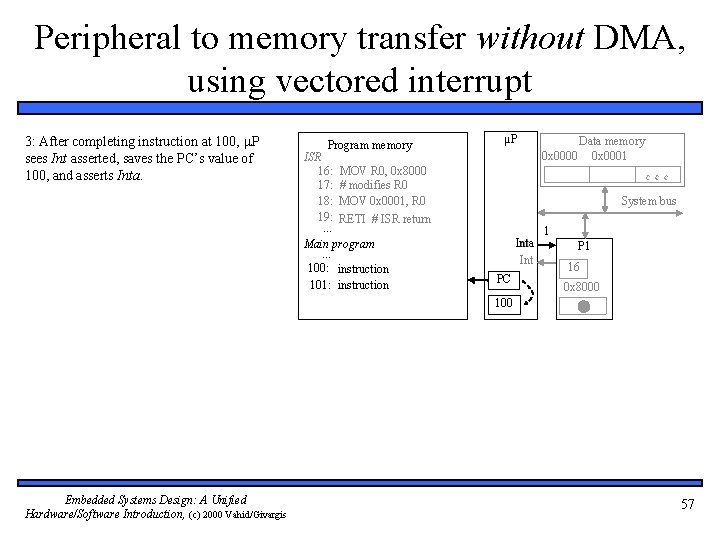

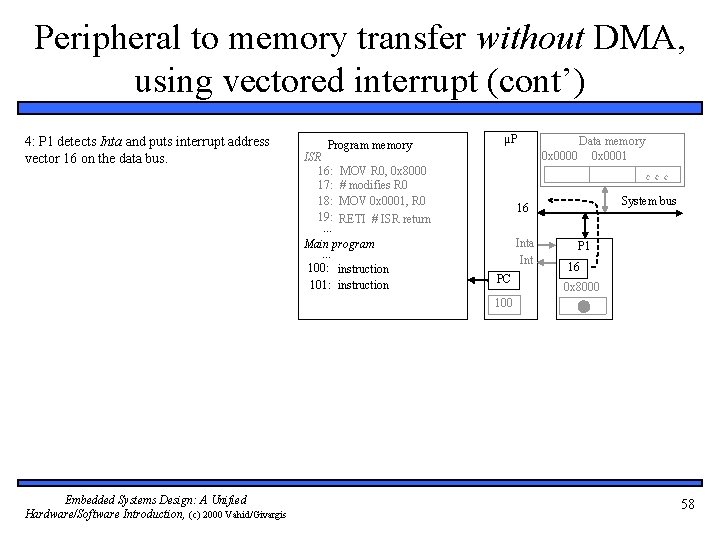

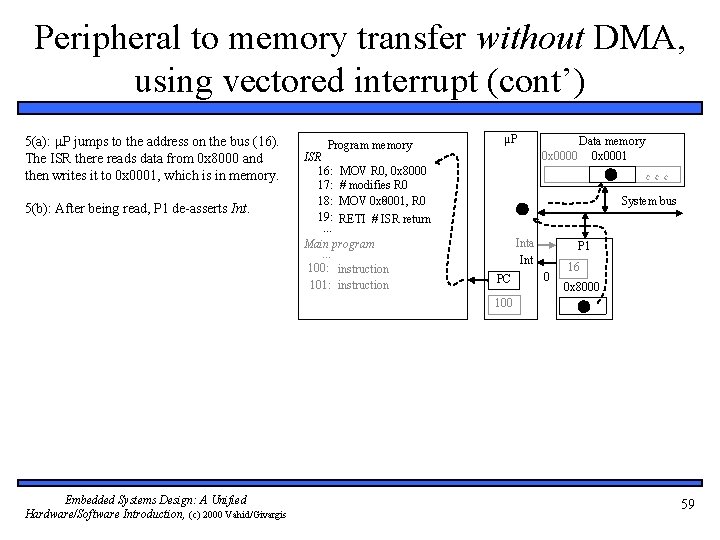

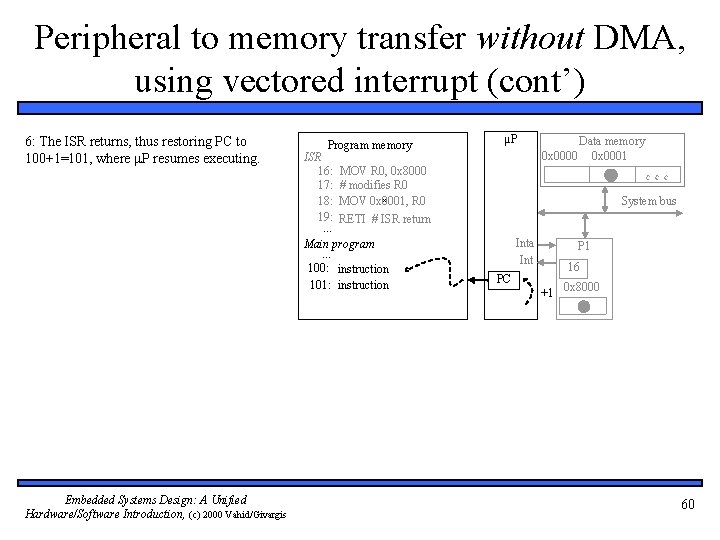

Peripheral to memory transfer without DMA, using vectored interrupt Time 1(a): μP is executing its main program. 3: After completing instruction at 100, μP sees Int asserted, saves the PC’s value of 100, and asserts Inta. 1(b): P 1 receives input data in a register with address 0 x 8000. 2: P 1 asserts Int to request servicing by the microprocessor. 4: P 1 detects Inta and puts interrupt address vector 16 on the data bus. 5(a): μP jumps to the address on the bus (16). The ISR there reads data from 0 x 8000 and then writes it to 0 x 0001, which is in memory. 5(b): After being read, P 1 deasserts Int. 6: The ISR returns, thus restoring PC to 100+1=101, where μP resumes executing. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 54

Peripheral to memory transfer without DMA, using vectored interrupt 1(a): P is executing its main program 1(b): P 1 receives input data in a register with address 0 x 8000. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 0001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory 0 x 0000 0 x 0001 System bus Inta Int PC P 1 16 0 x 8000 55

Peripheral to memory transfer without DMA, using vectored interrupt 2: P 1 asserts Int to request servicing by the microprocessor Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 0001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory 0 x 0000 0 x 0001 System bus Inta Int PC P 1 1 16 0 x 8000 100 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 56

Peripheral to memory transfer without DMA, using vectored interrupt 3: After completing instruction at 100, P sees Int asserted, saves the PC’s value of 100, and asserts Inta. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 0001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory 0 x 0000 0 x 0001 System bus Inta Int PC 1 P 1 16 0 x 8000 100 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 57

Peripheral to memory transfer without DMA, using vectored interrupt (cont’) 4: P 1 detects Inta and puts interrupt address vector 16 on the data bus. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 0001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory 0 x 0000 0 x 0001 System bus 16 Inta Int PC P 1 16 0 x 8000 100 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 58

Peripheral to memory transfer without DMA, using vectored interrupt (cont’) 5(a): P jumps to the address on the bus (16). The ISR there reads data from 0 x 8000 and then writes it to 0 x 0001, which is in memory. 5(b): After being read, P 1 de-asserts Int. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 18: MOV 0 x 0001, 0 x 8001, R 0 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP Data memory 0 x 0000 0 x 0001 System bus Inta Int PC P 1 0 16 0 x 8000 100 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 59

Peripheral to memory transfer without DMA, using vectored interrupt (cont’) 6: The ISR returns, thus restoring PC to 100+1=101, where P resumes executing. Program memory ISR 16: MOV R 0, 0 x 8000 17: # modifies R 0 0 x 0001, R 0 18: MOV 0 x 8001, 19: RETI # ISR return. . . Main program. . . 100: instruction 101: instruction μP System bus Inta Int PC 100 Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Data memory 0 x 0000 0 x 0001 P 1 16 +1 0 x 8000 60

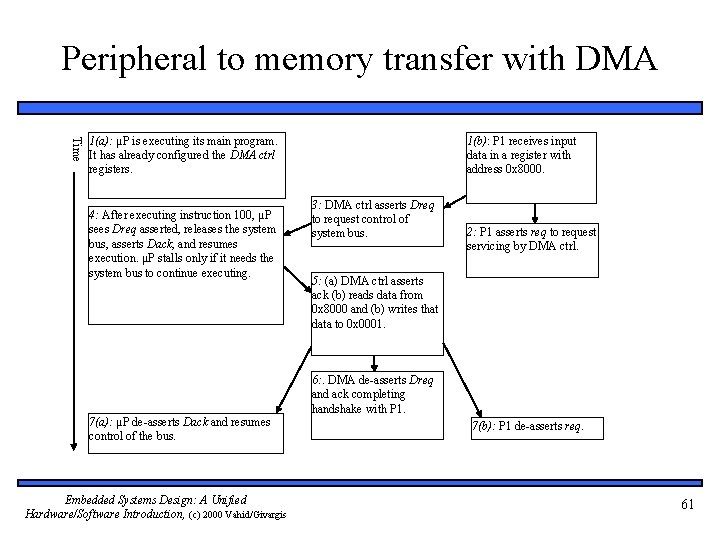

Peripheral to memory transfer with DMA Time 1(a): μP is executing its main program. It has already configured the DMA ctrl registers. 4: After executing instruction 100, μP sees Dreq asserted, releases the system bus, asserts Dack, and resumes execution. μP stalls only if it needs the system bus to continue executing. 7(a): μP de-asserts Dack and resumes control of the bus. Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis 1(b): P 1 receives input data in a register with address 0 x 8000. 3: DMA ctrl asserts Dreq to request control of system bus. 2: P 1 asserts req to request servicing by DMA ctrl. 5: (a) DMA ctrl asserts ack (b) reads data from 0 x 8000 and (b) writes that data to 0 x 0001. 6: . DMA de-asserts Dreq and ack completing handshake with P 1. 7(b): P 1 de-asserts req. 61

Peripheral to memory transfer with DMA (cont’) 1(a): P is executing its main program. It has already configured the DMA ctrl registers 1(b): P 1 receives input data in a register with address 0 x 8000. Program memory 0 x 0000 Data memory 0 x 0001 No ISR needed! System bus. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Dack Dreq PC 100 DMA ctrl 0 x 0001 ack 0 x 8000 req P 1 0 x 8000 62

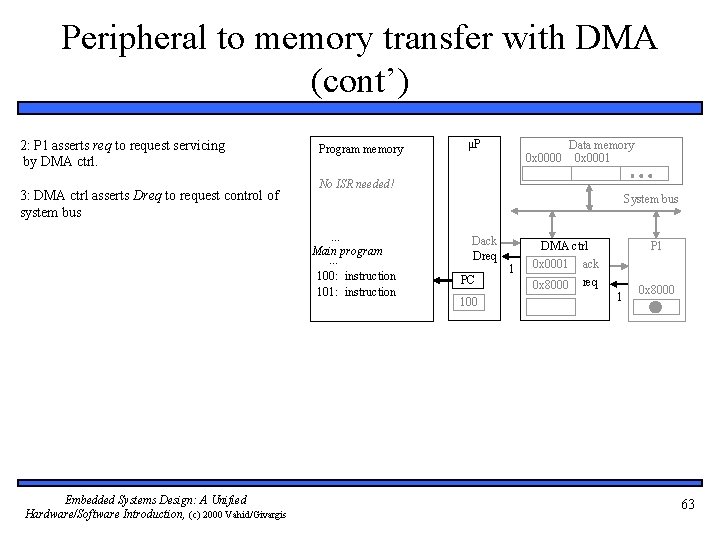

Peripheral to memory transfer with DMA (cont’) 2: P 1 asserts req to request servicing by DMA ctrl. 3: DMA ctrl asserts Dreq to request control of system bus Program memory 0 x 0000 Data memory 0 x 0001 No ISR needed! System bus. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Dack Dreq PC 100 1 DMA ctrl 0 x 0001 ack 0 x 8000 P 1 req 1 0 x 8000 63

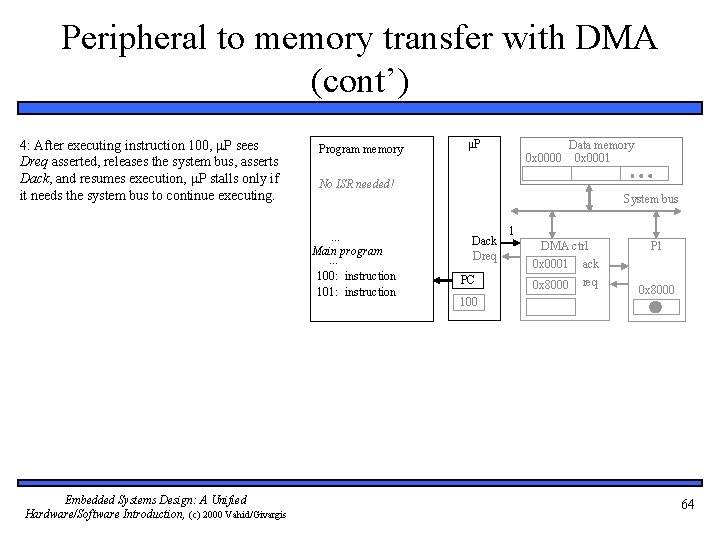

Peripheral to memory transfer with DMA (cont’) 4: After executing instruction 100, P sees Dreq asserted, releases the system bus, asserts Dack, and resumes execution, P stalls only if it needs the system bus to continue executing. Program memory 0 x 0000 Data memory 0 x 0001 No ISR needed! System bus. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis μP Dack Dreq PC 100 1 DMA ctrl 0 x 0001 ack 0 x 8000 req P 1 0 x 8000 64

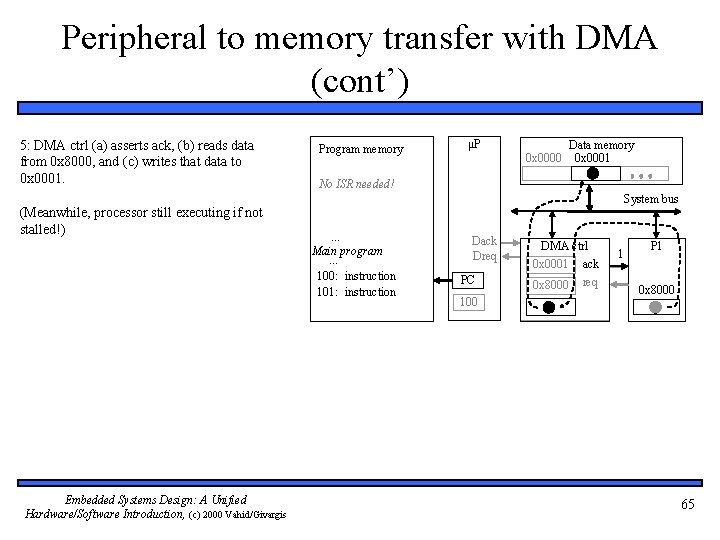

Peripheral to memory transfer with DMA (cont’) 5: DMA ctrl (a) asserts ack, (b) reads data from 0 x 8000, and (c) writes that data to 0 x 0001. (Meanwhile, processor still executing if not stalled!) Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Program memory μP Data memory 0 x 0001 0 x 0000 No ISR needed! System bus. . . Main program. . . 100: instruction 101: instruction Dack Dreq PC 100 DMA ctrl 0 x 0001 ack 0 x 8000 req 1 P 1 0 x 8000 65

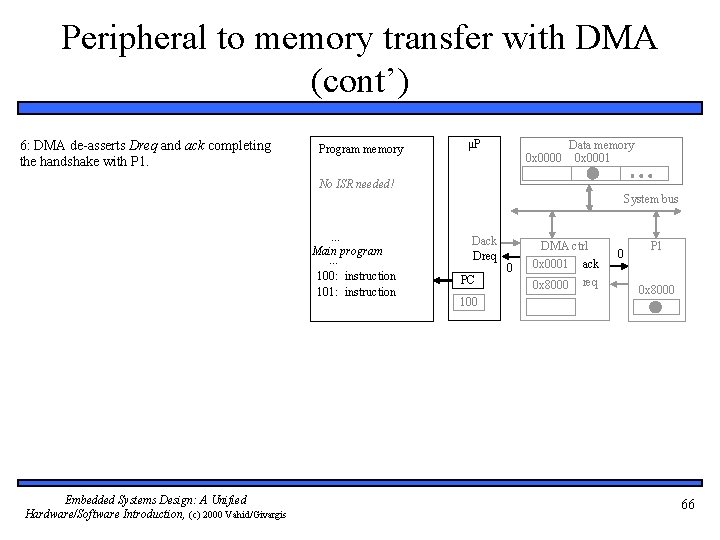

Peripheral to memory transfer with DMA (cont’) 6: DMA de-asserts Dreq and ack completing the handshake with P 1. Program memory μP 0 x 0000 Data memory 0 x 0001 No ISR needed! System bus. . . Main program. . . 100: instruction 101: instruction Embedded Systems Design: A Unified Hardware/Software Introduction, (c) 2000 Vahid/Givargis Dack Dreq PC 100 0 DMA ctrl 0 x 0001 ack 0 x 8000 req 0 P 1 0 x 8000 66

- Slides: 66