Embedded System Lab DFTL A Flash Translation Layer

Embedded System Lab. DFTL : A Flash Translation Layer Employing Demand-based Selective Caching of Page-level Address Mappings Gupta, Aayush, Youngjae Kim, and Bhuvan Urgaonkar. Vol. 44. No. 3. ASPLOS 2009. 2019. 10. 21 Presentation by Choi, Gunhee choi_gunhee@dankook. ac. kr

Embedded System Lab. Content 1. Flash Translation Layer 2. Problem 3. DFTL 4. Evaluations 5. Conclusions 2

1. Flash Translation Layer Embedded System Lab. 3

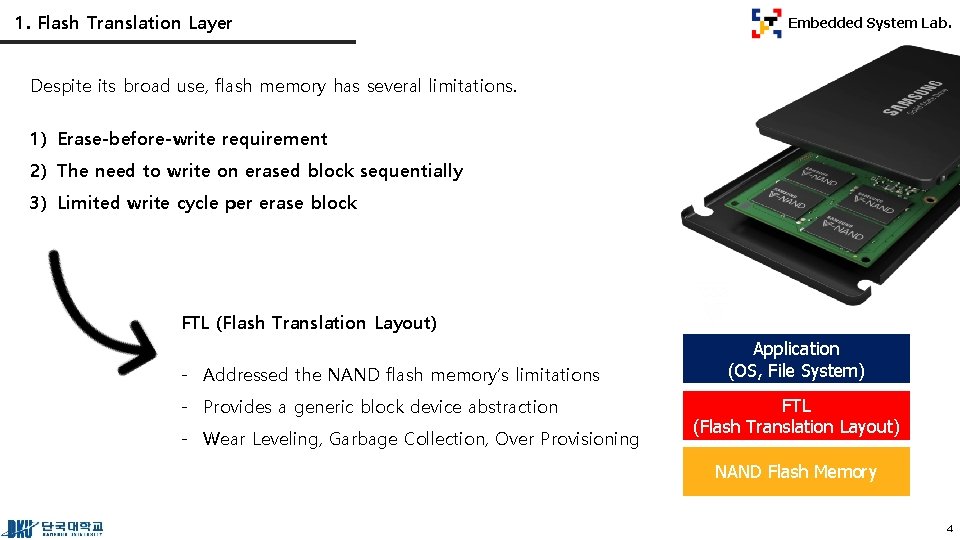

1. Flash Translation Layer Embedded System Lab. Despite its broad use, flash memory has several limitations. 1) Erase-before-write requirement 2) The need to write on erased block sequentially 3) Limited write cycle per erase block FTL (Flash Translation Layout) - Addressed the NAND flash memory’s limitations - Provides a generic block device abstraction - Wear Leveling, Garbage Collection, Over Provisioning Application (OS, File System) FTL (Flash Translation Layout) NAND Flash Memory 4

1. Flash Translation Layer Embedded System Lab. The Design of Flash Translation Layer Improve Performance 5

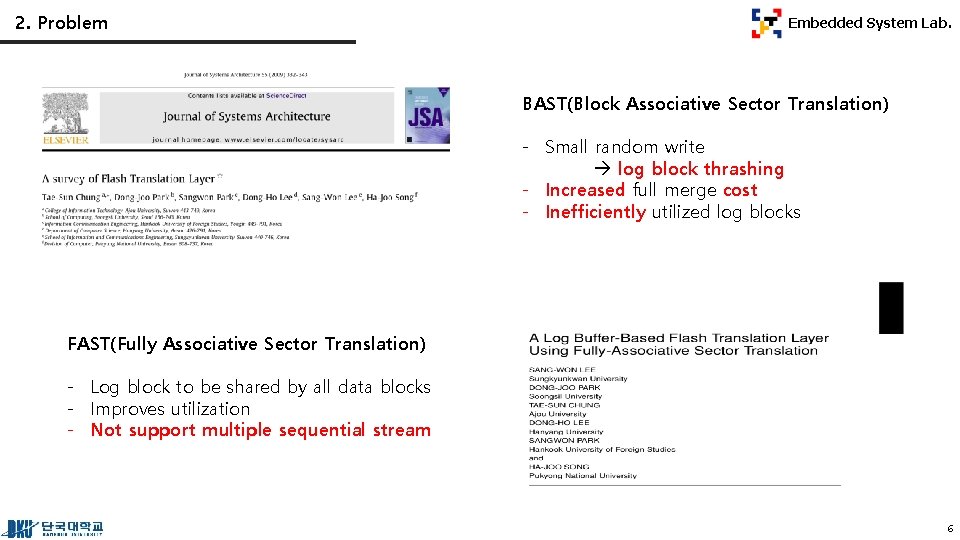

2. Problem Embedded System Lab. BAST(Block Associative Sector Translation) - Small random write log block thrashing - Increased full merge cost - Inefficiently utilized log blocks FAST(Fully Associative Sector Translation) - Log block to be shared by all data blocks - Improves utilization - Not support multiple sequential stream 6

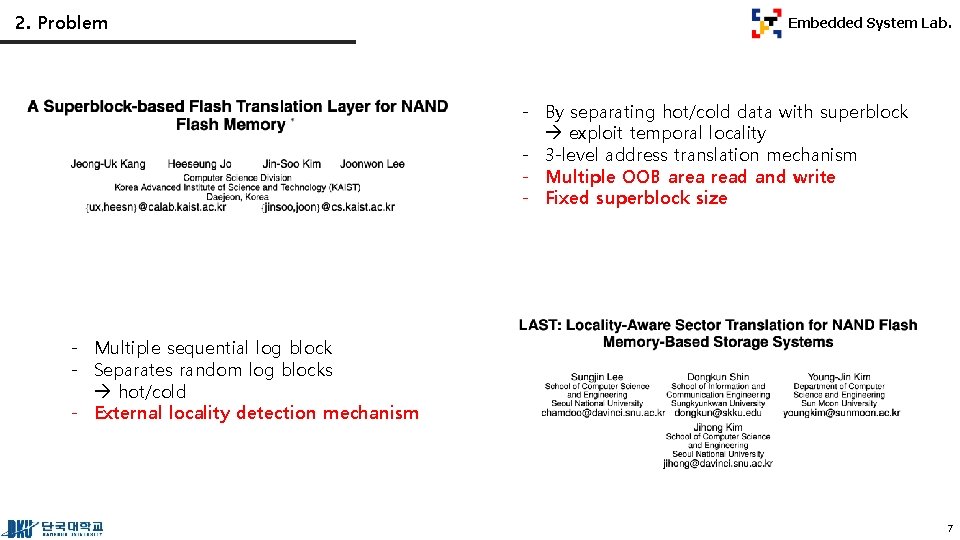

2. Problem Embedded System Lab. - By separating hot/cold data with superblock exploit temporal locality - 3 -level address translation mechanism - Multiple OOB area read and write - Fixed superblock size - Multiple sequential log block - Separates random log blocks hot/cold - External locality detection mechanism 7

2. Problem Embedded System Lab. The Problem is Money Hybrid FTL 8

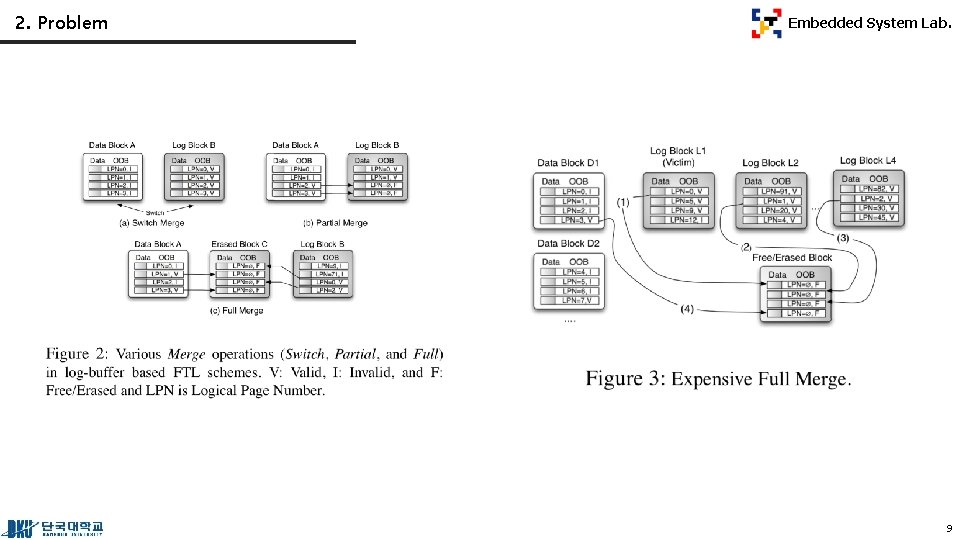

2. Problem Embedded System Lab. 9

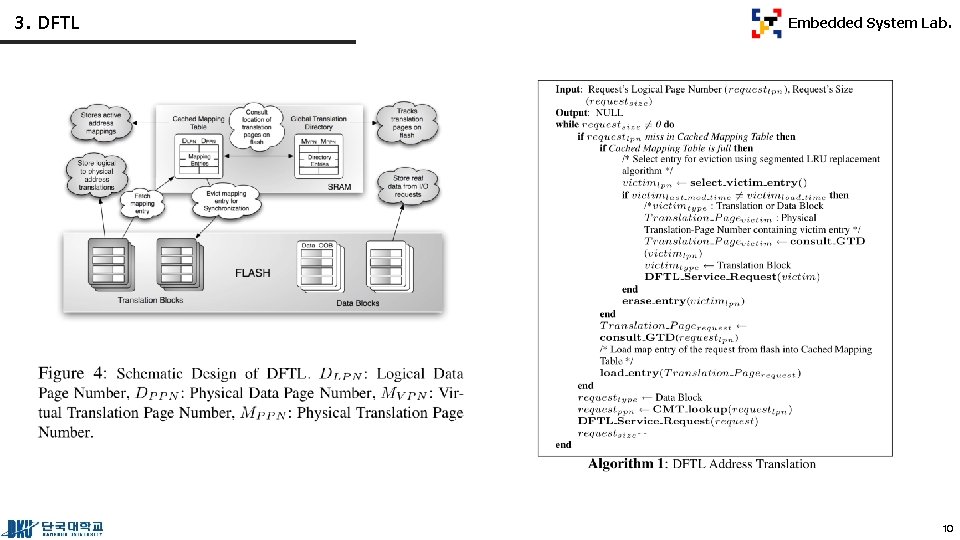

3. DFTL Embedded System Lab. 10

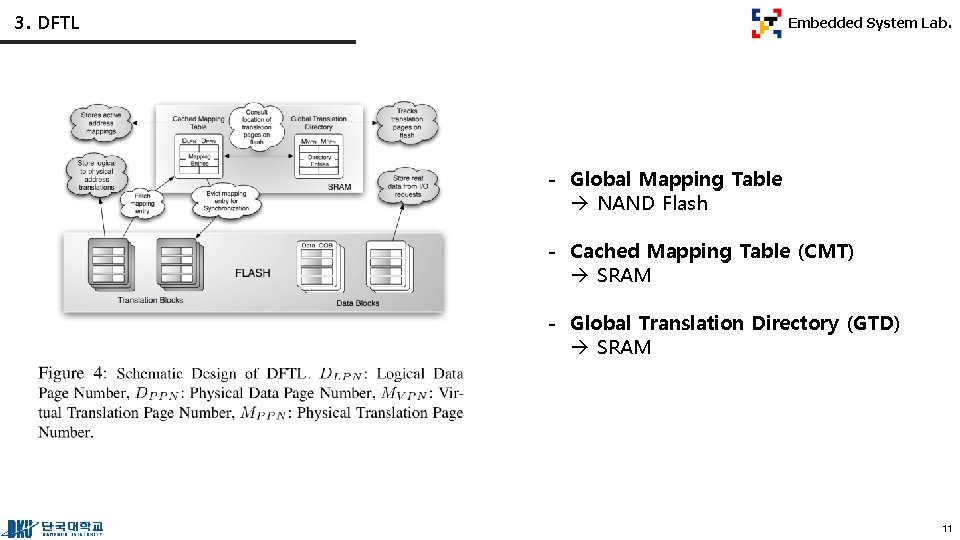

3. DFTL Embedded System Lab. - Global Mapping Table NAND Flash - Cached Mapping Table (CMT) SRAM - Global Translation Directory (GTD) SRAM 11

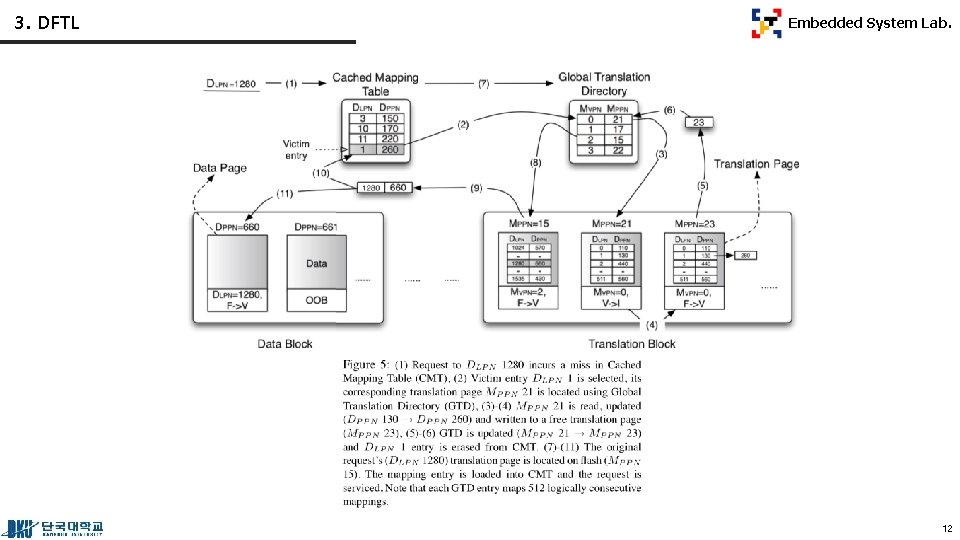

3. DFTL Embedded System Lab. 12

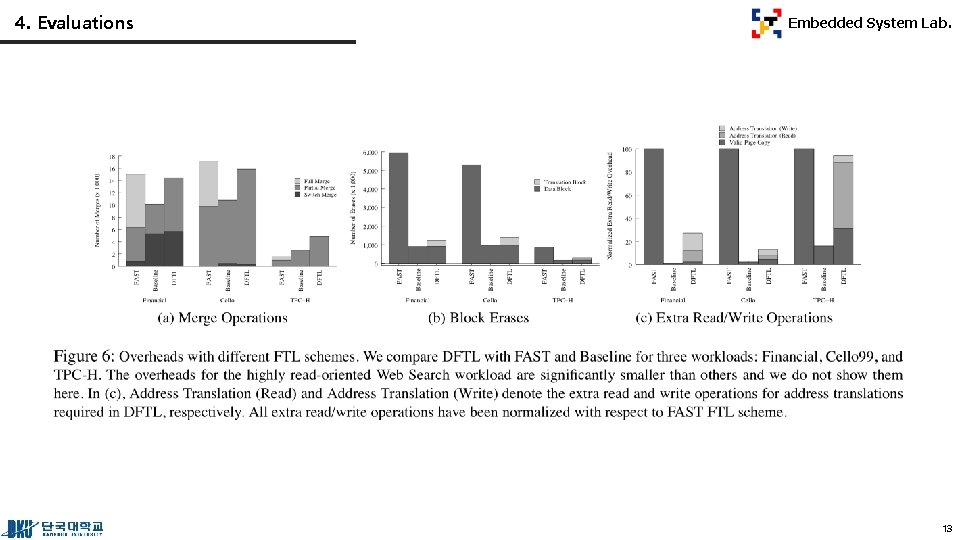

4. Evaluations Embedded System Lab. 13

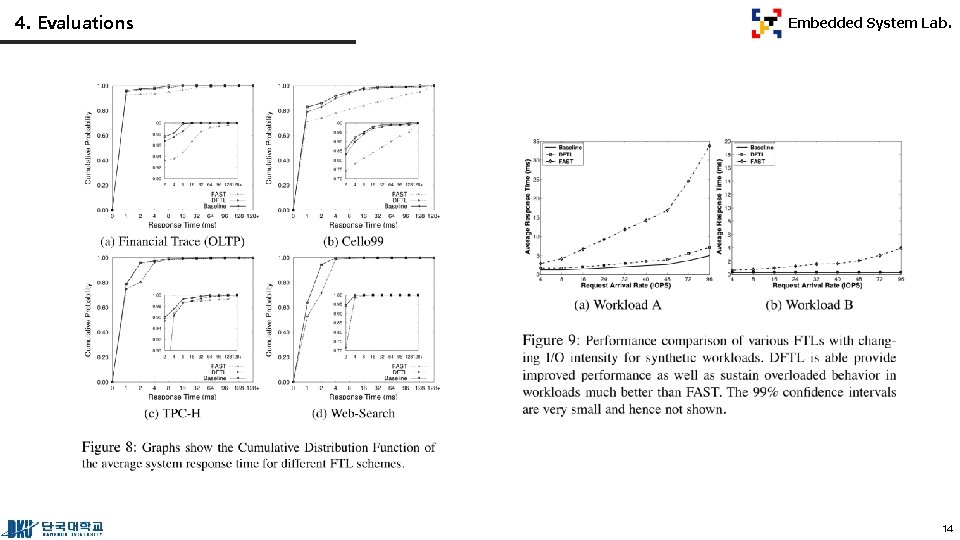

4. Evaluations Embedded System Lab. 14

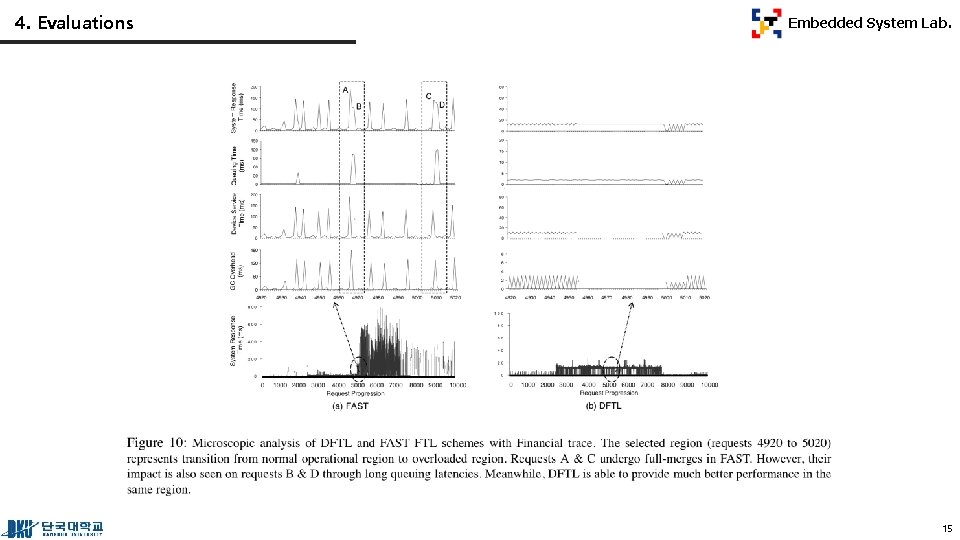

4. Evaluations Embedded System Lab. 15

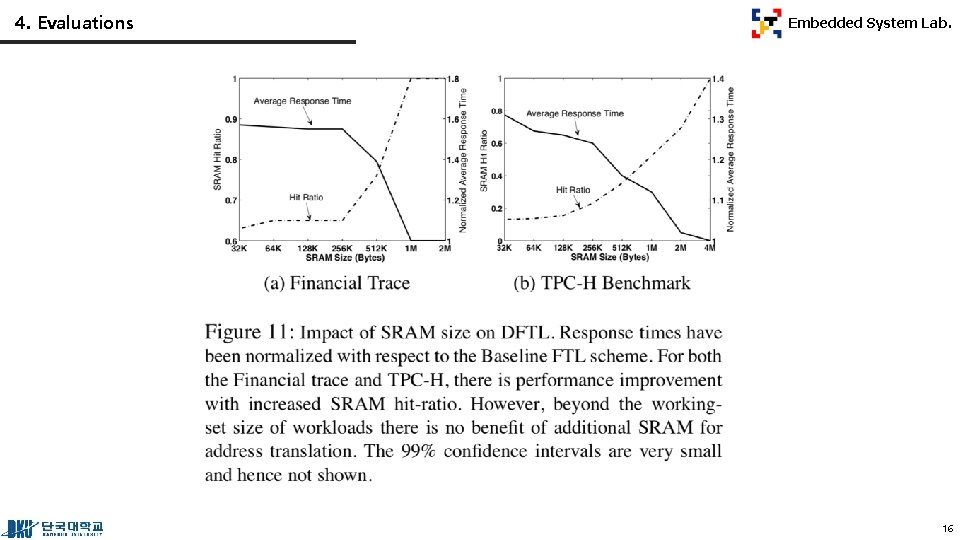

4. Evaluations Embedded System Lab. 16

5. Conclusions Embedded System Lab. • Proposed Demand-base Flash Translation Layer (DFTL) • Page-mapping FTL • Improved performance • Reduce GC overhead • Show 78% improvement in average response time 17

Embedded System Lab. DFTL : A Flash Translation Layer Employing Demand-based Selective Caching of Page-level Address Mappings Gupta, Aayush, Youngjae Kim, and Bhuvan Urgaonkar. Vol. 44. No. 3. ASPLOS 2009. Thank You! 2019. 10. 21 Presentation by Choi, Gunhee choi_gunhee@dankook. ac. kr

- Slides: 18