Embedded System Lab A Software Memory Partition Approach

Embedded System Lab. A Software Memory Partition Approach for Eliminating Bank-level Interference in Multicore Systems Lei Liu, Zehan Cui, Mingjie Xing, Yungang Bao, Mingyu Chen, Chengyong Wu Kilmo Choi rlfah 926@naver. com 최길모 Embedded System Lab.

Contents l Background and Motivation l Bank-Level Partition Mechanism(BPM) l Results l Conclusion l Reference 최길모 Embedded System Lab.

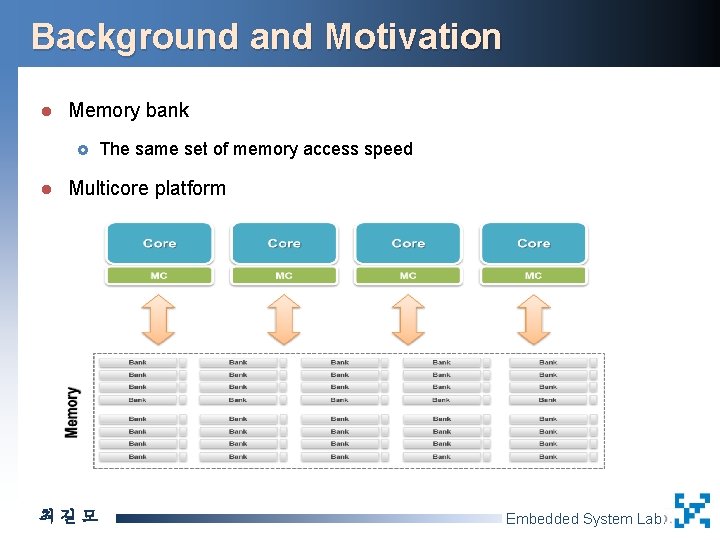

Background and Motivation l Memory bank £ l The same set of memory access speed Multicore platform 최길모 Embedded System Lab.

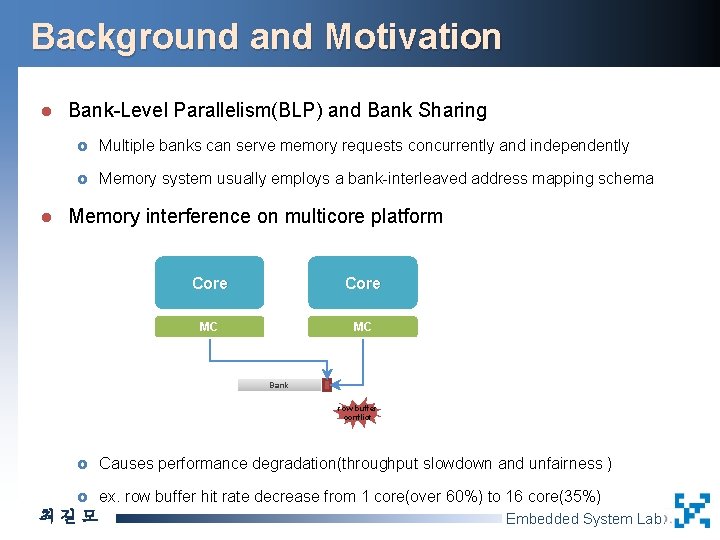

Background and Motivation l l Bank-Level Parallelism(BLP) and Bank Sharing £ Multiple banks can serve memory requests concurrently and independently £ Memory system usually employs a bank-interleaved address mapping schema Memory interference on multicore platform Core MC MC Bank row buffer conflict £ Causes performance degradation(throughput slowdown and unfairness ) £ ex. row buffer hit rate decrease from 1 core(over 60%) to 16 core(35%) 최길모 Embedded System Lab.

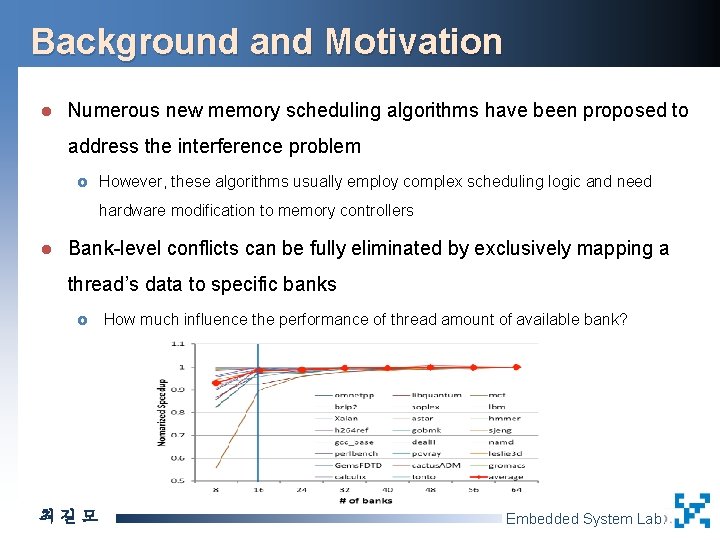

Background and Motivation l Numerous new memory scheduling algorithms have been proposed to address the interference problem £ However, these algorithms usually employ complex scheduling logic and need hardware modification to memory controllers l Bank-level conflicts can be fully eliminated by exclusively mapping a thread’s data to specific banks £ 최길모 How much influence the performance of thread amount of available bank? Embedded System Lab.

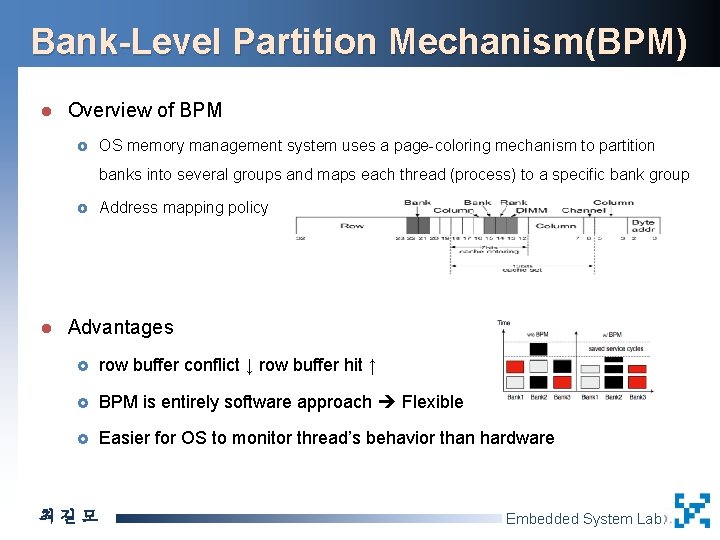

Bank-Level Partition Mechanism(BPM) l Overview of BPM £ OS memory management system uses a page-coloring mechanism to partition banks into several groups and maps each thread (process) to a specific bank group £ l Address mapping policy Advantages £ row buffer conflict ↓ row buffer hit ↑ £ BPM is entirely software approach Flexible £ Easier for OS to monitor thread’s behavior than hardware 최길모 Embedded System Lab.

Bank-Level Partition Mechanism(BPM) l Discover bank bits by software method 최길모 Embedded System Lab.

Results l Environments £ 4 cores, 2. 8 GHz Intel Core i 7 -860 processor, 8 GB DDR 3 main memory £ Cent. OS Linux 5. 4 with kernel 2. 6. 32. 15 £ SPEC CPU 2006 최길모 Embedded System Lab.

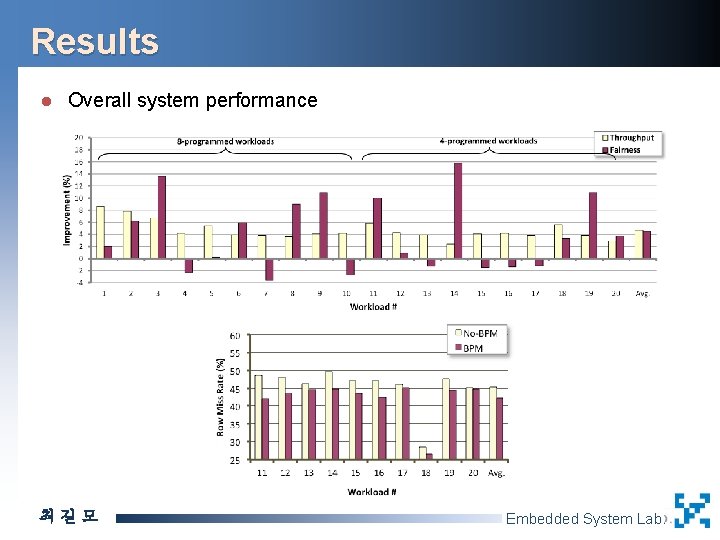

Results l Overall system performance 최길모 Embedded System Lab.

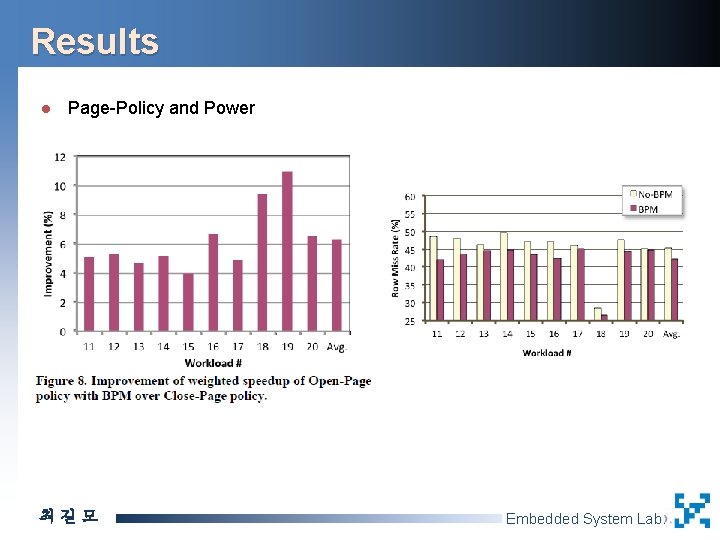

Results l Page-Policy and Power 최길모 Embedded System Lab.

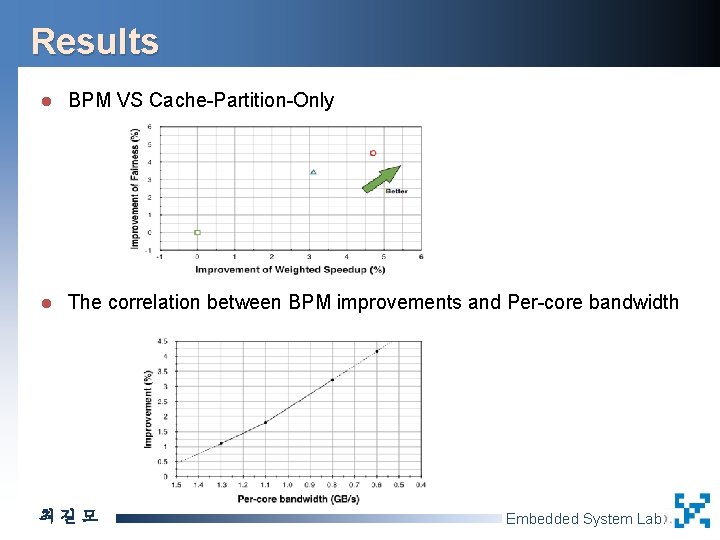

Results l BPM VS Cache-Partition-Only l The correlation between BPM improvements and Per-core bandwidth 최길모 Embedded System Lab.

Reference l J. Lin, Q. Lu, X. Ding, Z. Zhang, X. Zhang, and P. Sadayappan. Gaining Insights into Multicore Cache Partitioning: Bridging the Gap between Simulation and Real Systems. In HPCA-14, 2008. l Dimitris Kaseridis, Jeffrey Stuecheli, Lizy Kurian John. Minimalist Open-page: A DRAM Page-mode Scheduling Policy for the Many-core Era. In MICRO 44, 2011 최길모 Embedded System Lab.

- Slides: 12