Embedded Network Interface ENI What is ENI Embedded

Embedded Network Interface (ENI)

What is ENI? • Embedded Network Interface • Originally called DPO (Digital Product Option) card • Printer without network capability into interface with our network card • Enable an external device with a processor to interface the NET+ARM • The interface is used as a bridge to the LAN

More About ENI • Allows sharing of NET+ARM’s memory system • Useful for dual processor system • Second Processor must push / pull data – NET+ARM is a slave in ENI mode • Can use either FIFO mode or Shared Ram mode – FIFO is fast, but have less control over data – Shared RAM is slower, but have more control – ENI must become BUS Master to use Shared RAM • ENI is muxed with Parallel Ports (one or the other)

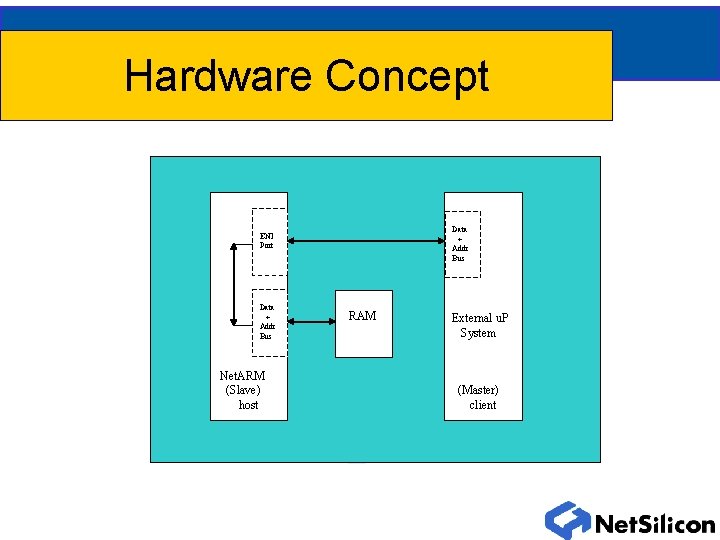

Hardware Concept Data + Addr Bus ENI Port Data + Addr Bus Net. ARM (Slave) host RAM External u. P System (Master) client

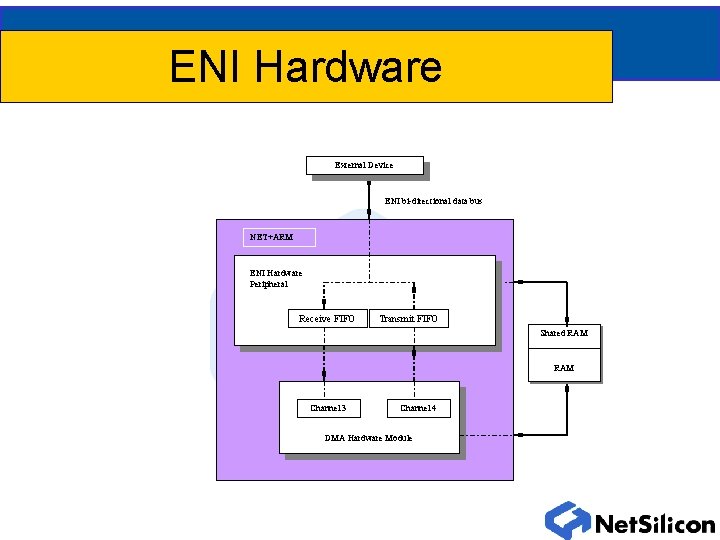

ENI Hardware External Device ENI bi-directional data bus NET+ARM ENI Hardware Peripheral Receive FIFO Transmit FIFO Shared RAM Channel 3 Channel 4 DMA Hardware Module

New GPIO ports on NET+50 • ENI module in GPIO mode provides four 8 -bit GPIO ports • Two ports are I/O ports (Port D and Port F) and two ports are input ports (Port G and Port H) • GPIO port pins are individually configurable to input, output, active high interrupt or active low interrupt • Interrupts are level sensitive

GPIO Port Interrupts on NET+50 • • Port D uses interrupt 21 (ENI port 1) Port F uses interrupt 20 (ENI port 2) Port G uses interrupt 19 (ENI port 3) Port H uses interrupt 18 (ENI port 4)

Modes of Operation • ENI Shared RAM – 16 bit interface • ENI Shared RAM – 8 bit interface • ENI FIFO – 16 interface with 8 K Shared memory • ENI FIFO – 8 interface with 8 K Shared memory

Shared RAM Mode • Allow external device (client) to random access external memory which is controlled by the NET+ARM (host) • 8/16 -bit interface • Size of Shared RAM is can be one of the following – 4 K, 8 K, 16. 32, or 64 K • Location of RAM must be a multiple of the size selected – E. g. ram size of 8 k must on located on a 8 k boundary

FIFO Mode • Data-streaming interface between the NET+ARM and the external device • 8/16 -bit interface • Two 32 -byte FIFOs used to transmit and receive data • DMA 3 is used to transfer receive data from FIFO to external memory • DMA 4 is used to transfer transmit data from external memory to FIFO • DMA buffers must start and end on a 32 -bit boundary • Data must be padded to conform to buffer requirement • 8 K of shared memory can be accessed

- Slides: 10