Embedded microcomputer systems design Communication interfaces and protocols

Embedded microcomputer systems design Communication interfaces and protocols in embedded systems M. Stojcev Faculty of Electronic Engineering Nis, Serbia 23 -27 June 2014, Skopje

Outline q Embedded systems definition and applications q Hardware structure of embedded system, So. C and MPSo. C q Types of embedded processors q Interconnect q Data transfer types q I 2 C q RS 232 q SPI

What are embedded systems? q Embedded systems are electronic systems that execute a limited number of fixed tasks. q Because the tasks do not change during the lifespan of an embedded system, it is not general programmable in the way that a personal computer or workstation is. q Examples of embedded systems are controller in washing machine or in a compact disk player, the automatic pilot in an aircraft, the controller of a robot arm.

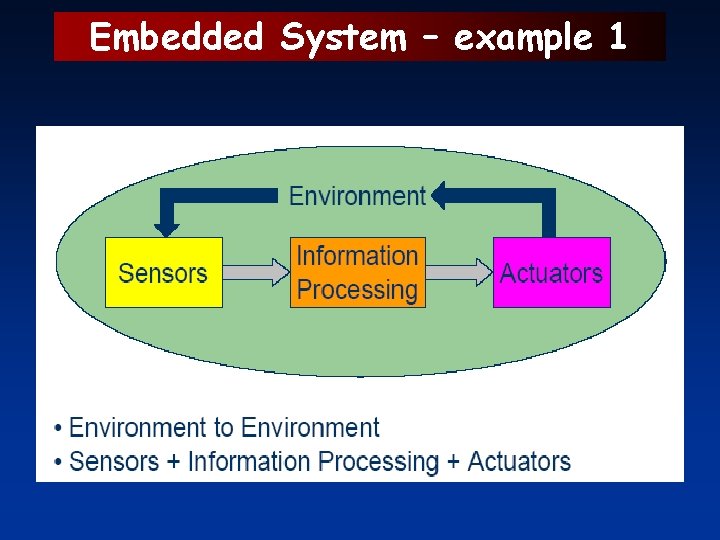

Embedded System – example 1

Embedded Systems – examples 2

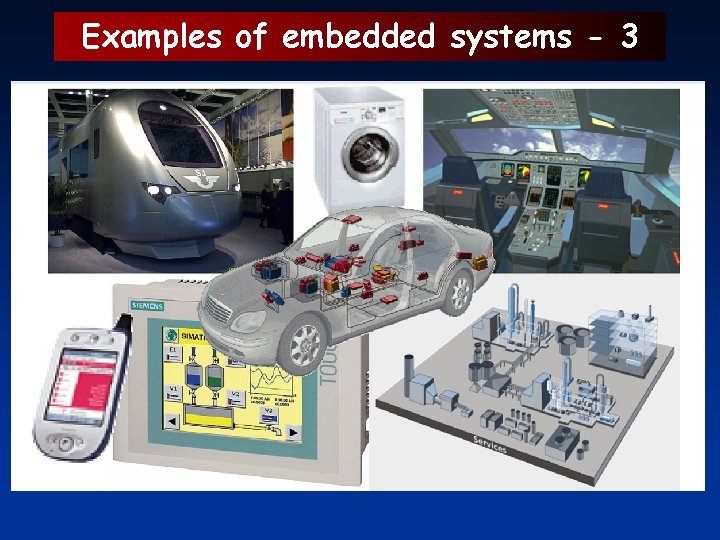

Examples of embedded systems - 3

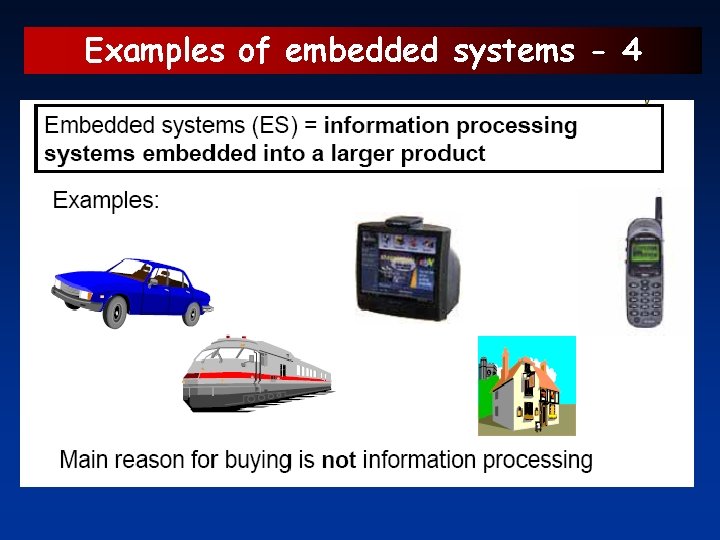

Examples of embedded systems - 4

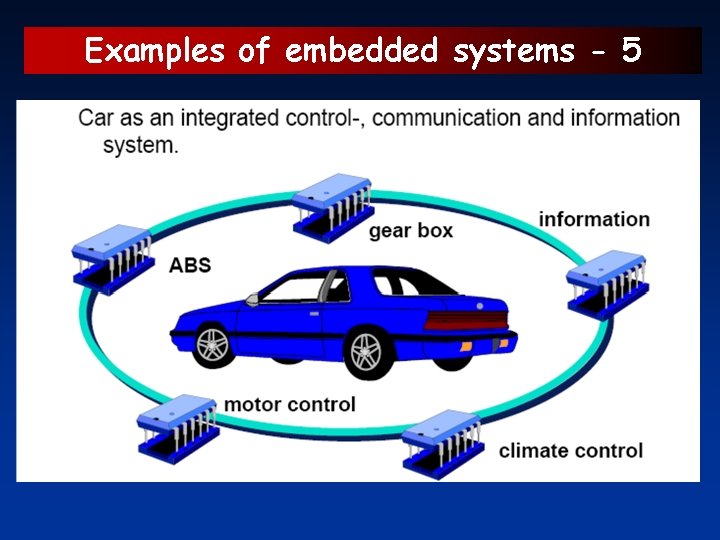

Examples of embedded systems - 5

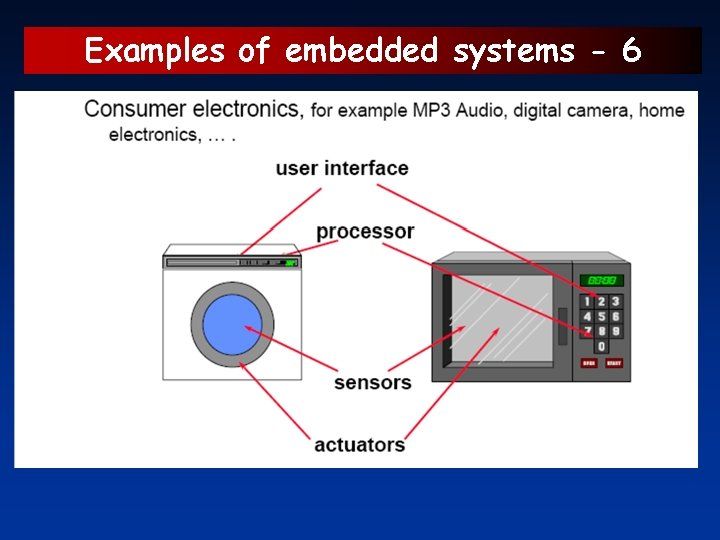

Examples of embedded systems - 6

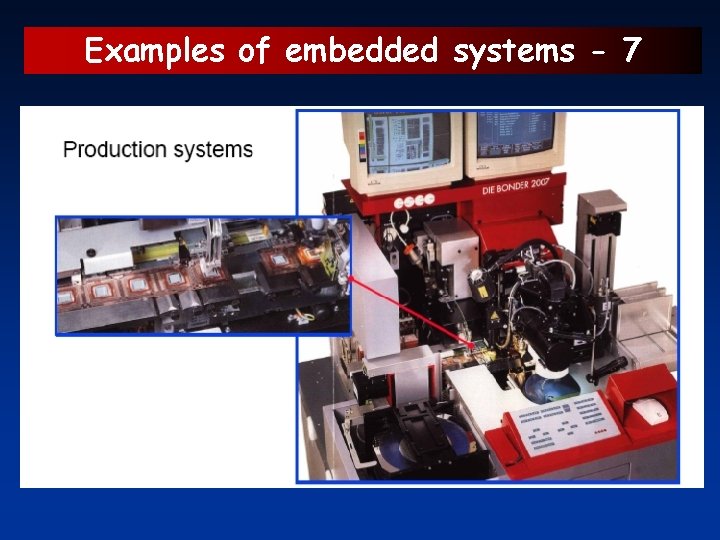

Examples of embedded systems - 7

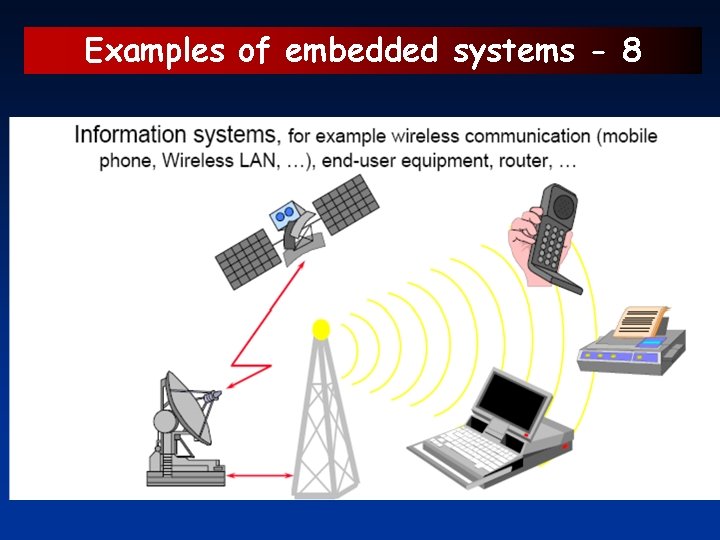

Examples of embedded systems - 8

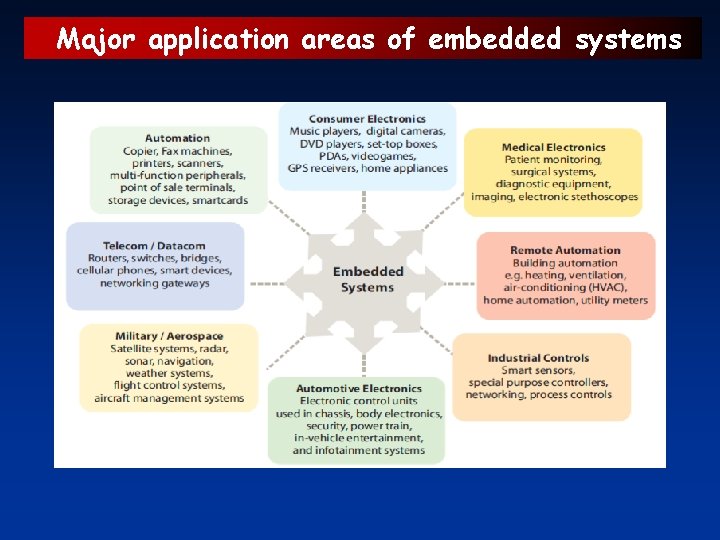

Major application areas of embedded systems

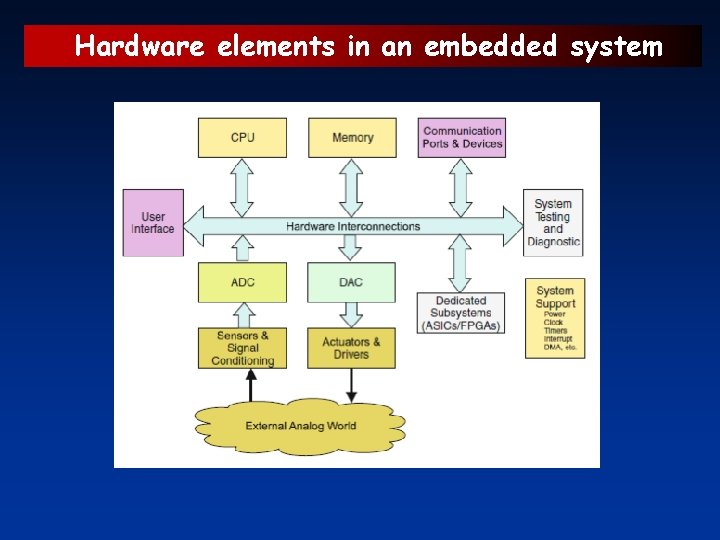

Hardware elements in an embedded system

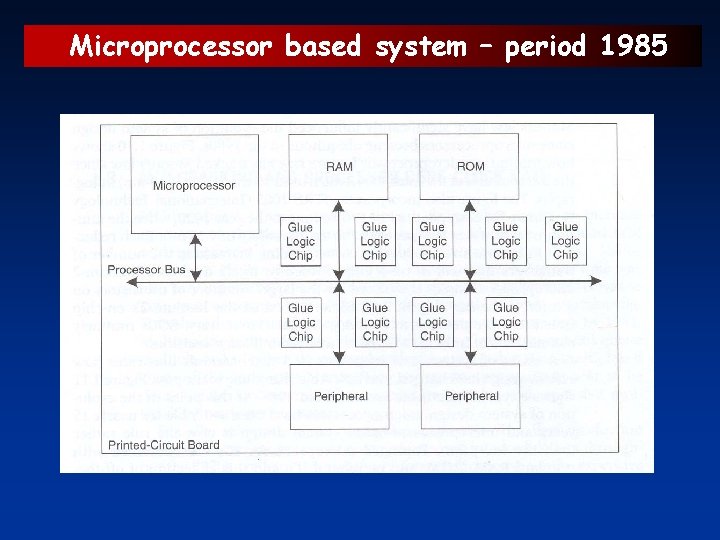

Microprocessor based system – period 1985

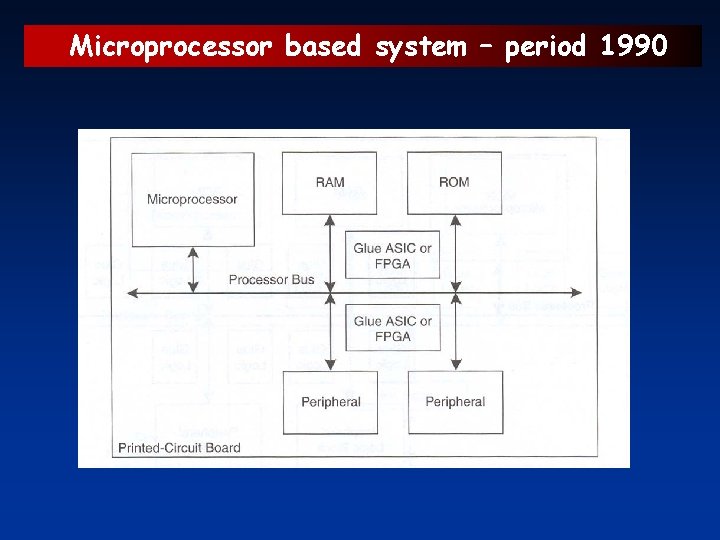

Microprocessor based system – period 1990

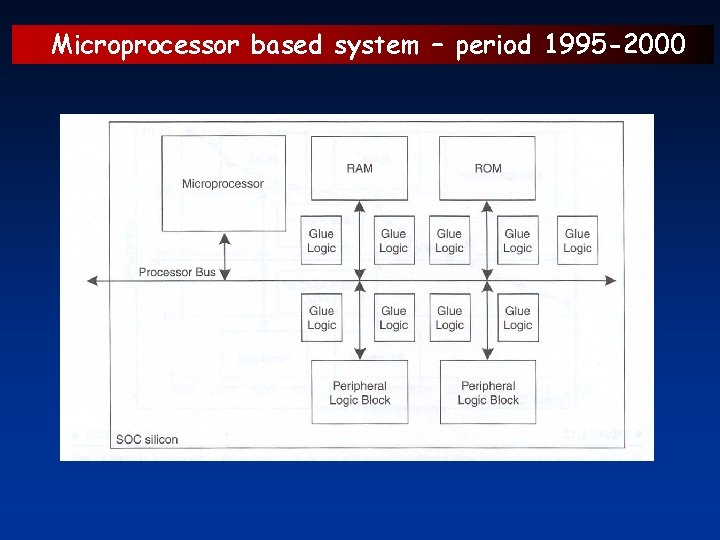

Microprocessor based system – period 1995 -2000

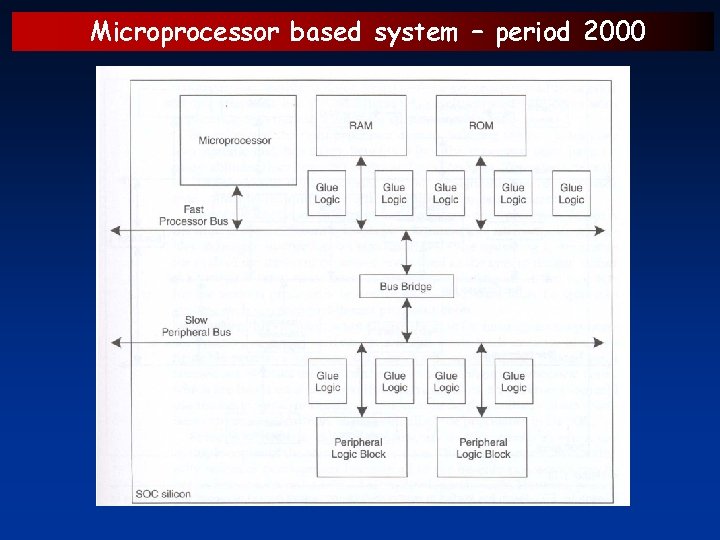

Microprocessor based system – period 2000

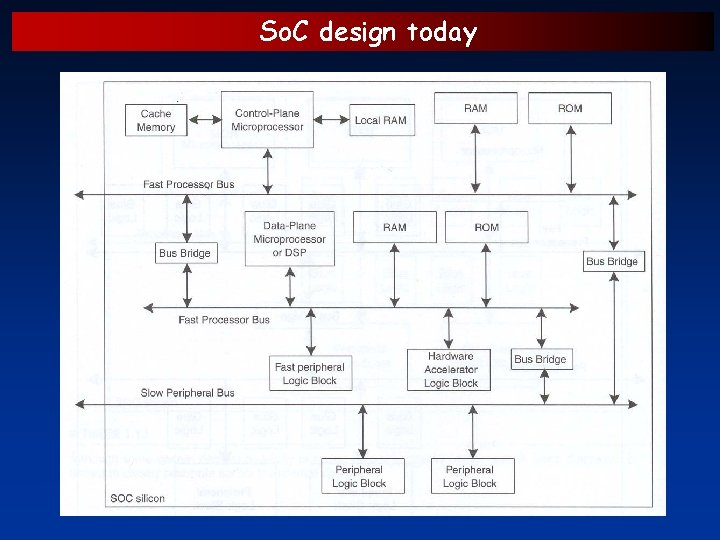

So. C design today

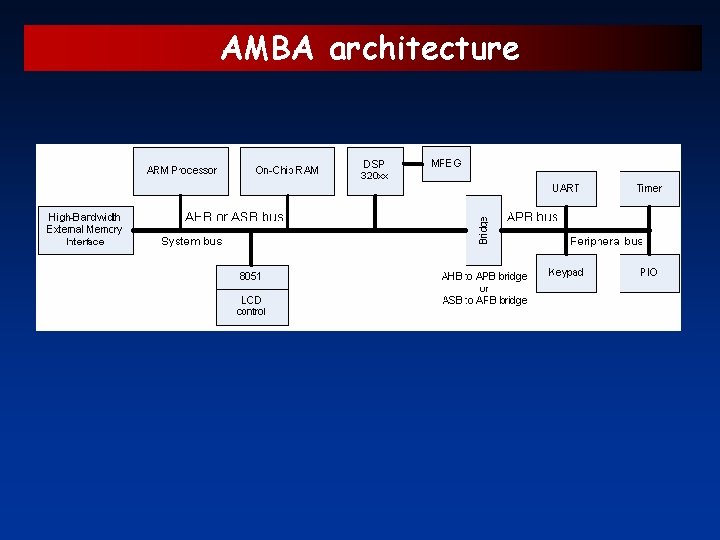

AMBA architecture

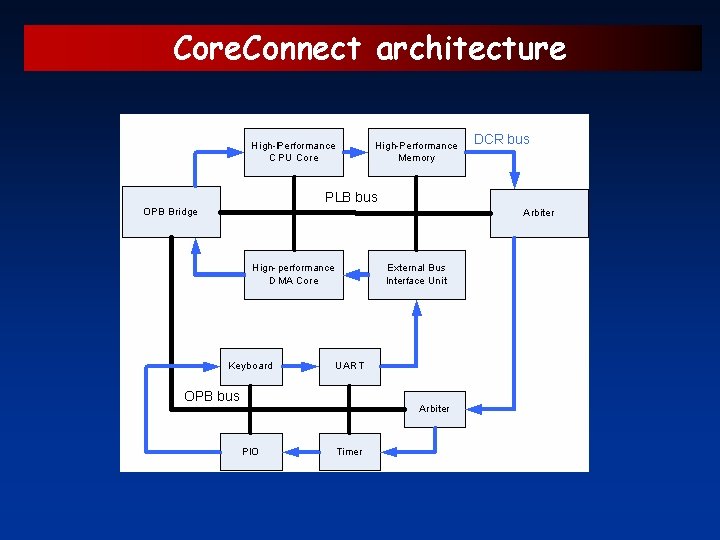

Core. Connect architecture

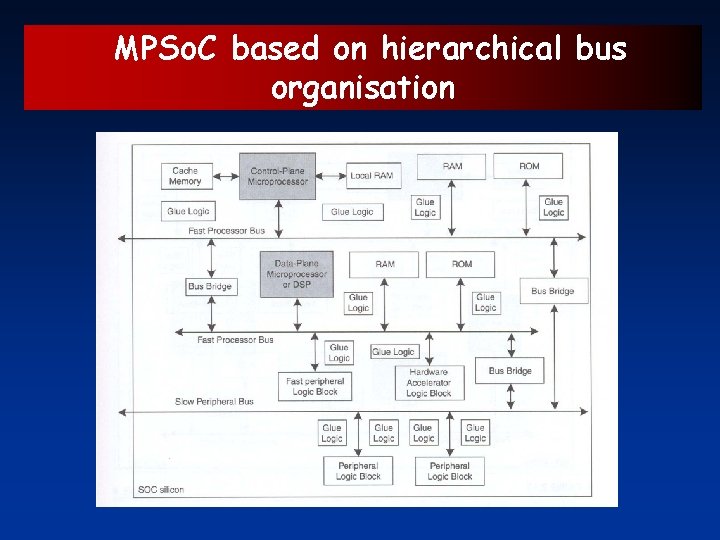

MPSo. C based on hierarchical bus organisation

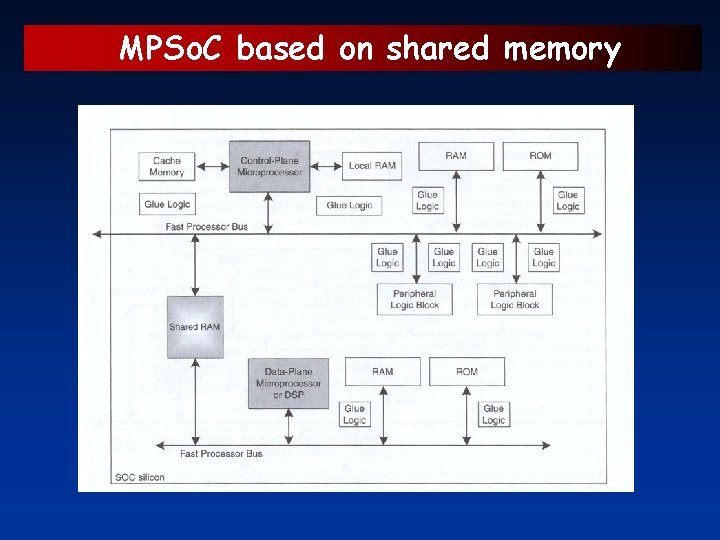

MPSo. C based on shared memory

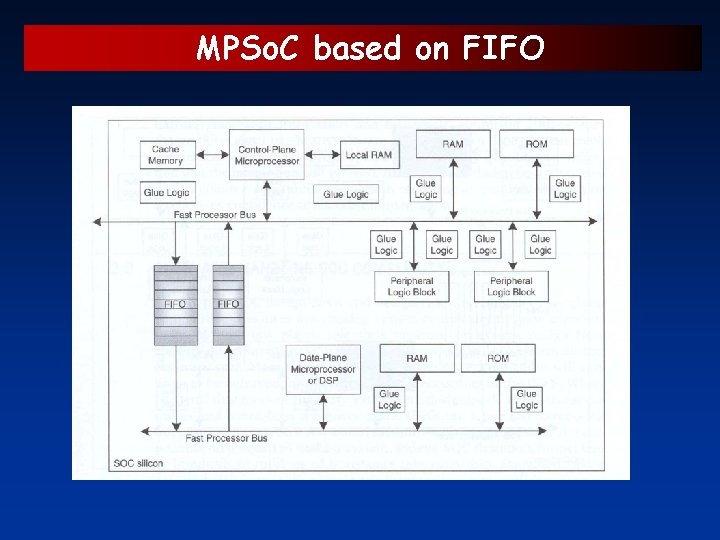

MPSo. C based on FIFO

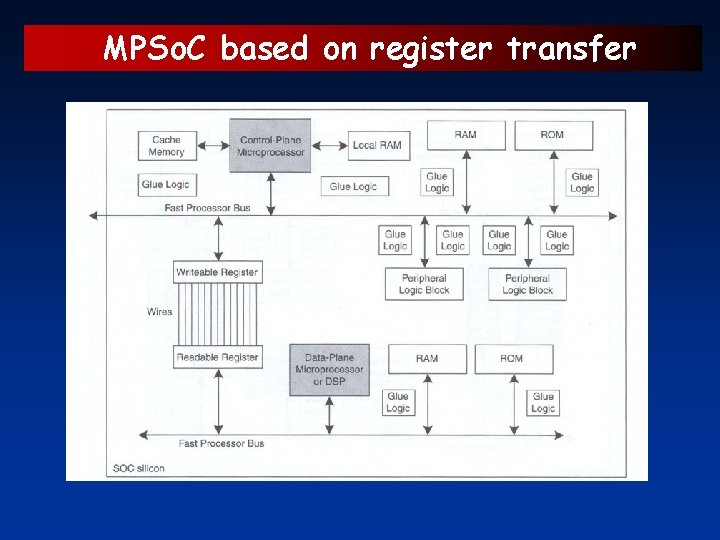

MPSo. C based on register transfer

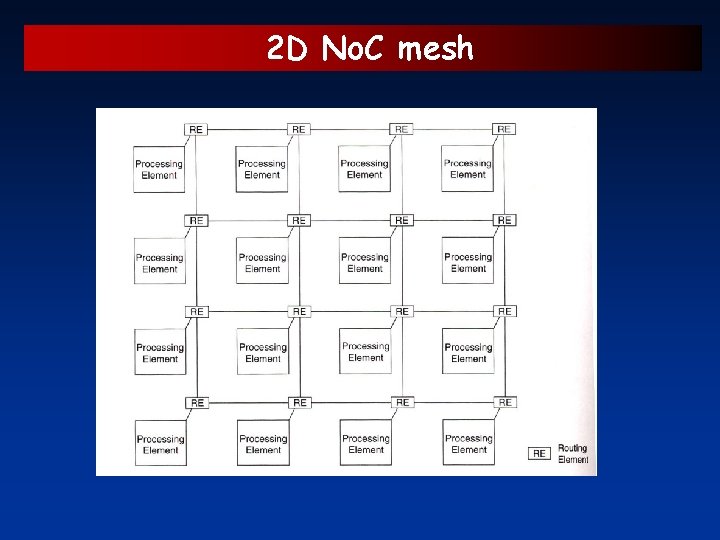

2 D No. C mesh

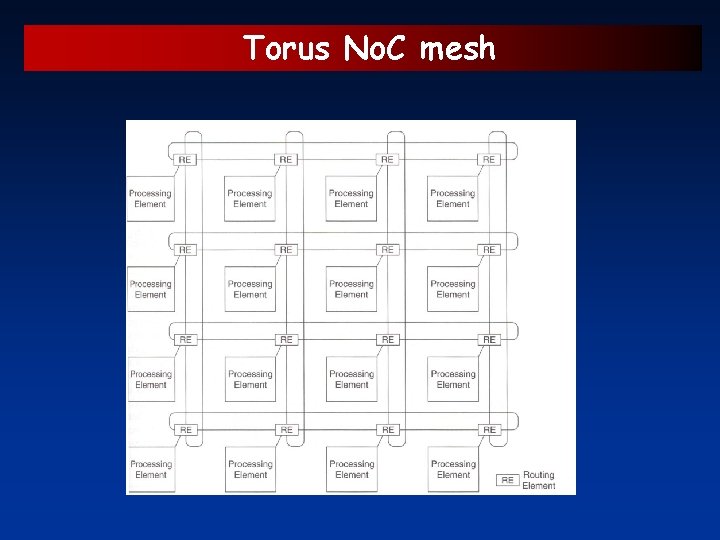

Torus No. C mesh

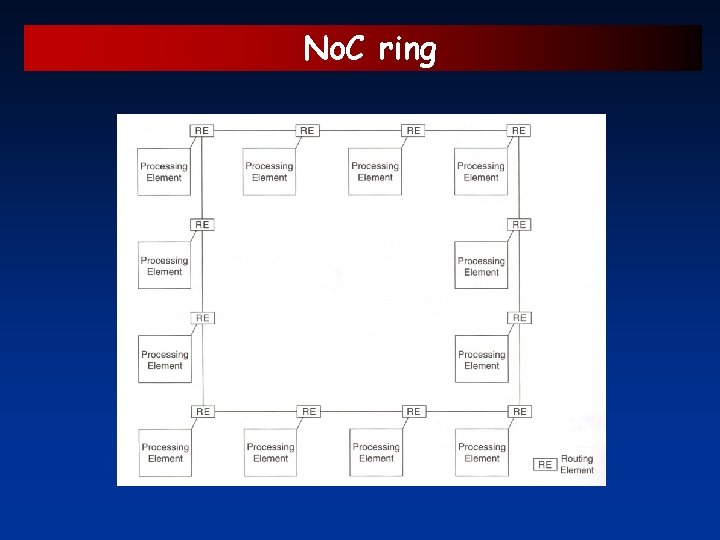

No. C ring

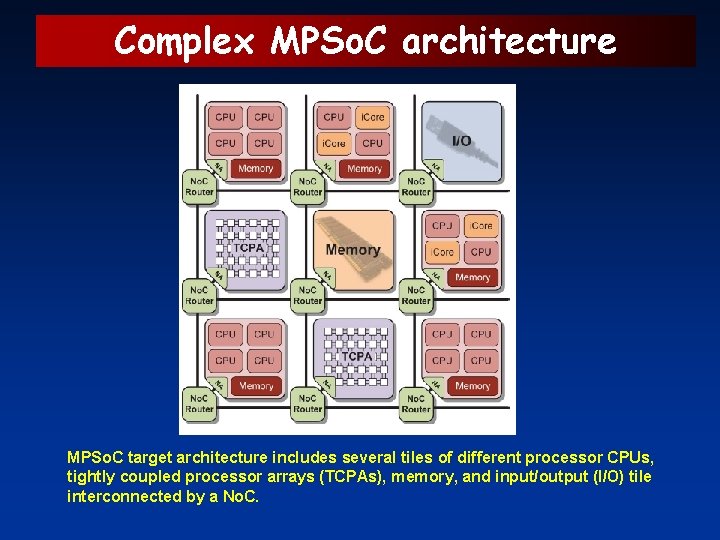

Complex MPSo. C architecture MPSo. C target architecture includes several tiles of different processor CPUs, tightly coupled processor arrays (TCPAs), memory, and input/output (I/O) tile interconnected by a No. C.

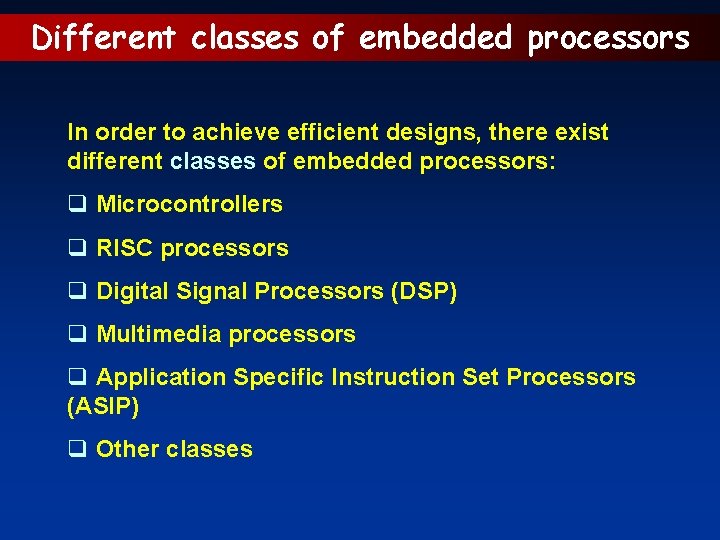

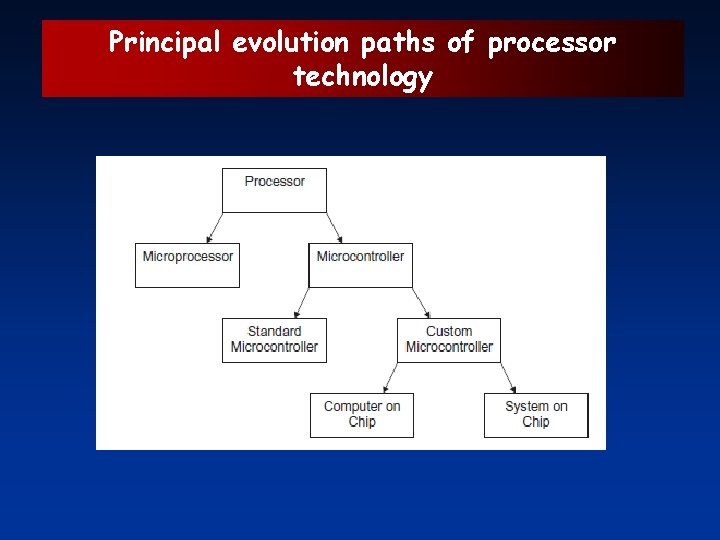

Different classes of embedded processors In order to achieve efficient designs, there exist different classes of embedded processors: q Microcontrollers q RISC processors q Digital Signal Processors (DSP) q Multimedia processors q Application Specific Instruction Set Processors (ASIP) q Other classes

Principal evolution paths of processor technology

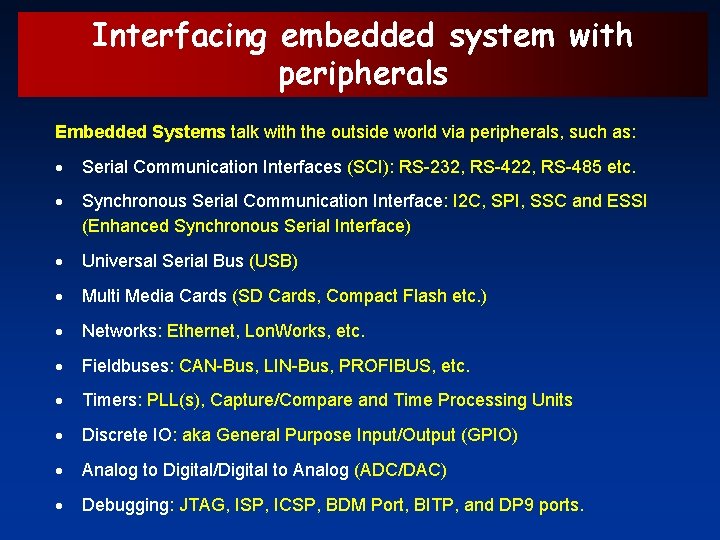

Interfacing embedded system with peripherals Embedded Systems talk with the outside world via peripherals, such as: Serial Communication Interfaces (SCI): RS-232, RS-422, RS-485 etc. Synchronous Serial Communication Interface: I 2 C, SPI, SSC and ESSI (Enhanced Synchronous Serial Interface) Universal Serial Bus (USB) Multi Media Cards (SD Cards, Compact Flash etc. ) Networks: Ethernet, Lon. Works, etc. Fieldbuses: CAN-Bus, LIN-Bus, PROFIBUS, etc. Timers: PLL(s), Capture/Compare and Time Processing Units Discrete IO: aka General Purpose Input/Output (GPIO) Analog to Digital/Digital to Analog (ADC/DAC) Debugging: JTAG, ISP, ICSP, BDM Port, BITP, and DP 9 ports.

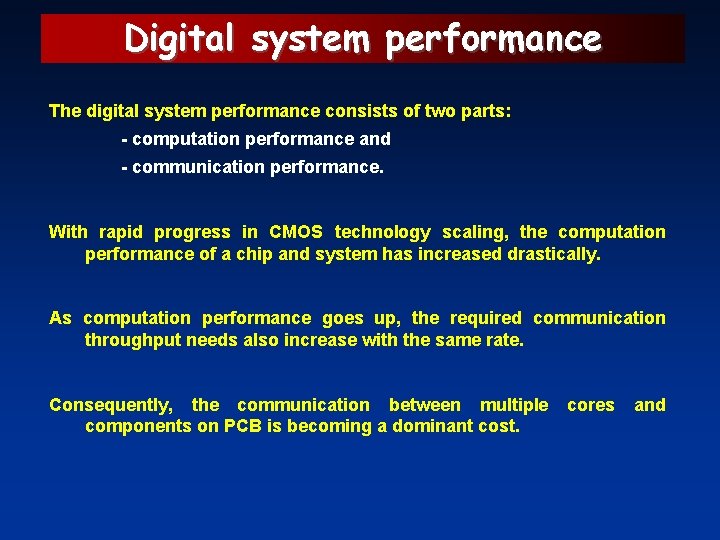

Digital system performance The digital system performance consists of two parts: - computation performance and - communication performance. With rapid progress in CMOS technology scaling, the computation performance of a chip and system has increased drastically. As computation performance goes up, the required communication throughput needs also increase with the same rate. Consequently, the communication between multiple cores and components on PCB is becoming a dominant cost.

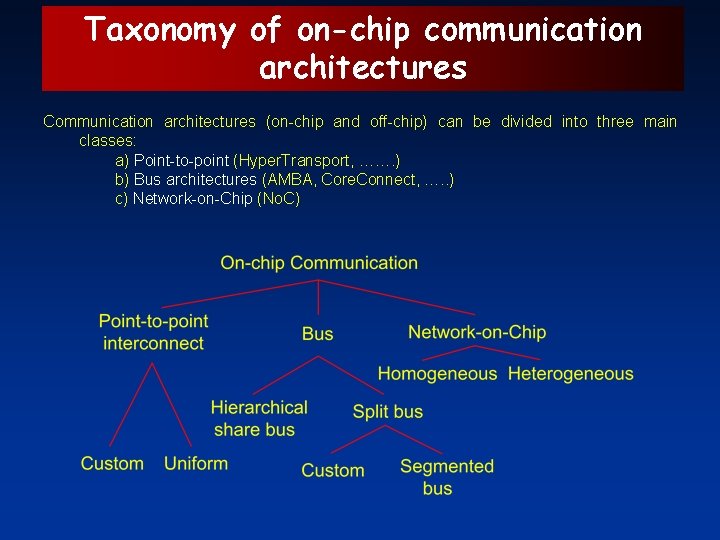

Taxonomy of on-chip communication architectures Communication architectures (on-chip and off-chip) can be divided into three main classes: a) Point-to-point (Hyper. Transport, ……. ) b) Bus architectures (AMBA, Core. Connect, …. . ) c) Network-on-Chip (No. C)

Main requirements for the interconnect Three main requirements to be met during the design of interconnection architectures are: a) High data transfer speed - both serial and parallel b) Fault tolerant operation - possibility to detect and correct transmission errors c) Low power consumption - saving energy

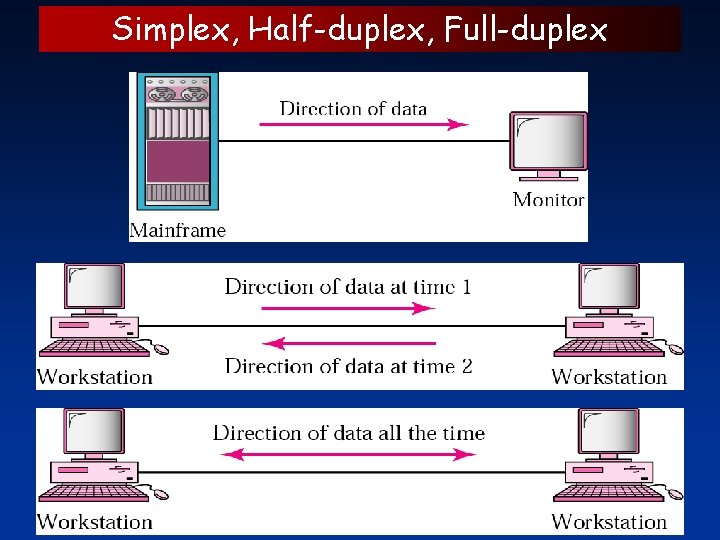

Simplex, Half-duplex, Full-duplex

Characteristics for peripherals classification Simplex, Duplex & Semi Duplex Serial Vs Parallel Synchronous Vs Asynchronous Data Throughput

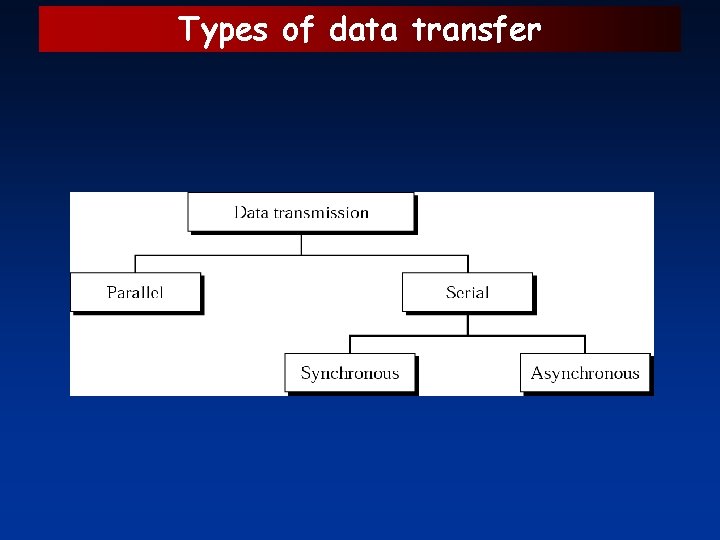

Types of data transfer

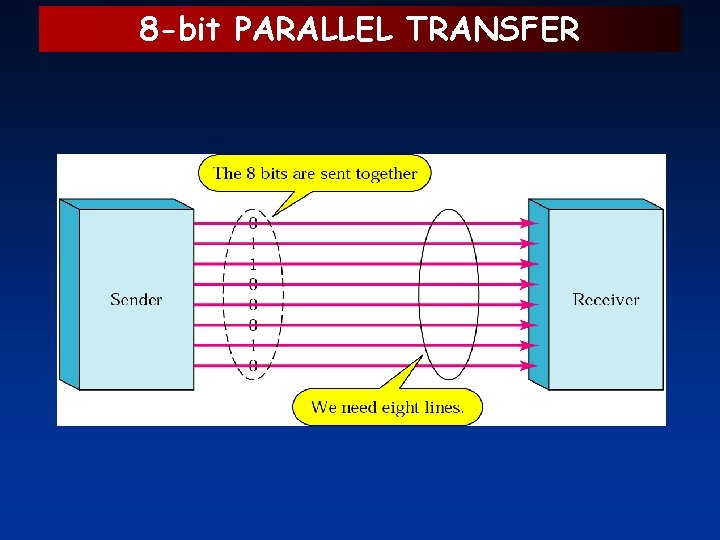

8 -bit PARALLEL TRANSFER

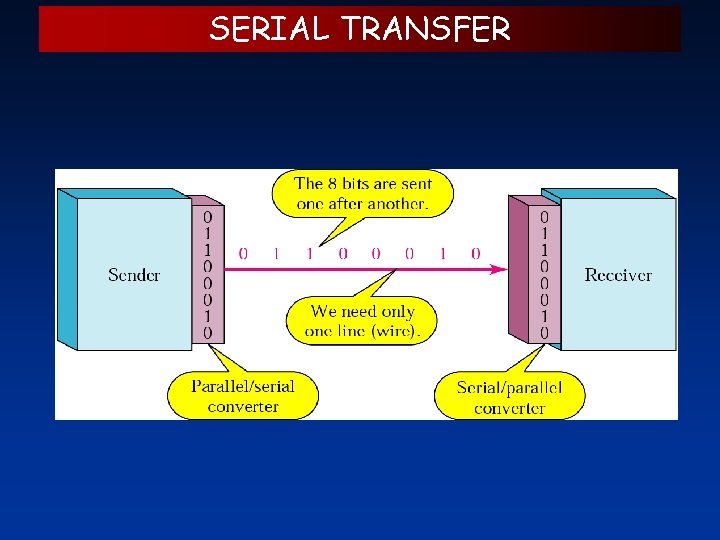

SERIAL TRANSFER

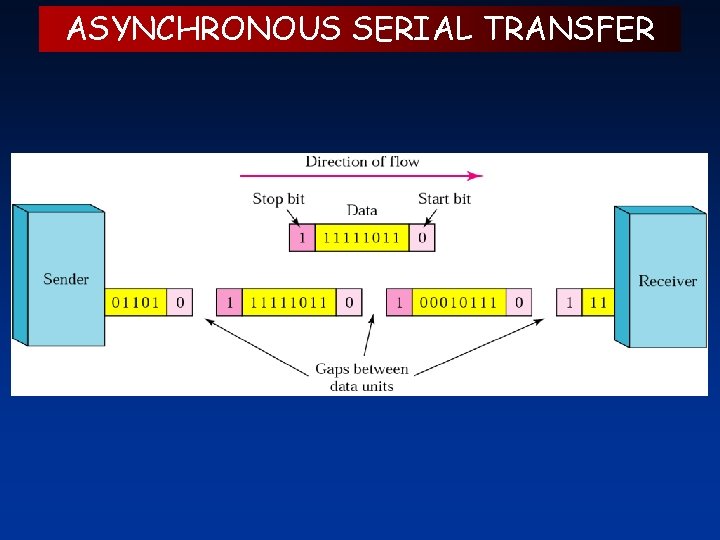

ASYNCHRONOUS SERIAL TRANSFER

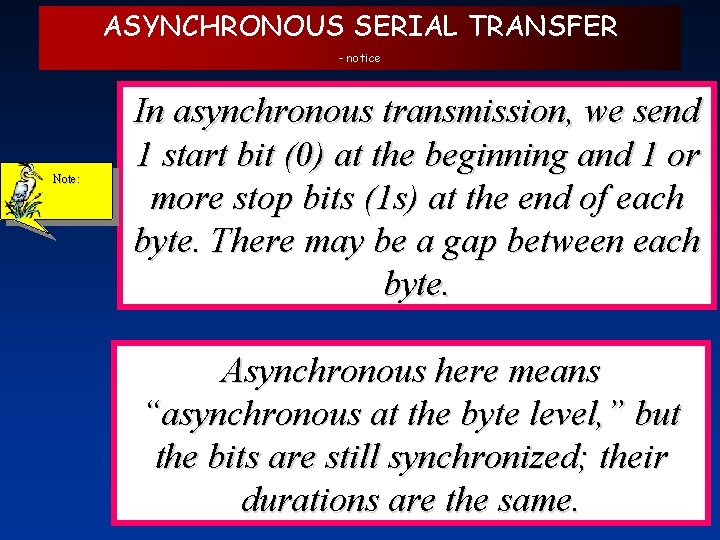

ASYNCHRONOUS SERIAL TRANSFER - notice Note: In asynchronous transmission, we send 1 start bit (0) at the beginning and 1 or more stop bits (1 s) at the end of each byte. There may be a gap between each byte. Asynchronous here means “asynchronous at the byte level, ” but the bits are still synchronized; their durations are the same.

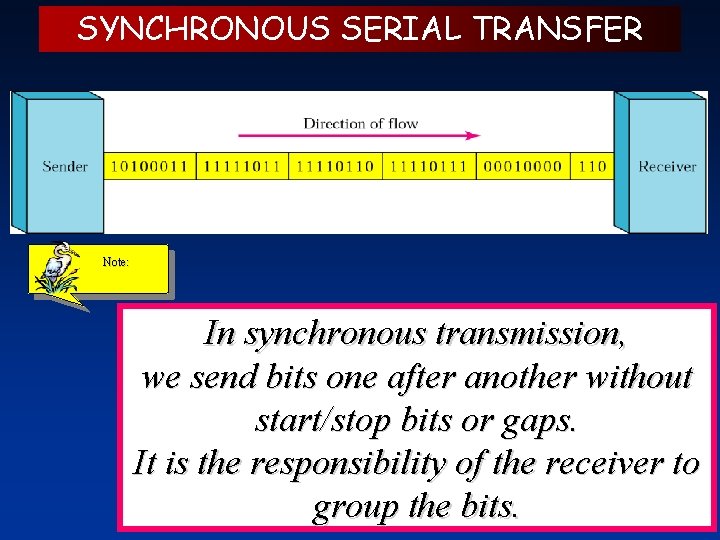

SYNCHRONOUS SERIAL TRANSFER Note: In synchronous transmission, we send bits one after another without start/stop bits or gaps. It is the responsibility of the receiver to group the bits.

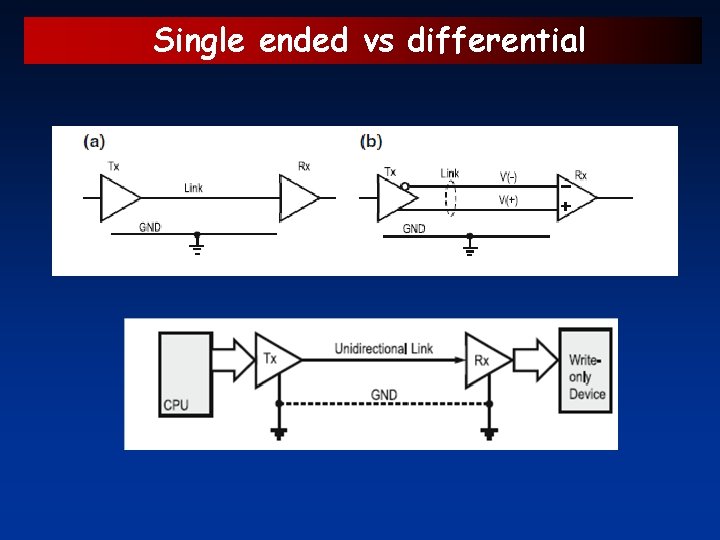

Single ended vs differential

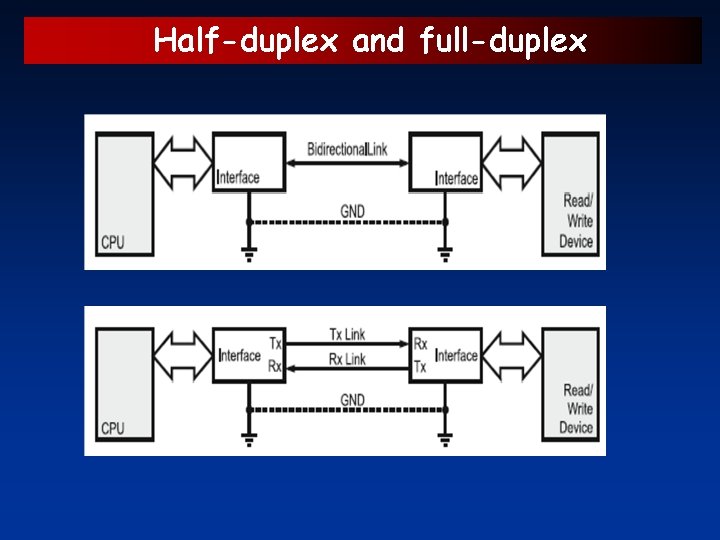

Half-duplex and full-duplex

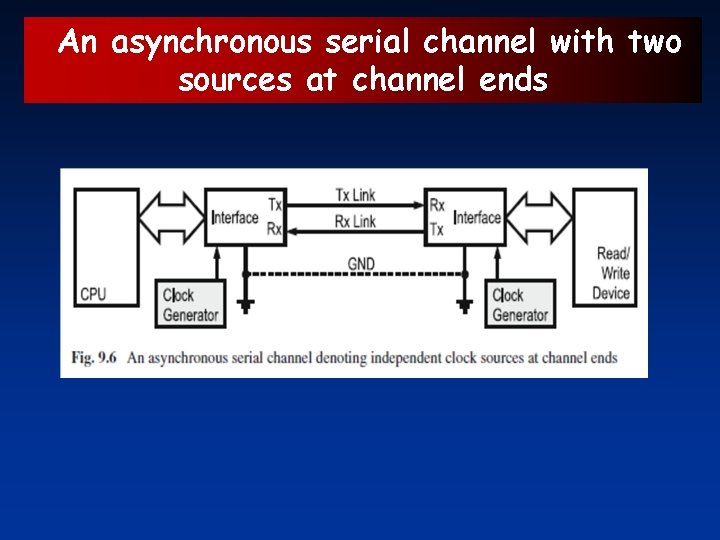

An asynchronous serial channel with two sources at channel ends

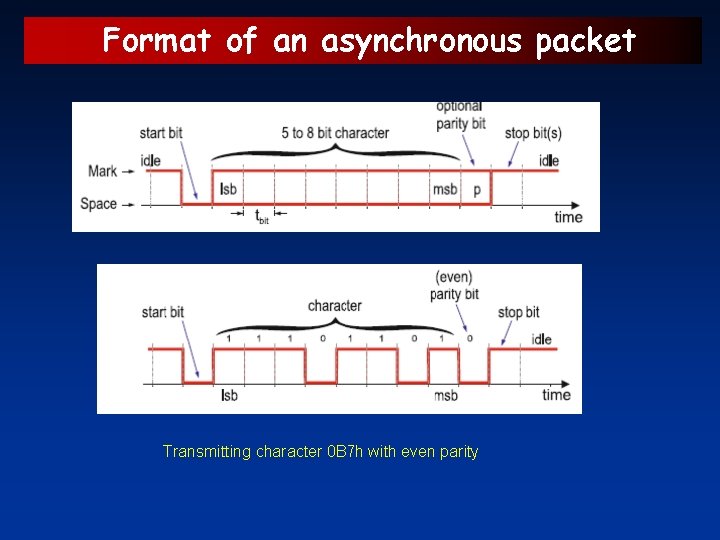

Format of an asynchronous packet Transmitting character 0 B 7 h with even parity

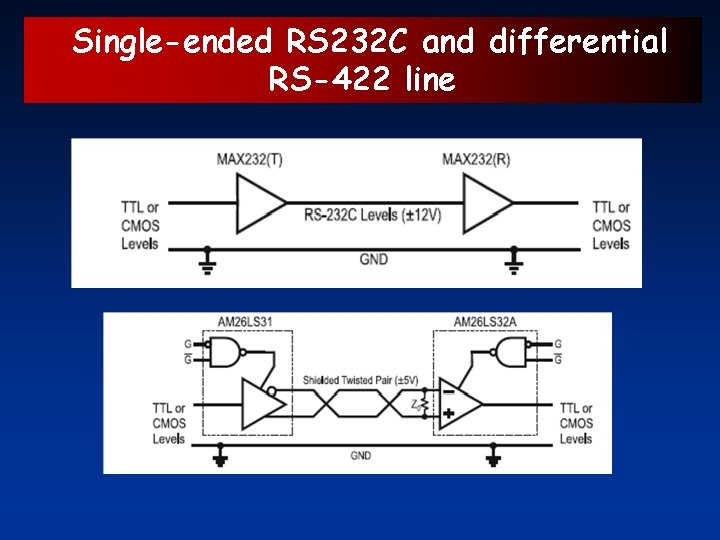

Single-ended RS 232 C and differential RS-422 line

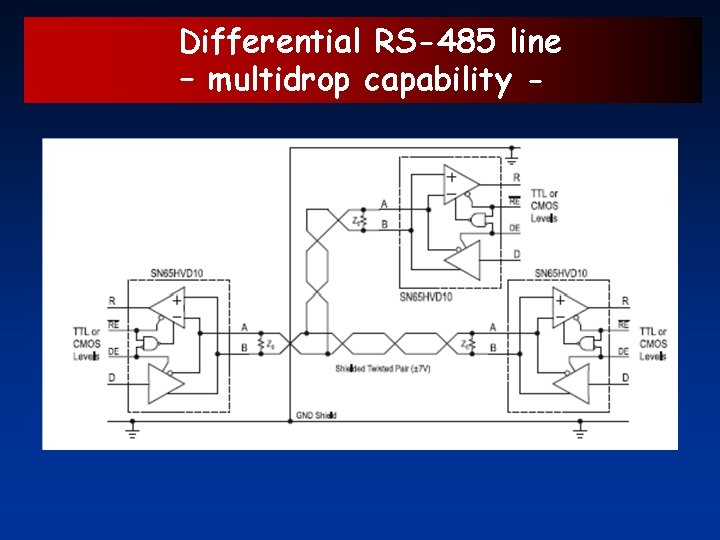

Differential RS-485 line – multidrop capability -

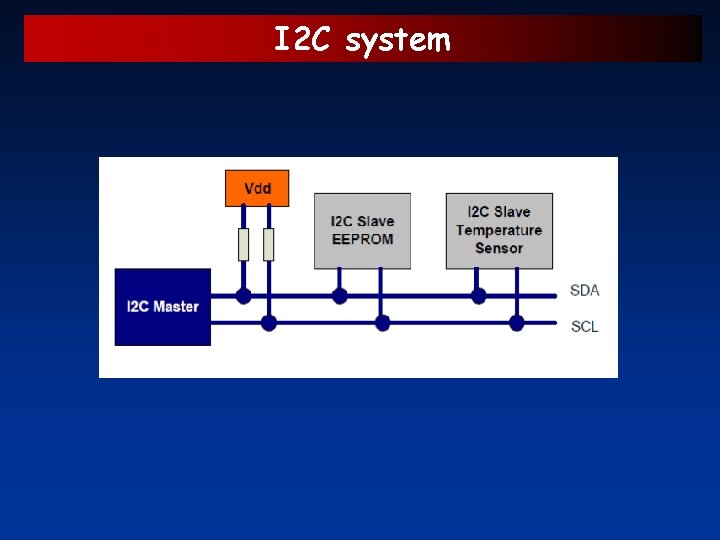

I 2 C system

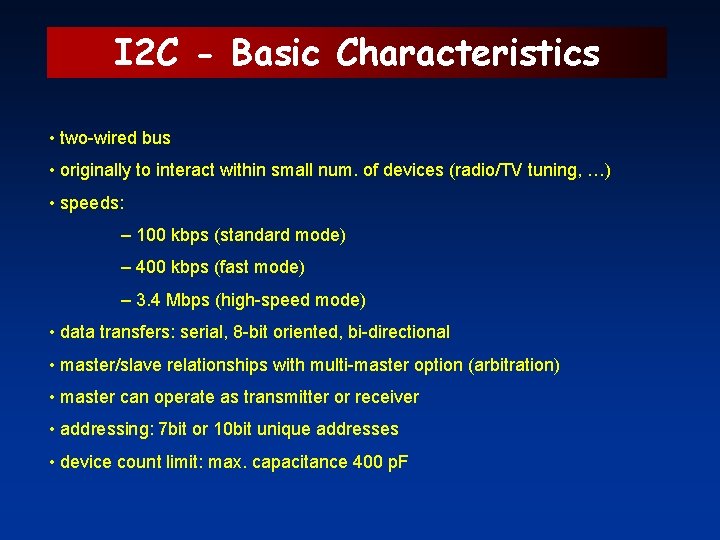

I 2 C - Basic Characteristics • two-wired bus • originally to interact within small num. of devices (radio/TV tuning, …) • speeds: – 100 kbps (standard mode) – 400 kbps (fast mode) – 3. 4 Mbps (high-speed mode) • data transfers: serial, 8 -bit oriented, bi-directional • master/slave relationships with multi-master option (arbitration) • master can operate as transmitter or receiver • addressing: 7 bit or 10 bit unique addresses • device count limit: max. capacitance 400 p. F

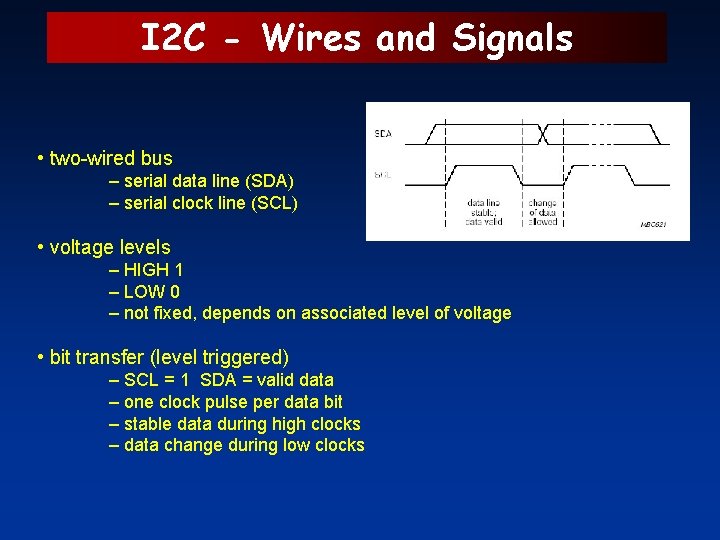

I 2 C - Wires and Signals • two-wired bus – serial data line (SDA) – serial clock line (SCL) • voltage levels – HIGH 1 – LOW 0 – not fixed, depends on associated level of voltage • bit transfer (level triggered) – SCL = 1 SDA = valid data – one clock pulse per data bit – stable data during high clocks – data change during low clocks

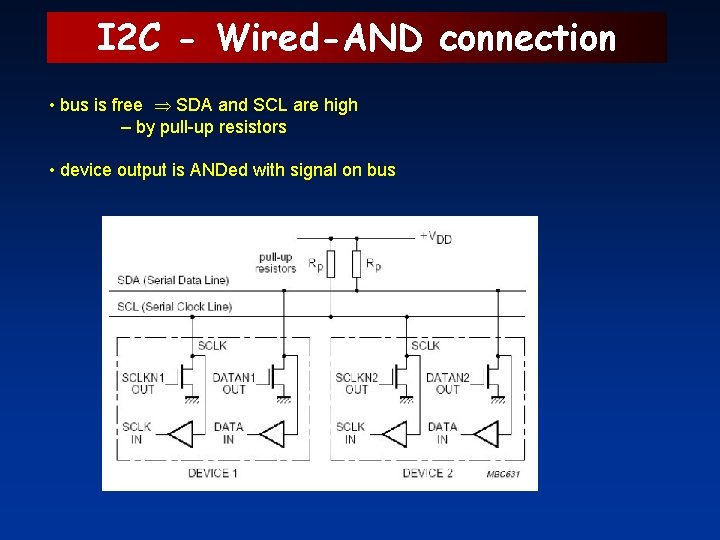

I 2 C - Wired-AND connection • bus is free SDA and SCL are high – by pull-up resistors • device output is ANDed with signal on bus

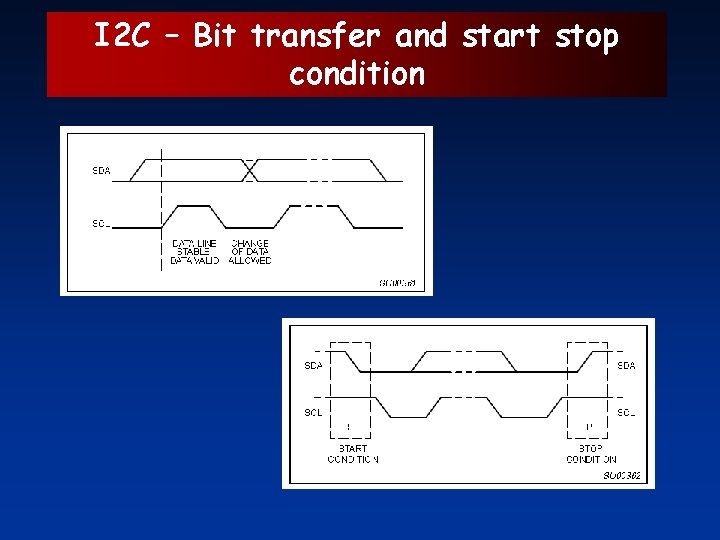

I 2 C – Bit transfer and start stop condition

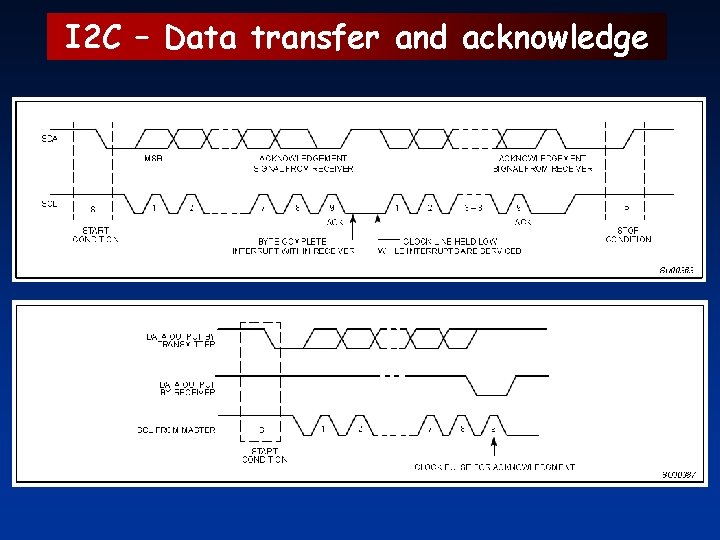

I 2 C – Data transfer and acknowledge

I 2 C - Masters and Slaves • Master device – controls the SCL – starts and stops data transfer – controls addressing of other devices • Slave device – device addressed by master • Transmitter/Receiver – master or slave – master-transmitter sends data to slave-recevier – master-receiver requires data from slave-transmitter

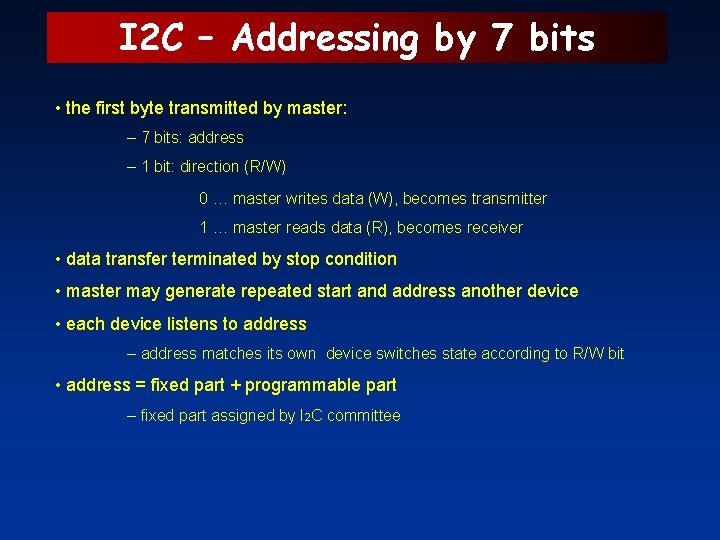

I 2 C – Addressing by 7 bits • the first byte transmitted by master: – 7 bits: address – 1 bit: direction (R/W) 0 … master writes data (W), becomes transmitter 1 … master reads data (R), becomes receiver • data transfer terminated by stop condition • master may generate repeated start and address another device • each device listens to address – address matches its own device switches state according to R/W bit • address = fixed part + programmable part – fixed part assigned by I 2 C committee

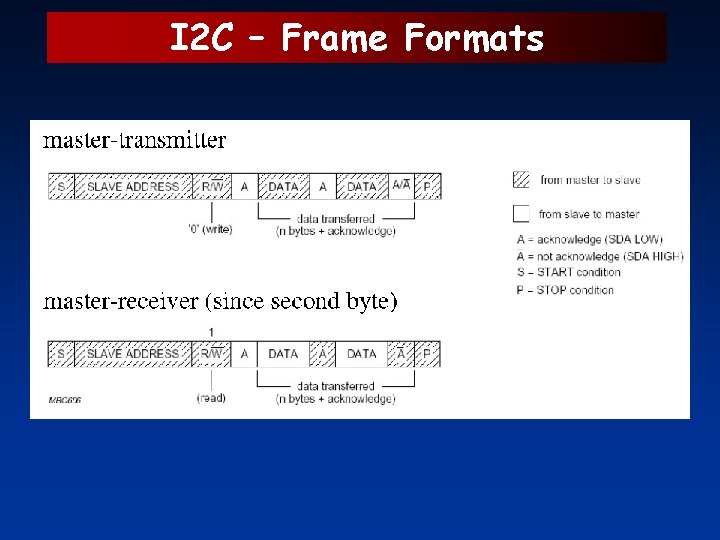

I 2 C – Frame Formats

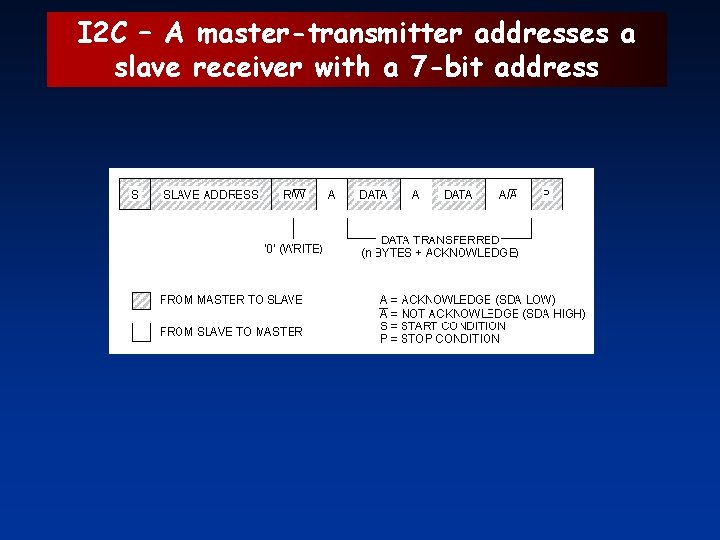

I 2 C – A master-transmitter addresses a slave receiver with a 7 -bit address

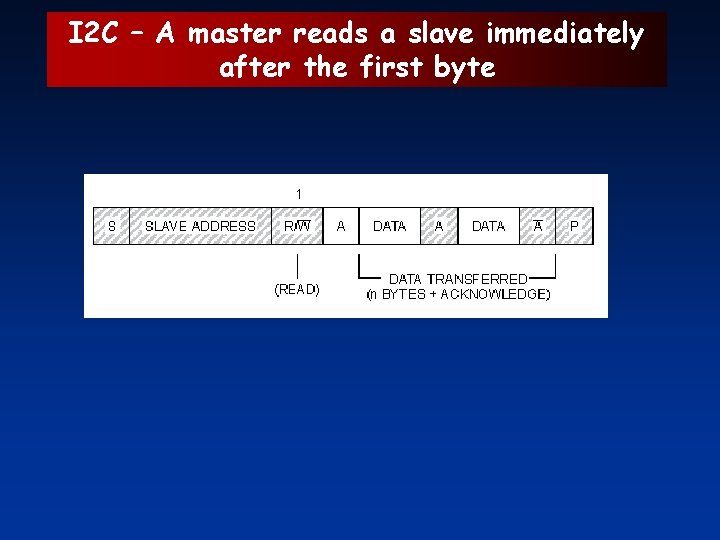

I 2 C – A master reads a slave immediately after the first byte

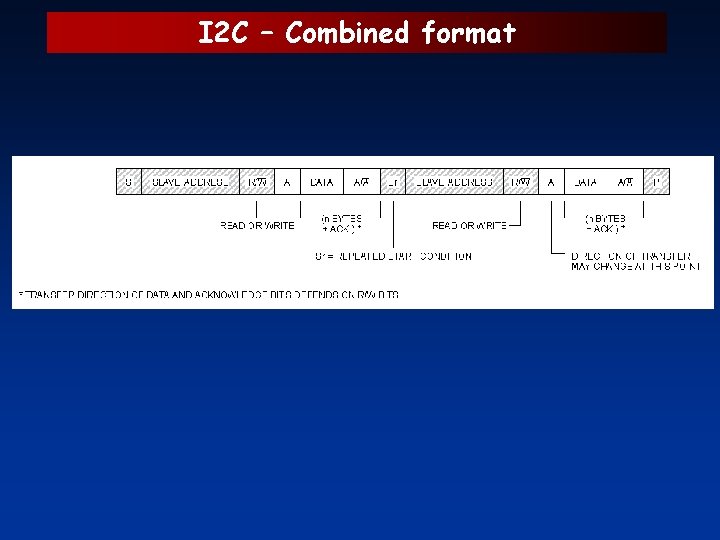

I 2 C – Combined format

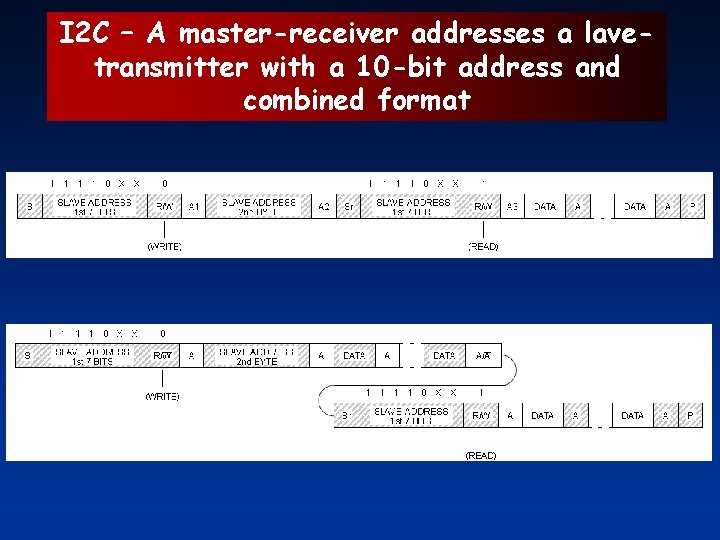

I 2 C – A master-receiver addresses a lavetransmitter with a 10 -bit address and combined format

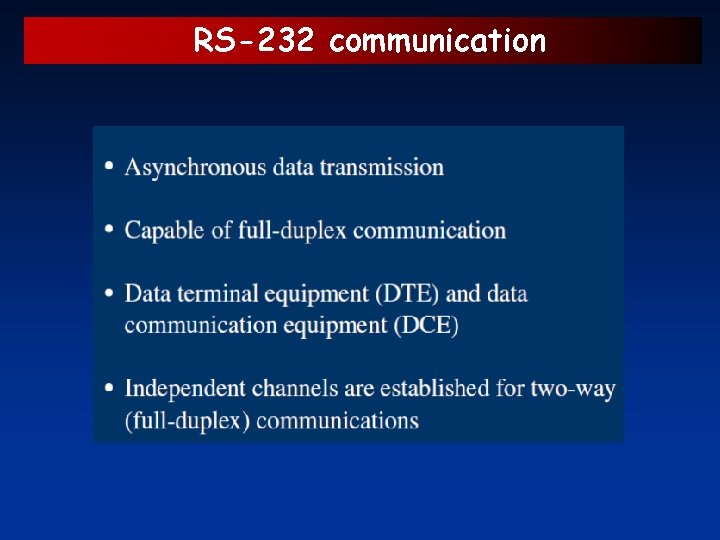

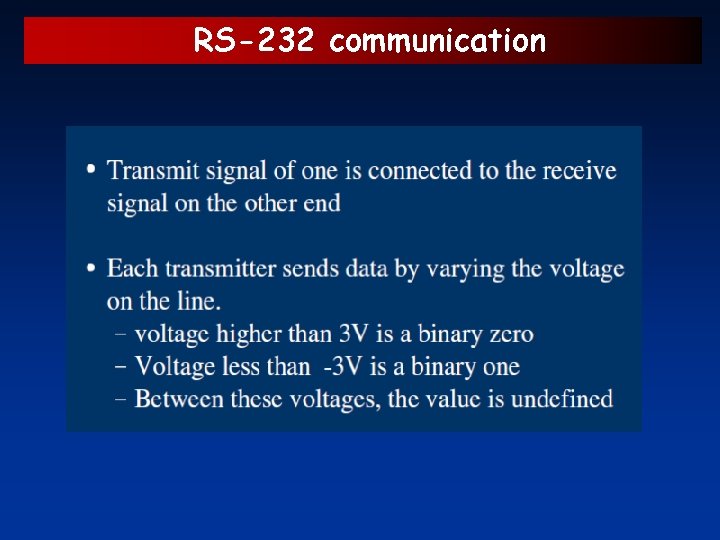

RS-232 communication

RS-232 communication

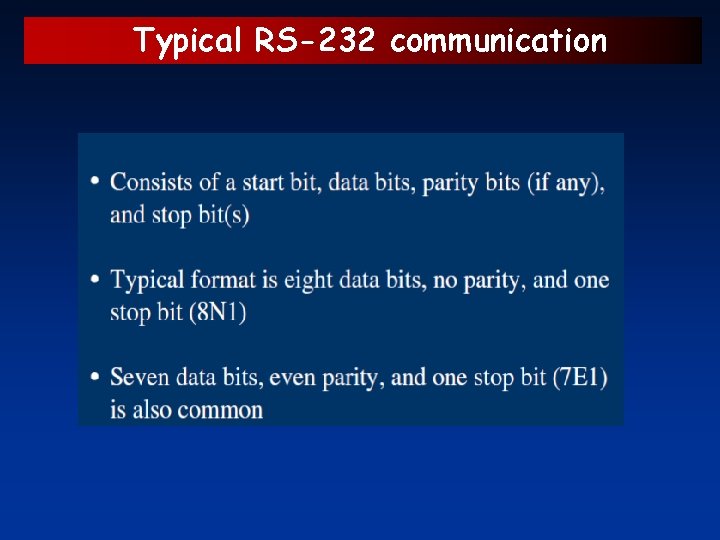

Typical RS-232 communication

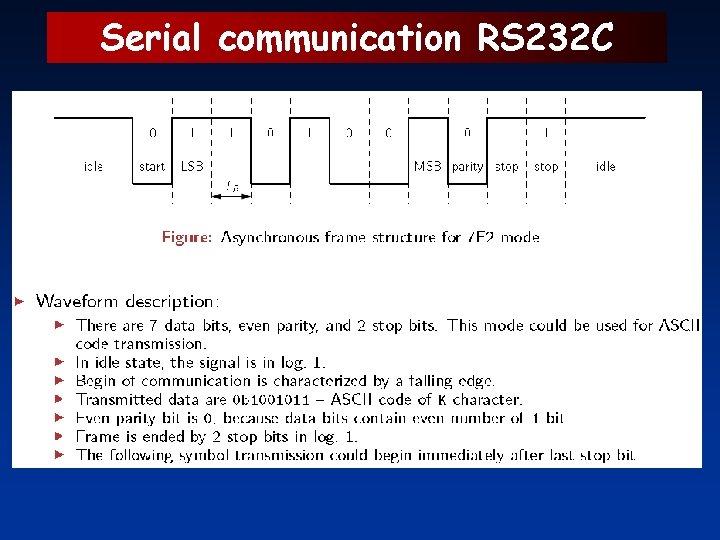

Serial communication RS 232 C

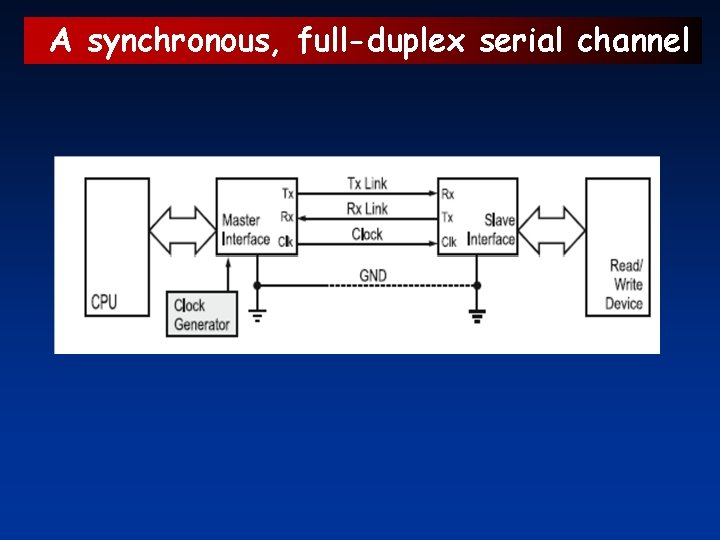

A synchronous, full-duplex serial channel

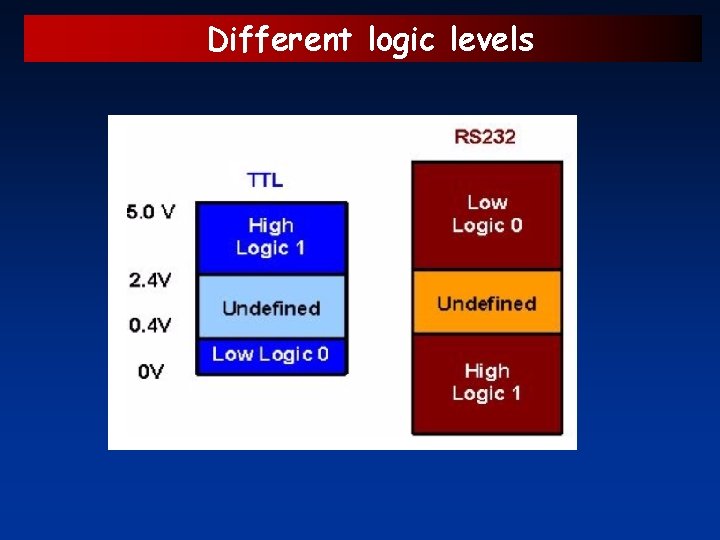

Different logic levels

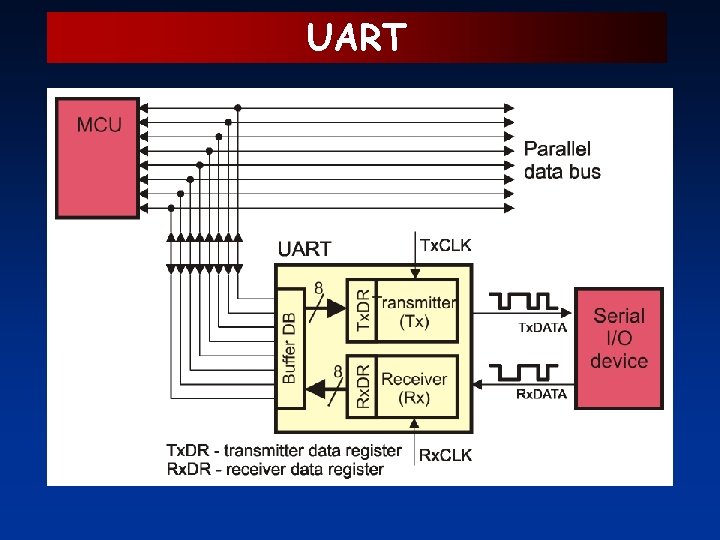

UART

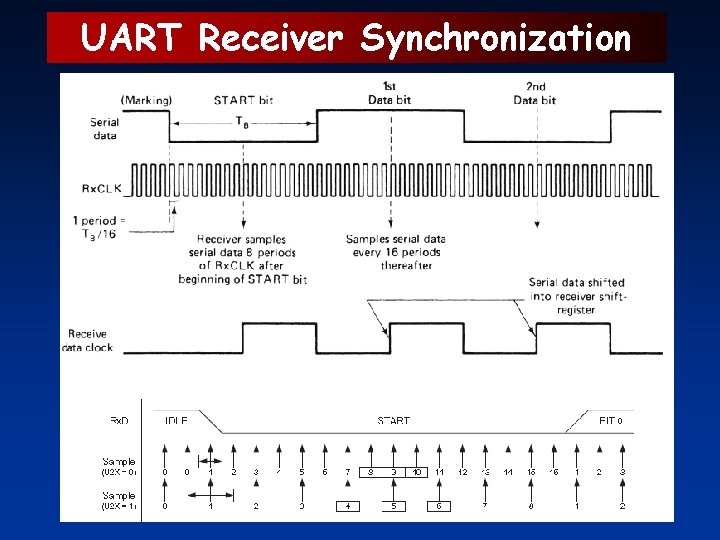

UART Receiver Synchronization

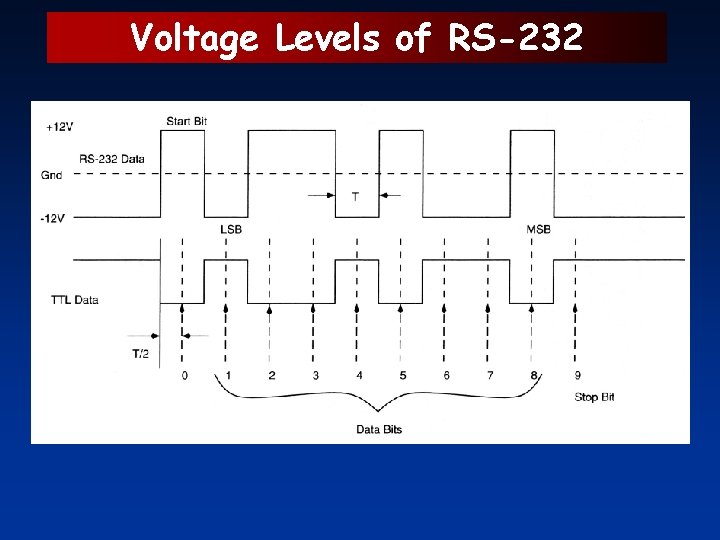

Voltage Levels of RS-232

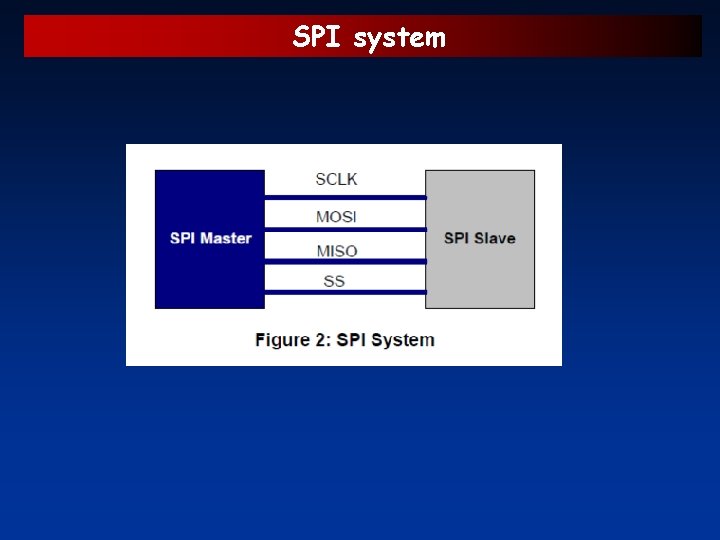

SPI system

SPI (Serial Peripheral Interface)

SPI (Serial Peripheral Interface)

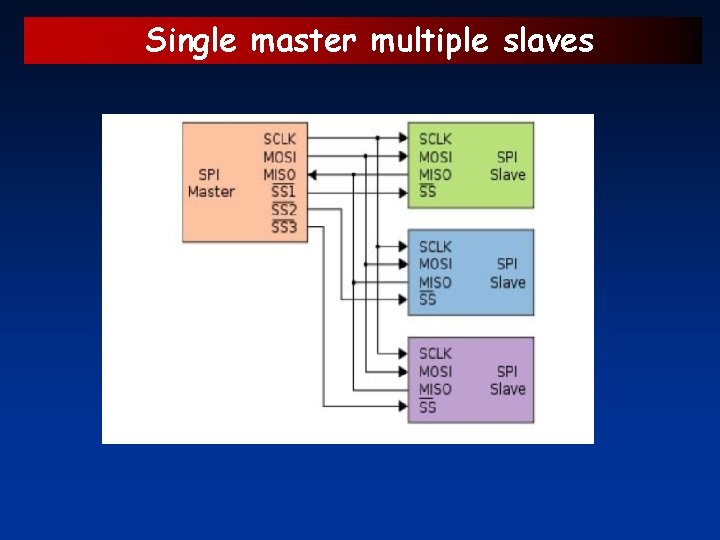

Single master multiple slaves

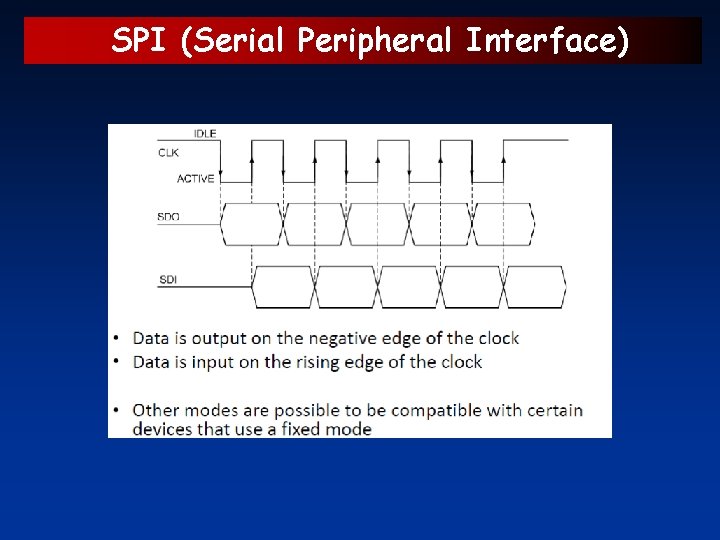

SPI (Serial Peripheral Interface)

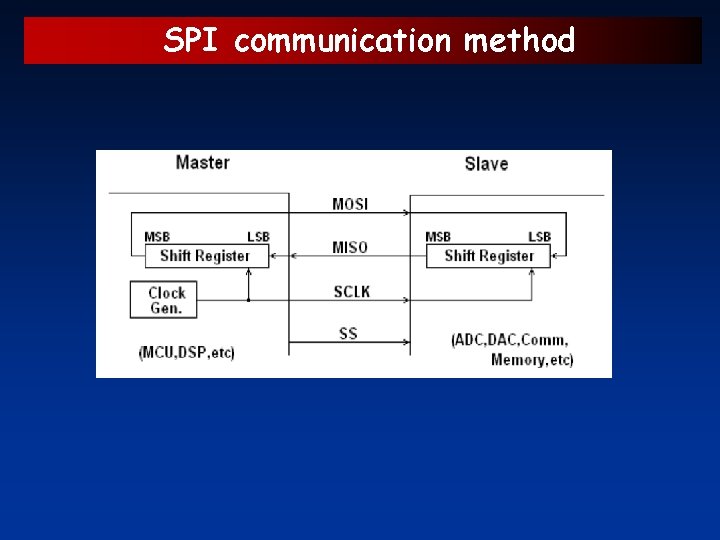

SPI communication method

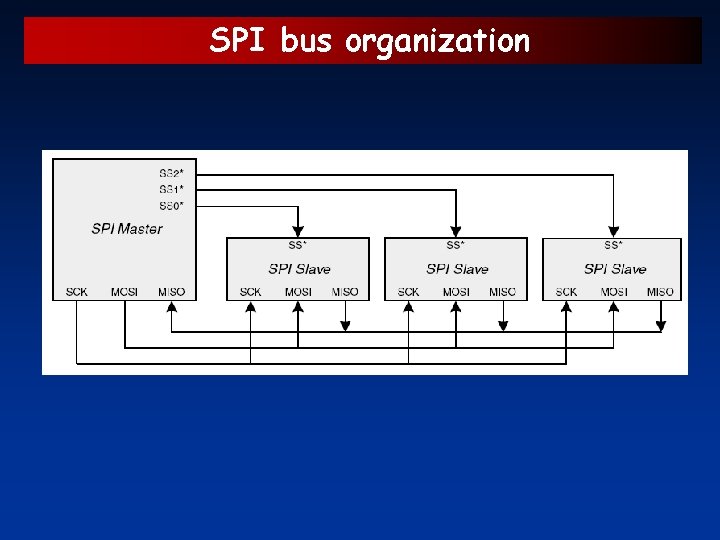

SPI bus organization

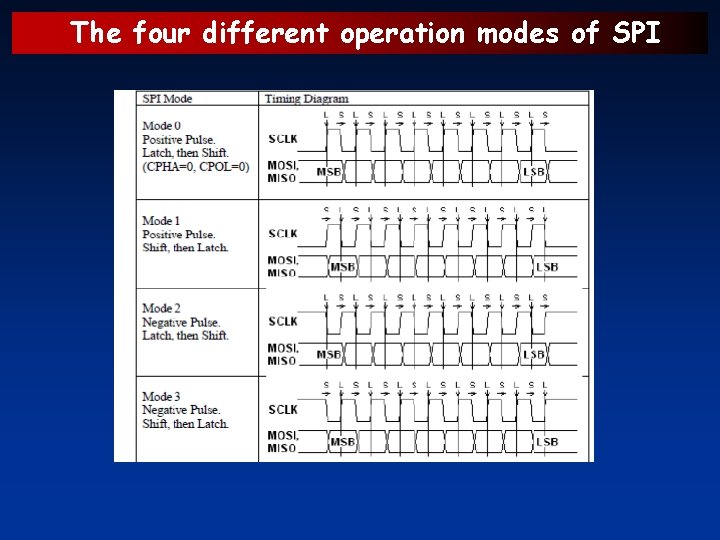

The four different operation modes of SPI

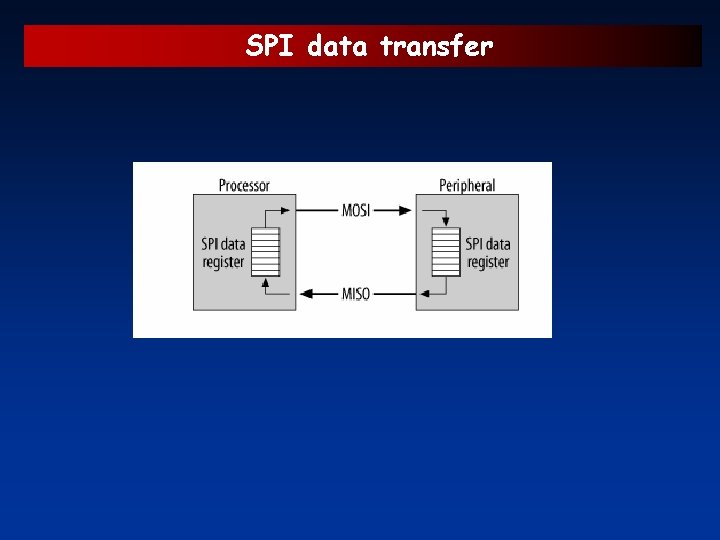

SPI data transfer

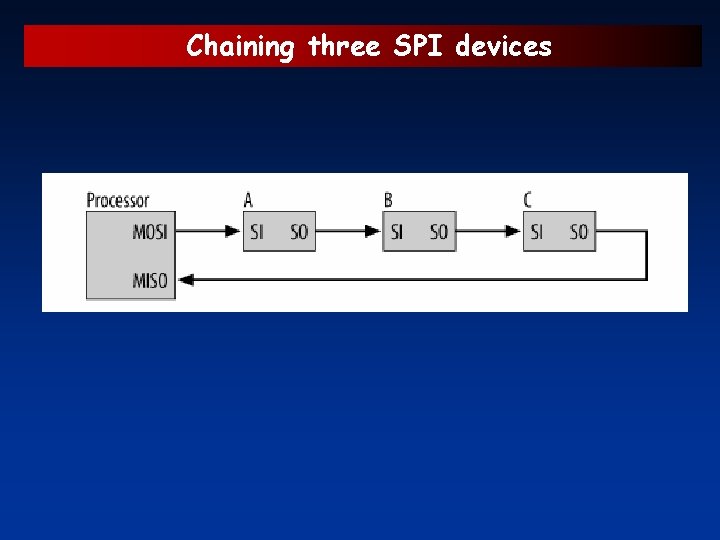

Chaining three SPI devices

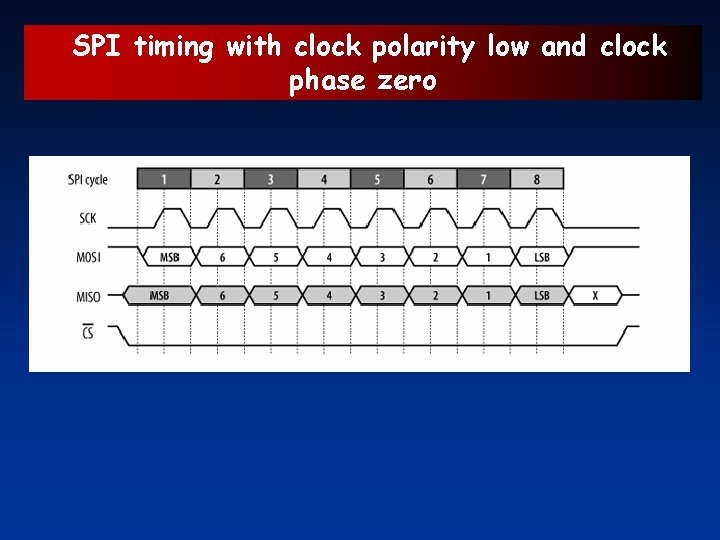

SPI timing with clock polarity low and clock phase zero

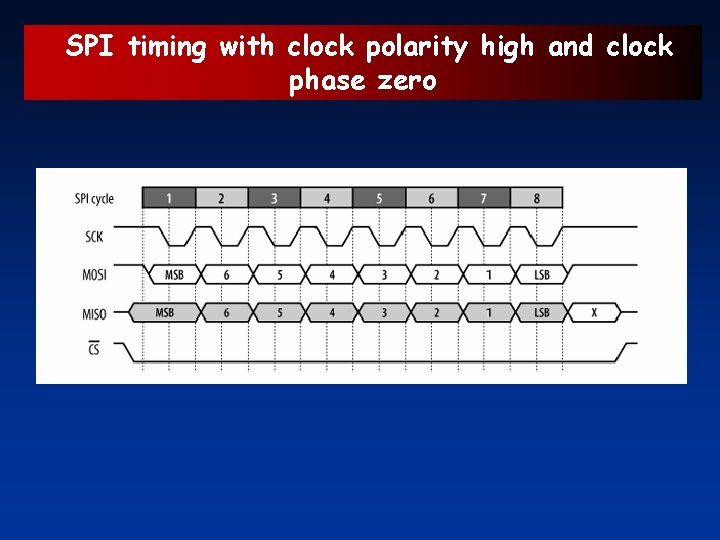

SPI timing with clock polarity high and clock phase zero

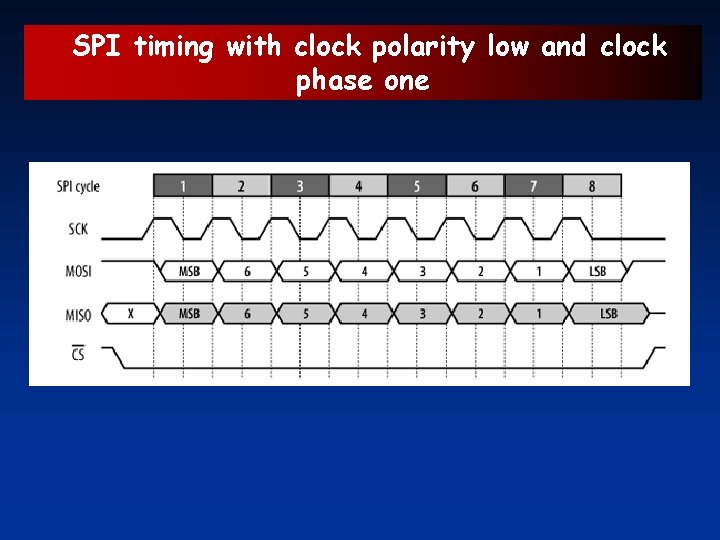

SPI timing with clock polarity low and clock phase one

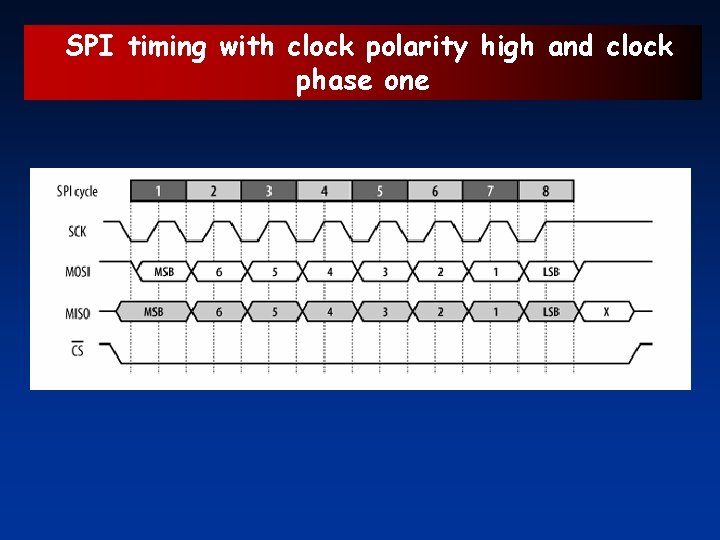

SPI timing with clock polarity high and clock phase one

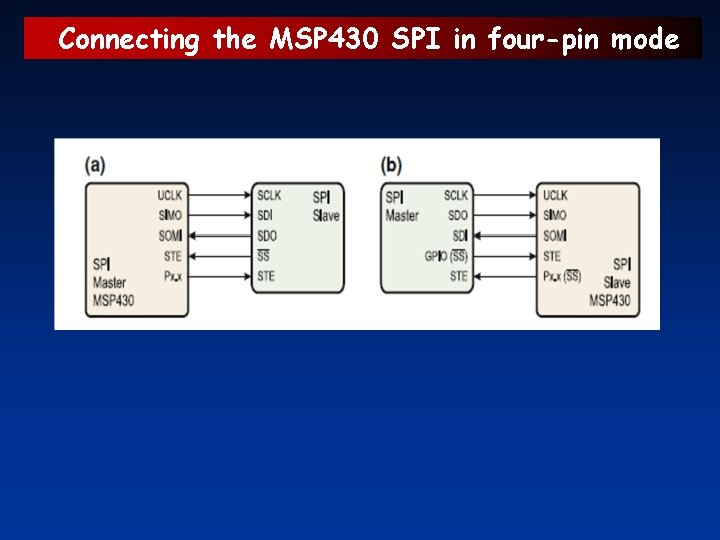

Connecting the MSP 430 SPI in four-pin mode

Q&A

- Slides: 86