Embedded Design with The PPC 440 Processor Core

Embedded Design with The PPC 440 Processor Core Xilinx Training

Welcome If you are new to Embedded design with Xilinx FPGA’s, this module will explain why you may want to use the PPC 440 processor in the Virtex-5 FX FPGA family Understanding the basics of the PPC 440 processor is essential if you are going to select an appropriate FPGA device family The Embedded Developers Kit software (EDK) is designed to make building a fast embedded design easy

Objectives After completing this module, you will be able to: Explain some of the benefits of the PPC 440 processor Explain how the utilities included with the Embedded Developers Kit (EDK) are optimized for the PPC 440 processor Explain how the Base System Builder makes it easy to make your embedded system

Lessons Hardware Overview PPC 440 Base System Builder Summary

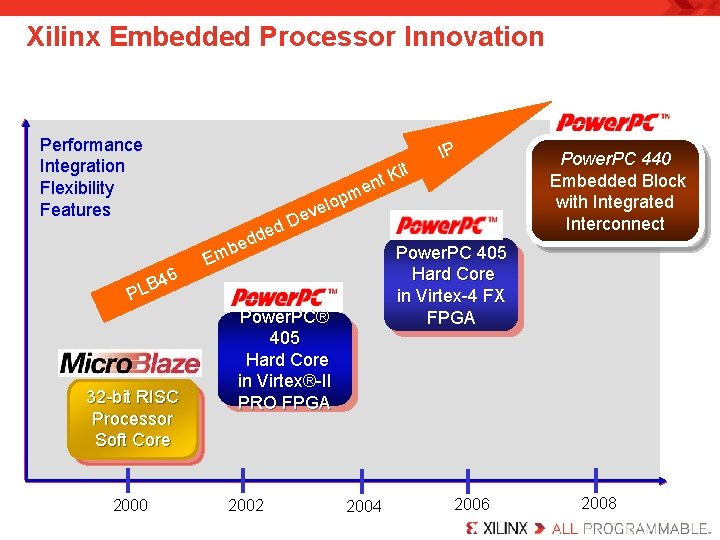

Xilinx Embedded Processor Innovation Performance Integration Flexibility Features 6 ve e d. D e edd b Em nt e m lop 2000 Power. PC® 405 Hard Core in Virtex®-II PRO FPGA 2002 Power. PC 440 Embedded Block with Integrated Interconnect Power. PC 405 Hard Core in Virtex-4 FX FPGA B 4 L P 32 -bit RISC Processor Soft Core Kit IP 2004 2006 2008

Supported FPGAs FPGA families – Spartan-3/3 A/3 AN/3 A DSP/3 E FPGA (Micro. Blaze processor) – Spartan-6 (Micro. Blaze Processor) – Virtex-4 FX (Micro. Blaze and Power. PC 405 processors) and LX/SX FPGA (Micro. Blaze processor) – Virtex-5 FXT (Micro. Blaze and Power. PC 440 processor) LX/LXT FPGA (Micro. Blaze) – Virtex-6 (Micro. Blaze processor)

Embedded Design in an FPGA Embedded design in an FPGA can consist of the following – FPGA hardware design • Processor system § Micro. Blaze processor (soft core) § Power. PC processor (PPC 440 hard core) § PLB or PLB v 46 bus § PLB bus components • Other FPGA hardware § Peripherals can either be custom made by the user with a Xilinx bus interface or a library of pre-optimized peripherals are available

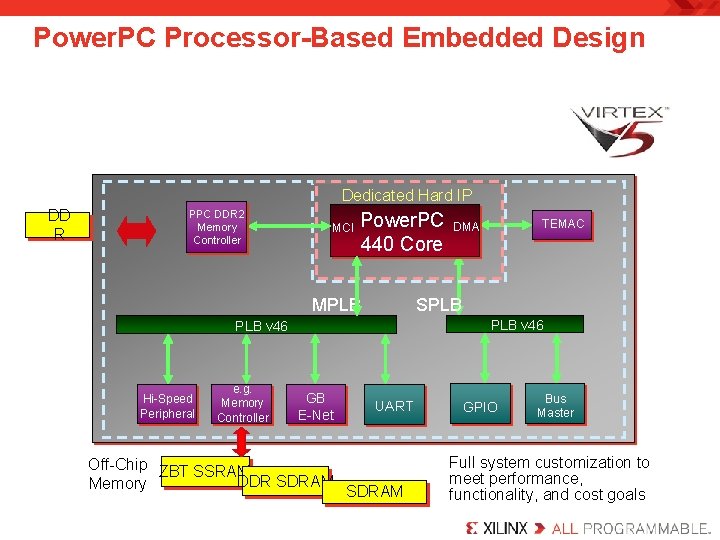

Power. PC Processor-Based Embedded Design Dedicated Hard IP DD R PPC DDR 2 Memory Controller MCI Power. PC 440 Core MPLB SPLB v 46 Hi-Speed Peripheral e. g. Memory Controller TEMAC DMA GB E-Net Off-Chip ZBT SSRAM DDR SDRAM Memory UART SDRAM GPIO Bus Master Full system customization to meet performance, functionality, and cost goals

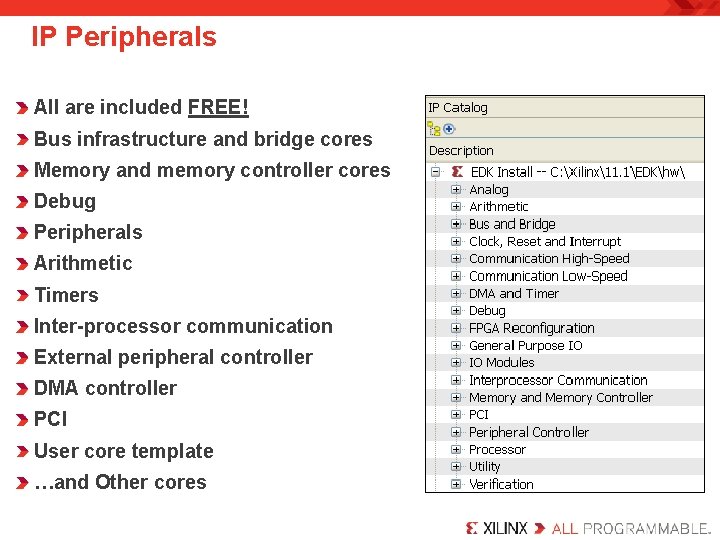

IP Peripherals All are included FREE! Bus infrastructure and bridge cores Memory and memory controller cores Debug Peripherals Arithmetic Timers Inter-processor communication External peripheral controller DMA controller PCI User core template …and Other cores

Lessons Hardware Overview PPC 440 Base System Builder Summary

Power. PC 440 Processor Core § High performance – 1, 100+ DMIPS – 29% faster per MHz than PPC 405 processor § Licensed IBM PPC 440 processor core – Industry standard – Superscalar • Multiple instructions per cycle § Uses PLB v 46 Core. Connect bus architecture § Third-generation embedded processor

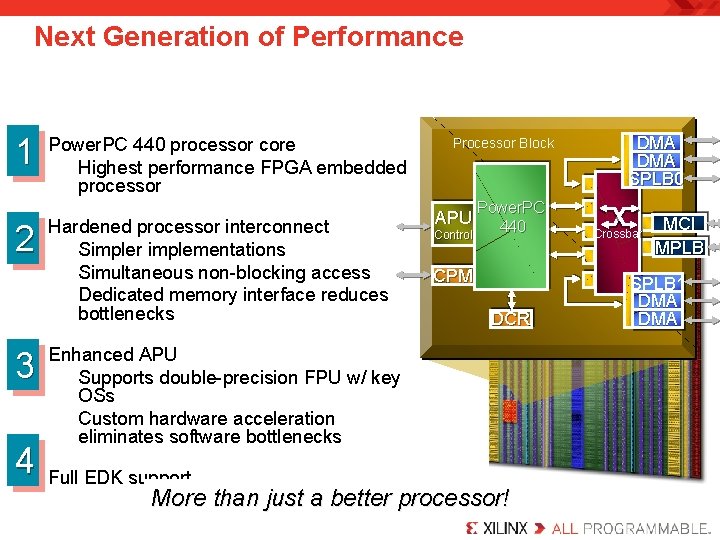

Next Generation of Performance 1 2 3 4 Power. PC 440 processor core Highest performance FPGA embedded processor Hardened processor interconnect Simpler implementations Simultaneous non-blocking access Dedicated memory interface reduces bottlenecks Processor Block P o w e r. P C 440 Control APU CP M DCR Enhanced APU Supports double-precision FPU w/ key OSs Custom hardware acceleration eliminates software bottlenecks Full EDK support More than just a better processor! DMA SPLB 0 Crossbar MC I MP L B SPLB 1 DMA

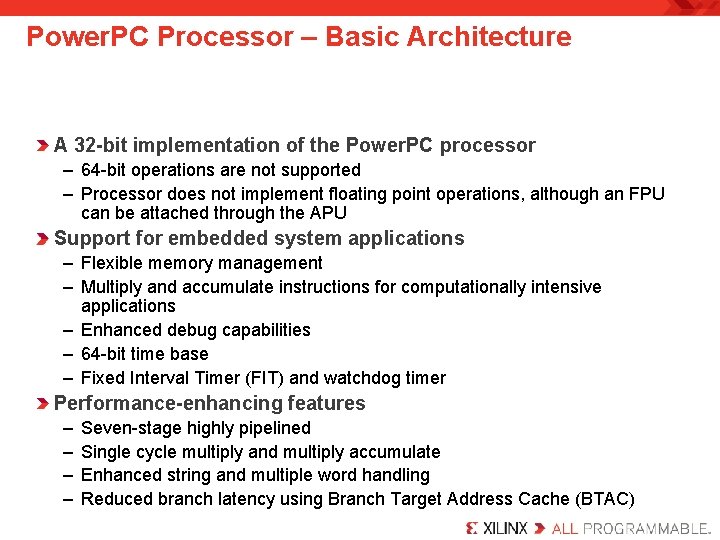

Power. PC Processor – Basic Architecture A 32 -bit implementation of the Power. PC processor – 64 -bit operations are not supported – Processor does not implement floating point operations, although an FPU can be attached through the APU Support for embedded system applications – Flexible memory management – Multiply and accumulate instructions for computationally intensive applications – Enhanced debug capabilities – 64 -bit time base – Fixed Interval Timer (FIT) and watchdog timer Performance-enhancing features – – Seven-stage highly pipelined Single cycle multiply and multiply accumulate Enhanced string and multiple word handling Reduced branch latency using Branch Target Address Cache (BTAC)

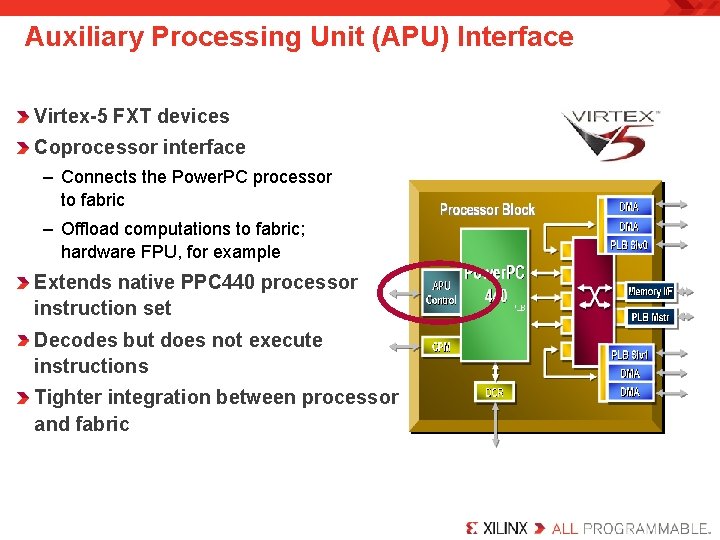

Auxiliary Processing Unit (APU) Interface Virtex-5 FXT devices Coprocessor interface – Connects the Power. PC processor to fabric – Offload computations to fabric; hardware FPU, for example Extends native PPC 440 processor instruction set Decodes but does not execute instructions Tighter integration between processor and fabric

Buses 101 Bus masters have the ability to initiate a bus transaction Bus slaves can only respond to a request Bus arbitration is a three-step process – A device requesting to become a bus master asserts a bus request signal – The arbiter continuously monitors the request and outputs an individual grant signal to each master according to the master’s priority scheme and the state of the other master requests at that time – The requesting master samples its grant line until granted access. When the current bus master releases the bus, the master then drives the address and control lines to initiate a data transaction to a slave bus agent. Arbitration mechanisms – Fixed priority, round-robin, or hybrid

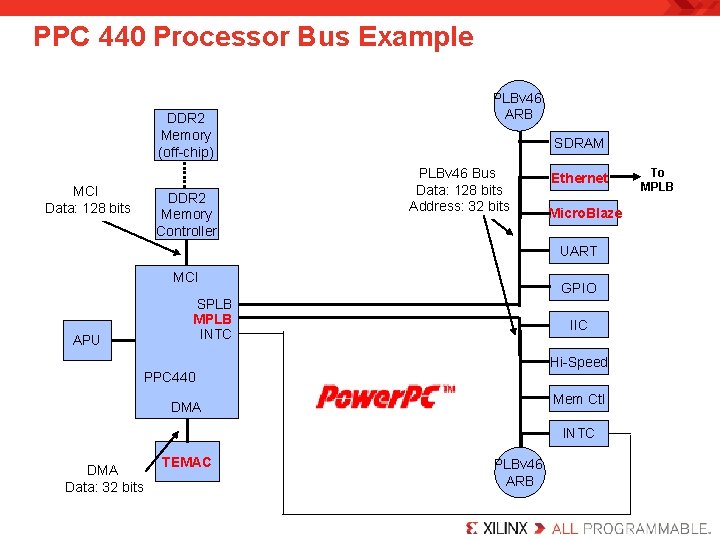

PPC 440 Processor Bus Example DDR 2 Memory (off-chip) MCI Data: 128 bits DDR 2 Memory Controller PLBv 46 ARB SDRAM PLBv 46 Bus Data: 128 bits Address: 32 bits Ethernet Micro. Blaze UART MCI APU GPIO SPLB MPLB INTC IIC Hi-Speed PPC 440 Mem Ctl DMA INTC DMA Data: 32 bits TEMAC PLBv 46 ARB To MPLB

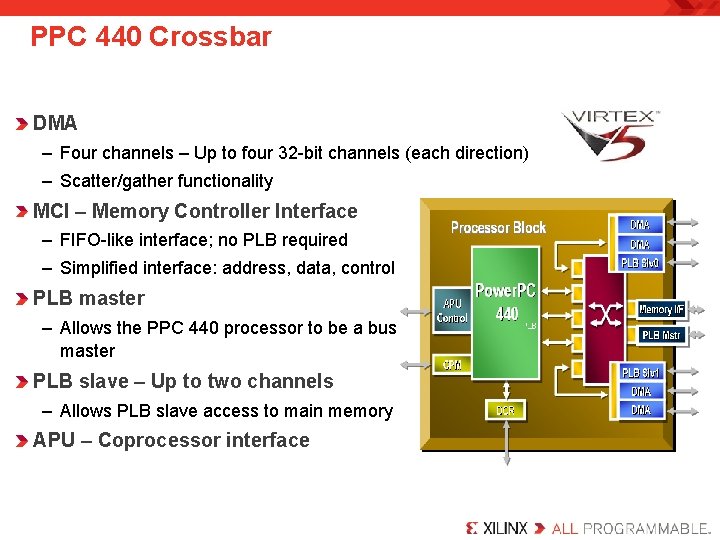

PPC 440 Crossbar DMA – Four channels – Up to four 32 -bit channels (each direction) – Scatter/gather functionality MCI – Memory Controller Interface – FIFO-like interface; no PLB required – Simplified interface: address, data, control PLB master – Allows the PPC 440 processor to be a bus master PLB slave – Up to two channels – Allows PLB slave access to main memory APU – Coprocessor interface

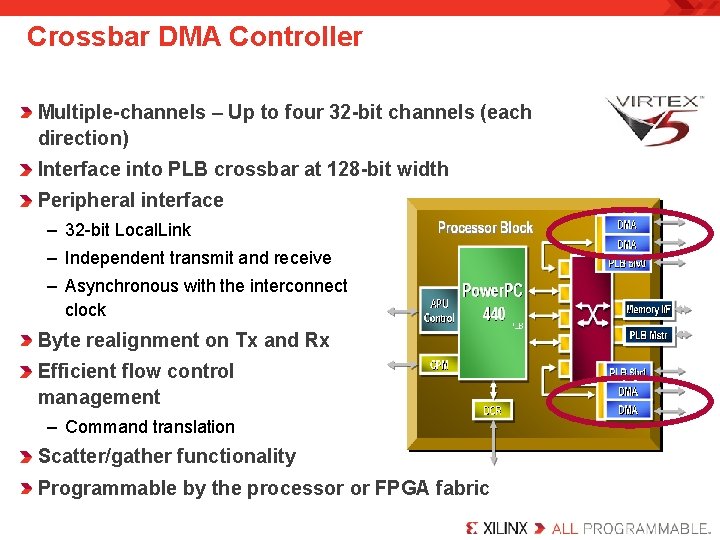

Crossbar DMA Controller Multiple-channels – Up to four 32 -bit channels (each direction) Interface into PLB crossbar at 128 -bit width Peripheral interface – 32 -bit Local. Link – Independent transmit and receive – Asynchronous with the interconnect clock Byte realignment on Tx and Rx Efficient flow control management – Command translation Scatter/gather functionality Programmable by the processor or FPGA fabric

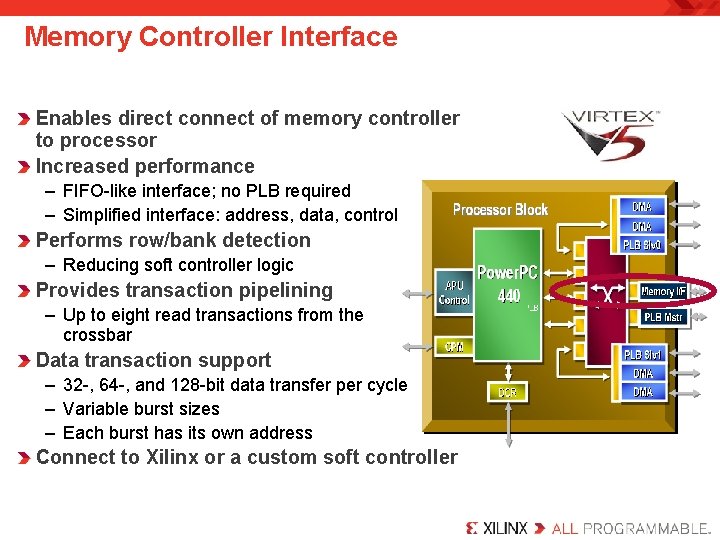

Memory Controller Interface Enables direct connect of memory controller to processor Increased performance – FIFO-like interface; no PLB required – Simplified interface: address, data, control Performs row/bank detection – Reducing soft controller logic Provides transaction pipelining – Up to eight read transactions from the crossbar Data transaction support – 32 -, 64 -, and 128 -bit data transfer per cycle – Variable burst sizes – Each burst has its own address Connect to Xilinx or a custom soft controller

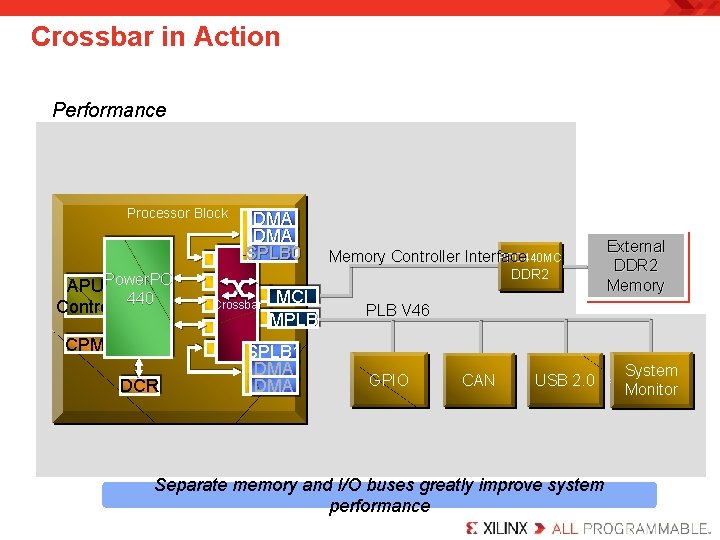

Crossbar in Action Performance Processor Block APU Power. PC 440 Control CPM DCR DMA SPLB 0 Memory Controller Interface PPC 440 MC DDR 2 Crossbar MC I MP L B SPLB 1 DMA External DDR 2 Memory PLB V 46 GPIO CAN USB 2. 0 Separate memory and I/O buses greatly improve system performance System Monitor

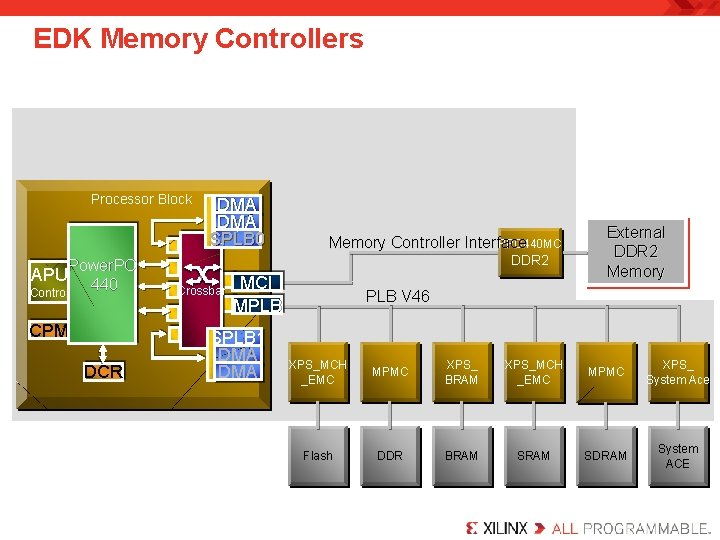

EDK Memory Controllers Processor Block P o w e r. P C APU 440 Control CPM DCR DMA SPLB 0 Memory Controller Interface PPC 440 MC DDR 2 Crossbar MC I MP L B SPLB 1 DMA External DDR 2 Memory PLB V 46 XPS_MCH _EMC MPMC XPS_ BRAM XPS_MCH _EMC MPMC XPS_ System Ace Flash DDR BRAM SDRAM System ACE

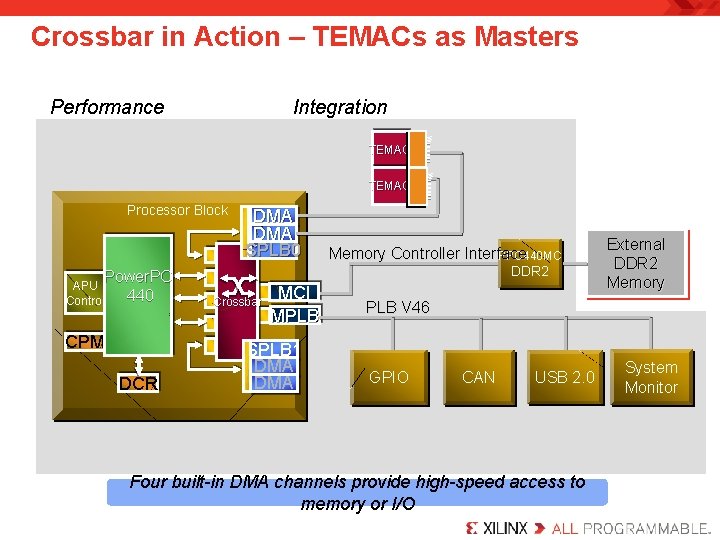

Crossbar in Action – TEMACs as Masters Integration Performance CPM DCR T E MA C Wrapper P o w e r. P C APU 440 Control DMA SPLB 0 Wrapper Processor Block T E MA C Memory Controller Interface PPC 440 MC DDR 2 Crossbar MC I MP L B SPLB 1 DMA External DDR 2 Memory PLB V 46 GPIO CAN USB 2. 0 Four built-in DMA channels provide high-speed access to memory or I/O System Monitor

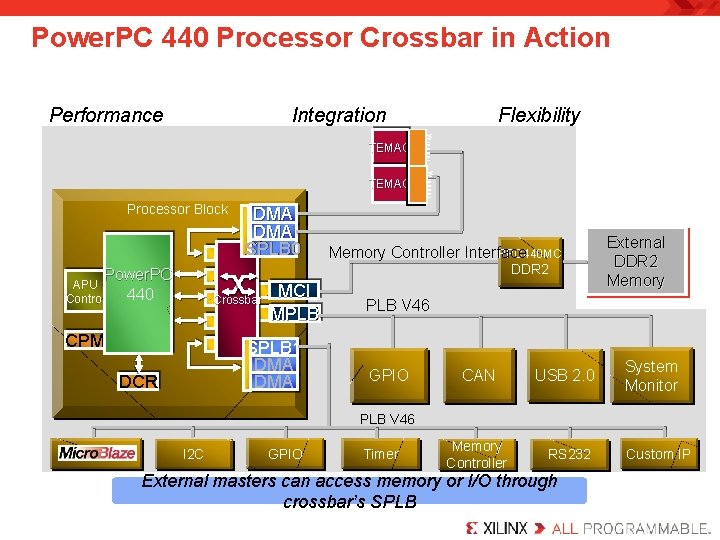

Power. PC 440 Processor Crossbar in Action Performance Integration T E MA C Wrapper DMA SPLB 0 T E MA C Wrapper Processor Block Flexibility Memory Controller Interface PPC 440 MC DDR 2 P o w e r. P C APU 440 Control Crossbar CPM MC I MP L B SPLB 1 DMA DCR External DDR 2 Memory PLB V 46 GPIO CAN USB 2. 0 System Monitor PLB V 46 I 2 C GPIO Timer Memory Controller RS 232 External masters can access memory or I/O through crossbar’s SPLB Custom IP

Lessons Hardware Overview PPC 440 Base System Builder Summary

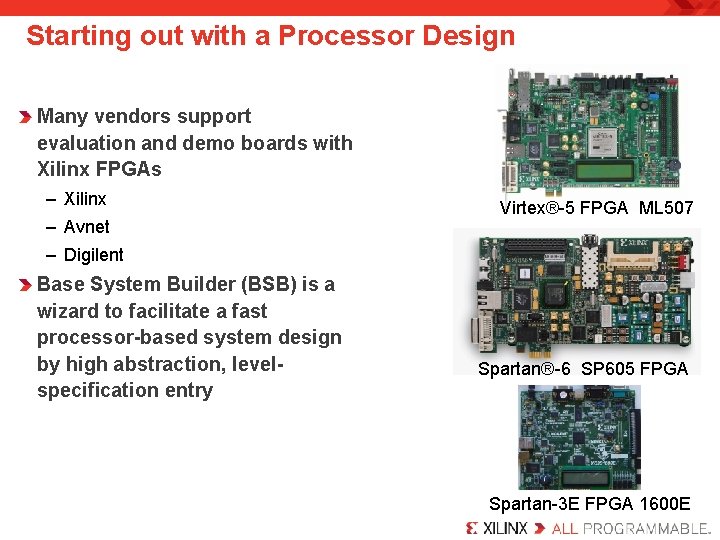

Starting out with a Processor Design Many vendors support evaluation and demo boards with Xilinx FPGAs – Xilinx – Avnet Virtex®-5 FPGA ML 507 – Digilent Base System Builder (BSB) is a wizard to facilitate a fast processor-based system design by high abstraction, levelspecification entry Spartan®-6 SP 605 FPGA Spartan-3 E FPGA 1600 E

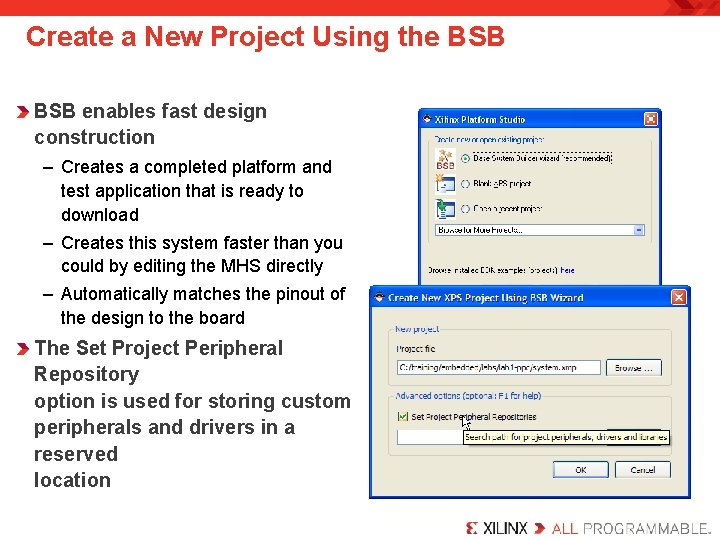

Create a New Project Using the BSB enables fast design construction – Creates a completed platform and test application that is ready to download – Creates this system faster than you could by editing the MHS directly – Automatically matches the pinout of the design to the board The Set Project Peripheral Repository option is used for storing custom peripherals and drivers in a reserved location

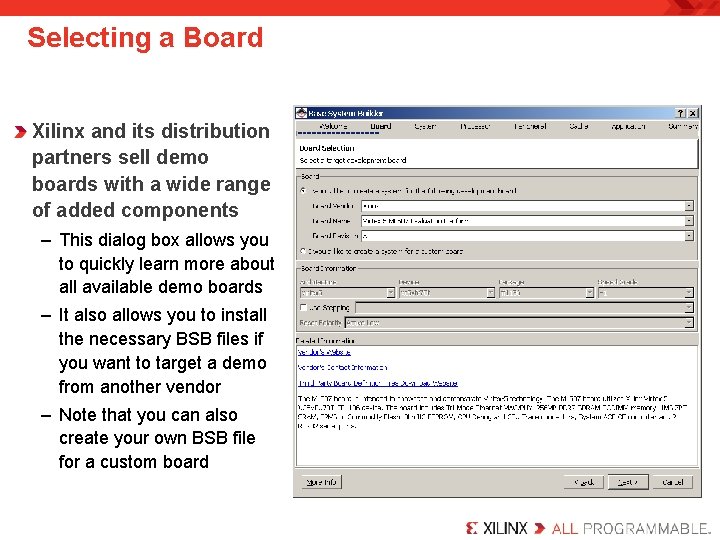

Selecting a Board Xilinx and its distribution partners sell demo boards with a wide range of added components – This dialog box allows you to quickly learn more about all available demo boards – It also allows you to install the necessary BSB files if you want to target a demo from another vendor – Note that you can also create your own BSB file for a custom board

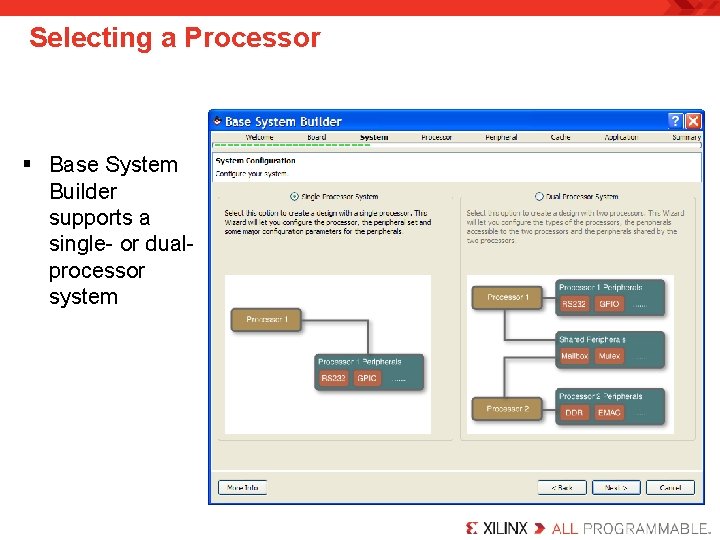

Selecting a Processor § Base System Builder supports a single- or dualprocessor system

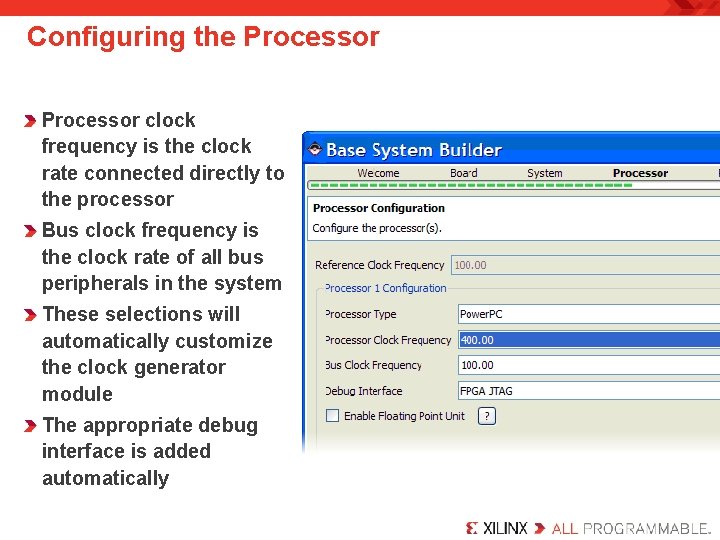

Configuring the Processor clock frequency is the clock rate connected directly to the processor Bus clock frequency is the clock rate of all bus peripherals in the system These selections will automatically customize the clock generator module The appropriate debug interface is added automatically

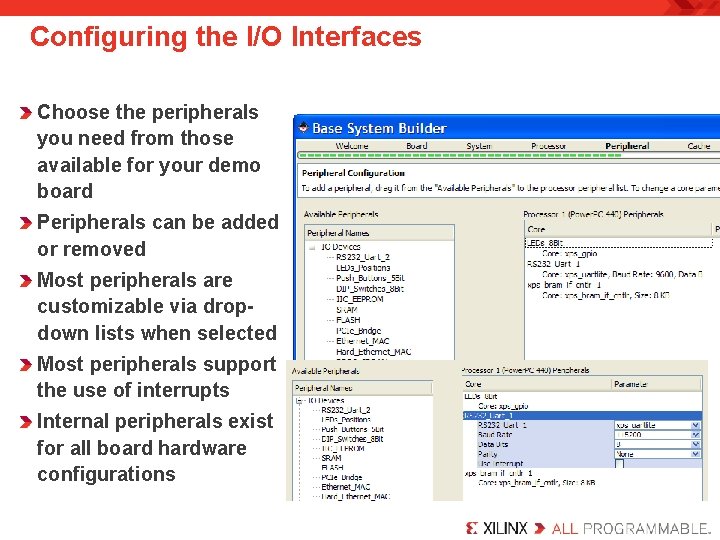

Configuring the I/O Interfaces Choose the peripherals you need from those available for your demo board Peripherals can be added or removed Most peripherals are customizable via dropdown lists when selected Most peripherals support the use of interrupts Internal peripherals exist for all board hardware configurations

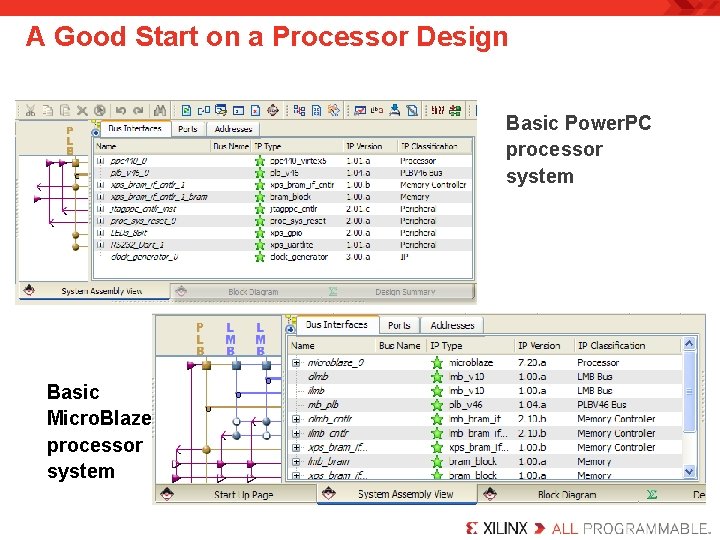

A Good Start on a Processor Design Basic Power. PC processor system Basic Micro. Blaze processor system

Lessons Hardware Overview PPC 440 Base System Builder Summary

Summary The PPC 440 processor crossbar switch speeds system performance utilizing an alternative architecture (to bus) that is 128 -bit wide – The crossbar clock is usually the fastest in the embedded system – All other embedded clocks are relative to the crossbar clock (bus, memory, DMA) The PPC 440 processor supports the attachment of one master PLB bus (for connection to slave peripherals) and two slave PLB buses (for connection to other system master components) The PPC 440 processor has a Memory Controller Interface (MCI) – Allows the fastest memory access possible by connecting to a Xilinx memory controller The PPC 440 processor has four DMA controller ports The PPC 440 APU supports co-processors built in FPGA fabric

Where Can I Learn More? Xilinx Embedded Processing page – www. support. xilinx. com/embedded – Learn more about Embedded Design Kits for all of our device families Xilinx online documents – www. support. xilinx. com • Getting Started with the Embedded Development Kit • Processor IP Reference Guide § Right-click any peripheral from the IP Catalog to learn more about it • Embedded Systems Tools Guide • Xilinx Drivers • Processor reference guides § Power. PC 405/440 Processor Block Reference Guide § Micro. Blaze Processor Reference Guide • For all docs, select Help EDK Online Documentation from the EDK tools

Where Can I Learn More? Xilinx Training Courses – www. xilinx. com/training • Embedded Systems Development course § Rapidly architect an embedded system § Introduction to most of the EDK tools • Embedded Systems Software Development course § Rapidly architect an embedded software system § Introduction to the SDK (Software Development Kit) • Advanced Embedded Systems Development course § Take advantage of advanced features of the PPC 440 § Apply advanced debugging techniques including Chip. Scope § Design a Flash memory-based system and boot load from off-chip Flash memory • Customers spend 50% of their time in lab

What’s Next? Related Video Courses – Embedded Design with the Micor. Blaze Soft Processor Core – Embedded Design with the Xilinx Embedded Developers Kit

Trademark Information Xilinx is disclosing this Document and Intellectual Property (hereinafter “the Design”) to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes. Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design. THE DESIGN IS PROVIDED “AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY. The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems (“High-Risk Applications”). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk. © 2012 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

- Slides: 37