Elmore Delay Logical Effort Modern Interconnect Rabaey ch

Elmore Delay, Logical Effort

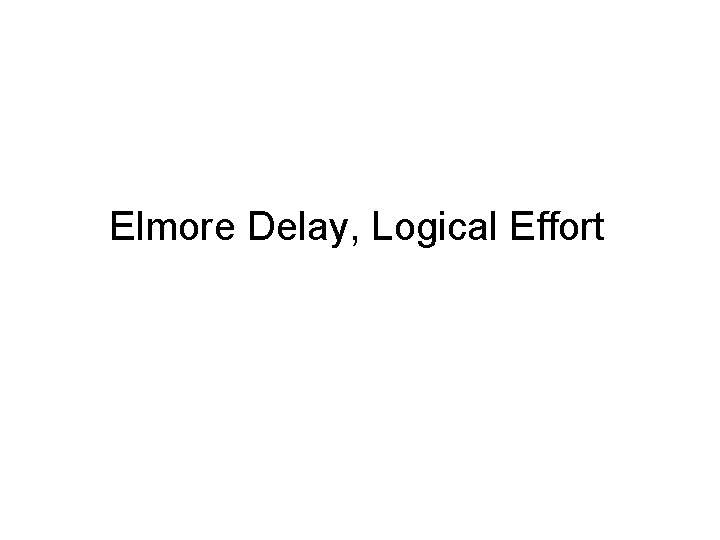

Modern Interconnect © Rabaey, ch 4 Wire. ppt, slide 22

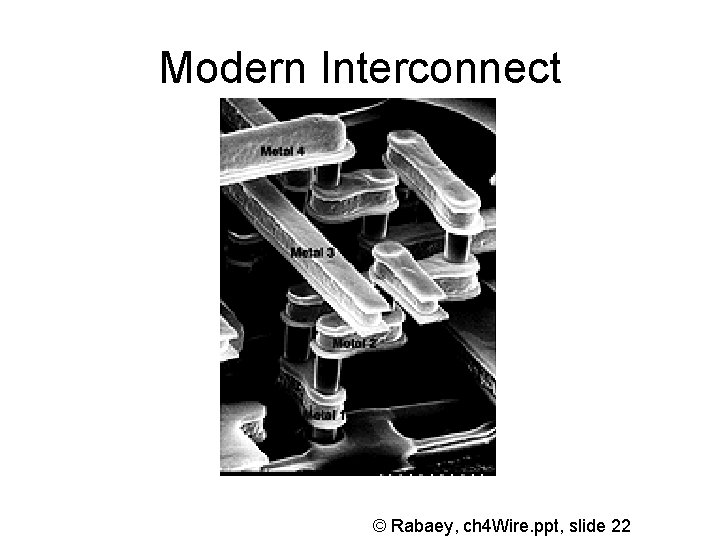

Example: Intel 0. 25 micron Process 5 metal layers Ti/Al - Cu/Ti/Ti. N Polysilicon dielectric © Rabaey, ch 4 Wire. ppt, slide 23

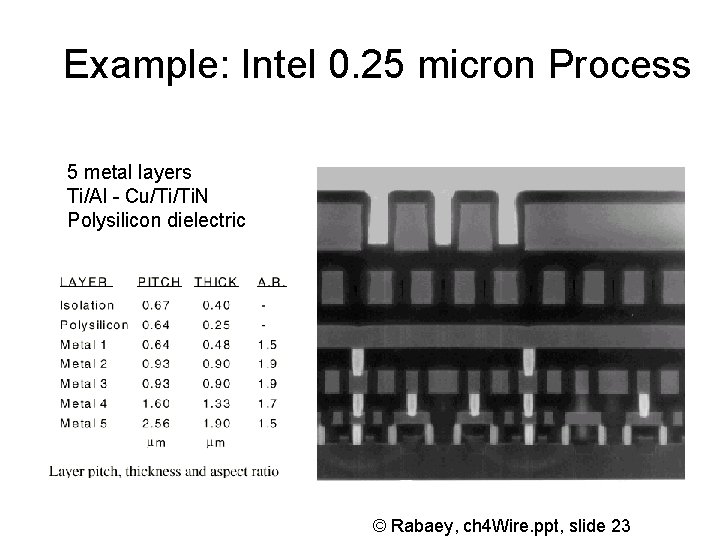

Modern Interconnect • 90 nm process © Chris Kim (image from Intel? )

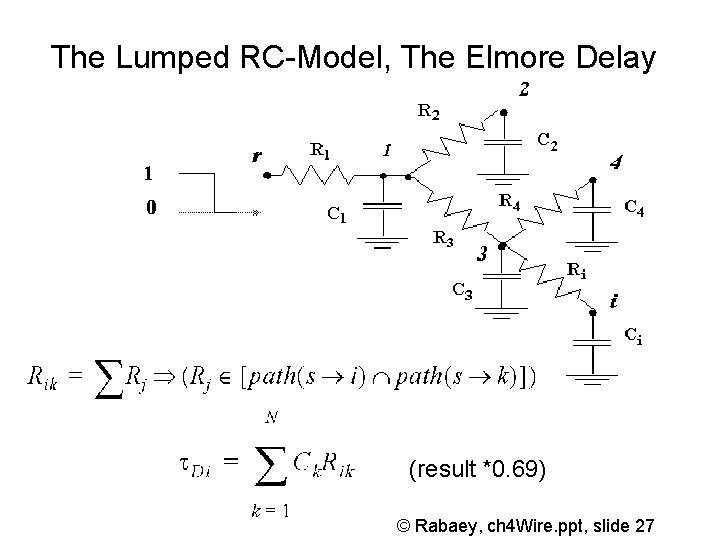

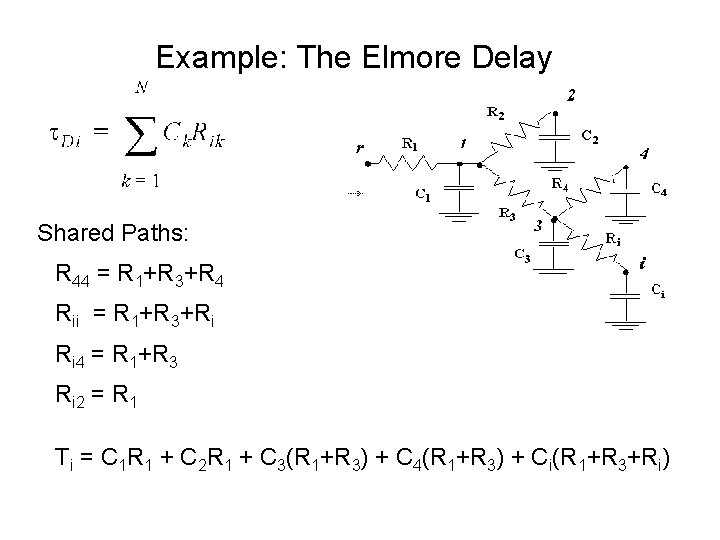

The Lumped RC-Model, The Elmore Delay (result *0. 69) © Rabaey, ch 4 Wire. ppt, slide 27

Example: The Elmore Delay Shared Paths: R 44 = R 1+R 3+R 4 Rii = R 1+R 3+Ri Ri 4 = R 1+R 3 Ri 2 = R 1 Ti = C 1 R 1 + C 2 R 1 + C 3(R 1+R 3) + C 4(R 1+R 3) + Ci(R 1+R 3+Ri)

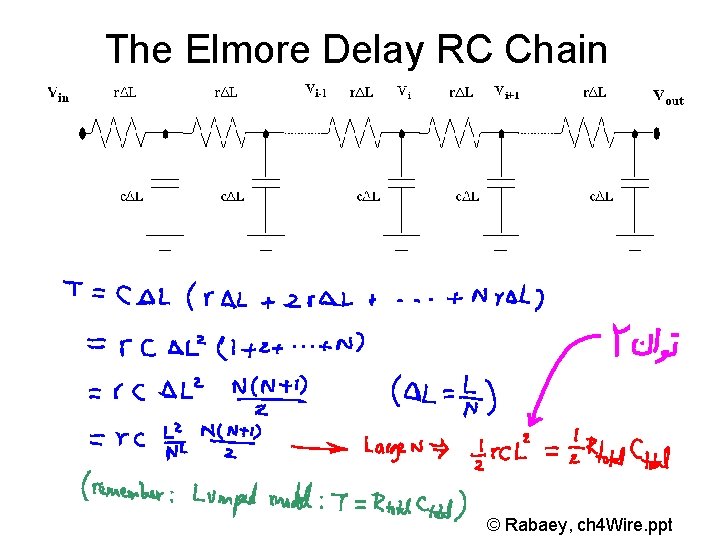

The Elmore Delay RC Chain © Rabaey, ch 4 Wire. ppt

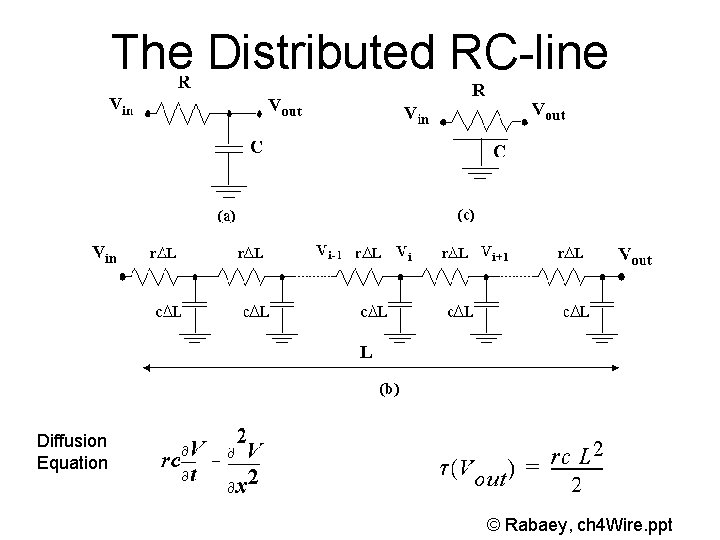

The Distributed RC-line Diffusion Equation © Rabaey, ch 4 Wire. ppt

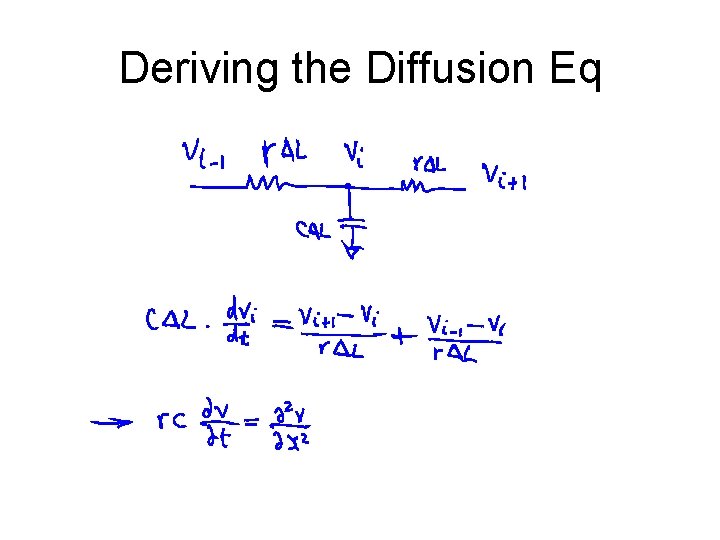

Deriving the Diffusion Eq

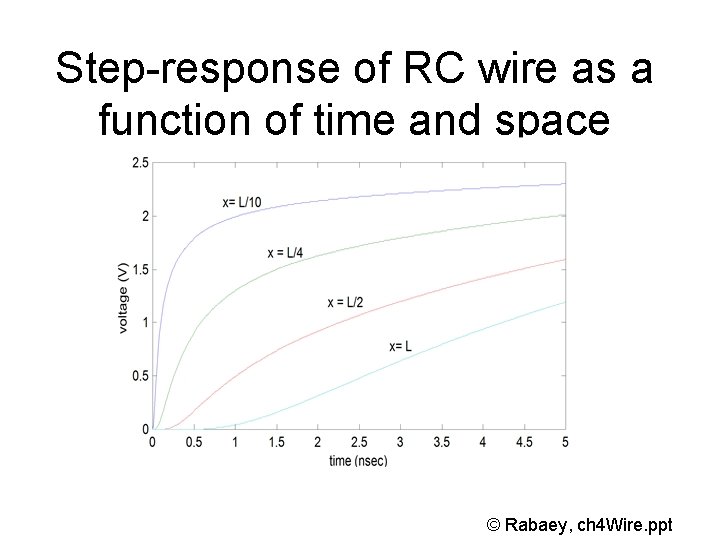

Step-response of RC wire as a function of time and space © Rabaey, ch 4 Wire. ppt

RC-Models © Rabaey, ch 4 Wire. ppt

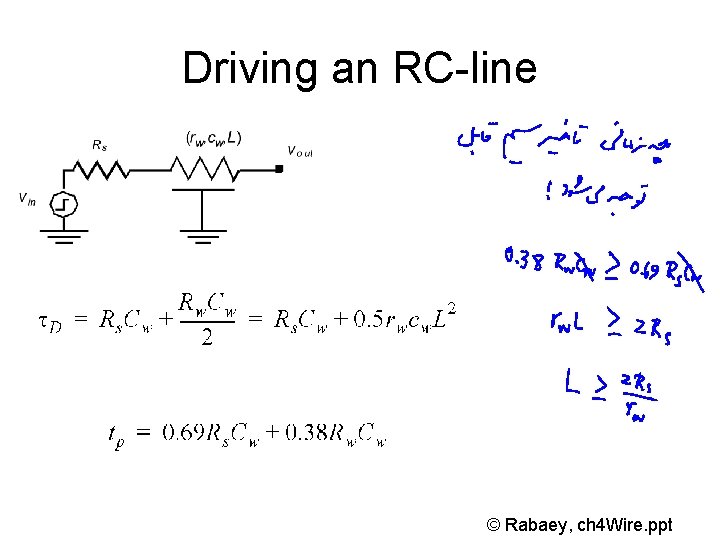

Driving an RC-line © Rabaey, ch 4 Wire. ppt

Designing Fast CMOS Gates Slides from chapter 6. ppt of Rabaey’s page

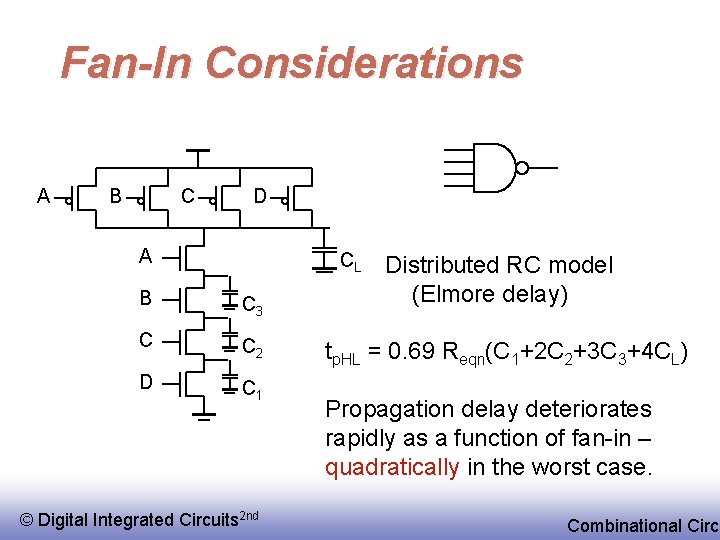

Fan-In Considerations A B C D A CL B C 3 C C 2 D C 1 © EE 141 Digital Integrated Circuits 2 nd Distributed RC model (Elmore delay) tp. HL = 0. 69 Reqn(C 1+2 C 2+3 C 3+4 CL) Propagation delay deteriorates rapidly as a function of fan-in – quadratically in the worst case. Combinational Circu

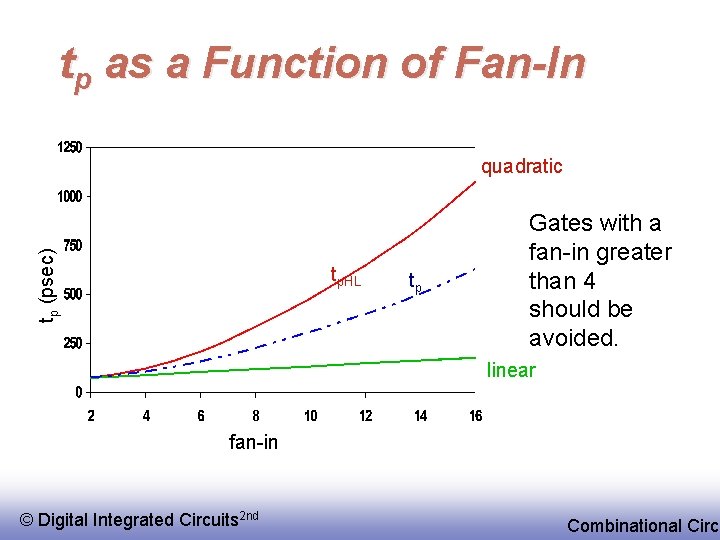

tp as a Function of Fan-In tp (psec) quadratic tp. HL tp tp. LH Gates with a fan-in greater than 4 should be avoided. linear fan-in © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

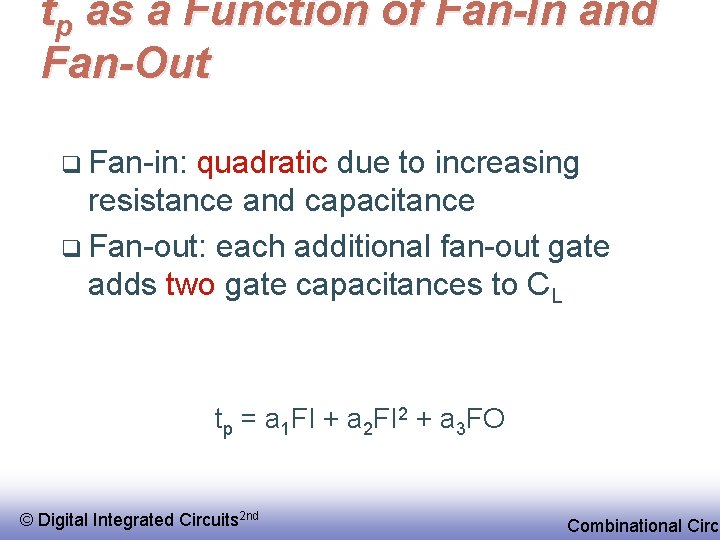

tp as a Function of Fan-In and Fan-Out q Fan-in: quadratic due to increasing resistance and capacitance q Fan-out: each additional fan-out gate adds two gate capacitances to CL tp = a 1 FI + a 2 FI 2 + a 3 FO © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

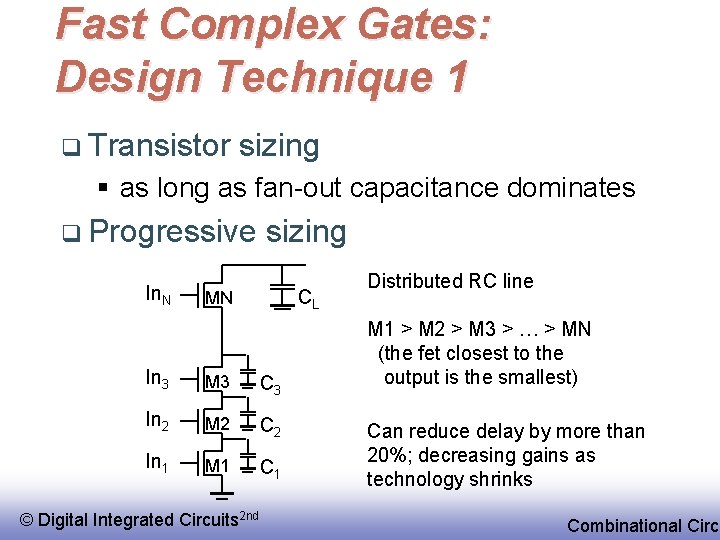

Fast Complex Gates: Design Technique 1 q Transistor sizing § as long as fan-out capacitance dominates q Progressive In. N sizing CL MN In 3 M 3 C 3 In 2 M 2 C 2 In 1 M 1 C 1 © EE 141 Digital Integrated Circuits 2 nd Distributed RC line M 1 > M 2 > M 3 > … > MN (the fet closest to the output is the smallest) Can reduce delay by more than 20%; decreasing gains as technology shrinks Combinational Circu

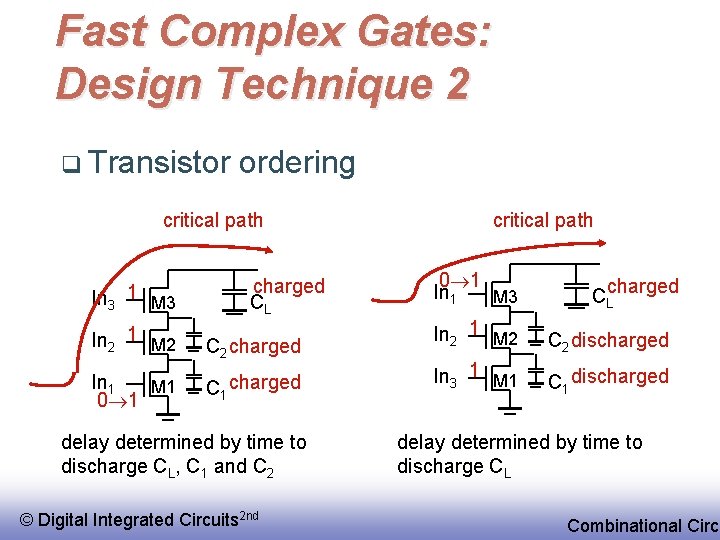

Fast Complex Gates: Design Technique 2 q Transistor ordering critical path In 3 1 M 3 charged CL In 2 1 M 2 C 2 charged In 1 M 1 0 1 C 1 charged delay determined by time to discharge CL, C 1 and C 2 © EE 141 Digital Integrated Circuits 2 nd critical path 0 1 In 1 M 3 CLcharged In 2 1 M 2 C 2 discharged In 3 1 M 1 C 1 discharged delay determined by time to discharge CL Combinational Circu

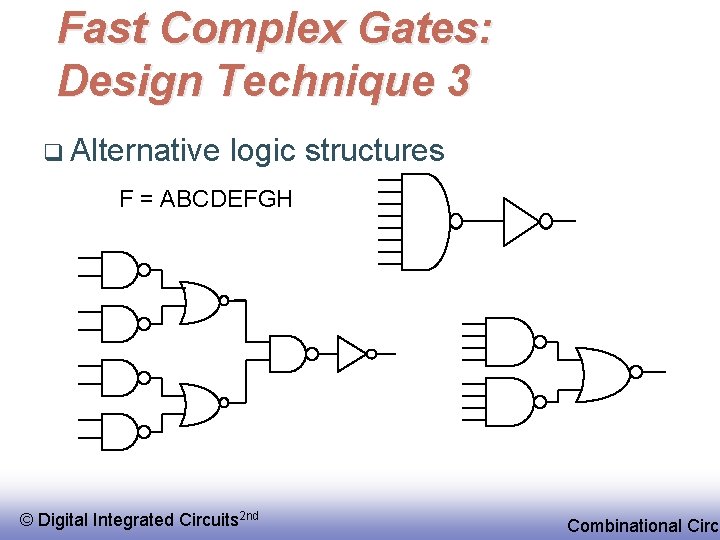

Fast Complex Gates: Design Technique 3 q Alternative logic structures F = ABCDEFGH © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

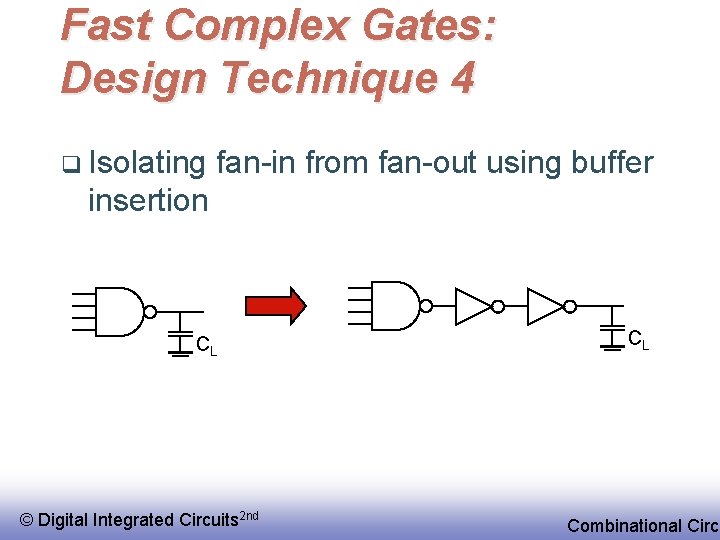

Fast Complex Gates: Design Technique 4 q Isolating fan-in from fan-out using buffer insertion CL © EE 141 Digital Integrated Circuits 2 nd CL Combinational Circu

Logical Effort Slides from chapter 6. ppt of Rabaey’s page

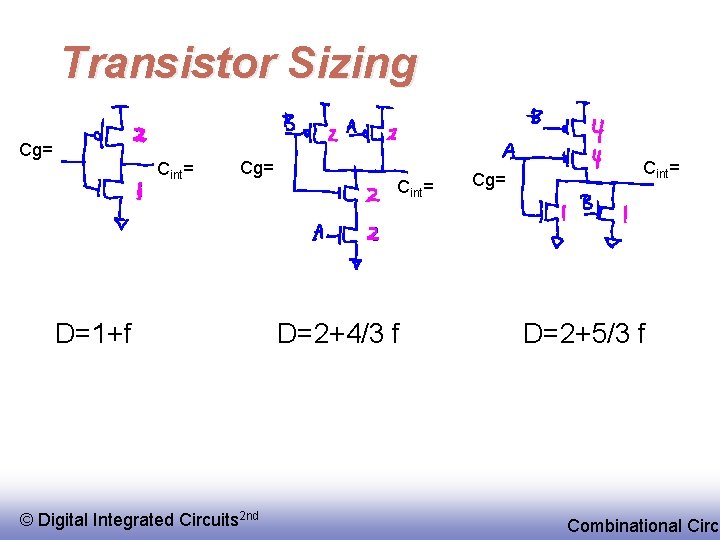

Transistor Sizing Cg= Cint= Cg= D=1+f © EE 141 Digital Integrated Circuits 2 nd Cint= D=2+4/3 f Cg= Cint= D=2+5/3 f Combinational Circu

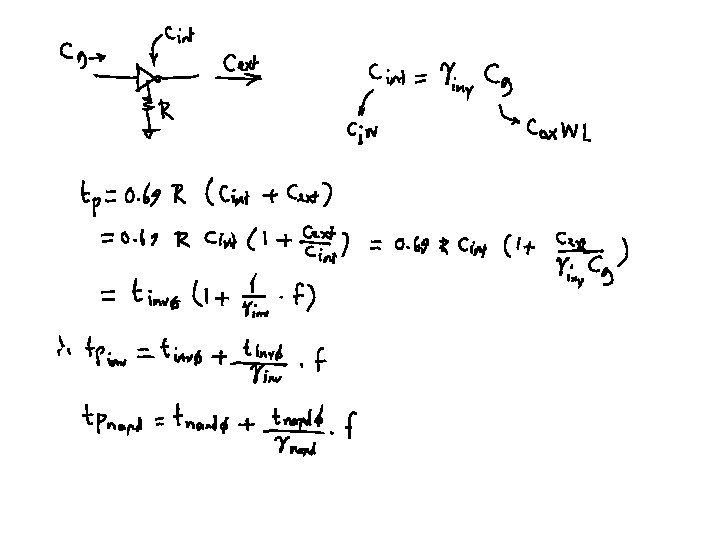

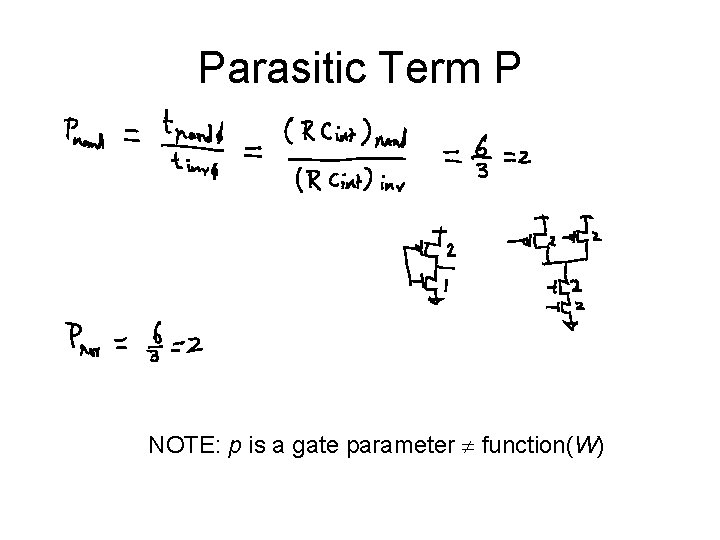

Normalized Space

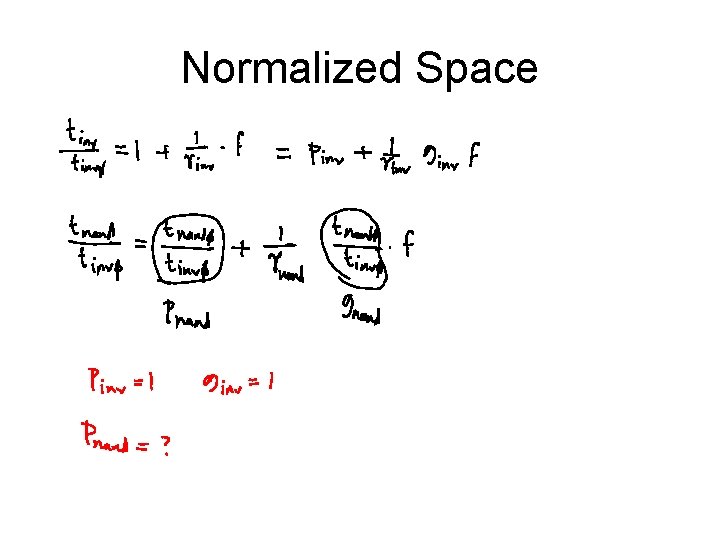

Parasitic Term P NOTE: p is a gate parameter function(W)

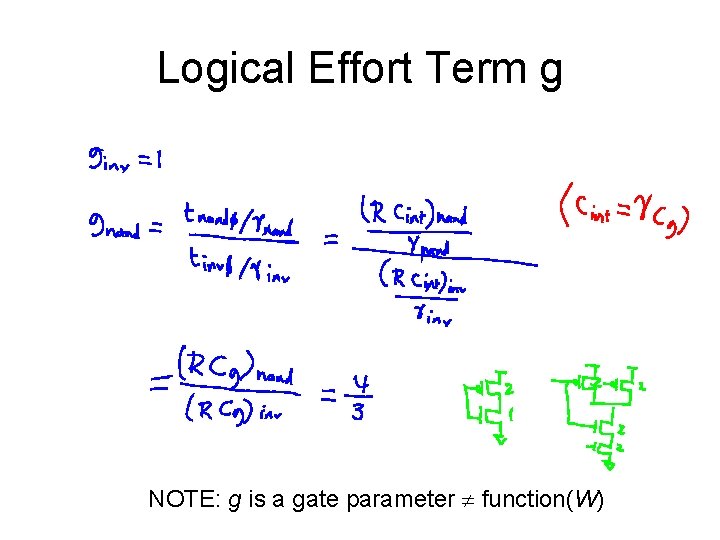

Logical Effort Term g NOTE: g is a gate parameter function(W)

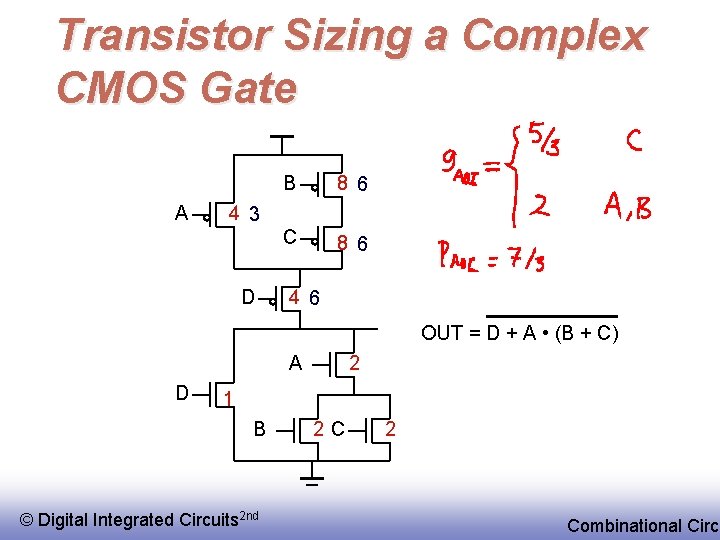

Transistor Sizing a Complex CMOS Gate A B 8 6 C 8 6 4 3 D 4 6 OUT = D + A • (B + C) A D 2 1 B © EE 141 Digital Integrated Circuits 2 nd 2 C 2 Combinational Circu

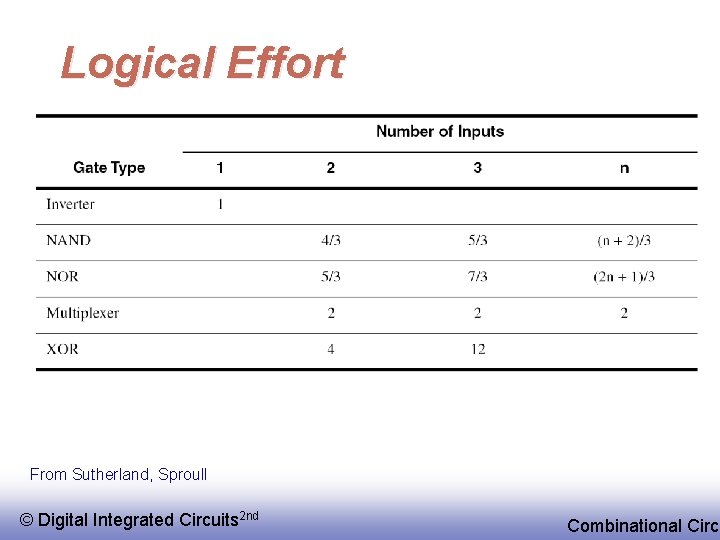

Logical Effort From Sutherland, Sproull © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

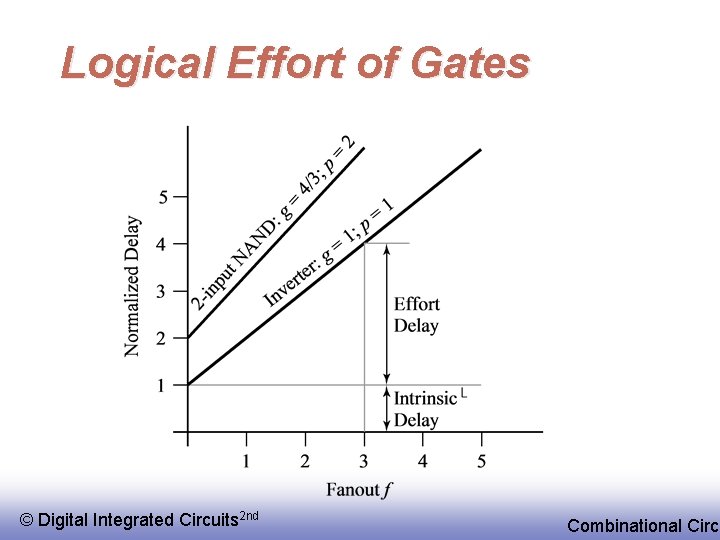

Logical Effort of Gates © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

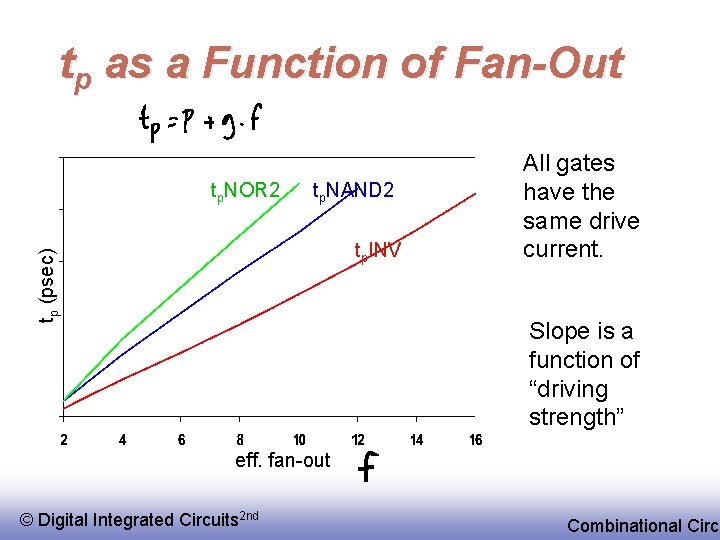

tp as a Function of Fan-Out tp. NOR 2 tp. NAND 2 tp (psec) tp. INV All gates have the same drive current. Slope is a function of “driving strength” eff. fan-out © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

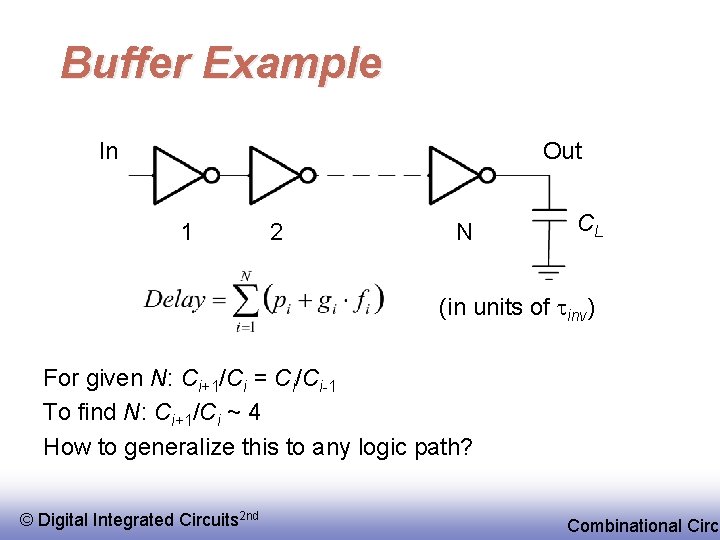

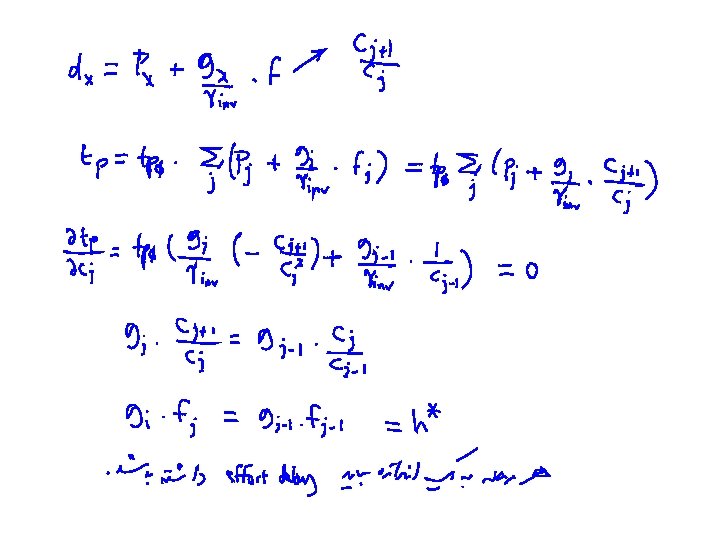

Buffer Example In Out 1 2 N CL (in units of tinv) For given N: Ci+1/Ci = Ci/Ci-1 To find N: Ci+1/Ci ~ 4 How to generalize this to any logic path? © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

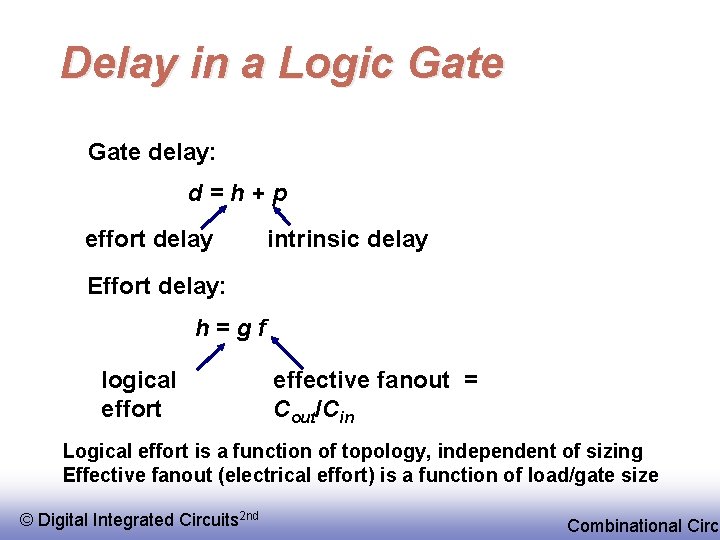

Delay in a Logic Gate delay: d=h+p effort delay intrinsic delay Effort delay: h=gf logical effort effective fanout = Cout/Cin Logical effort is a function of topology, independent of sizing Effective fanout (electrical effort) is a function of load/gate size © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

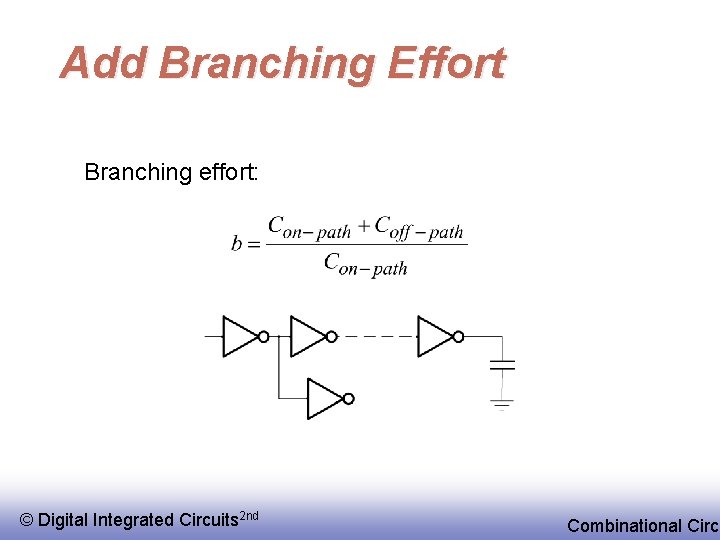

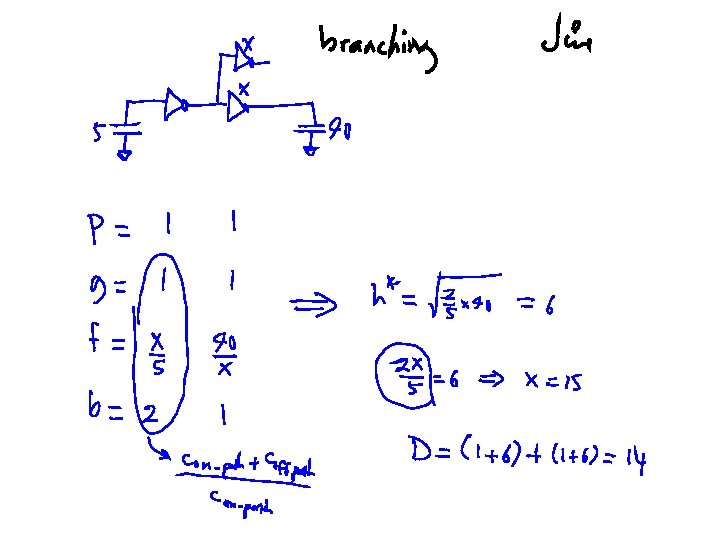

Add Branching Effort Branching effort: © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

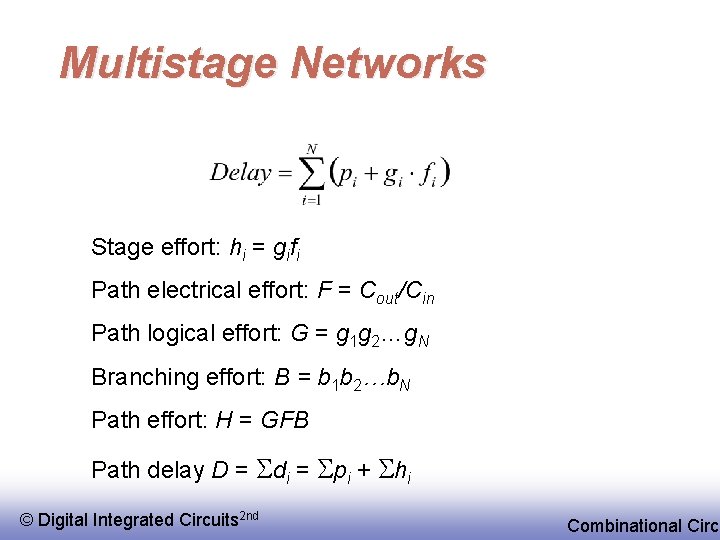

Multistage Networks Stage effort: hi = gifi Path electrical effort: F = Cout/Cin Path logical effort: G = g 1 g 2…g. N Branching effort: B = b 1 b 2…b. N Path effort: H = GFB Path delay D = Sdi = Spi + Shi © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

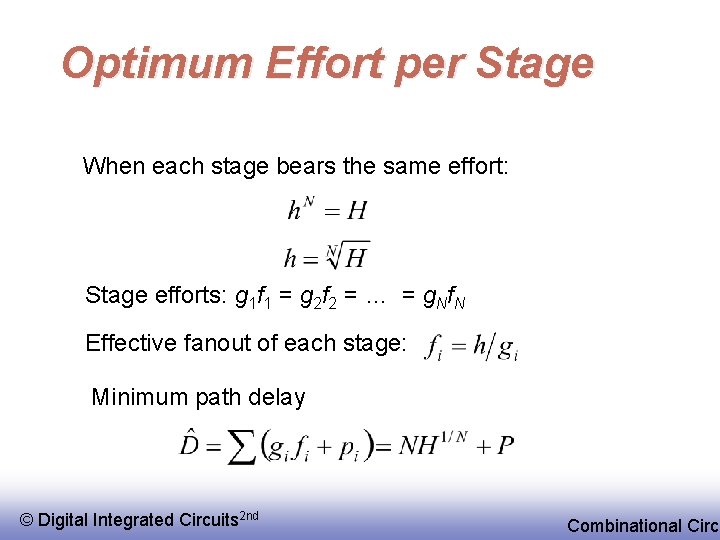

Optimum Effort per Stage When each stage bears the same effort: Stage efforts: g 1 f 1 = g 2 f 2 = … = g. Nf. N Effective fanout of each stage: Minimum path delay © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

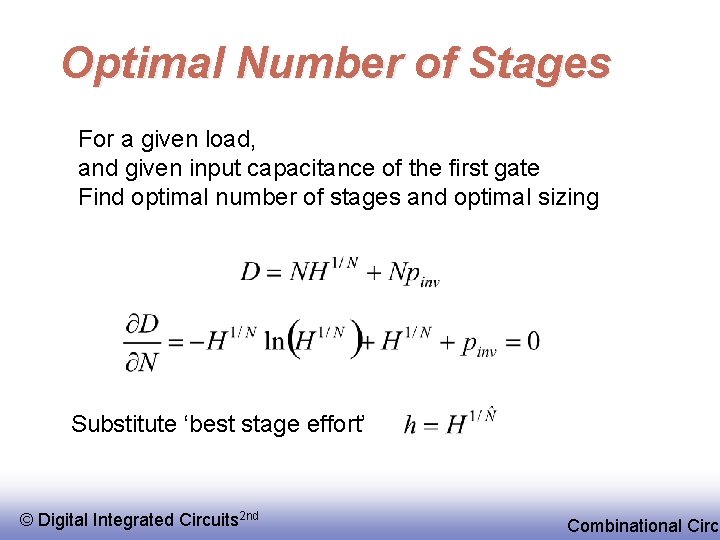

Optimal Number of Stages For a given load, and given input capacitance of the first gate Find optimal number of stages and optimal sizing Substitute ‘best stage effort’ © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

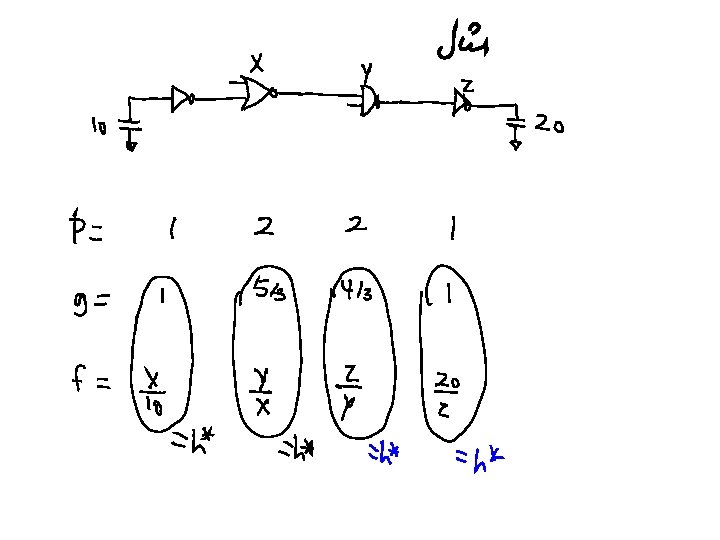

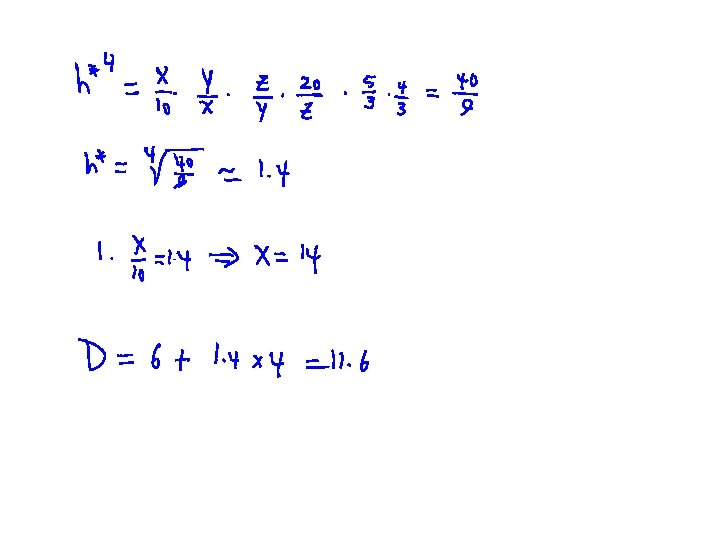

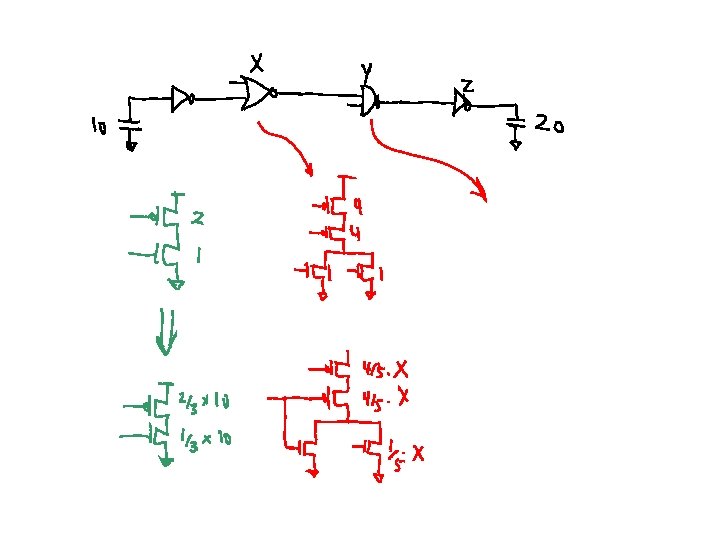

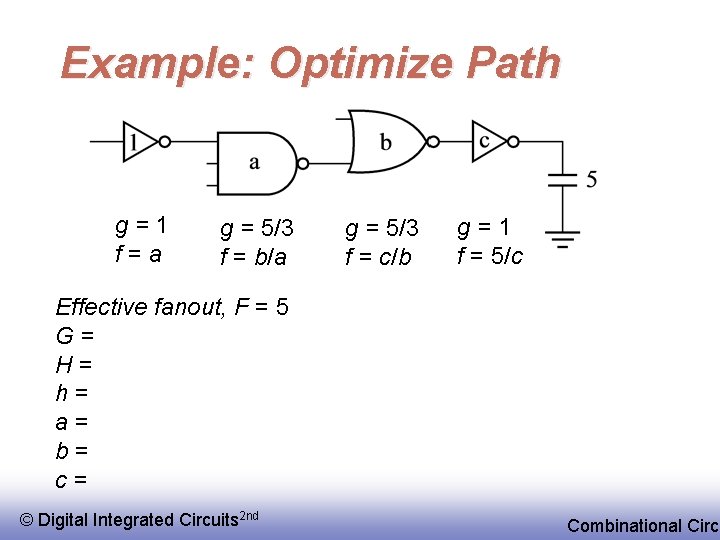

Example: Optimize Path g=1 f=a g = 5/3 f = b/a g = 5/3 f = c/b g=1 f = 5/c Effective fanout, F = 5 G= H= h= a= b= c= © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

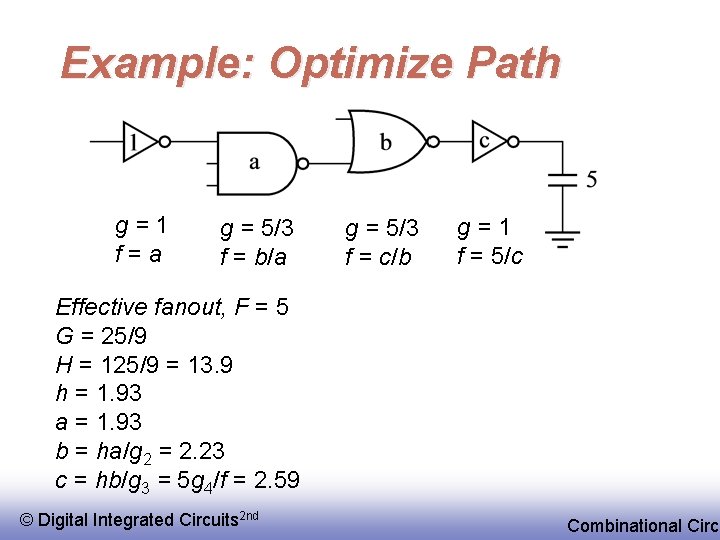

Example: Optimize Path g=1 f=a g = 5/3 f = b/a g = 5/3 f = c/b g=1 f = 5/c Effective fanout, F = 5 G = 25/9 H = 125/9 = 13. 9 h = 1. 93 a = 1. 93 b = ha/g 2 = 2. 23 c = hb/g 3 = 5 g 4/f = 2. 59 © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

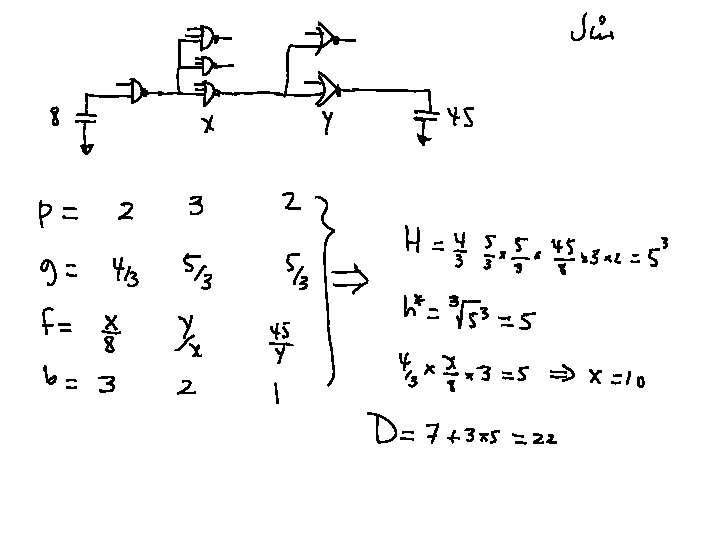

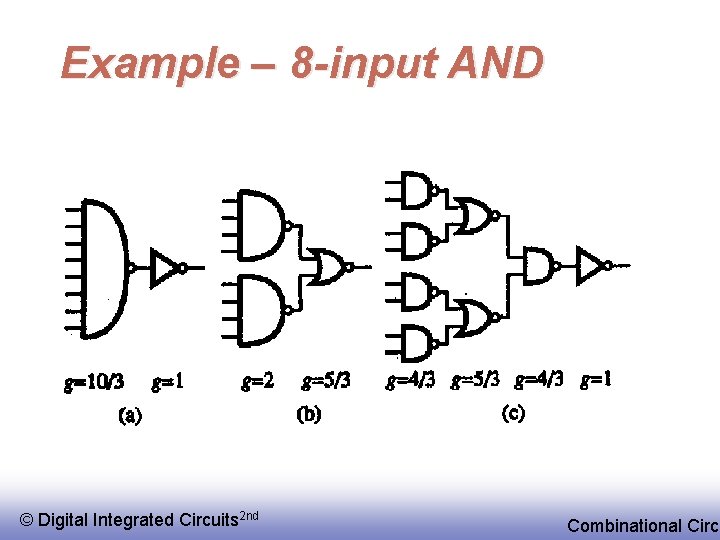

Example – 8 -input AND © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

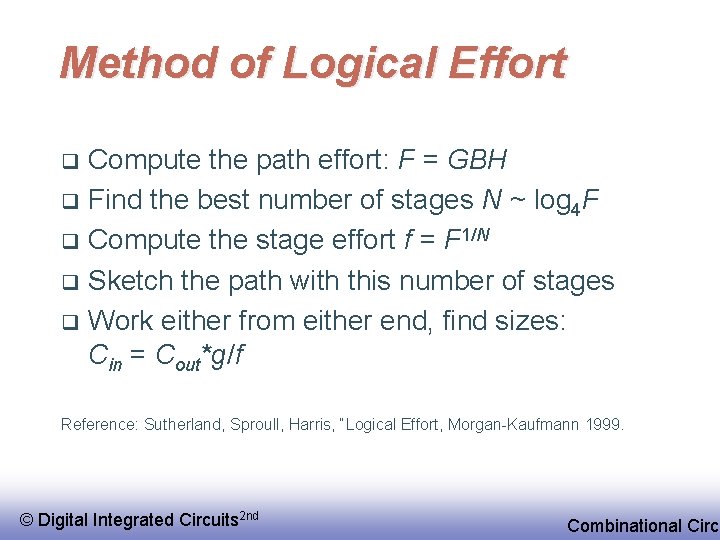

Method of Logical Effort Compute the path effort: F = GBH q Find the best number of stages N ~ log 4 F q Compute the stage effort f = F 1/N q Sketch the path with this number of stages q Work either from either end, find sizes: Cin = Cout*g/f q Reference: Sutherland, Sproull, Harris, “Logical Effort, Morgan-Kaufmann 1999. © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

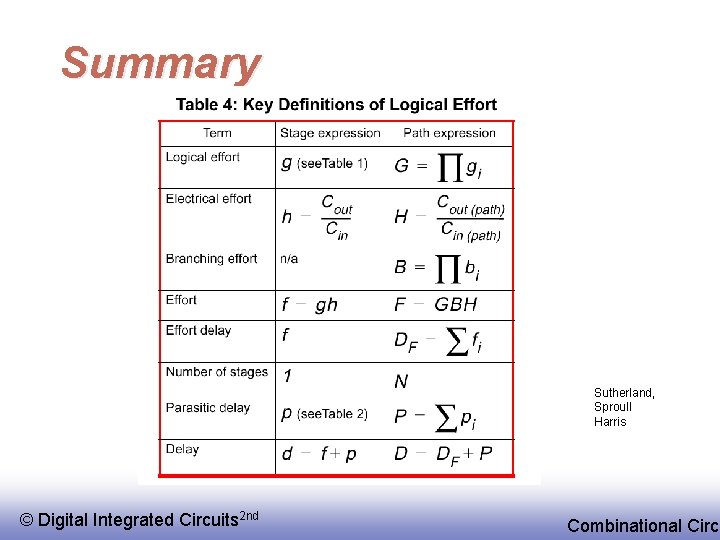

Summary Sutherland, Sproull Harris © EE 141 Digital Integrated Circuits 2 nd Combinational Circu

- Slides: 47